4;;

ГС

со

00 9

Изобретение относится к импульс н|ой технике и может быть использо- в|ано в различных устройствах дискрет- йой автоматики.

Цель изобретения - расширение функциональных возможностей устройства за счет выполнения дополнитель-. НОЙ контролируемой функщш 2НЕ.

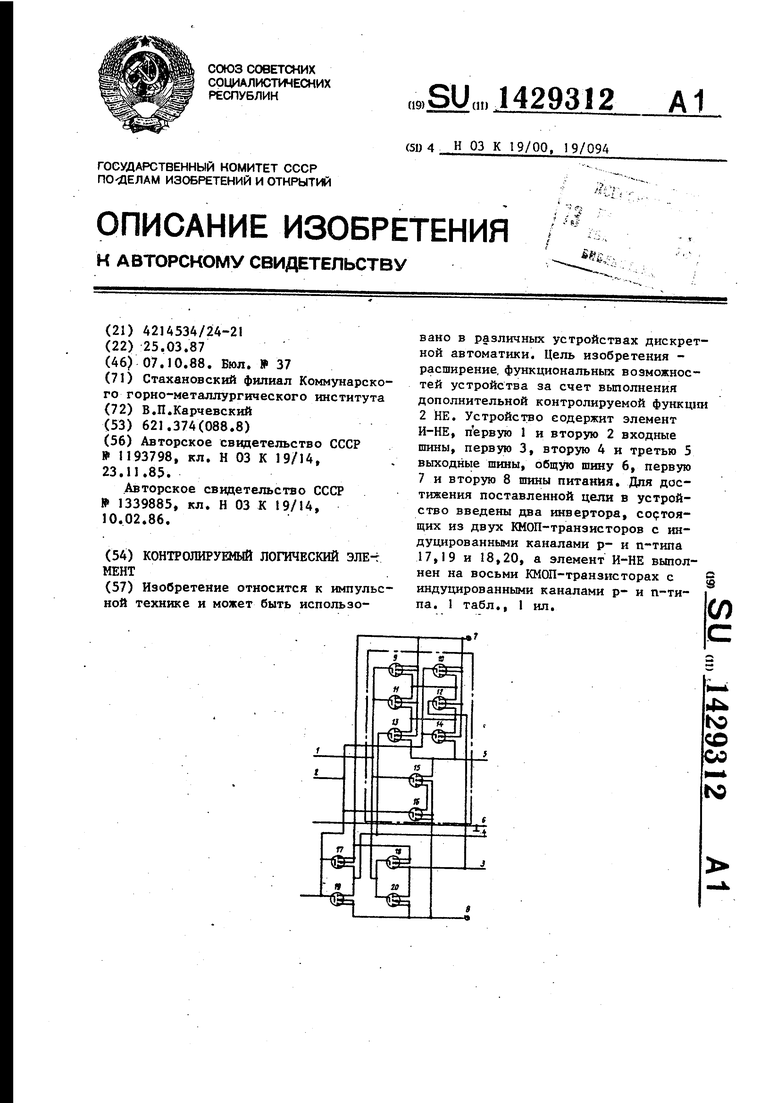

На чертеже представлена принципи- г1льная схема контролируемого логи- lecKoro элемента.

Контролируемый элемент содержит первую 1 и вторую 2 входные шины, первую 3, вторую 4 и третью 5 вы- гчодяые шины, общую шину 6, первую 7 л вторую 8 шины питания, КМОП-тран- |9исторы 9-20 с индуцированным кана- J10M. Транзисторы 9-14, 17, 18 относятся к транзисторам с каналом р-ти- па, а транзисторы 15, 16, 19 и 20 - с каналом п-типа. Входная шина 1 роединена с затворами транзисторов 9, 11, 15, 18 и 20, а входн ая шина 2-е затворами транзисторов 10, 1А, 16, 17 и 19. Первая шина 7 питания соединена с истоками транзисторов 9, 10, 17 и 18, к которой также подключены подложки транзисторов 9-14, 17 и 18. Вторая шина 8 питания соединена с истоками транзисторов 16, 19 и 20, к которой также подключены подложки транзисторов 15, 16, 19 и 20. Стоки транзисторов 18 и 20, а также затвор транзистора 12 подключены к первой выходной шине 3. Стоки транзисторов 17 и 19, а также затвор транзистора 13 подключены к второй, выходной шине 4. Стоки транзисторов 9, 10 и источник транзисторов 11, 12 соединены между собой. Соединены между собой также стоки транзисторов П, 12 и истоки транзисторов 13 и 14, а стоки транзисторов 13, 14 и 15- соединены между собой и подклю- чены к третьей выходной шине 5.

Контролируемый логический элемент управляется разнополярными уровнями двоичных логических сигналов U и Uo и сигналом об отказе в самом элементе или в цепях, связанных со входами данного элемента, уровень такого сигнала обозначается Uj,

Питание элемента осуществляется положительным напряжением +Е и от- рицательньм напряжением -Е относительно общей шины 6, которые подаются соответственно на шины питания 7 и 8.

0

5

КМОП-транзисторы проводят ток, когда напряжение затвора превысит некоторое отпиранлцее, или пороговое значение Чадр.

Для эффективной работы устройства желательно использовать транзисторы с пороговым напряжением порядка 60- 70% от номинального напряжения питания (2Е).

Сигнал с уровнем больше V и меньше +Е считает логическим сигна- лом с уровнем U,, т.е. 4 U Ei аналогично -Е Uo - Unop а -Uno,. и- + .

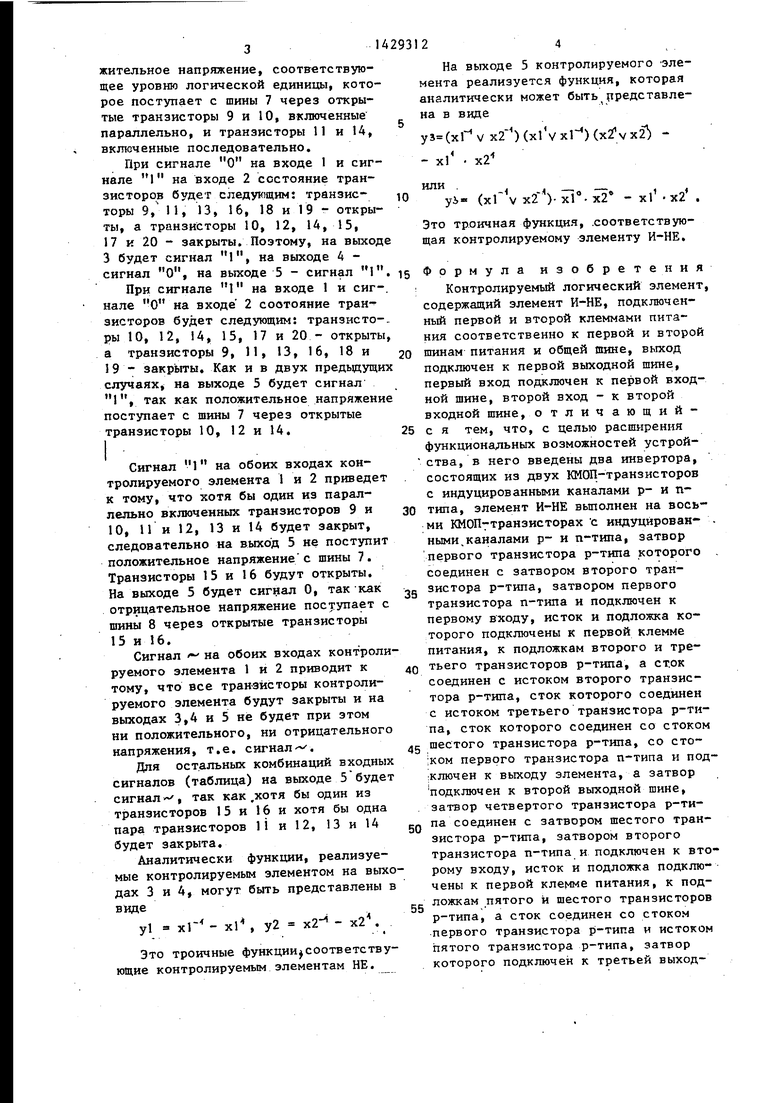

В таблице приведено соответствие выходных сигналов контролируемого элемента всем возможным комбинациям входных сигналов.

О

Сигнал О на обоих входах контролируемого элемента 1 и 2 приведет к отпиранию транзисторов с индуцированным каналом р-типа 9-11 14, 17 и 18. Транзисторы 15, 16, 19 и 20 с каналом п-типа, затворы которых соединены со входами 1 и 2, будут закрыты. Открытые транзисторы 17 и 18 обеспечивают поступление с шины 7 на выходы 3 и 4 элемента положительного напряжения, соответствующего уровню логической единицы. Так как затворы транзисторов 12 и 13 с каналом р-типа соединены с выходами элемента 3 и 4, то эти транзисторы будут закрыты. На выходе элем(шта 5 будет положительное напряжение, соотнетствую- щее уровню логической единицы, которое поступает с шины 7 через открытые транзисторы 9 и 10, включенные параллельно, и транзисторы 11 и 14, включенные последовательно.

При сигнале О на входе 1 и сигнале 1 на входе 2 состояние транзисторов будет следующим: транзис- торы 9, 11, 13, 16, 18 и 19 - открыты, а транзисторы 10, 12, 14, 15, 17 к 20 - закрыты. Поэтому, на выход 3 будет сигнал 1, на выходе 4 - сигнал О, на выходе 5 - сигнал 1

При сигнале 1 на входе 1 и сигнале О на входе 2 состояние тран- зисторов будет следующим: транзисторы 10, 12, 14, 15, 17 и 20 - открыты а транзисторы 9, 11, 13, 16, 18 и 19 - закрыты. Как и в двух предьдущи случаях на выходе 5 будет сигнал 1, так как положительное напряжени поступает с шины 7 через открытые транзисторы 10, 12 и 14.

Сигнал 1 на обоих входах контролируемого элемента 1 и 2 приведет к тому, что хотя бы один из параллельно включенных транзисторов 9 и 10, Пи 12, 13 и 14 будет закрыт, следовательно на выход 5 не поступит положительиое напряжение с шины 7. Транзисторы 15 и 16 будут открыты. На выходе 5 будет сигнал О, так как отрицательное напряжение поступает с шины 8 через открытые транзисторы 15 и 16.

Сигнал - на обоих входах контролируемого элемента 1 и 2 приводит к тому, что все тран-зйсторы контролируемого элемента будут закрыты и на выходах 3,4 и 5 не будет при этом ни положительного, ни отрицательного напряжения, т.е. сигнал-,

Для остальных комбинаций входных сигналов (таблица) на выходе 5 будет сигнал - , так как .хотя бы один из транзисторов 15 и 16 и хотя бы одна пара транзисторов П и 12, 13 и 14 будет закрыта.

Аналитически функции, реализуемые контролируемым элементом на выходах 3 и 4, могут быть представлены в виде

у1 х1, у2 х2- - х2

Это троичные функции соответству- ющие контролируемым элементам НЕ.

14293124

На выходе 5 контролируемого элемента реализуется функция, которая аналитически может быть цредставле- на в виде

y3(xl v x2 )(xlVxl)(x2 vx2 - хГ . х2

или

yi- (хГЧ х2 )- хГ. х2 - xl х2 .

Это троичная функция, .соответствующая контролируемому злементу И-НЕ.

Формула изобретения Контролируемый логический элемент содержащий элемент И-НЕ, подключенный первой и второй клеммами питания соответственно к первой и второй шинам питания и общей тине, выход подключен к первой выходной шине, первый вход подключен к первой входной шине, второй вход - к второй входной шине, отличающий- с я тем, что, с целью расширения функциональных возможностей устройства, в него введены два инвертора, состоящих из двух КМОП-транзисторов с индуцированными каналами р- и п- типа, элемент И-НЕ выполнен на восьми КМОП- транзисторах с индуцирован- ными,каналами р- и п-типа, затвор первого транзистора р-тнпа которого соединен с затвором второго транзистора р-типа, затвором первого транзистора п-типа и подключен к первому входу, исток и подложка которого подключены к первой клемме питания, к подложкам второго и третьего транзисторов р-типа, а сток соединен с истоком второго транзистора р-типа, сток которого соединен с истоком третьего транзистора р-типа, сток которого соединен со стокам шестого транзистора р-типа, со сто ;ком первого транзистора п-типа и под ;ключен к выходу элемента, а затвор подключен к второй выходной шине, затвор четвертого транзистора р-типа соединен с затвором шестого транзистора р-типа, затвором второго транзистора п-типа и подключен к второму входу, исток и подложка подключены к первой клемме питания, к подложкам пятого И шестого транзисторов р-типа, а сток соединен со стоком первого транзистора и истоком пятого транзистора р-типа, затвор которого подключен к третьей выходмой шине, а сток соединен со стокоК BlTopdro транзистора р-типа и истоком п естого транзистора р-типа, исток первого транзистора п-типа соединен cto стоком второго транзистора п-типа ai подложка соединена с подложкой и фтоком второго транзистора п-типа и п|одклгочена к второй клемме питания, з|атвор седьмого транзистора р-типа njepBoro инвертора соединен с затвором третьего транзистора п-типа пер- вЬго инвертора и подключен к второй вкодйой Шине, исток соединен с под- лржкой и подключен к первой шине пи- , а сток соединен со ctoKOM

0

5

третьего транзистора п-типа и второй выходной шинойу исток третьего транзистора п-типа первого инвертора подключен к подложке и второй шине питания, затвор восьмого транзистора р-типа второго инвертора соединен с затвором четвертого транзистора п-типа второго инвертора и первой входной шиной, исток соединен с подложкой и подключен к первой шине питания, а сток подключен к третьей выходной шине и стоку четвертого транзистора п-типа, исток и подложка которого подключены к второй шийе питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1989 |

|

SU1723667A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

| Многоканальный коммутатор | 1982 |

|

SU1078616A1 |

| Формирователь сигнала начальной установки делителя частоты кварцевых наручных часов | 1986 |

|

SU1365041A1 |

| Циклический инвертор на КМОП-транзисторах | 1985 |

|

SU1352642A1 |

| Циклический инвертор @ ( @ ) на КМОП-транзисторах | 1985 |

|

SU1287280A1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| Ключевой элемент | 1984 |

|

SU1202048A1 |

Изобретение относится к импульсной технике и может быть использовано в различных устройствах дискретной автоматики. Цель изобретения - расширение, функциональных возможностей устройства за счет выполнения дополнительной контролируемой функции 2 НЕ. Устройство содержит элемент И-НЕ, п ервую 1 и вторую 2 входные шины, первую 3, вторую 4 и третью 5 выходные шины, общую шину 6, первую 7 и вторую 8 шины питания. Для достижения поставленной цели в устройство введены два инвертора, сортоя- щих из двух КМОП-транзисторов с индуцированными каналами р- и п-типа 17,19 и 18,20, а элемент И-НЕ выполнен на восьми КМОП-транзисторах с индуцированными каналами р- и п-типа. 1 табл., 1 ил. (Л

| 0 |

|

SU93798A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Контролируемый логический элемент И-НЕ | 1986 |

|

SU1339885A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1987-03-25—Подача