Изобретение относится к импульсной .технике и может быть использовано в различных цифровых устройствах с четырехзначным алфавитом.

Целью изобретения является выпол- нение логической функции X+2/mod4/ путем использования резисторной матрицы типа R-2R-R.

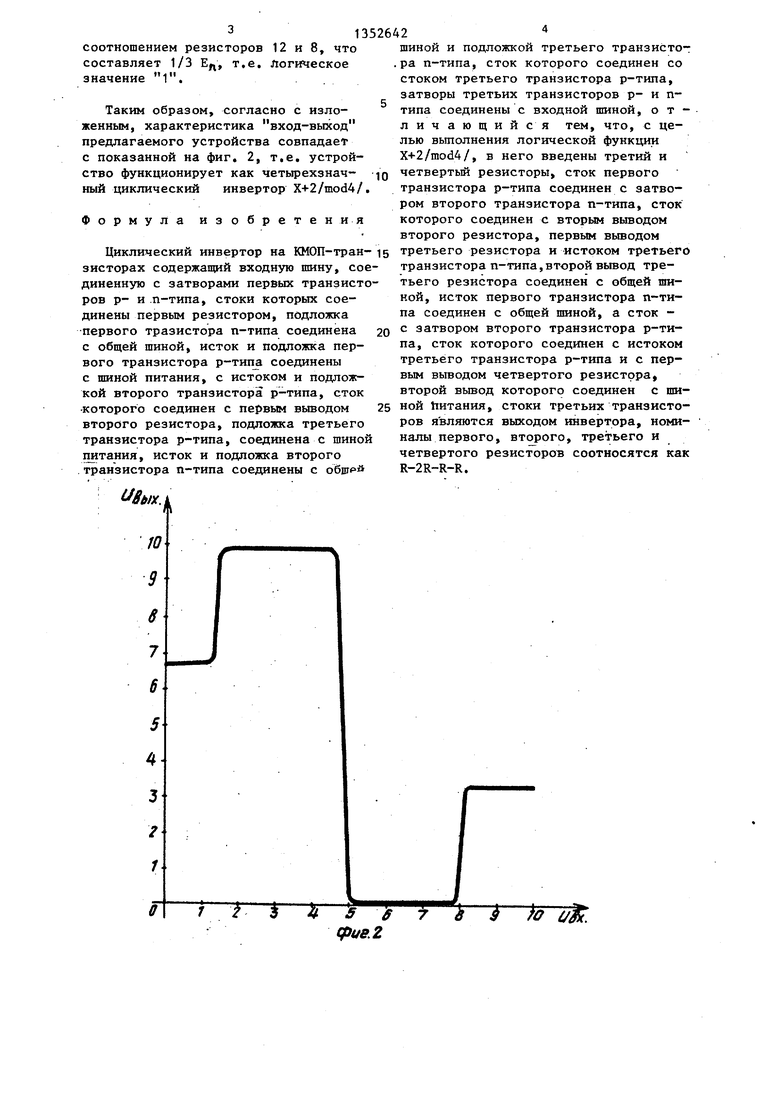

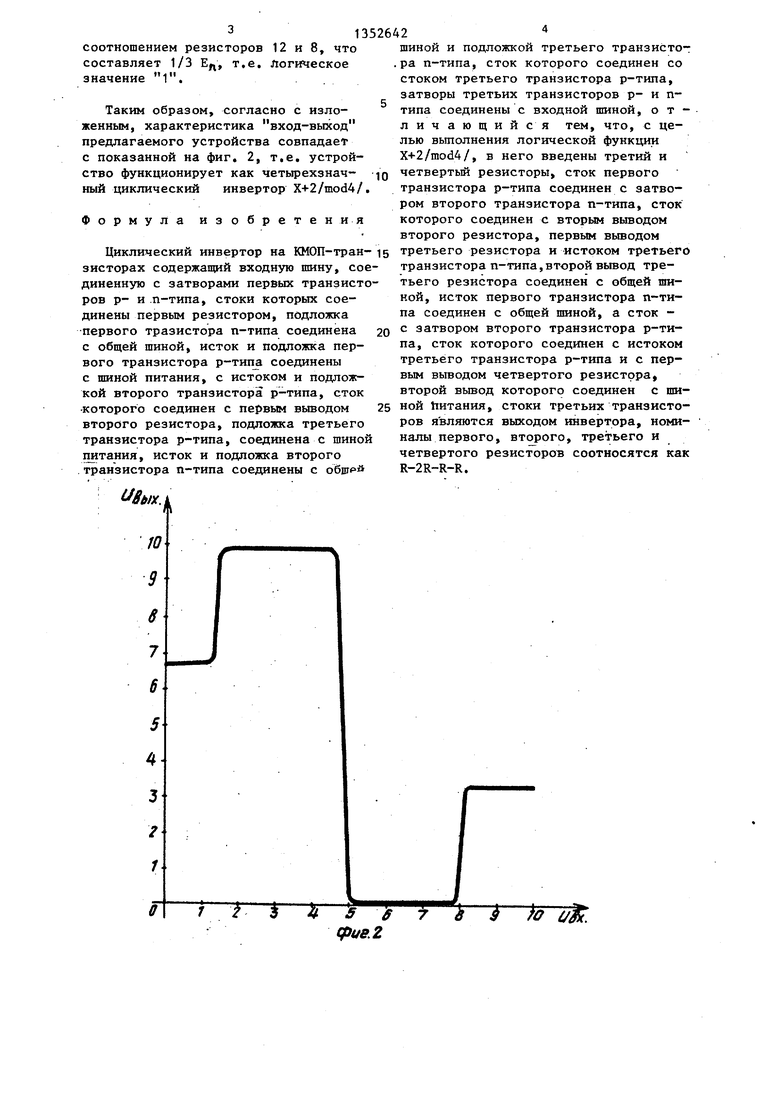

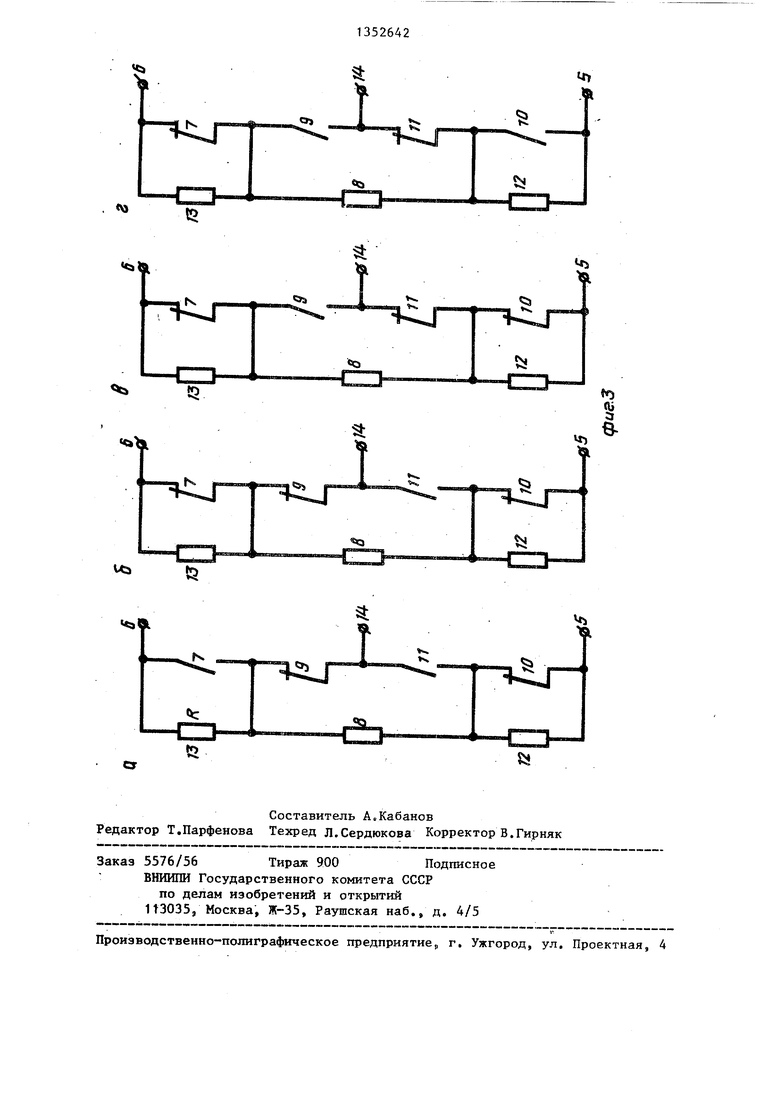

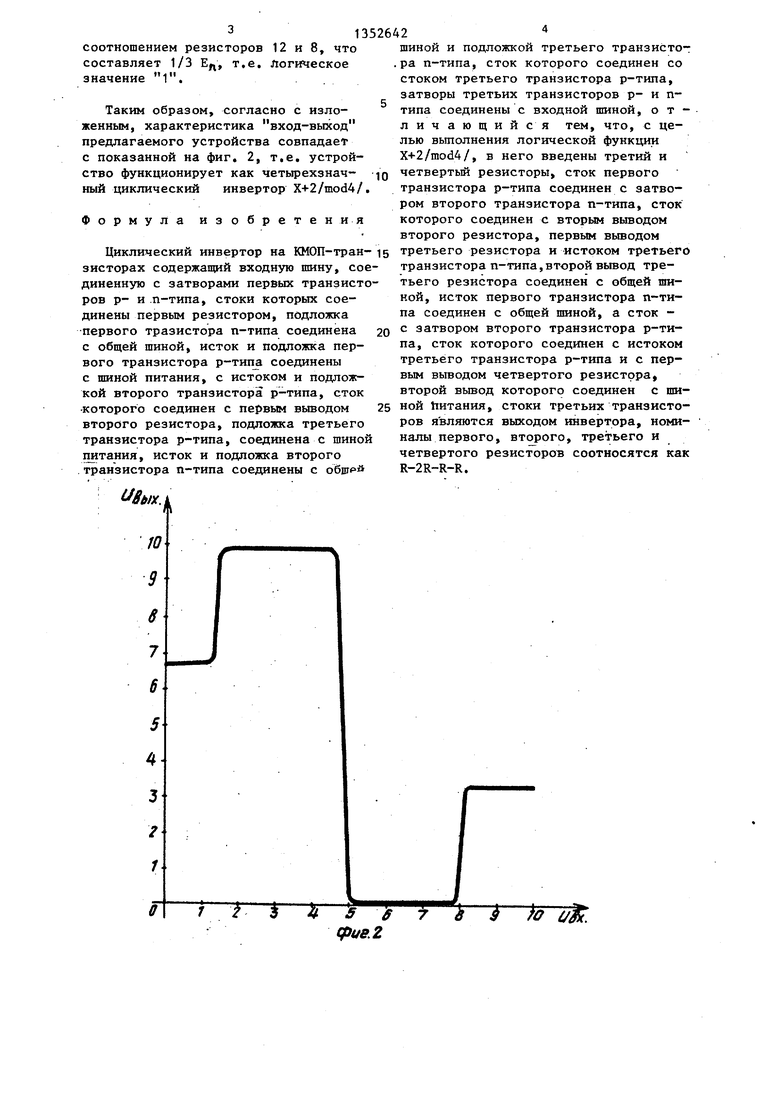

На фиг. 1 изображена схема электрическая принципиальная цилического инвертораi на фиг. 2 - характеристика вход-выход ; на фиг. 3 - эквивалентные схемы, поясняющие его рабо- ту.

Устройство соедржит входную шину 1, первый транзистор 2 р-типа, первый транзистор 3 п-типа, первый резистор 4, общую шину 5, шину питания 6, второй транзистор 7 р-типа, второй резистор 8, третий транзистор 9 р-тйпа, второй транзистор 10 п-типа, третий транзистор 11 п-типа, третий резистор 12, четвертый резистор 13, стоки третьих транзисторов 9 и 11 р- и п-типа являются выходами 14, номиналы резисторов 4, 8, 12 и 13 соотносятся как R-2R-R-R.

Циклический инвертор на КМОП-тран- зисторах работает следующим образом.

На вход 1 устройства поступают сигналы в виде напряжения постоянного тока в диапазоне от О В до напряжения источника питания Е, что в логическом плане соответствует алфавиту Е ,1,2,31. Предположим, что входной сигнал равен О, т.е. напряжение Ug на входе 1 находится в пределах

О и,, и„,р,

где - напряжение порог МОП-транзисторов.

В этом случае транзисторы 3 и 11 с каналами п-типа закрыты, поскольку напряжение на их затворах не превьш1а- ет и„р- , а транзисторы 2 и 9 с каналом р-типа открыты в силу того, что напряжение на их затворах по отношению к потенциалу их истоков меньше на величину, превьш1ающую , Так как транзистор 2 открыт, к затвору . транзистора 10 приложено напряжение, превышающее U , вследствие чего транзистор 10 oткpыt, обеспечивая при этом наличие нулевого потенциала на истоке транзистора 11 в точке соединения резисторов 12 и 8. Закрытое состояние транзистора 3 обеспечивает

пор

передачу через резистор 4 на затвор транзистора 7 напряжения/ которое по отношению к его истоку меньше и„ При этом, транзистор 7 закрыт.

Эквивалентная схема (фиг. За) иллюстрирует состояние транзисторов в рассматриваемой ситуации посредством ключей, обозначение которых аналогично принятому для обозначения транзисторов в схеме ус тройства (фиг. 1). В результате, согласно фиг. За, напряжение на выходе 14 устройства определяется Ер и соотношением резисторов 13 и 8, что составляет 2/3 Е, и соответствует логическому значению 2. Если входной сигнал равен 1, т.е. напряжение Uj на входе 1 нахо- дйтся в пределах U и, 1/ЗЕп + Uj,g , то транзисторы 2 и 9 по-прежнему открыты, так как напряжение на их затворах по отношению к потенциалу их истоков меньше на величину, превьш1ающую U .

Транзисторы 3, 10 и 11 также открыты, поскольку напряжение на их затворах превьппает . Так как транзистор 3 открыт, к затвору транзистора 7 приложено напряжение, кс5- торое по отношению к потенциалу его истока меньше на величину, превьшгаю- шую , вследствие чего транзистор 7 открыт . Открытое состояние транзистора 7 обеспечивает подачу на исток транзистора 9 напряжения источника питания. В рассматриваемой ситуации открытые транзисторы 9 и 11 образуют двоичный инвертор, выходной сигнал которого до Ug 6 1/2Е„ близок к Е, следовательно, на выходе 14 устройства сигнал с логическим значением 3 (фиг. Зб). Допустим, что входной сигнал равен 2, т.е. напряжение Ug на входе 1 находится в пределах . 1/3E +U op6Ue, ; 2/ЗЕ„ + Upop- этой ситуации, как и в предьщущей, все транзисторы 2, 3, 7, 10, 9 и 11 открыты (фиг, Зв). Однако, на выходе двоичного инвертора, образованного транзисторами 9 и 11, а значит и на выходе устройства, сигнал равен О (Ujj 1/2Е), Наконец, когда входной сигнал равен 3, т.е. напряжение и вл на входе 1 находится в пределах 2/ЗЕп + Unop - Ug ЕП то имеет место состояние транзисторов, показанное на эквивалентной схеме фиг. 3г. В этом случае напряжение на выходе 14 устройства определяется Е, и

соотношением резисторов 12 и 8, что составляет 1/3 Ед, т.е. Логическое значение 1.

Таким образом, согласно с изложенным, характеристика вход-выход предлагаемого устройства совпадает с показанной на фиг, 2, т.е. устройство функционирует как четьфехзнач- ный циклический инвертор X+2/mod4/.

Формула изобретения

Циклический инвертор на КМОП-тран зисторах содержащий входную шину, со динениз с затворами первых транзистров р- и .п-типа, стоки которых соединены первьм резистором, подложка первого тразистора п-типа соединена с общей шиной, исток и подложка первого транзистора р-тип соединены с шиной питания, с истоком и подложкой второго транзистора р-типа, сток -которого соединен с первым выводом второго резистора, подложка третьего транзистора р-типа, соединена с шино питания, исток и подложка второго транзистора п-типа соединены с обпгр

.

W

9

в

7 6

5

43

7

/

г i

k ff }f

cpue.Z

0

5 шиной и подложкой третьего транзисто- .ра п-типа, сток которого соединен со стоком третьего транзистора р-типа, затворы третьих транзисторов р- и п- типа соединены с входной шиной, отличающийся тем, что, с целью вьшолнения логической функции X-«-2/mod4/, в него введены третий и Q четвертьш резисторы, сток первого транзистора р-типа соединен с затвором второго транзистора п-типа, сток которого соединен с вторым выводом второго резистора, первым выводом третьего резистора и истоком третьего транзистора п-типа,второй вывод третьего резистора соединен с общей шиной, исток первого транзистора п-типа соединен с общей шиной, а сток - с затвором второго транзистора р-типа, сток которого соединен с истоком третьего транзистора р-типа и с первым выводом четвертого резистора второй вьшод которого соединен с ши- 5 ной йитания, стоки третьих транзисторов являются выходом инвертора, номиналы первого, второго, третьего и четвертого резисторов соотносятся как

. .S tV Сч

h /.

I

.-Ц

«va

12

4

M

4ata

| название | год | авторы | номер документа |

|---|---|---|---|

| Циклический инвертор @ ( @ ) на КМОП-транзисторах | 1985 |

|

SU1287280A1 |

| Многовходовый многозначный логический элемент максимум | 1983 |

|

SU1126172A1 |

| Многовходовый многозначный логический элемент минимум | 1983 |

|

SU1126171A1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

| Комбинационный сумматор | 1988 |

|

SU1674108A1 |

| Буферный усилитель на К-МОП транзисторах | 1984 |

|

SU1220118A1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| УСИЛИТЕЛЬ | 1994 |

|

RU2069448C1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| Контролируемый логический элемент | 1987 |

|

SU1429312A1 |

Изобретение относится к импульсной технике и может быть использовано в различных цифровых устройствах с четьфехзначным алфавитом. Цель изобретения - выполнение логической функции X+2/mod4/ - достигается за счет использования резистивной матрицы типа R-2R-R. Устройство содержит входную шину 1, первый транзистор 2 р-типа, первый транзистор 3 п-типа, резисторы 4, 8, 12 и 13, общую шину 5, шину 6 питания, второй транзистор 7 р-типа, второй транзистор 10 п-ти- , па, третий транзистор 9 р-типа, тре-:л тий транзистор 11 п-типа. Стоки транзисторов 9 и 11 являются выходом 14 циклического инвертора. Условия выбора номиналов резисторов приводятся в описании изобретения. Цри этом устройство функционирует как четырехзначный циклический инвертор Х+2/ /mod4/. 3 ил. с сл Ipufi

Составитель А.Кабанов Редактор Т.Парфенова Техред Л.Сердюкова Корректор В.Гирняк

Заказ 5576/56 Тираж 900 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий It3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-похшграфическое предприятие,, г, Ужгород, ул. Проектная, 4

| Патент США № 4107549, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Циклический инвертор @ ( @ ) на КМОП-транзисторах | 1985 |

|

SU1287280A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ,(54) ЦИКЛИЧЕСКИЙ ИНВЕРТОР НА КМОП- ТРАНЗИСТОРАХ | |||

Авторы

Даты

1987-11-15—Публикация

1985-01-04—Подача