112

Изобретение относится к импульсной технике и может быть использовано при построении узлов многозначной логики.

Целью изобретения является расши- рение функциональных возможностей путем увеличения значности сигналов до четырех.

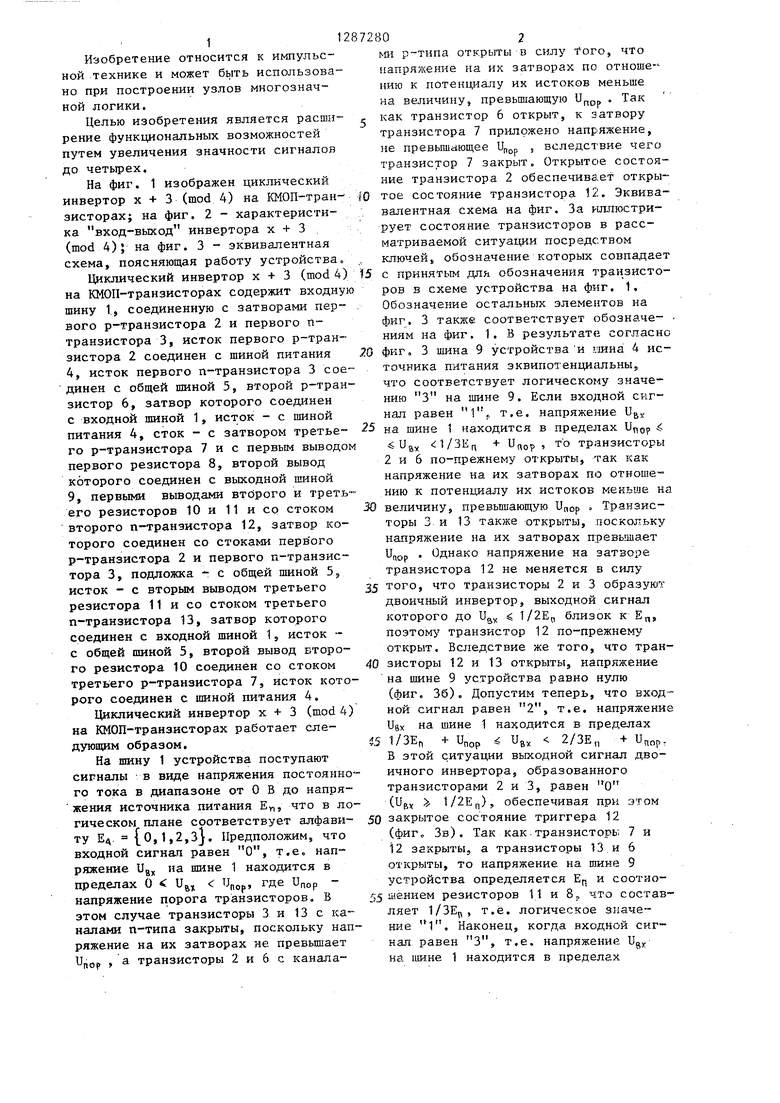

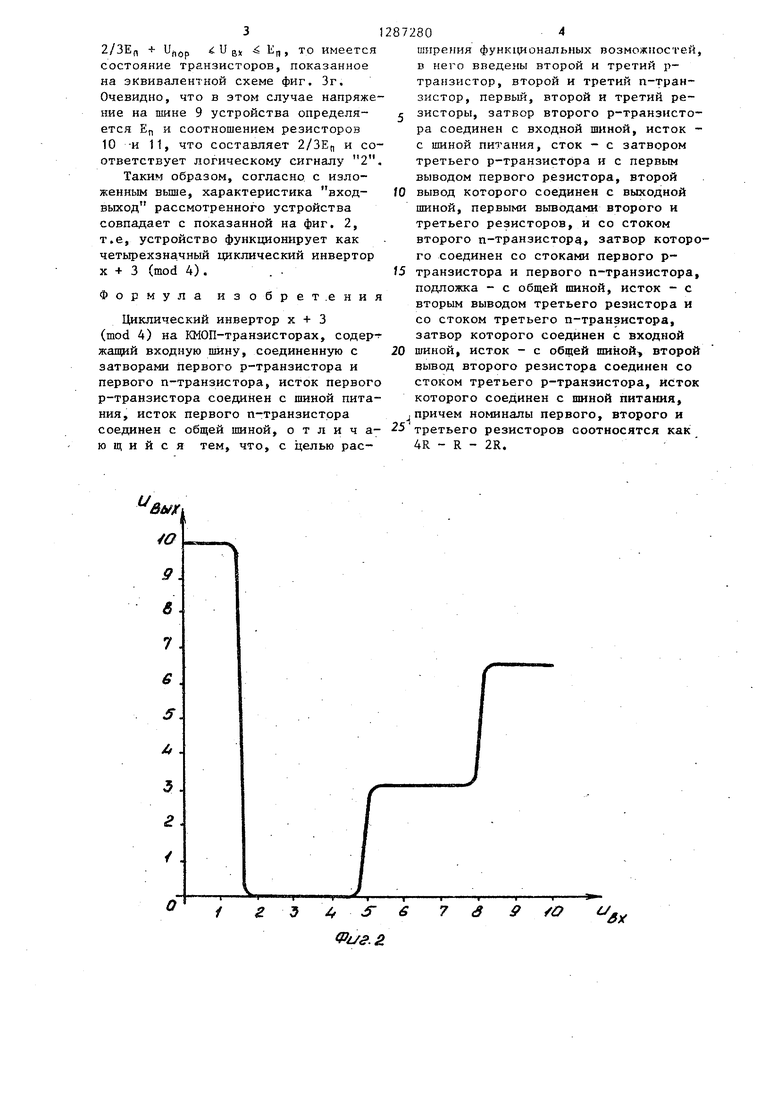

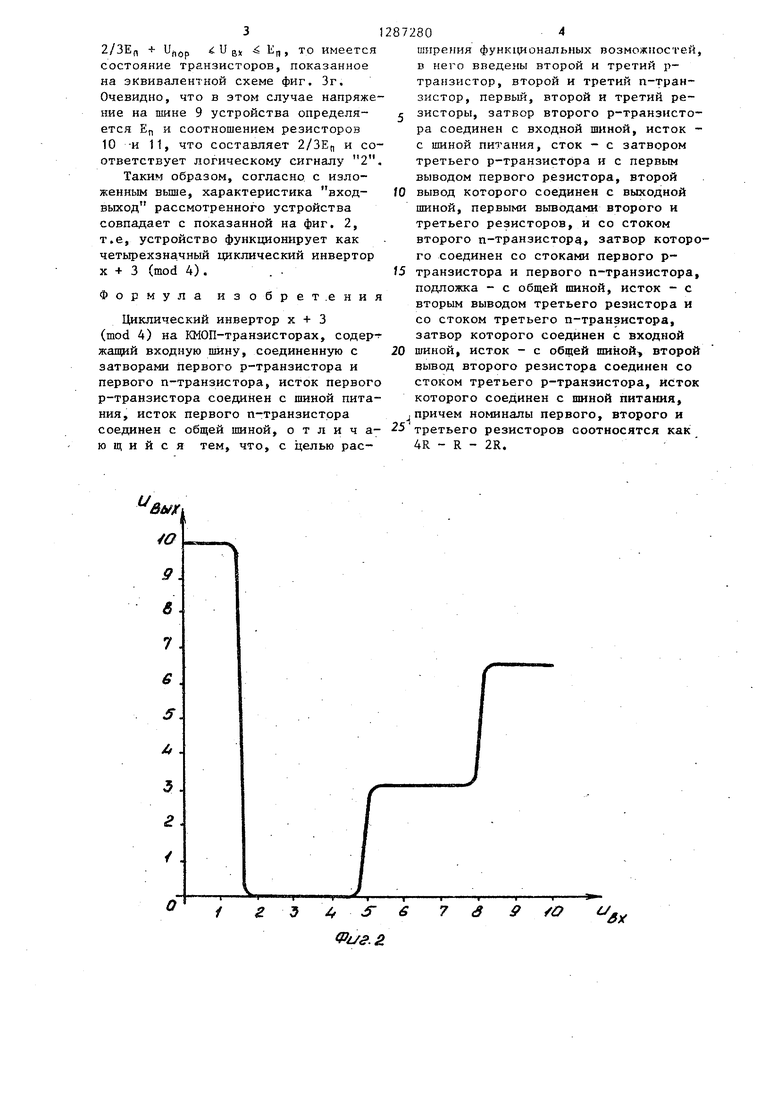

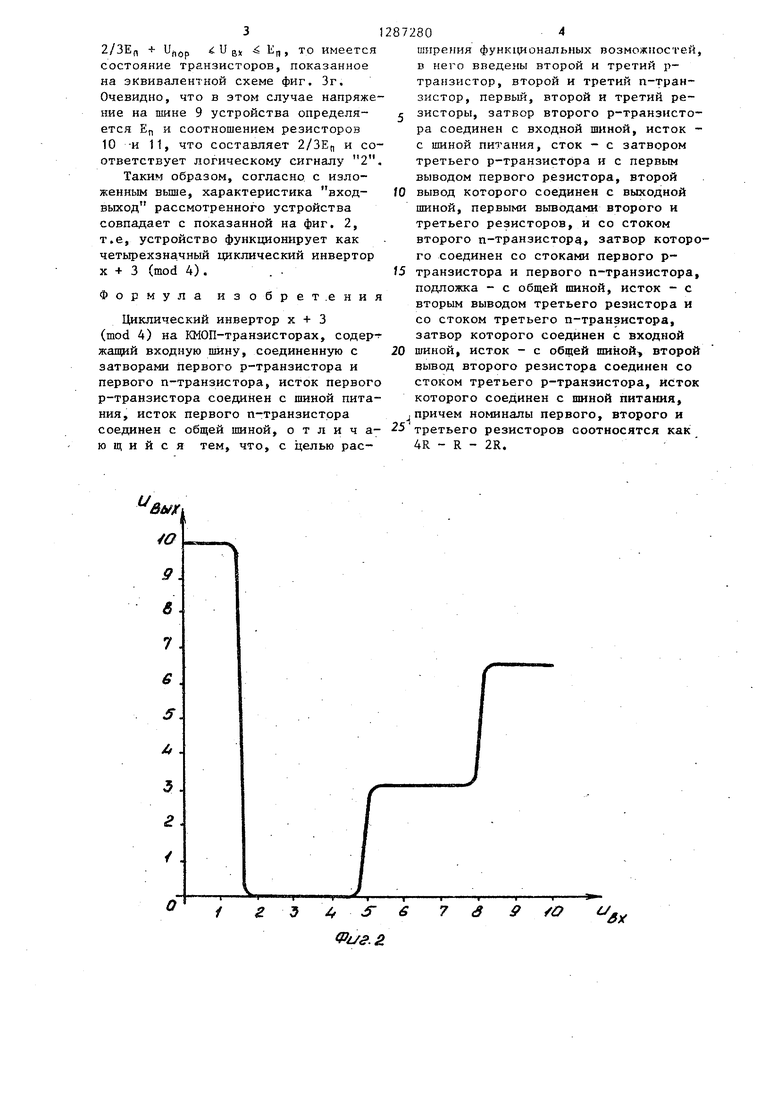

На фиг. 1 изображен циклический инвертор X 3 (mod 4) на КМОП-тран- зисторах; на фиг. 2 характеристика вход-выход инвертора х + 3 (mod 4); на фиг. 3 - эквивалентная схема, поясняющая работу устройства.

Циклический инвертор х + 3 (mod 4) на КМОП-транзисторах содержит входную шину 1, соединенную с затворами пер вого р-транзистора 2 и первого п- транзистора 3, исток первого р-тран- зистора 2 соединен с шиной питания 4, исток первого п-транзистора 3 соединен с общей шиной 5, второй р-тран- зистор 6, затвор которого соединен с входной шиной 1, исток - с шиной питания 4, сток - с затвором третье- го р-транзистора 7 и с первым выводом первого резистора 8, второй вывод которого соединен с выходной шиной 9, первыми выводами второго и третьего резисторов 10 и 11 и со стоком второго п транзистора 12, затвор которого соединен со стоками перв ого р-транзистора 2 и первого п-транзистора 3, подложка - с общей шиной 5, исток - с вторым выводом третьего резистора 11 и со стоком третьего п-транзистора 13, затвор которого соединен с входной шиной 1j исток - с общей шиной 5, второй вывод второго резистора 10 соединен со стоком третьего р-транзистора 7, исток которого соединен с шиной питания 4.

Циклический инвертор х + 3 (mod 4) на КМОП-транзисторах работает следующим образом.

На шину 1 устройства поступают сигналы в виде напряжения постоянного тока в диапазоне от О В до напря- жения источника питания Е„, что в логическом плане соответствует алфави ту Е {о,1,2,3}. Предположим, что входной сигнап равен О, т.е. напряжение Ug на шине 1 находится в пределах О U , где Unop - напряжение порога транзисторов, В этом случае транзисторы 3 и 13 с каналами п-типа закрыты, поскольку напряжение на их затворах не превьшает и„ор , а транзисторы 2 и 6 с канапа802

Mil открыты в силу foro, что напряжение на их затворах по отношв иию к потенциалу ик истоков меньше на величину, превышающую U . Так как транзистор 6 открыт, к затвору транзистора 7 приложено напр Яжение, не превышающее и„ , вследствие чего транзистор 7 закрыт. Открытое состояние транзистора 2 обеспечива.ет открытое состояние транзистора 12. Эквива валентная схема на фиг. За иллюстрирует состояние транзисторов в рассматриваемой ситуации посредством ключей, обозначение которых совпадае с принятым для обозначения транзисторов в схеме устройства на фиг. 1, Обозначение остальных элементов на фиг. 3 также соответствует обозначе- ниям на фиг, 1. В результате согласн фиг. 3 шина 9 устройства и j sina 4 источника питания зквипотенцигшьны, что соответствует логическому значению 3 на шине 9. Если входной сигнал равен I, т.е. напряжение U на шине 1 находится в пределах и, iUgy ;1/ЗЕц U(,Qp , то транзисторы 2 и 6 по-прежнему открыты, так как напряжение на их затворах по отношению к потенциалу их истоков меньше н величину, превьш1ающую Unop Транзисторы 3. и 13 также -открыты, поскольку напряжение на их затворах превышает и„ор . Однако напряжение на затворе транзистора 12 не меняется в силу того, что транзисторы 2 и 3 образуют двоичный инвертор, выходной сигнал которого до Ug 1/2Е„ близок к Е, поэтому транзистор 12 по-прежнему открыт. Вследствие же того, что транзисторы 12 и 13 открыты, напряжение на шине 9 устройства равно нулю (фиг. 36), Допустим теперь, что входной сигнал равен 2, т.е. напряжени Ugx на шине 1 находится в пределах 1/ЗЕп + Unop UBX 2/ЗЕ,1 Unopr В этой ситуации выходной сигнап двоичного инвертора, образованного транзисторами 2 и 3, равен О (Ug 1/2Ер)5 обеспечивая при этом закрытое состояние триггера 12 (фиг Зв). Так как.транзисторы 7 и 12 закрыты, а транзисторы 13 и 6 открыты, то напряжение на шине 9 устройства определяется Et- и соотношением резисторов 11 и 8р что составляет 1/ЗЕр, т.е. логическое значение М. Наконец, когда входной сигнал равен 3, т.е. напряжение Ug,, на шине 1 находится в пределах

и соlioll

2/ЗЕп + Unop и Bj ЕП, то имеется состояние транзисторов, показанное на эквивалентной схеме фиг, Зг, Очевидно, что в этом случае напряжение на шине 9 устройства определяется ЕП и соотношением резисторов 10 -и 11, что составляет 2/ЗЕп ответствует логическому сигналу

Таким образом, согласно с изложенным выше, характеристика вход- выход рассмотренного устройства совпадает с показанной на фиг. 2, т.е, устройство функционирует как четырехзначный циклический инвертор X + 3 (mod 4) . . .

Формула изобрет.ения

Циклический инвертор х + 3 (mod 4) на КМОП-транзисторах, содержащий входную шину, соединенную с затворами первого р-транзистора и первого п-транзистора, исток первого р-транзистора соединен с шиной питания, исток первого п-транзистрра соединен с общей шиной, отличающийся тем, что, с целью расW

872804

ширения функциональных возможностей, в него введены второй и третий р- транзистор, второй и третий п-тран- зистор, первьш, второй и третий резисторы, затвор второго р-транзистора соединен с входной шиной, исток - с шиной питания, сток - с затвором третьего р-транзистьра и с первым выводом первого резистора, второй вывод которого соединен с выходной шиной, первыми выводами второго и третьего резисторов, и со стоком второго п-транзистора, затвор которого соединен со стоками первого р- транзистора и первого п-транзистора, подложка - с общей шиной, исток - с вторым выводом третьего резистора и со стоком третьего п-транзистора, затвор которого соединен с входной шиной, исток - с общей шиной второй вывод второго резистора соединен со стоком третьего р-транзистора, исток которого соединен с шиной питания, .причем номиналы первого, второго и третьего резисторов соотносятся как 4R - R - 2R.

f5

20

25

4s

ff)

«cT

| название | год | авторы | номер документа |

|---|---|---|---|

| Циклический инвертор на КМОП-транзисторах | 1985 |

|

SU1352642A1 |

| Многовходовый многозначный логический элемент максимум | 1983 |

|

SU1126172A1 |

| Многовходовый многозначный логический элемент минимум | 1983 |

|

SU1126171A1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

| Контролируемый логический элемент | 1987 |

|

SU1429312A1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| Формирователь сигнала начальной установки делителя частоты кварцевых наручных часов | 1986 |

|

SU1365041A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| Селектор импульсов по длительности | 1977 |

|

SU951686A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

Изобретение относится к области импульсной техники. Может быть использовано при построении узлов многозначной логики. Целью изобретения является расширение функциональных - возможностей путем увеличения знач- ности сигналов до четырех. Для достижения поставленной цели в устройство введены р-транзисторы 6, 7, п-транзисторы 12, 13, резисторы 8, 10, 11, образованы новые функциональные связи. 3 шт. (Л и 00 4j to 00

Редактор М.Циткина

Составитель А.Кабанов

Техред И.Попович Корректор М.Демчик

Заказ 7728/58Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1130- 5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, уп. Проектная, А

| Пономарев М.Ф | |||

| и др | |||

| Многоуровневые логические элементы и устройства БИС, - Обзоры по электронной технике | |||

| Сер | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микроэлектроника | |||

| Вьш, 2 (879), 1982 | |||

| Патент США № 4107549, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-30—Публикация

1985-01-03—Подача