4

00

о со

00

со

Изобретение относится к аналоговой вычислительной технике, к устройствам обработки выходного сигнала микросхем с зарядовой связью (МСЗС).

Цель изобретения - повышение точности и быстродействия устройства.

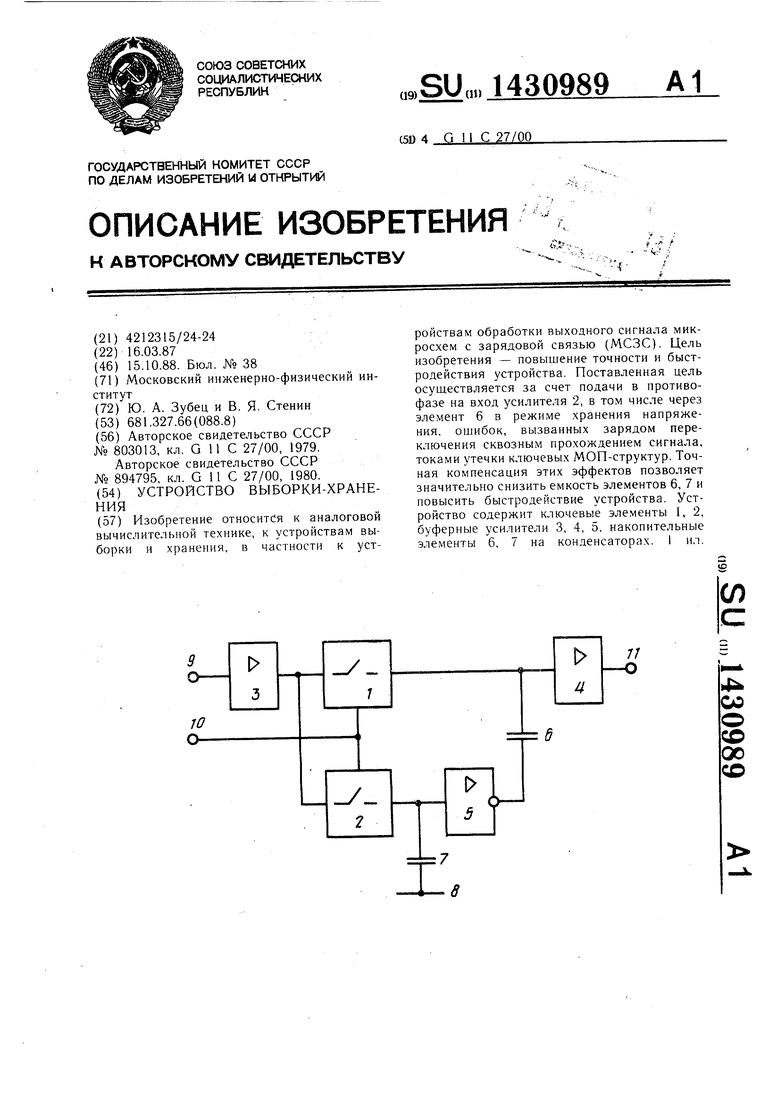

На чертеже представлена функциональная схема устройства.

Устройство содержит первый, второй аналоговые ключейые эл е1чёнты 1, 2, Л ервыи , второй буферные усилители 3, 4, третий ин- вертирующий буферный усилитель 5, первый, второй накопительные элементы 6, 7, на конденсаторах, шину 8 нулевого потенциала устройства, входы 9, 10 информационный и управляющий, информационный выход 1.

Устройство работает следующим образом.

В режиме выборки при высоком значении логического сигнала на входе 10 устройства элементы 1, 2 открыты, потен- циа.чы на первом и втором выводах элементов 6, 7 уравниваются с потенциалом на выходе усилителя 3. На выходе усили- I CJiH 4. выходе 1 1 устройства ф()|)мирует- ся напряжение, соответствующее выходному напряжению усилителя 1 и напряжению на входе 9 х стройства. На выходе усилителя 5 II втором выводе элемента 6 формируется напряжение, величина которого определяется коэффициентом передачи и напряжением сдвига инвертирующего усилителя 5. напряжением, на втором выводе элемента 7.

В )ежиме хранения при низком значении лошческогс) сигнала на входе И) устройства э.юмснгы I. 2 закрьггы. элементы (). 7 сохраняют запасенный на интер- ва.че в|)емени выборки заряд, поэтому иотен- циа.И) В1 1ходов элементов 1, 2 остаются рав- Н1)1ми потенциалу на ннтерва.че времени выборки. В режиме хранения напряжение па выходе 11 устройства также соответствует потеициалу на первом выводе элемента 6 и. с.ледовательно. напряжению на 11нтерва,1е времени выборки.

В режиме выборки напряжение сдвига CTpoiicToa онреде.чяется только суммой напряжений сдвщ-а усилителей 3, 4, при использовании в качестве элементов , 2 нолупроводниковых структур с ио.чевым эф- (licKTOM, например ИС быстродействующих МОП-ключей (например, 590КН8). При переходе из режимов выборки в режим хранения э.чеменгы 1, 2 закрьизаются и из их цепей управления на иервый вывод элемента 6 и первый вывод э.чемента 7 поступает заряд через паразитные емкости, величины которых близки для ключей 1, 2, так как потенциалы на выводах эле.мен- тов 1, 2 сохраняются практически равными в обоих режимах работы устройства. При выборе коэффициента усилителя 5 рави1 1м отнонк нню ве.чичин емкостей элемен- тов 6, 7 нриран1ение напряжения на об- к. шдках конденсатора 6 от заряда переклю

15

20

Ю

5

40 55 30

35

45

50

2

чения элемента 1 будет равно и противоположно по знаку приращению напряжения на выходе усилителя 5, которое вызывается соответствующим изменением напряжения на элементе 7 от заряда переключения элемента 2. Таким образом, на входе и выходе усилителя 4 при переходе в режим хранения напряжение не изменится. Аналогично будут взаимокомпенсироваться помехи и невыбираемые сигналы, проходящие через за- крыть е элементы 1, 2 в режи.ме хранения устройства.

При выборе уси;1ителей 4, 5 в качестве входных приборов с полевым эффектом точ- ноеть устройства в режиме хранения будет фактически опреде.чяться разностью токов утечки элементов 1, 2 благодаря действию компенсирующ,ей цепочки: элемент 7, уеили- тель 5, элемент 6. Для полной компенсации при заданной температуре источников погрешности емкость эле.мента 7 или коэффициент передачи усилителя 5 могут быть подрегулированы без ущерба для работы устройства.

Использование в качестве элементов 1, 2 ИС с согласованными МОП-к.тючами позво- ,-1яет наиболее полно реализовать достоинства устройства, например значительно одновременно с новьннение.м точности увеличить быстродействие за счет снижения емкостей э.чементов 6, 7 при заданной norpeiuHOc- ти обработки сигнала.

Формула и:юп1 е 1ени /

Устройство выборки-хранен 11 я. щее первый, второй и третий буферные усилители, первый и BTOpoii накопите.чьные элементы на конденсаторах, иервый и второй ключевые элементы, управляющие входы которых являются управляющим входом устройства, вход первого буферного усилителя является информационны.м входом устройства, а выход подключен к входу первого ключевого элемента, первые обкладки конденсаторов первого и второго наконите.пь- ных элементов подключены соответственно к входам второго и третьего буферных усилителей, вторая обкладка конденсатора второго накопительного элемента подключена к щине нулевого потенциала устройства. отличающееся те.м, что, с целью повышения точности и упрощения устройства, вход второго ключево1-о э.чемента подключен к входу первого ключевого элемента, выходы первого и второго ключевых элементов подключены соответственно к входам второго и третьего буферных усилителей, вторая об- к.чадка конденсатора нервого накопительного элемента подключена к выходу третьего буферного усилителя, выход второго буферного усилителя является инфор.мационным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

| Устройство считывания | 1986 |

|

SU1348911A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Устройство выборки-хранения | 1987 |

|

SU1425786A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU894795A1 |

| Устройство выборки-хранения | 1987 |

|

SU1474745A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1001179A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

Изобретение относится к аналоговой вычислительной технике, к устройствам выборки и хранения, в частности к устройствам обработки выходного сигнала микросхем с зарядовой связью (МСЗС). Цель изобретения - повышение точности и быстродействия устройства. Поставленная цель осуществляется за счет подачи в противо- фазе на вход усилителя 2, в том числе через элемент 6 в режиме хранения напряжения, ошибок, вызванных зарядом переключения сквозным прохождением сигнала, токами утечки ключевых МОП-структур. Точная компенсация этих эффектов позволяет значительно снизить емкость элементов 6, 7 и повысить быстродействие устройства. Устройство содержит ключевые элементы 1, 2, буферные усилители 3, 4, 5, накопительные элементы 6, 7 на конденсаторах. I ил.

| Аналоговое запоминающее устрой-CTBO | 1979 |

|

SU803013A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU894795A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-15—Публикация

1987-03-16—Подача