11

Изобретение относится к аналоговой вычислительной технике и может быть иснользовано в измерительной аппаратуре на основе интегральных схем с зарядовой связью (ИСЗС).

Цель изобретения - повьш1ение точности и быстродействия считывания путем снижения требований к соотношению емкости второго накопительного конденсатора хранения и проходной емкости закрытого ключевого элемента за счет дополнительного ослабления входных сигналов в интервалах времени между выборками потенциала инфор- мационного уровня.

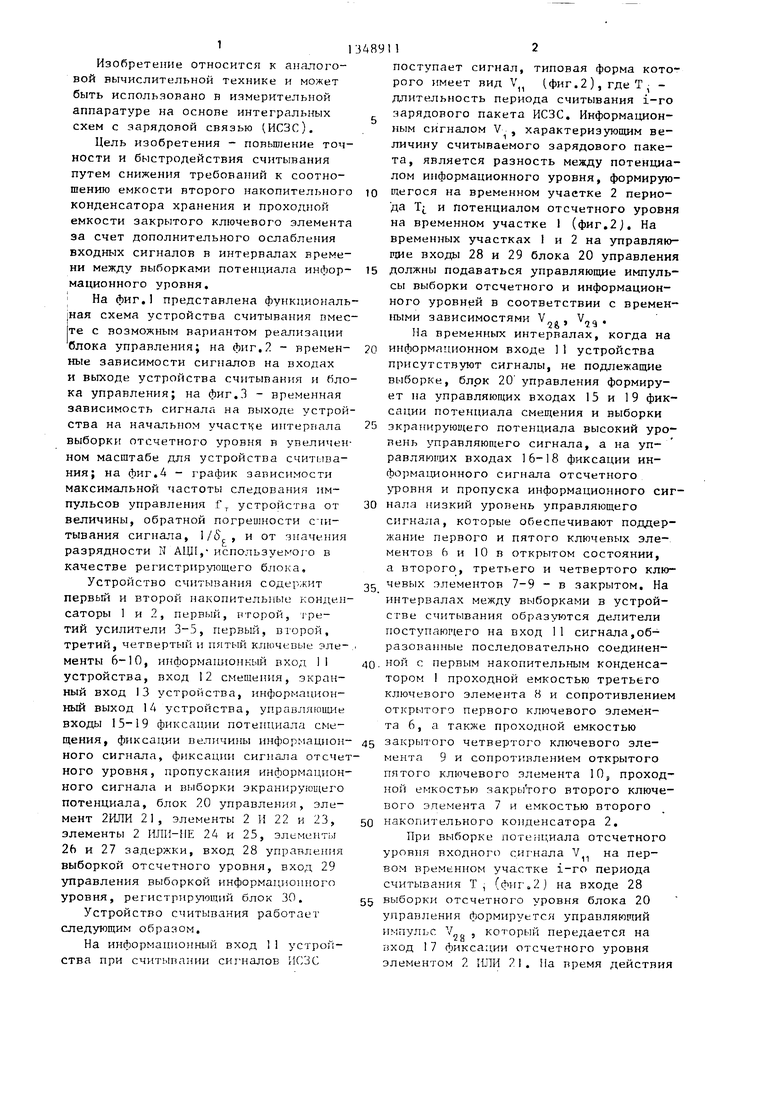

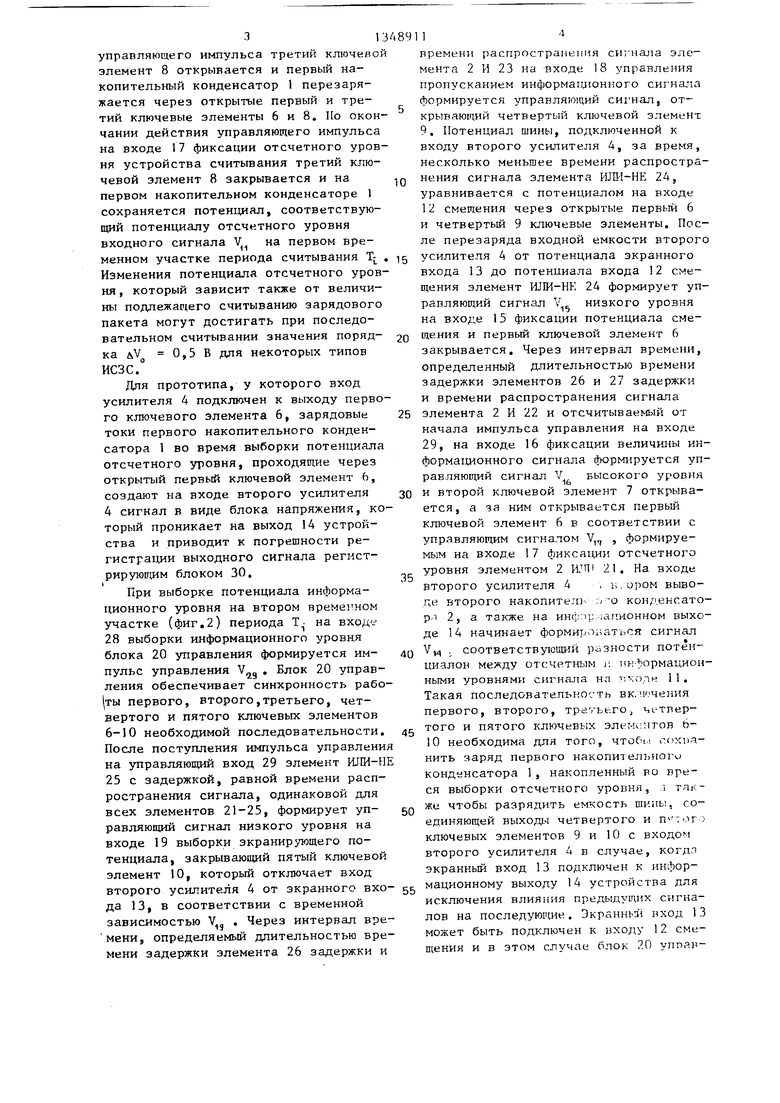

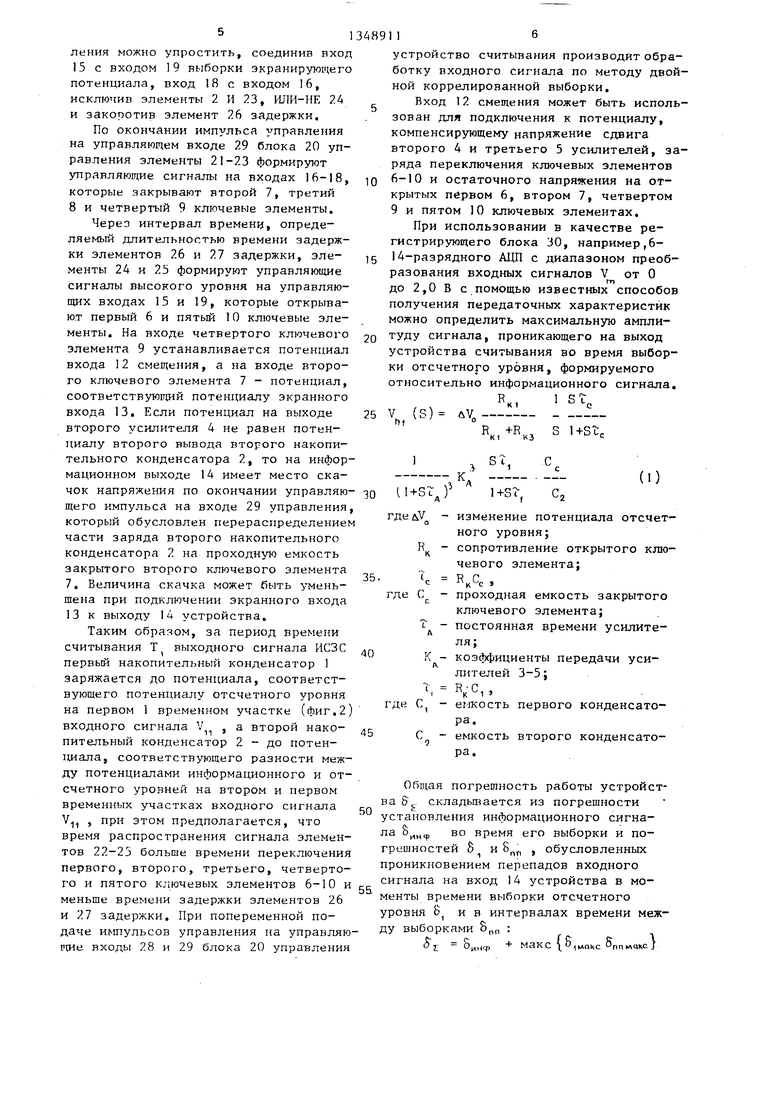

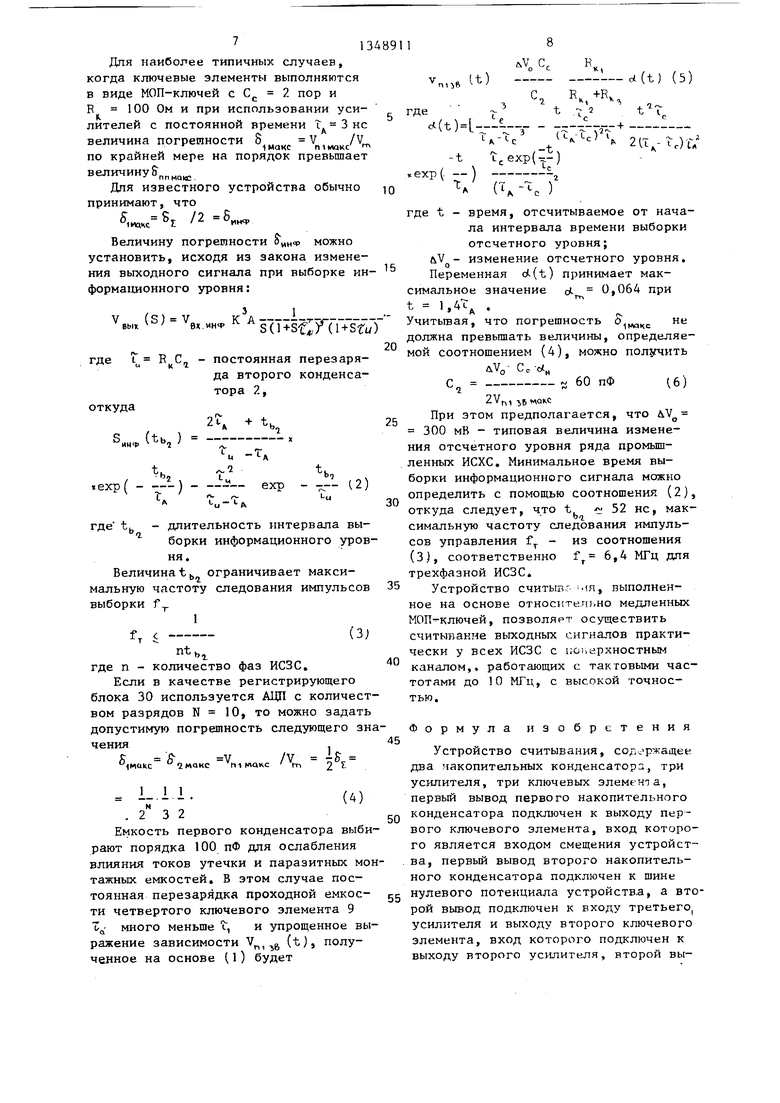

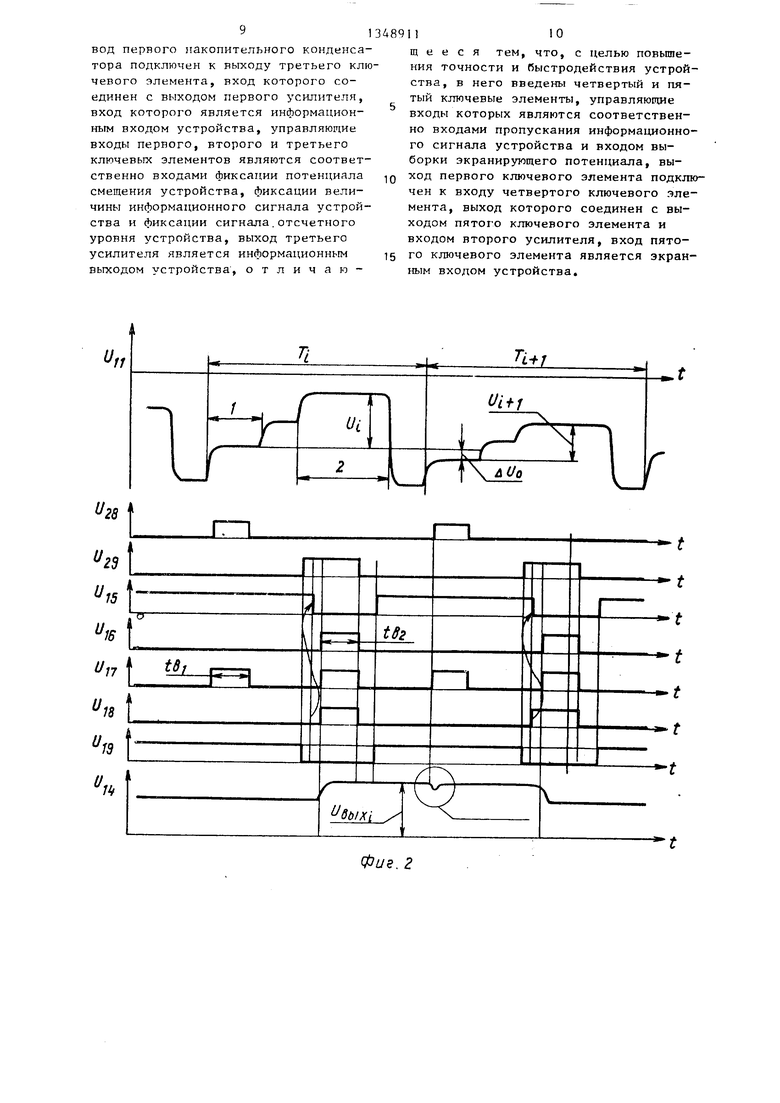

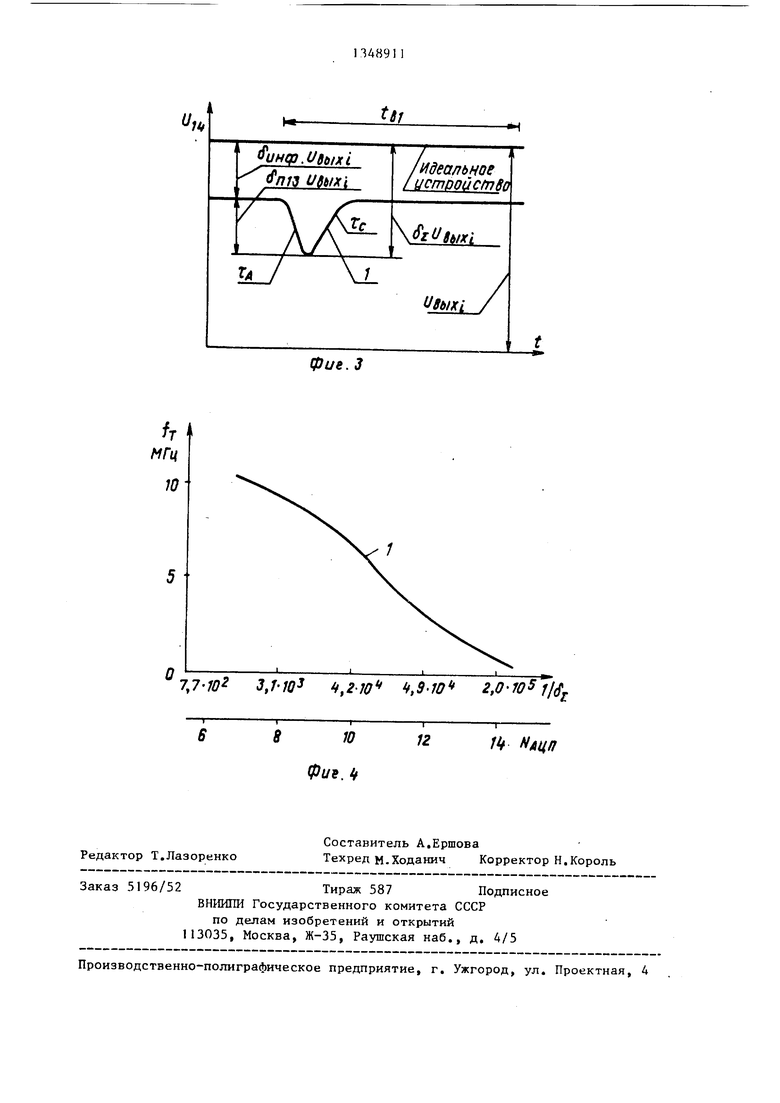

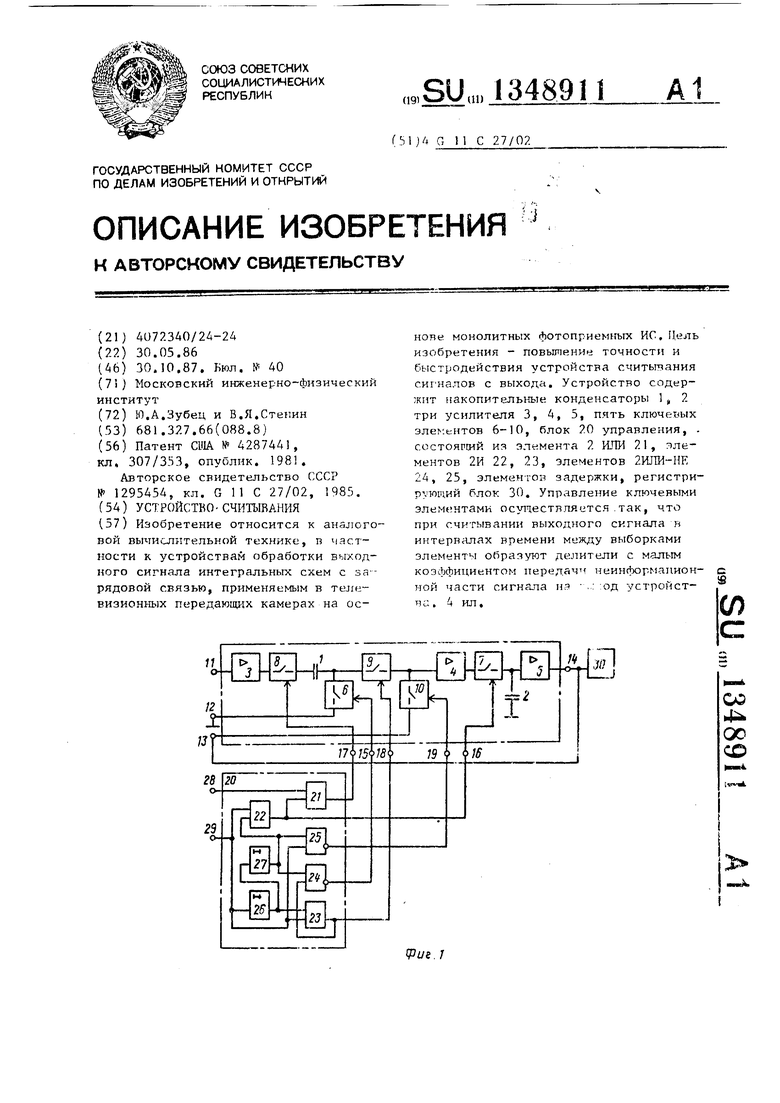

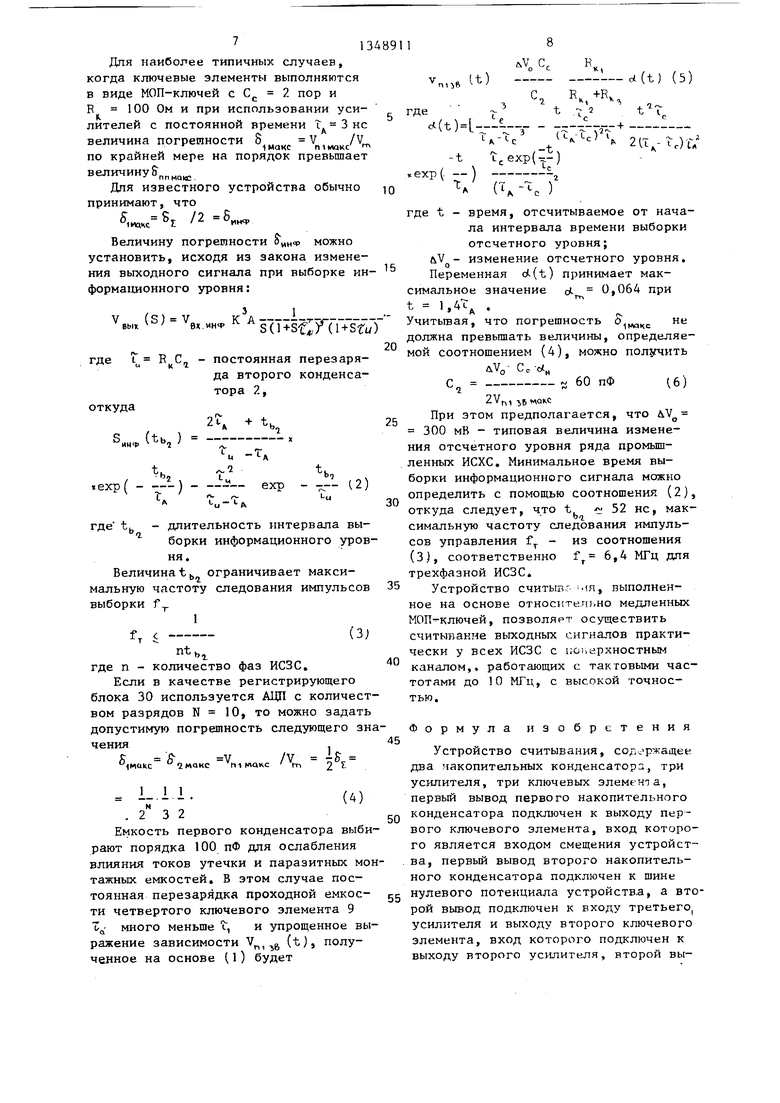

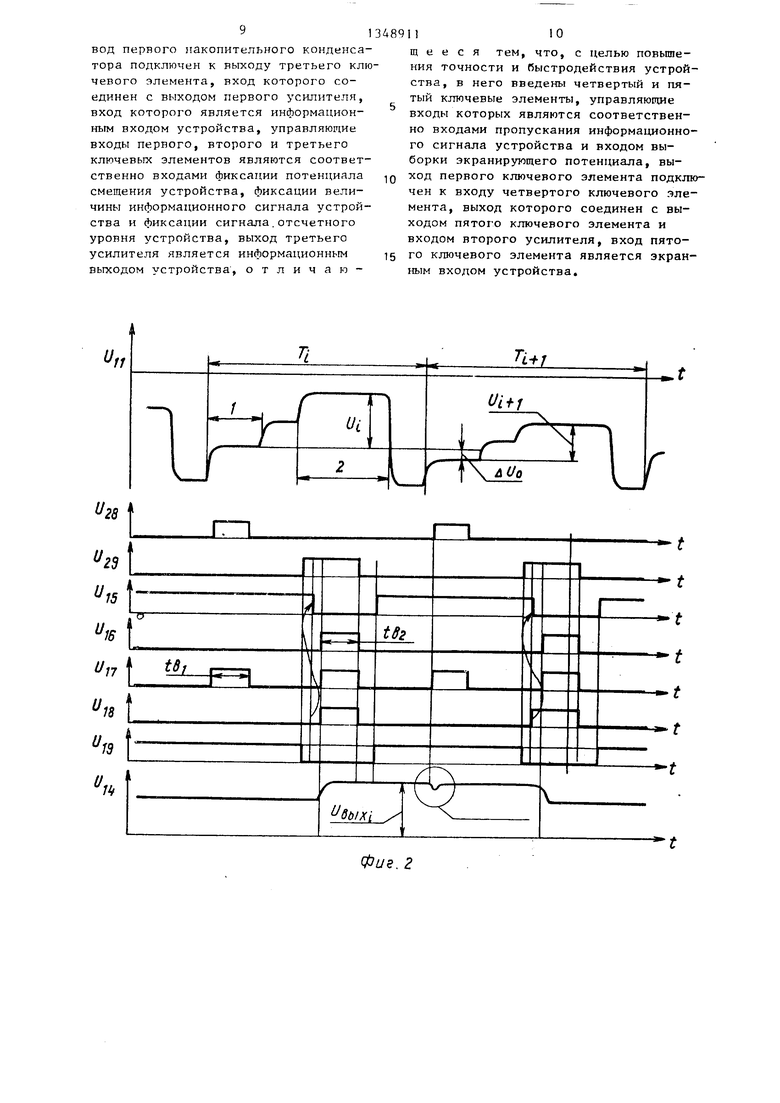

На Аиг.1 представлена функциональная схема устройства считывания пмес те с возможным вариантом реализации блока управления; на фиг.2 - времен- ные зависимости сигналов на входах и выходе устройства считывания и блока управления; на фиг.З - временная зависимость сигнала на выходе устройства на начальном участие интерпала выборки отсчетного уровня в увеличенном масштабе для устройства считывания; на фиг.А - график зависимости максимальной частоты следования импульсов управления f устройства от величины, обратной погрешности считывания сигнала, 1/6 , и от значения разрядности N А1Ц1,- используем01-о в качестве регистрирующего .

Устройство считывания содержит первый и второй накопительные конденсаторы

и л, первый, иторой, гретий усилители 3-5, первый, второй, третий, четвертый и пятый ключевые элементы 6-10, информаиио}1кый вход 11 устройства, вход 12 смешения, экранный вход 13 устройства, информацион- ньй выход 14 устройства, управляющие входы 15-19 фиксации потенциала смещения, фиксации величи}1ы информацион ного сигнала, фиксации сигнала отсченого уровня, пропускания информационного сигнала и выборки экраниругощего потенциала, блок 20 управления, элемент 2ИЛИ 21, элементы 2 И 22 и 23, элементы 2 24 и 25, элементы 2f) и 27 задержки, вход 28 управления выборкой отсчетного уровня, вход 29 управления выборкой информационного уровня, регистрирующий блок 30.

Устройство считывания работает следующим образом.

На информационный вход 11 устройства при считывании сиг-налов ИСЗС

112

поступает сигнал, типовая форма которого имеет вид V, (фиг. 2 ), где Т , - длительность периода считывания i-ro зарядового пакета ИСЗС. Информационным сигналом V , характеризующим величину считываемого зарядового пакета, является разность между потенциалом информационного уровня, формирующегося на временном участке 2 периода Т и потенциалом отсчетного уровня на временном участке 1 (фиг.2. На временных участках 1 и 2 на управляющие входы 28 и 29 блока 20 управления должны подаваться управляющие импульсы выборки отсчетного и информационного уровней в соответствии с временными зависимостями V ., V.

На временных интервалах, когда на информационном входе 1 устройства присутствуют сигналы, не подлежащ 1е выборке, блок 20 управления формирует на управляющих входах 15 и 19 фиксации потенциала смещения и выборки экранирующего потенциала высокий уровень управляющего сигнала, а на уп- равляю гд1х входах 16-18 фиксации информационного сигнала отсчетного фовня и пропуска информационного сигнала низкий уровень управляющего сигнала, которые обеспечивают поддержание первого и пятого ключевых эле-, ментов 6 и 10 в открытом состоянии, а второго, третьего и четвертого ключевых элементов 7-9 - в закрытом. На интервалах между выборками в устройстве считывания образуются делители поступающего на вход 11 сигнала,образованные последовательно соединенной с первым накопительным конденсатором 1 проходной емкостью третьего ключевого элемента 8 и сопротивлением открытого первого ключевого элемента 6, а также проходной емкостью закрытого четвертого ключевого элемента 9 и сопрот1 влением открытого пятого ключевого элемента 10, проходной емкостью закры того второго ключевого элемента 7 и емкостью второго накопительного конденсатора 2.

При выборке потенциала отсчетного уровня входного сигнала V на первом временном участке i-ro периода считывания Т, (фиг.2) на входе 28 выборки отсчетного уровня блока 20 управления формируется управляющий импульс Y, , который передается на вход 17 фиксации отсчетного уровня элементом 2 ИЛИ 21. На время действия

31

управляющего импульса третий ключевой элемент 8 открывается и первый накопительный конденсатор 1 перезаряжается через открытые первый и третий ключевые элементы 6 и 8, По окончании действия управляющего импульса на входе 17 фиксации отсчетного уровня устройства считывания третий ключевой элемент 8 закрывается и на первом накопительном конденсаторе 1 сохраняется потенциал, соответствующий потенциалу отсче.тного уровня входного сигнала V на первом временном участке периода считывания Tj Изменения потенциала отсчетного уровня , который зависит также от величины подлежар1его считыванию зарядового пакета могут достигать при последовательном считывании значения поряд- ка &V 0,5 В для некоторых типов ИСЗС.°

Для прототипа, у которого вход усилителя А подключен к выходу первого ключевого элемента 6, зарядовые токи первого накопительного конденсатора 1 во время выборки потенциала отсчетного уровня, проходящие через открытый первый ключевой элемент 6, создают на входе второго усилителя А сигнал в виде блока напряжения, который проникает на выход 1А устройства и приводит к погрешности регистрации выходного сигнала регистрирующим блоком 30. I

При выборке потенциала информационного уровня на втором временном участке (фиг,2) периода Т на входе 28 выборки информационного уровня блока 20 управления формируется им- пульс управления V , Блок 20 управления обеспечивает синхронность рабо- ты первого, второго,третьего, четвертого и пятого ключевых элементов 6-10 необходимой последовательности. После поступления импульса управления на зшравляющий вход 29 элемент ИЛИ-НЕ 25 с задержкой, равной времени распространения сигнала, одинаковой для всех элементов 21-25, формирует уп- равляющий сигнал низкого уровня на входе 19 выборки экранирующего потенциала, закрывающий пятый ключевой элемент 10, который отключает вход второго усилителя А от экранного вхо- да 13, в соответствии с временной зависимостью V . Через интервал вре- мени, определяемый длительностью времени задержки элемента 26 задержки и

1 1 1

времени pacnpocrpaiiein-iH сит нала элемента 2 И 23 на входе 18 управления пропусканием информащюнного сигнала формируется управляющий сигнал, открывающий четвертый ключевой элемент 9. Потенциал шины, подключенной к входу второго усилителя 4, за время, несколько меньшее времени распространения сигнала элемента ИЛИ-НЕ 2А, уравнивается с потенциалом на входе 12 смещения через открытые первый 6 и четвертый 9 ключевые элементы. После перезаряда входной емкости второг усилителя А от потенциала экранного входа 13 до потенциала входа 12 смещения элемент ИЛИ-НЕ 2А формирует управляющий сигнал V низкого уровня на входе I5 фиксации потенциала смещения и первый ключевой элемент 6 закрывается. Через интервал времени, определенный длительностью времени задержки элементов 26 и 27 задержки и времени распространения сигнала элемента 2 И 22 и отсчитываемый от начала импульса управления на входе 29, на входе 16 фиксации величины ин формагщонного сигнала формируется управляющий сигнал V, высокого угювня 16

и второй ключевой элемент 7 открывается, а за ним открывается первый ключевой элемент 6 в соответствии с управляющим сигналом V,, , формируемым на входе 17 фиксации отсчетного уровня элементом 2 ШП 21. На входе второго усилителя А i i;. ором выводе второго накопител) конденсато Р Ч 2, а также на инфпи-laiiHOHHOM выходе 1А начинает формироваться сигнал V соответствующий разности потенциалов между отсчетным i; информационными уровнями сигнала на лхпдн 11. Такая последовательность вк.мочения первого, второго, третьегоj четвертого и пятого ключевых эле:-к;нтов 6- 10 необходима для того, . г.охря- нить заряд первого накопительного конденсатора 1, накопленный во пре- ся выборки отсчетного уровня, л также чтобы разрядить емкость щины, соединяющей выходы четвертого и п Т Лго ключевых элементов 9 и 10 с входом второго усилителя А в случае, когдл экранный вход 13 подключен к информационному выходу 1А устройства для исключения влияния предыдущих сигналов на последую1дие. Экранньз вход 13 может быть подключен к входу 12 смещения и в этом случае блок 20 уппавления можно упростить, соединив вход 15 с входом 19 яыборки экранирующего потенциала, вход 18 с входом 16,

исключив элементы 2 И 23, ИЛИ-НЕ 24

„,

и закоротив элемент /о задержки.

По окончании импульса управления на управляющем входе 29 блока 20 управления элементы 21-23 формируют управляющие сигналы на входах 16-18, которые закрывают второй 7, третий 8 и четвертый 9 ключевые элементы.

Через интервал времени, определяемый длительностью времени задержки элементов 26 и 27 задержки, эле- менты 24 и 25 формируют управляющие сигналы высокого уровня на управляющих входах 15 и 19, которые открывают первый 6 и пятый 10 ключевые элементы. На входе четвертого ключевого элемента 9 устанавливается потенциал входа 12 смещения, а на входе второго ключевого элемента 7 - потенциал, соответствующий потенциалу экранного входа 13, Если потенциал на выходе второго усилителя 4 не равен потенциалу второго вывода второго накопительного конденсатора 2, то на информационном выходе 14 имеет место скачок напряжения по окончании управляю- щего импульса на входе 29 управления который обусловлен перераспределением части заряда второго накопительного конденсатора 2 на проходную емкость закрытого второго ключевого элемента 7, Величина скачка может быть уменьшена при подключении экранного входа 13 к выходу 1Д устройства.

Таким образом, за период времени считывания Т выходного сигнала ИСЗС первый накопительныр конденсатор 1 заряжается до потенциала, соответствующего потенциалу отсчетного уровня на первом 1 временном участке (фиг,2 входного сигнала V , а второй нако- пительный конденсатор 2 - до потен- 1Ц1ала, соответствующего разности между потенциалами информационного и отсчетного уровней на втором и первом временных участках входного сигнала V, , при этом предполагается, что время распространения сигнала элементов 22-25 больше времени переключения первого, второго, третьего, четверто

го и пятого ключевых элементов 6-10 и меньше времени задержки элементов 26 И 27 задержки. При попеременной подаче импульсов управления на управляю- npie входы 28 и 29 блока 20 управлении

устройство считывания производит обработку входного сигнала по методу двойной коррелированной выборки.

Вход 12 смещения может быть использован для подключения к потенциалу, компенсирующему напряжение сдвига второго 4 и третьего 5 усилителей, заряда переключения ключевых элементов 6-10 и остаточного напряжения на открытых первом 6, втором 7, четвертом 9 и пятом 10 ключевых элементах.

При использовании в качестве регистрирующего блока 30, например,6- 14-разрядного АЦП с диапазоном преобразования входных сигналов V от О

гл

до 2,0 В с помощью известных способов получения передаточных характеристик можно определить максимальную амплитуду сигнала, проникающего на выход устройства считывания во время выборки отсчетного уровня, формируемого относительно информационного сигнала.

R.

1 S

(1)

U+sr) l+sr Сг где&V - изменение потенциала отсчето

ного уровня; Е - сопротивление открытого клю-

К

чевого элемента; с R,C, , где С - проходная емкость закрытого

ключевого элемента; L - постоянная времени усилителя;

К - коэффициенты передачи усилителей 3-5;

,

где С - емкость первого конденсатора,

С - емкость второго конденсатора.

Q g CQ

55

Общая погрешность работы устройства & складьшается из погрешности установления информационного сигнала Sp,mp во время его выборки и погрешностей S и S , обусловленных проникновением перепадов входного сигнала на вход 14 устройства в моменты времени выборки отсчетного уровня Б и в интервалах времени между выборками :

Г - 0„нф макс 0, nnMQKcJ

13А89

Для наиболее типичных случаев, когда ключевые элементы выполняются в виде МОП-ключей с С. 2 пор и R 100 Ом и при использовании усилителей с постоянной времени t 3 не

величина погрешности 8 V /У„

1маке niMQKc

по крайней мере на порядок превьппает величину

Для известного устройства обычно д принимают, что

,«, /2 В

Величину погрешности , можно установить, исходя из закона изменения выходного сигнала при выборке ин- формационного уровня:

вых (S вх.инФ к А ---- - -где Т - постоянная перезаряда второго конденсатора 2,

(tb, )

24 + tb

b

u -t

h, ,

,exp( - ---) exp - -- (2)

-u-

где tjj - длительность интервала выборки информационного уровня.

Величина t ограничивает максимальную частоту следования импульсов выборки f

1

fr

nt I

где n - количество фаз ИСЗС,

Если в качестве регистрирующего блока 30 используется АЦП с количеством разрядов N 10, то можно задать допустимую погрешность следующего значения 5г- (V ,т /V - «-Я

(МОКс OMQKC niMQKC m 9 Я

1MUKC7MQKCniMQKC m2

1 1 1

(4)

.232

Емкость первого конденсатора выбирают порядка 100 пФ для ослабления влияния токов утечки и паразитных монтажных емкостей, В этом случае постоянная перезарядка проходной емкое- ти четвертого ключевого элемента 9 Тц- много меньше ц и упрощенное выражение зависимости V,g (t), полученное на основе (1) будет

д

-20

25

30

35

50

gгде

П. )

V С, R

ппб

d(t) (5)

cA(t) -

С. RK,+

С. t -„ ; f I,

3 . : ..-t t,exp() ,ехр(, --)

л (ч )

a,-t,)t

-t, .. V 217-г.)Г/

Л с

где t - время, отсчитываемое от начала интервала времени выборки отсчетного уровня;

изменение отсчетного уровня.

Переменная c(.(t) принимает максимальное значение dt. 0,064 при t l,4t .

Учитьгоая, что погрешность 5,,/vaKc должна превышать величины, определяемой соотношением (4), можно получить лУд С с -Ы

С и 60 пФ 6)

2Vf,, -.,6 v(Q.c

При этом предполагается, что AV 300 мВ - типовая величина изменения отсчетного уровня ряда промышленных ИСХС, Минимальное время выборки информационного сигнала можно определить с помощью соотношения (2), откуда следует, что t -с 52 не, максимальную частоту следования импульсов управления f - из соотношения (3), соответственно f 6,4 МГц для трехфазной ИСЗС.

Устройство считывг чп, выполненное на основе относитетп.но медленных МОП-ключей, позволяет осуществить считывание выходных сигналов практически у всех ИСЗС с 1;оьерхностным каналом, работающих с тактовыми частотами до 10 МГц, с высокой точностью.

Формула изобретения

Устройство считывания, сор фжащее два накопительных конденсатора, три усилителя, три ключевых элемента, первый вывод первого накопительного конденсатора подключен к выходу первого ключевого элемента, вход которого является входом смещения устройства, первый вывод второго накопительного конденсатора подключен к шине нулевого потенциала устройства, а второй вывод подключен к входу третьего усилителя и выходу второго ключевого элемента, вход которого подключен к выходу второго усилителя, второй вы9

вод первого накопительного конденсатора подключен к выходу третьего ключевого элемента, вход которого соединен с выходом первого усилителя, вход которого является информационным входом устройства, управляющие входы первого, второго и третьего ключевых элементов являются соответственно входами фиксации потенциала смещения устройства, фиксации величины информационного сигнала устройства и фиксации сигнала.отсчетного уровня устройства, выход третьего усилителя является информационным выходом устройства, отличаюи

и

Т,

t

Ui

% zA

Un

1

10

щ е е с я тем, что, с целью повьппе- ния точности и Г5ыстродействия устройства, в него введены четвертый и пятый ключевые элементы, управляющие входы которых являются соответственно входами пропускания информационного сигнала устройства и входом выборки экранирующего потенциала, выход первого ключевого элемента подключен к входу четвертого ключевого элемента, выход которого соединен с выходом пятого ключевого элемента и входом второго усилителя, вход пятого ключевого элемента является экранным входом устройства.

П

A1Z.

t

ч

u

и

lit

UHCpMOoixi ffniy Udbixi

/ Ммт

фие. 3

/r

МГц W

7,7-10 3,1-10 4,2-Ю «,5-7 2.0-70 f/f

8Ю

Фие. It

Редактор Т.Лазоренко

Составитель А.Ершова

Техред М.Ходанич Корректор Н.Король

Заказ 5196/52Тираж 587 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

tSf

/Идеальное

UCmDQUCfnSO

USblXi

f2Ht НАЦП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство считывания | 1985 |

|

SU1295454A1 |

| Устройство считывания | 1987 |

|

SU1495852A2 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1345262A1 |

| Устройство аналоговой памяти | 1986 |

|

SU1377916A1 |

| Устройство выборки-хранения | 1987 |

|

SU1425786A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

Изобретение относится к аналоговой вычислительной технике, в частности к устройствам обработки выходного сигнала интегральных схем с за-- рядовой связью, применяемым в телевизионных передающих камерах на основе монолитных фотоприемргых ИС. Цель изобретения - повьотение точности и быстродействия устройства считывания сиг налов с выхода. Устройство содержит накопительные конденсаторы 1„ 2 три усилителя 3, 4, 5, пять ключевых .ентов 6-10, блок 20 управления, . состояготй из элемента 2 ИЛИ 21, элементов 2И 22, 23, элементов 2ИЛИ-НЕ 24, 25, элементов задержки, регистрирующий блок 30. Управление ключевыми элементами осуществляется.так, что при считывании выходного сигнала в интервалах времени между выборками элементы образуют делители с малым коэффициентом передачи неинформапион- ной части сигнала нз устройст- я с . 4 ил. с s (Л со 4 оо со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство считывания | 1985 |

|

SU1295454A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-10-30—Публикация

1986-05-30—Подача