31575203

ства входят блок 1 памяти, коммутатор 2, yMHOKHtenb 3, накапливающий сумматор 4, блок 5 постоянной памяти, счетчик 6 каналов, элемент ИЛИ 7, сумматор 8 адреса, счетчик 9 выборки, счетчик 10 адреса, блок 11 синхроб2

низации, накапливающий сумматор счетчик 13, сумматор 14 адреса, блок 15 памяти адреса, элемент ИЛИ 16, счетчик 17 и коммутатор 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный перестраиваемый цифровой фильтр | 1988 |

|

SU1569955A1 |

| Многоканальный цифровой интерполирующий фильтр для частотного уплотнения каналов | 1987 |

|

SU1525716A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано в многоканальных устройствах связи с цифровой отработкой сигналов. Цель изобретения - расширение функциональных возможностей за счет формирования сигналов с частотным уплотнением каналов. Поставленная цель достигается за счет того, что в состав устройства входят блок памяти 1, коммутатор 2, умножитель 3, накапливающий сумматор 4, блок 5 постоянной памяти, счетчик каналов 6, элемент ИЛИ 7, сумматор адреса 8, счетчик выборки 9, счетчик адреса 10, блок синхронизации 11, накапливающий сумматор 12, счетчик 13, сумматор адреса 14, блок 15 памяти адреса, элемент ИЛИ 16, счетчик 17 и коммутатор 18. 2 ил.

Изобретение относится к радиотехнике и вычислительной технике и мо- жет быть использовано в многоканальных устройствах связи с цифровой обработкой сигналов.

Цель изобретения - расширение функциональных возможностей устройства путем формирования сигналов с частотным уплотнением каналов.

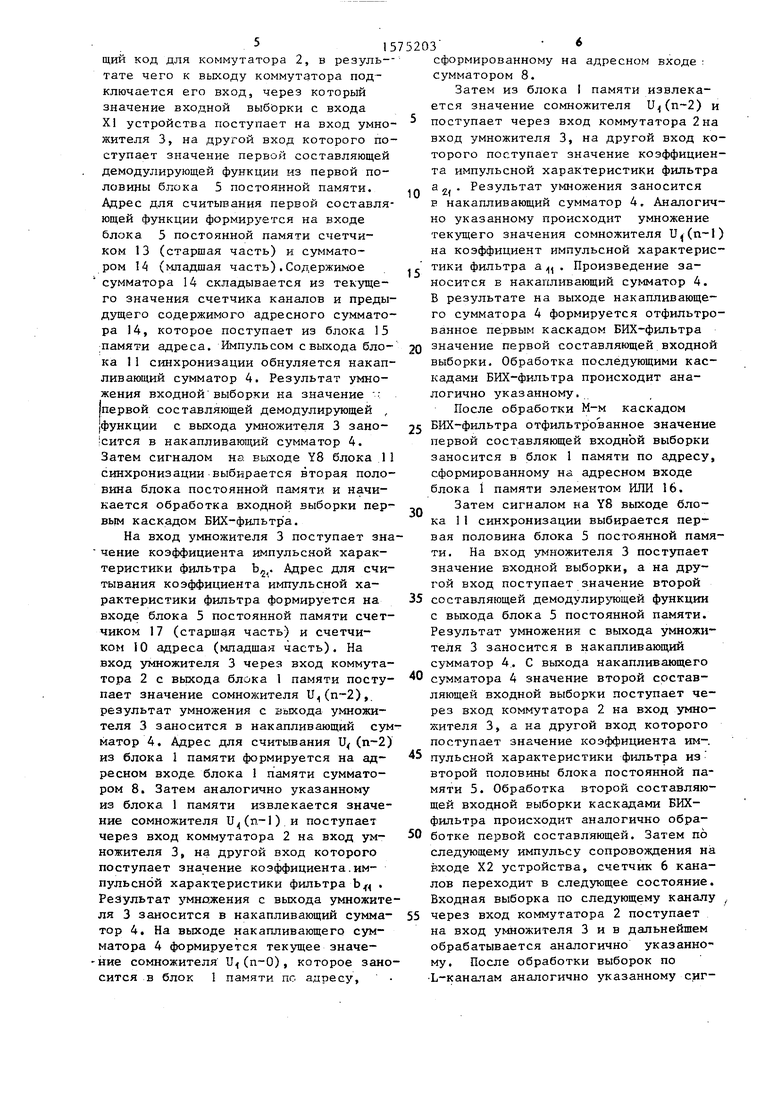

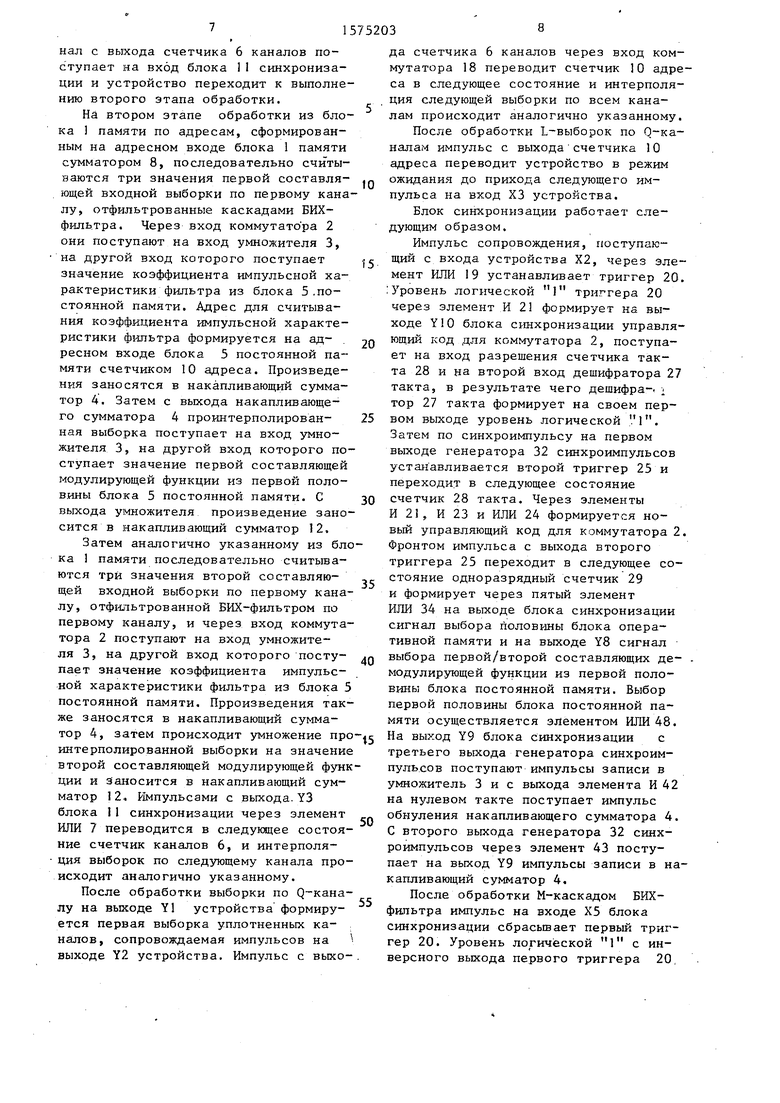

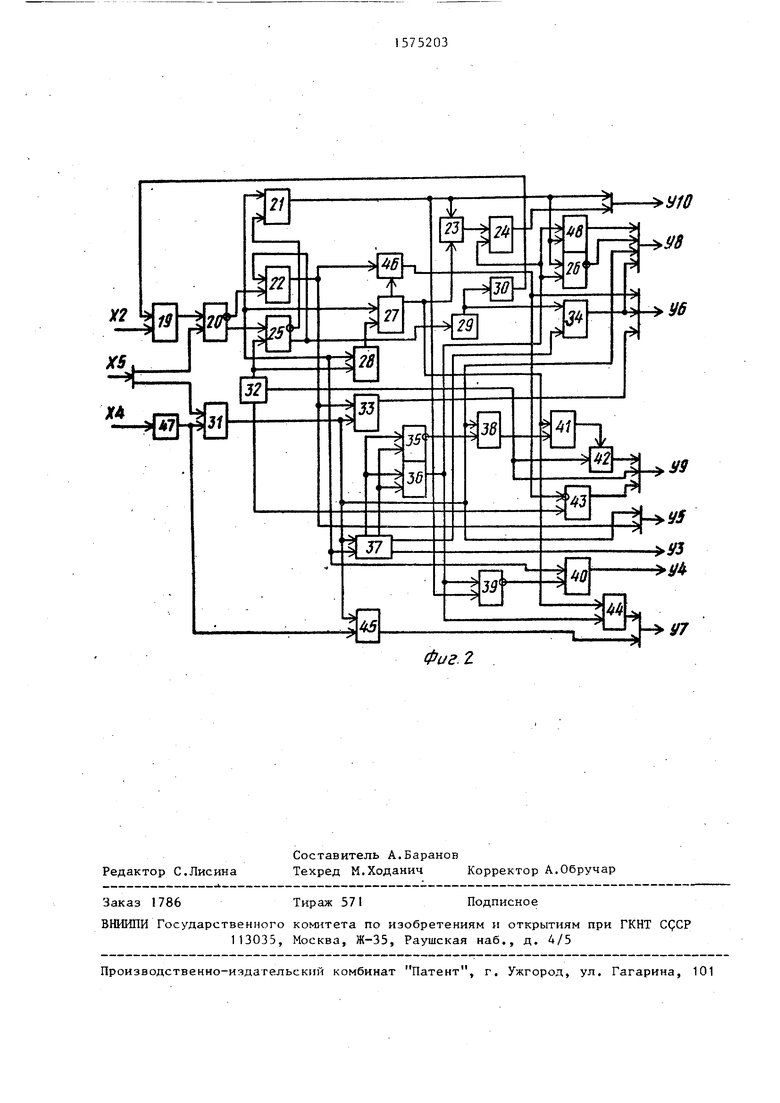

На фиг.1 приведена структурная схема устройства частотного уплотнителя каналов; на фиг.2 - структурная схема блока синхронизации.

Устройство (фиг.1) содержит блок 1 памяти, коммутатор 2, умножитель 3, накапливающий сумматор 4, блок 5 постоянной памяти, счетчик 6 каналов, элемент ИЛИ 7, сумматор 8 адреса, счетчик 9 выборки, счетчик 10 адреса, блок 11 синхронизации, накапливающий сумматор 12, счетчик 13, сумматор 14 адреса, блок 15 памяти адреса, эле- мент ИЛИ 16, счетчик 17 и коммутатор 18.

Блок синхронизации (фиг.2) содержит элемент ИЛИ 19, триггер 20, эле- менты И 21-23, элемент ИЛИ 24, триггер 25, элемент ИЛИ 26, дешифратор 27 шага, счетчик 28 шага, счетчик 29, формирователь 30, триггер 31, генератор 32 тактовых импульсов, элементы ИЛИ 33-35, элемент И 36, счетчик 37, элемент И 38, элемент ИЛИ 39, элемент И 40, элемент ИЛИ 41, элементы И 42-45, элемент ИЛИ 46, формирователь 47, элемент ИЛИ 48.

Частотное уплотнение каналов происходит в четыре этапа.

На нервом этапе выборка входного сигнала умножается на демодулирую- щую функцию вида

e i «Mfi

где fГр - граничная частота среза; fa - частота дискретизации.

Затем производится БИХ-фильтрация квадратурных компонент в соответствии с выражением

U;(n) b,;.U;(n-l) +b2;U;(n-2) +

+ S;.,X ;.,(n)

X;(n) U,(n) (n -1) +

+ a2;U.;(n -1), i ТТм,

где a;,b - коэффициенты БИХ-фильтра;

S i - масштабирующий множитель;

X (n) - текущее значение выборки.

На третьем этапе производится повышение частоты дисретизации в L

раз в соответствии с выражением

к/z

Y;(n) 2lH(L-i+ k)- Х(п -1), J NO

j 0,L,

где X(n) H(L-i+ k)

Y;(n)

J

-текущее значение выборки;

-коэффициент импульсной характеристики фильтра;

-проинтерполированная выборка сигнала.

Затем производится модуляция текущей выборки путем умножения на мно-jeW+Ofrp/ ж

жители вида е 9 и формирование суммарного сигнала путем суммирования полученных составляющих.

Устройство работает следующим об- разом.

По импульсу, приходящему на вход ХЗ устройства, счетчик 13 и счетчик 9 выборки переходят в следующее состояние. Затем по импульсу сопро --- вождения, поступающему на вход Х2 устройства, счетчик каналов переходит в следующее состояние и блок 11 синхронизации начинает генерировать управляющие сигналы первого этапа обработки. На выходе Y10 блока 11 синхронизации формируется управляющий код для коммутатора 2, в резуль- тате чего к выходу коммутатора подключается его вход, через который значение входной выборки с входа XI устройства поступает на вход умножителя 3, на другой вход которого поступает значение первой составляющей демодулирующей функции из первой половины блока 5 постоянной памяти. Адрес для считывания первой составляющей функции формируется на входе блока 5 постоянной памяти счетчиком 13 (старшая часть) и сумматором 14 (младшая часть).Содержимое сумматора 14 складывается из текущего значения счетчика каналов и предыдущего содержимого адресного сумматора 14, которое поступает из блока 15 памяти адреса. Импульсом с выхода блока 11 синхронизации обнуляется накапливающий сумматор 4. Результат умножения входной выборки на значение (первой составляющей демодулирующей , (функции с выхода умножителя 3 зано- сится в накапливающий сумматор 4. Затем сигналом нэ выходе Y8 блока 11 синхронизации выбирается вторая половина блока постоянной памяти и начинается обработка входной выборки первым каскадом БИХ-фильтр а.

На вход умножителя 3 поступает значение коэффициента импульсной характеристики фильтра Ь. Адрес для считывания коэффициента импульсной характеристики фильтра формируется на входе блока 5 постоянной памяти счетчиком 17 (старшая часть) и счетчиком 10 адреса (младшая часть). На вход умножителя 3 через вход коммутатора 2 с выхода блока 1 памяти поступает значение сомножителя ), результат умножения с зогхода умножителя 3 заносится в накапливающий сумматор 4. Адрес для считывания U (n-2) из блока 1 памяти формируется на адресном входе блока 1 памяти сумматором 8. Затем аналогично указанному из блока 1 памяти извлекается значение сомножителя U,,(n-l) и поступает через вход коммутатора 2 на вход умножителя 3, на другой вход которого поступает значение коэффициента.импульсной характеристики фильтра Ь . Результат умножения с выхода умножитея 3 заносится в накапливающий сумматор 4. На выходе накапливающего суматора 4 формируется текущее значеие сомножителя и(п-0), которое заносится в блок 1 памяти пг. адресу,

5203

сформированному на адресном входе сумматором 8.

Затем из блока 1 памяти извлекается значение сомножителя U(n-2) и поступает через вход коммутатора 2 на вход умножителя 3, на другой вход которого поступает значение коэффициента импульсной характеристики фильтра а2 . Результат умножения заносится в накапливающий сумматор 4, Аналогично указанному происходит умножение текущего значения сомножителя U(n-l) на коэффициент импульсной характерис10

тики фильтра а . Произведение за

носится в накапливающий сумматор 4. В результате на выходе накапливающего сумматора 4 формируется отфильтрованное первым каскадом БИХ-фильтра

значение первой составляющей входной выборки. Обработка последующими каскадами БИХ-фильтра происходит аналогично указанному.

После обработки М-м каскадом

БИХ-фильтра отфильтрованное значение первой составляющей входной выборки заносится в блок 1 памяти по адресу, сформированному на адресном входе блока 1 памяти элементом ИЛИ 16.

Затем сигналом на Y8 выходе блока 11 синхронизации выбирается первая половина блока 5 постоянной памяти. На вход умножителя 3 поступает значение входной выборки, а на другой вход поступает значение второй

составляющей демодулирующей функции с выхода блока 5 постоянной памяти. Результат умножения с выхода умножителя 3 заносится в накапливающий сумматор 4. С выхода накапливающего

сумматора 4 значение второй составляющей входной выборки поступает через вход коммутатора 2 на вход умножителя 3, а на другой вход которого поступает значение коэффициента им-.

пульсной характеристики фильтра из второй половины блока постоянной памяти 5. Обработка второй составляющей входной выборки каскадами БИХ- фильтра происходит аналогично обработке первой составляющей. Затем по следующему импульсу сопровождения на входе Х2 устройства, счетчик 6 каналов переходит в следующее состояние. Входная выборка по следующему каналу ,

через вход коммутатора 2 поступает на вход умножителя 3 и в дальнейшем обрабатывается аналогично указанному. После обработки выборок по L-каналам аналогично указанному сиг10

15

нал с выхода счетчика 6 каналов поступает на вход блока 11 синхронизации и устройство переходит к выполнению второго этапа обработки.

На втором этапе обработки из блока 1 памяти по адресам, сформированным на адресном входе блока 1 памяти сумматором 8, последовательно считываются три значения первой составляющей входной выборки по первому каналу, отфильтрованные каскадами БИХ- фильтра. Через вход коммутатора 2 они поступают на вход умножителя 3, на другой вход которого поступает значение коэффициента импульсной характеристики фильтра из блока 5.постоянной памяти. Адрес для считывания коэффициента импульсной характеристики фильтра формируется на адресном входе блока 5 постоянной памяти счетчиком 10 адреса. Произведения заносятся в накапливающий сумматор 4. Затем с выхода накапливающего сумматора 4 проинтерполирован- ная выборка поступает на вход умножителя 3, на другой вход которого поступает значение первой составляющей модулирующей функции из первой половины блока 5 постоянной памяти. С 30 выхода умножителя произведение заносится в накапливающий сумматор 12,

Затем аналогично указанному из блока памяти последовательно считываются три значения второй составляющей входной выборки по первому каналу, отфильтрованной БИХ-фильтром по первому каналу, и через вход коммутатора 2 поступают на вход умножителя 3, на другой вход которого поступает значение коэффициента импульсной характеристики фильтра из блока 5 постоянной памяти. Прроизведения также заносятся в накапливающий сумма15752038

да счетчика 6 каналов через вход коммутатора 18 переводит счетчик 10 адреса в следующее состояние и интерполяция следующей выборки по всем каналам происходит аналогично указанному. После обработки L-выборок по Q-ка- налам импульс с выхода счетчика 10 адреса переводит устройство в режим ожидания до прихода следующего импульса на вход ХЗ устройства.

Блок синхронизации работает следующим образом.

Импульс сопровождения, поступающий с входа устройства Х2, через элемент ИЛИ 19 устанавливает триггер 20. Уровень логической 1 триггера 20 через элемент И 21 формирует на выходе YIO блока синхронизации управляющий код для коммутатора 2, поступает на вход разрешения счетчика такта 28 и на второй вход дешифратора 27 такта, в результате чего дешифра-. ; тор 27 такта формирует на своем первом выходе уровень логической 1. Затем по синхроимпульсу на первом выходе генератора 32 синхроимпульсов устанавливается второй триггер 25 и переходит в следующее состояние счетчик 28 такта. Через элементы И 21, И 23 и ИЛИ 24 формируется новый управляющий код для коммутатора 2. Фронтом импульса с выхода второго триггера 25 переходит в следующее состояние одноразрядный счетчик 29 и формирует через пятый элемент ИЛИ 34 на выходе блока синхронизации сигнал выбора половины блока оперативной памяти и на выходе Y8 сигнал выбора первой/второй составляющих де- модулирующей функции из первой половины блока постоянной памяти. Выбор первой половины блока постоянной памяти осуществляется элементом ИЛИ 48.

20

25

35

40

тор 4, затем происходит умножение про- На выход Y9 блока синхронизации с

интерполированной выборки на значение второй составляющей модулирующей функции и заносится в накапливающий сумматор 12.. Импульсами с выхода Y3 блока 11 синхронизации через элемент ИЛИ 7 переводится в следующее состояние счетчик каналов 6, и интерполяция выборок по следующему канала происходит аналогично указанному.

После обработки выборки по Q-кана- лу на выходе Y1 устройства формируется первая выборка уплотненных каналов, сопровождаемая импульсов на выходе Y2 устройства. Импульс с выхо50

55

третьего выхода генератора синхроимпульсов поступают импульсы записи в умножитель 3 и с выхода элемента И 4 на нулевом такте поступает импульс обнуления накапливающего сумматора 4 С второго выхода генератора 32 синхроимпульсов через элемент 43 поступает на выход Y9 импульсы записи в н капливающий сумматор 4.

После обработки М-каскадом БИХ- фильтра импульс на входе Х5 блока синхронизации сбрасывает первый триг гер 20. Уровень логической 1 с инверсного выхода первого триггера 20

50

55

третьего выхода генератора синхроимпульсов поступают импульсы записи в умножитель 3 и с выхода элемента И 42 на нулевом такте поступает импульс обнуления накапливающего сумматора 4. С второго выхода генератора 32 синхроимпульсов через элемент 43 поступает на выход Y9 импульсы записи в накапливающий сумматор 4.

После обработки М-каскадом БИХ- фильтра импульс на входе Х5 блока синхронизации сбрасывает первый триггер 20. Уровень логической 1 с инверсного выхода первого триггера 20

через элемент И 22 формирует на выходе Y5 блока синхронизации импульс для управления элементом ИЛИ 16 и через элемент ИЛИ 46 формирует на выходе Y6 блока синхронизации сигнал записи в блок 1 памяти, который через элемент И 43 блокирует на выходе Y9 синхронизации импульсы записи в накапливающий сумматор 4 и через элементы И 40 и ИЛИ 39 пропускает с первого выхода генератора 32 синхроимпульсов один импульс на выход Y4 блока синхронизации, который переводит второй счетчик 17 в следующее состояние. Этот же синхронизатор сбрасывает второй триггер 25. Фронтом сигнала с выхода второго триггера 25 переводится в следующее состояние одноразрядный счетчик 29, в результате чего через элемент ИЛИ 34 сигналом с выхода одноразрядного счетчика 29 выбирает на выходеY6 блока синхронизации вторую половину блока 1 памяти и на выходе Y8 блока синхронизации вторую составляющую де модулирующей функции для блока 5 постоянной памяти и через формирователь 30 формирует короткий импульс, который устанавливает первый триггер 20. Во время обработки второй составляющей входной выборки блок синхронизации работает аналогично указанному. Затем следующий импульс сопровождения поступает на вход Х2 блока синхронизации и указанная последовательность действий повторяется для выборки по следующему каналу

После обработки Q-канала сигнал входа Х4 блока синхронизации поступает на вход формирователя 47, который формирует короткий импульс, устанавливающий третий триггер 3), и блок синхронизации переходит по второму этапу обработки. Уровень логической 1 с выхода третьего триггера 31 поступает на вход разрешения трехразрядного счетчика 37, через выход Y5 блока синхронизации переводит в следующее состояние счетчик 10 адреса, на выходе Y8 и через элемент ИЛИ 33, на выходе Y6 блока синхронизации определяет режим второго этапа обработки для блоков 5 и 1 памяти соответственно .

С первого выхода генератора 32 синхроимпульсов синхроимпульсы поступают на вход трехразрядного счетчика 37 и второй вход элемента И 40. С четвертого выхода трехразрядного

1

75203

10

10

15

20

счетчика 37 на выход Y3 блока синх-, ронизации поступают тактовые импульсы для счетчика 6 каналов. С вы- , хода элемента И 40 на выход Y4 блока синхронизации поступают тактовые импульсы для второго счетчика 17. Элементы И 35 и ИЛИ 36 служат для выделения первого и последнего тактов трехразрядного счетчика 37. По первому тркту счетчика 37 через элементы И 18, 42 и ИЛИ 41 формируется на выходе Y9 блока синхронизации импульс обнуления накапливающего сумматора 4, по последнему такту счетчика 37 через элемент ИЛИ 43 на выходе Y8 блока синхронизации формируется сигнал выбора первой половины блока 5 постоянной памяти. Через элемент И 44 на выходе Y7 блока синхронизации формируется импульс записи в накапливающий сумматор 12 и через элемент ИЛИ 39 блокируется прохождение синхроимпульсов для второго счетчика 17 на выход jc Y4 блока синхронизации. Импульс с четвертого трехразрядного счетчика 37 через выход Y3 блока синхронизации переводит в следующее состояние счетчик 6 каналов и второй этап обработки повторяется для следующего канала аналогично указанному. После обработки выборок по Q-каналу импульс, сформироранный формирователем 47 из сигнала на входе Х4 блока синхронизации, формирует через элемент И 45 на выходе Y7 блока синхронизации импульс сопровождения первой уплотненной точки по всем каналам которой является одновременно импульсом обнуления накапливающего сумматора 12. При формировании последующих уплотненных точек блок синхронизации функционирует аналогично указанному.

После получения L-точки по всем каналам импульсом с входа Х5 сбрасывается третий триггер 31 и блок синхронизации переходит в режим ожидания до прихода следующего импульса сопровождения на вход Х2 блока синхронизации.

Формула изобретения

Згстройство для цифровой обработки 55 сигналов, содержащее блок памяти, блок постоянной памяти, умножитель, первый накапливающий сумматор, первый элемент ИЛИ, первый сумматор адреса, счетчик канала, счетчик выборки,

30

35

40

45

50

счетчик адреса и блок синхронизации, первый выход которого подключен к певому входу первого элемента ИЛИ, выход которого подключен к счетному входу счетчика каналов, информационный выход которого подключен к пер- вому адресному входу блока памяти, второй адресный вход которого под- хпючен к выходу первого сумматора адреса, первый вход которого подключен к информационному выходу счетчика выборки, счетный вход которого подключен к тактовому входу устройства, входом запуска которого являются соединенные между собой второй вход первого элемента ИЛИ и вход запуска

блока синхронизации, второй выход которого подключен к тактовому входу первого накапливающего сумматора и входу синхронизации умножителя первого накапливающего сумматора, выход которого подключен к информационному входу блока памяти, третий выход блока синхронизации подключен к счетному входу счетчика адреса, информационный выход которого подключен к первому адресному входу блока постоянной памяти, выход переполнения счетчика адреса подключен к входу останова блока синхронизации, чет вертый выход которого подключен к входу управления считыванием блока

постоянной памяти, выход которого подключен к первому информационному входу умножителя, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования сигналов с частотным уплотнением каналов, в него введены второй накапливающий сумматор, второй элемент ИЛИ, второй сумматор адреса, первый и второй счетчики,первый и второй коммутаторы и блок памяти адреса, выход которого подключен к первому входу второго сумматора адреса, выход которого подключен к информационному входу блока памяти адреса и второму адресному входу блока постоянной памяти, третий адресный вход которого подключен к информационному выходу первого счетчика, счет0

5

0

5

0

5

0

5

0

ныи вход которого подключен к тактовому входу устройства, информационный вход которого подключен к первому информационному входу первого коммутатора, выход которого подключен к информационному входу второго накапливающего сумматора, выход которого является информационным выходом устройства, выход окончания вычислений которого соединен с тактовым входом второго накапливающего сумматора и подключен к пятому выходу блока синхронизации, шестой выход которого подключен к управляющему входу первого коммутатора, второй и третий информационные входы которого подключены к выходам соответственно блока памяти и первого накапливающего сумматора, информационный выход счетчика канала подключен к второму входу второго сумматора адреса и адресному входу блока памяти адреса, вход управления записью считыванием которого подключен к четвертому выходу блока синхронизации, седьмой выход которого подключен к счетному входу второго счетчика,,первый информационный выход которого подключен к первому информационному входу второго коммутатора, выход которого подключен к установочному входу счетчика адреса, выход младшего разряда которого подключен к первому входу второго элемента ИЛИ, выход которого подключен к входу управления записью-считыванием блока памяти, второй информационный выход счетчика, подключен к второму входу первого сумматора адреса и четвертому адресному входу блока постоянной памяти, выход переполнения счетчика каналов подключен к управляющему входу второго коммутатора и входу выбора режима блока синхронизации, третий выход которого подключен к второму информационному входу второго коммутатора и второму вхо- ,ду второго элемента ИЛИ, а третий вход второго сумматора адреса является входом задания логической единицы устройства.

Редактор С.Лисина

Составитель А.Баранов

Техред М.Ходанич Корректор А.Обручар

Заказ 1786

Тираж 571

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

. - - -- - - « - - - - - - --

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

У6

УЗ

Фиг. Z

Подписное

| Цифровое устройство преобразования групповых сигналов систем связи с частотным разделением каналов | 1983 |

|

SU1145485A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-05—Подача