Изобретение относится к автоматике и телемеханики, может быть использовано в системах тeлevпpaвлeния-тe- лесигнализации, а также для приема различной дискретной информации в системах передачи данных.

Целью изобретения является повышение достоверности информации.

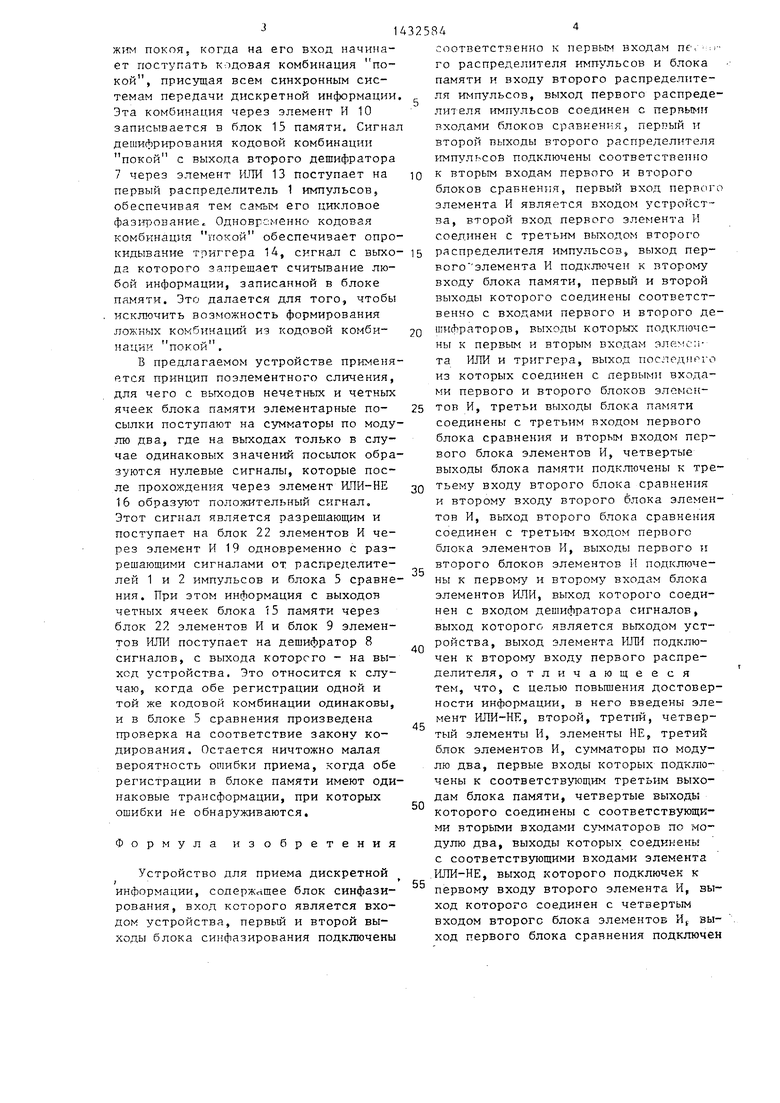

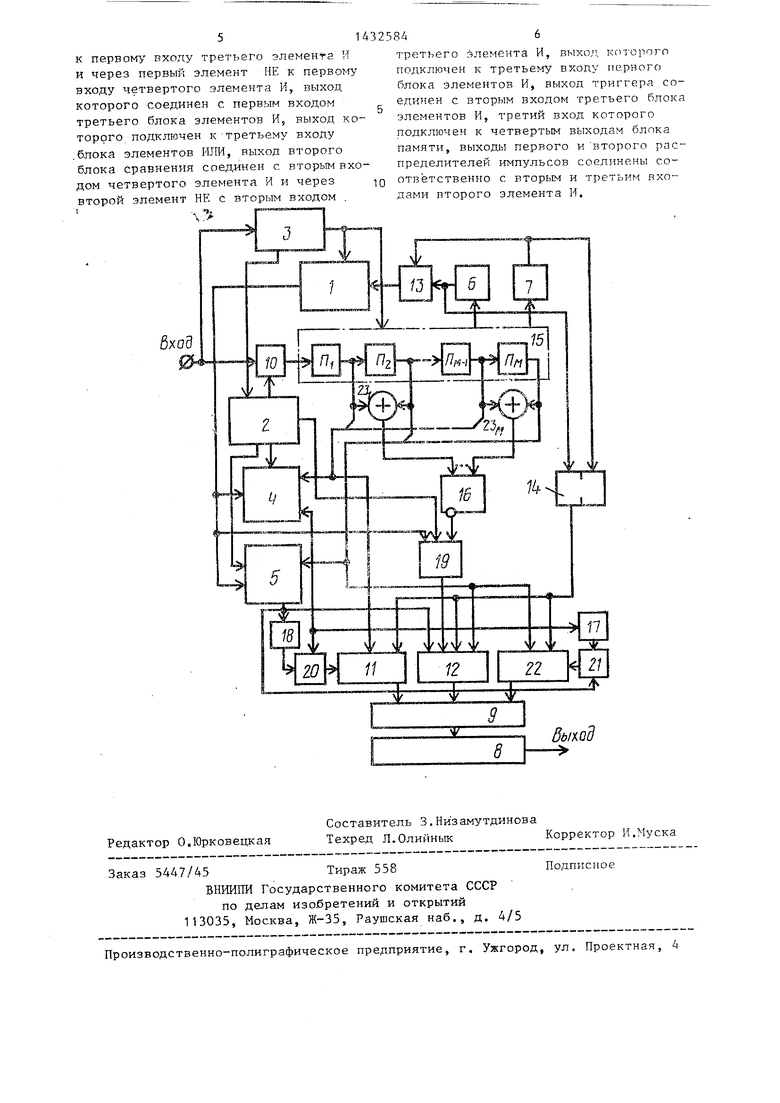

На чертеже показана структурная схема предлагаемого устройства.

Устройство содержит распределители 1 и 2 импульсов, блок 3 синфазиро вания, блоки 4 и 5 сравнения, дешифраторы 6 и 7, дешифратор 8 сигналов, блок 9 Элементов ИЛИ, первый элемент И 10, первьм и второй блоки 11,12 элементов И, элемент ИЛИ 13, триггер 14, блок 15 памяти, элемент ИЛИ-НЕ 16, элементы НЕ 17 и 18, второй, тре тий и четвертый элементы И 19-21, третий блок 22 элементов И-и сумматоры ,д по модулю два I

Блок 15 памяти выполнен по схеме продвигающего регистра с числбм ячее памяти, в два раза превьппающим количество разрядов кода, поступающего на вход устройства. Дешифраторы б и 7 представляют собой диодные сборки и служат для декодирования кодовых комбинаций фазирования по циклу и вскрытия устройства и покой соответственно. Триггер 14 обеспечивает разрешение считывания информации с блока памяти при поступлении с выход дешифратора 8 сигналов сигнала фазирования по циклу, которьй одновременно служит сигналом вскрытия устройства. При поступлении кодовой комбинации покой сигналом с выхода да шифратора 7 Т13иггер 14 опрокидывается, тем самым с входов блоков элементов И снимается сигнал разрешения считывания информации, накопленной в блоке 15 памяти. Распределитель 1 им пульсов служит для формирования импульсов, соответствующих по времени началу и концу кодовых комбинаций, записываемых в блок памяти. Точное совпадение формируемых импульсов с началом и концом кодовой комбинации информации обеспечивается сбросом распределителя импульсов в исходное состояние при декодировании кодовой комбинации покой или специальное передаваемой в начале цикла телеуправления кодовой комбинации фазирования по циклу. Блоу 3 синфазирования управляется информационными импуль

поступающими на вход устройстQ

5 0

5

0

5 0 5

0

5

ва, и обеспечивает формирование импульсной последовательности для работы блоков 4 и 5 сравнения, а также формирование тактовых импульсов распределителя 1 1-1Нпульсов. Распределитель 2 импульсов формирует рабочие импульсы блоков 4 и 5 сравнения, а также стробирующие импульсы удвоенной тактовой частоты, отстоящие от середин информационных импульсов на четверть такта. Блоки 4 и 5 сравнения обеспечивают проверку кода на соответствие закону кодирования

Устройство работает следующим образом.

На вход устройства поступают и;- - пульсы дискретной информации в виде последовательности кодовых комбинаций „ Они подаются на вход блока 3 ски- фазирования и элемент И 10, на второй вход которого подаются сдвоенные стробирующие кипульсы распределителя 2, управляемого блоком 3 синфазирова- ния С выхода элемента И 10 дискретная информация записывается в блок 15 памяти. После регистрации кодовой комбинации цшслового фазирования, предназначенной для установки икло вой фазы устройства, а также для его вскрытия, на выходе дешифратора б появляются импульсы сброса распределителя 1 в исходное полож;ение и импульсы опрокидывания триггера 14, обеспечивающего вьздачу сигнала разрешения считывания дискретной информации через один из блоков 11,12 или 22 элементов. В процессе приема и записи в блок памяти кодовых комбинаций производится их анализ на соответствие закону кодирования, вьтолняемый блоками 4 и 5 сравнения, а такжа слежение по модулю два каждого разряда двух регистрации одной и той же кодовой комбинации, используемое для повышения достоверности принимаемой информации, В зависимости от результатов проверки с выходов блоков 4 и 5 сравнения на один из блоков 11,12 или 22 элементов И выдается разрешающий потенциал, по которому одна из двух регистрации, записанных в блоке 15 памяти через блок 9 элементов ИЛИ считьгоается на дешифратор 8 сиг налов и поступает на выход устройства.

После завершения приема дискретной информации устройство переходит в ре

3

жим покоя, когда на его вход nam-iFfa- ет поступать кодовая комбинация покой, присущая всем синхронным системам передачи дискретной информации Эта комбинация через элемент И 10 записывается в блок 15 памяти. Сигна деошфрирования кодовой комбинации покой с выхода второго дешифратора 7 через элемент ИЛИ 13 поступает на первый распределитель 1 импульсов, обеспечивая тем самым его цикловое фаз фонание. Oднoвpc eннo кодовая комбинация покой обеспечивает опрокидывание триггера 14, сигнал с вьгхо да которого запрещает считывание любой информации, записанной в блоке памяти. Это далается для того, чтобы исключить возможность формирования ложных комбинаций из кодовой комби- нации покой.

В предлагаемом устройстве применяется принцип поэлементного сличения, для чего с выходов нечетных и четных ячеек блока памяти элементарные по- сылки поступают на сумматоры по модулю два, где на выходах только в случае одинаковых значений посылок образуются нулевые сигналы, которые после прохох дения через элемент ИЛИ-НЕ 16 образуют положительный сигнал. Этот сигнал является разрещающим и поступает на блок 22 элементов И через элемент И 19 одновременно с разрешающими сигналами от распределителей 1 и 2 импульсов и блока 5 сравнения. При этом информация с выходов четных ячеек блока 15 памяти через блок 22 элементов И и блок 9 элементов ИЛИ поступает на дещифратор 8

сигналов, с выхода которого - на выход устройства. Это относится к случаю, когда обе регистрации одной и той же кодовой комбинации одинаковы, и в блоке 5 сравнения произведена проверка на соответствие закону кодирования. Остается ничтожно малая вероятность ошибки приема, когда обе регистрации в блоке памяти имеют одинаковые трансформации, при которых ошибки не обнаруживаются.

Формула изобретения

Устройство для приема дискретной I

информации, содержащее блок синфази- рования, вход которого является входом устройства, первый и второй выходы блока синфазирования подключены

IA32584

s

5 о

5

0

5

0

5

соответственно к первы входам по.. го распределителя и тульсов и блока памяти и входу второго распределителя импульсов, выход первого распределителя импульсов соединен с; первыми входами блоков сравнения, перпый и второй выходы второго распределителя импульсов подключены соответственно к вторым входам первого и второго блоков сравнения, первый вход первого элемента И является входом устройства, второй вход первого элемента И соединен с третьим выходом второго распределителя импульсов, выход пер- вого элемента И подключен к BTopoNfy входу блока памяти, первьй и второй выходы которого соединены соответственно с входами первого и второго дешифраторов, выходы которых подключены к первьпч и вторым входам та ИЛИ и триггера, выход последпрго из которых соединен с первыми входами первого и второго блоков элементов И, третьи выходы блока памяти соединены с третьим входом первого блока сравнения и вторьгм входом первого блока элементов И, четвертые выходы блока памяти подк.точены к третьему входу второго блока сравнения и второму входу второго блока элементов И, выход второго блока сравнения соединен с треты-гм входом первого блока элементов И, выходы первого и второго блоков элементов И подключены к первому и второму входам блока элементов ИЛИ, выход которого соединен с входом дещифратора сигналов, выход которого является выходом устройства, выход элемента ИЛИ подключен к второму входу первого распределителя, отличающееся тем, что, с целью повыщения достоверности информации, в него введены элемент ИЛИ-НЕ, второй, трет1гй, четвертый элементы И, элементы НЕ, третий блок элементов И, сумматоры по модулю два, первые входы которых подключены к соответствующим третьим выходам блока памяти, четвертые выходы которого соединены с соответствующими вторыми входами сумматоров по модулю два, выходы которых соединены с соответствующими входами элемента .ШШ-НЕ, выход которого подключен к первому входу второго элемента И, выход которого соединен с четвертым входом второго блока элементов Hf вы- . ход первого блока сравнения подключен

6хо9

N/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1985 |

|

SU1275508A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство для приема команд телеуправления | 1981 |

|

SU991473A1 |

| Адаптивное устройство для приема информации с рассредоточенных объектов | 1990 |

|

SU1751798A1 |

| Устройство для приема телесигналов | 1980 |

|

SU942112A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для приема телесигналов | 1976 |

|

SU610152A1 |

| Адаптивный приемник информации с удаленных рассредоточенных объектов | 1991 |

|

SU1807510A1 |

| Адаптивный приемник информации с рассредоточенных объектов | 1991 |

|

SU1807508A1 |

| Устройство для профессионального отбора операторов | 1989 |

|

SU1695362A1 |

Изобретение относится к технике автоматизации приема и передачи дискретной информации, информации телеуправления, телесигнализадш, телеизмерений и телеконтроля. Целью изобретения является повышение достоверности приема дискретной информации. Устройство содержит распределители импульсов, блок синфазирования, блоки сравнения, дешифраторы , блок элементов ИЛИ, элементы И, элемент ИЛИ, триггер, блок памяти, элемент РШИ-ИЕ, элементы НЕ, блоки элементов И, сумматоры. Цель достигается путем снижения вероятности регистрации искажений кодовых комбинаций типа трансформация. 1 ил. S

Авторы

Даты

1988-10-23—Публикация

1987-04-29—Подача