л

(

11432608

Изобретет-ше относится к вычисли- тельной технике и может найти применение для распознавания и синтеза Сигналов9 в частности речевыхj, и поиска справочной информации.

Цель изобретения расширение области применения устройства за счет ывода из устройства инфор1у ационных

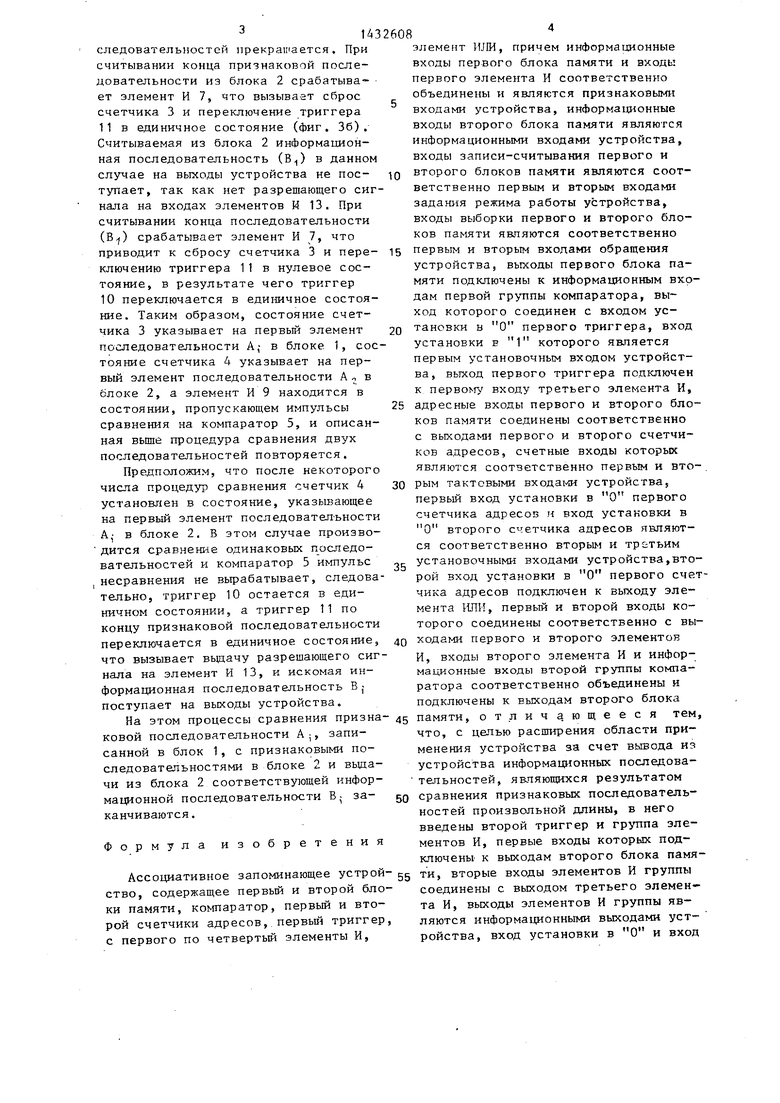

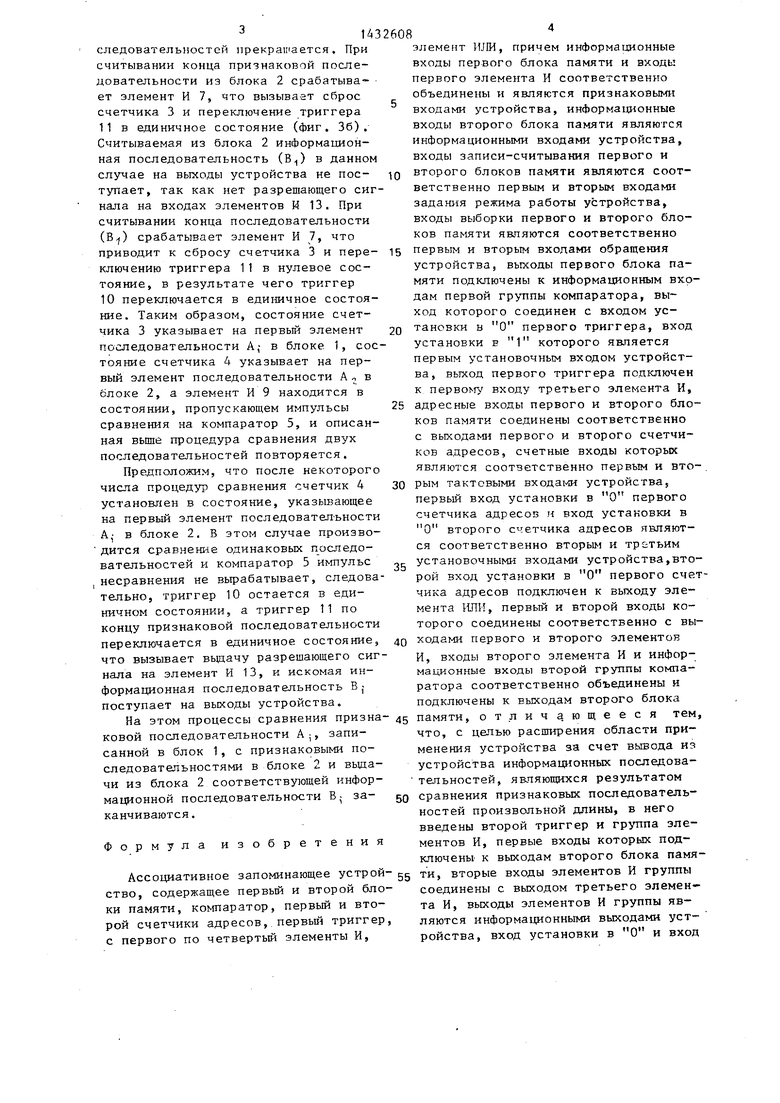

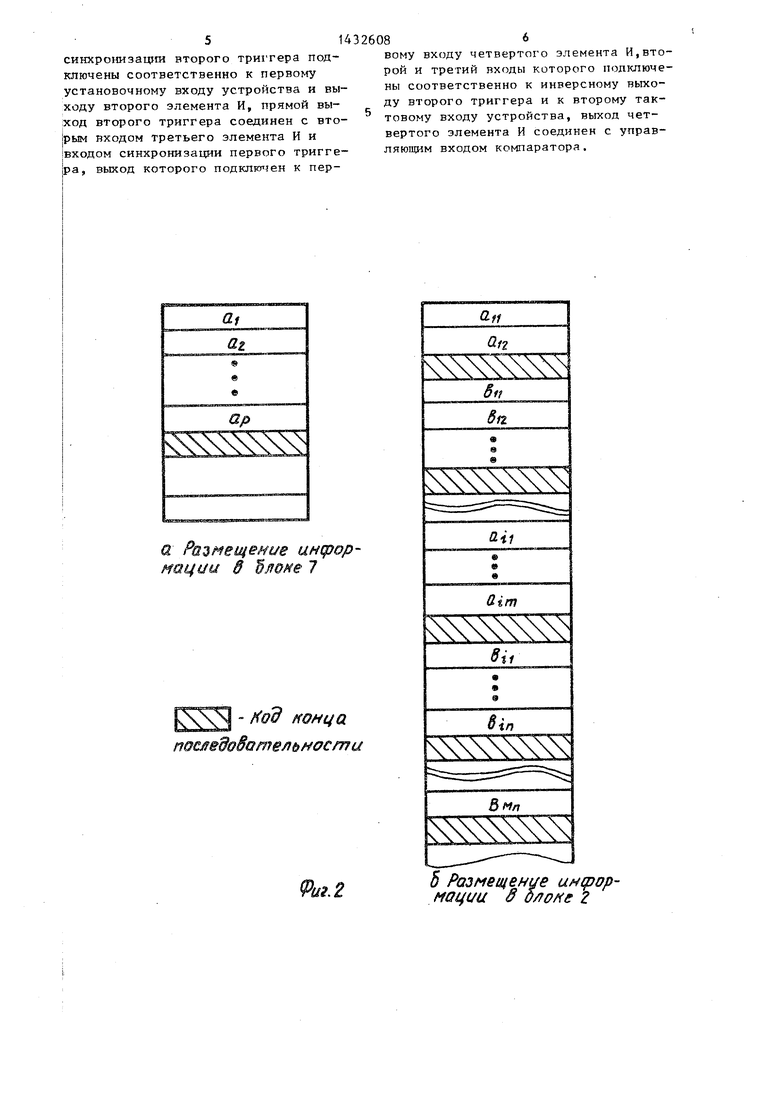

Последовательностей, являющихся ре ультатом сравнения признаковьсс но- рледовательностай произвольной длиньь I На фиг, 1 изображена структурная схема ассоциативного запоминающего устройства (ЗУ)J на фиг, 2 размещение информации в первом и втором блоках памяти; на фиг. 3 - временная liHarpaffl a работы устройства. : Устройство содержит первый 1 и , :рторой 2 блоки па -1яти„ Блох 1 пред- тавляет собой буферное ЗУ,, в кото- :)ое записывается признаковая последовательность А

(а., а

1

ар)

-де р - переменная ветшчина (фнг.2а) } блоке 2 храш1тся массив признако- зых последовательноетей А (..pj 1дд) 5- каждому элементу А которого тоставлена в соответствиа ннформаци- последовательность В (Ь, .o.jbo), где q - переменная величина. Иными словами, структура данных В накопителе 2 имеет вид АВ (А В, э о о е 5 ,,) 5 причем каждый элемент А- И В . этой структзФЫ заканчивается кодом конца поспедозательности (фиг.26)

К адресным входам блоков 1 и 2 Подключены первый 3 и второй 4 счетчики адресов 5 счетные входы которых являются тактовыми входами устройства,. Сравнение признаковой последовательности А-з записанной в блоке 1, с массивом признаковых последовательностей А А ,s ,. .- эА р,1 5 хранимым в блоке 25 производится в компараторе 5

Устройство также содержит первый 6, второй Ур третий 8 и четвертый 9 элементы И, первьй 10 и второй 11 триггеры элемент ИЛИ 12 и группу элементов И 13, Устройство имеет первый 14 и второй 15 тактовые входы, первый 16 и второй 17 входы задания режима работы, признаковые входы 18 и информащ-юнные выходы 19 первьй 20 и второй 21 входы обращения,, первый 22, второй 23 и третий 24 установочные входы, инФормащюнные входы 25

Устройство работает следующем образом

0

При включении устройства в работу счетчики 3 и 4 сбрасьюаются в нуль, триггеры 10 и 11 устанавливаются соответственно в единичное и нулевое состояние,

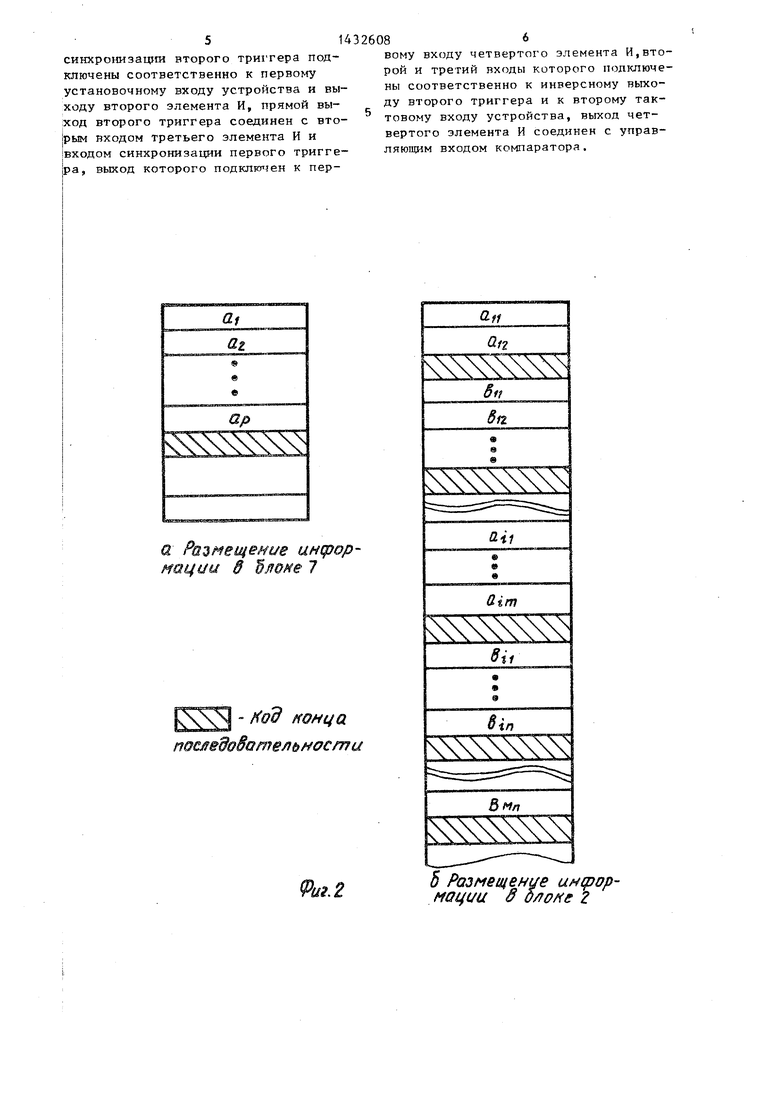

На первом этапе проводится запись признаковой последовательности в блок 1, Запись осуществляется в порядке поступления счетных импульсов на счетчик 3 При поступлении на информационные входы устройства кода конца последовательности, которьй тоже записывается в блок 1, срабатьшает

5 элемент И 6, что приводит к сбросу счетчика 3 и прекращению записи в блок 1 (фиг, За),

На втором этапе проводится сравнение признаковой последовательности,

0 записанной в блоке 1, с признаковыми последовательностями, содержапщ- шcя в блоке 2.

Допустим, что в результате проведенной процедуры в блоке 1 записана

5 признаковая последовательность А;. Сначала сравниваются последовательность А ; с блока 1 и последовательность А 1 с блока 2. Счетчики 3 и 4 установлены на первые элементы после0 довательностей А и А соответственно lisiK сброшены в нуль.

Считывание информации из блоков 1 и 2 производится синхронно по мере поступления импульсов на счетные входы счетчиков 3 и 4, Импульсы на вход счетчика 4 поступают на устройство при условии, что присутствует сигнал Выборка ЗУ (фиг. Зб,в,г,д).. Считываемая информация поступает на входы компаратора 5.

Сравнение признаковых последовательностей проводится по поступпеник импульсов сравнения с- выхода элемента И 9, которые поступают в соответствии с импульсами, приходящими на вход счетчика 4, при условии, что триггеры 10 и 11 находятся соответ- ственнр в единичном и нулевом состоянии. Компаратор 5 срабатьшает по несовпадению, что приводит к установке триггера 10 в нулевое состояние, чтоэ в свою очередь ведет к прекращению подачи импульсов сравнения на компаратор 5,

Таким образом, если в ходе сравнения слов признаковых последовательностей А; и А, произошло несовпадение, дальнейшее сравнение считываемых слов данных признаковых по5

0

5

O

следовательиосте 1 прекраи ается, При считывании конца признаковой последовательности из блока 2 срабатывает элемент И 7, что вызыва-зт сброс счетчика 3 и переключение триггера 11 в единичное состояние (фиг. 36). Считываемая из блока 2 информационная последовательность (В) в данном случае на вьтаоды устройства не пес- тупает, так как нет разрешающего сигнала на входах элементов И 13. При считывании конца последовательности (В) срабатывает элемент И 7, что приводит к сбросу счетчика 3 и пере- ключению триггера 11 в нулевое состояние, в результате чего триггер 10 переключается в единичное состояние. Таким образом, состояние счетчика 3 указывает на первьй элемент последовательности А,- в блоке 1, состояние счетчика 4 указывает на первый элемент последовательности А в блоке 2, а элемент И 9 находится в состоянии, пропускающем импульсы сравнения на компаратор 5, и описанная выше процедура сравнения двух последовательностей повторяется.

Предположим, что после некоторого числа процедур сравнения счетчик 4 установлен в состояние, указывающее на первый элемент последователъности А,- в блоке 2, В этом случае производится сравнение одинаковых последовательностей и компаратор 5 импульс несравнения не вьфабатывает, следовательно, триггер 10 остается в единичном состоянии, а триггер 11 по концу признаковой последовательности переключается в единичное состояние, что вызывает вьщачу разрешающего сигнала на элемент И 13, и искомая информационная последовательность В поступает на выходы устройства.

5 5

0 0

5

элемент ШМ, причем информагдионные входы первого блока памяти и входы первого элемента И соответственно объединены и являются признаковыми входами устройства, информационные входы второго блока памяти являются информационными входами устройства, входы записи-считывания первого и второго блоков памяти являются соответственно первым и вторым входами задания режима работы устройства, входы выборки первого и второго блоков памяти являются соответственно первым и вторым входами обращения устройства, выходы первого блока памяти подключены к информационным входам первой группы компаратора, выход которого соединен с входом установки в О первого триггера, вход установки в 1 которого является первым установочным входом устройства, выход первого триггера подключен к nepBONry входу третьего элемента И, адресные входы первого и второго блоков памяти соединены соответственно с выходами первого и второго счетчиков адресов, счетные входы которых являются соответственно первым и вто-. рым тактовыми входат и устройства, первый вход установки в О первого счетчика адресов и вход установки в О второго счетчика адресов являются соответственно вторым и третьим установочными входами устройства,второй вход установки в О первого счетчика адресов подключен к выходу элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов

И, входы второго элемента И и информационные входы второй группы компаратора соответственно объединены и подключены к выходам второго блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1987 |

|

SU1501163A1 |

| Ассоциативное запоминающее устройство | 1988 |

|

SU1587586A1 |

| Ассоциативное запоминающее устройство | 1987 |

|

SU1501164A1 |

| Устройство для сбора статистических данных о работе программ ЭВМ | 1987 |

|

SU1471202A1 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| ИНФОРМАЦИОННО-СПРАВОЧНАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2003 |

|

RU2246756C1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЙ ПО ИХ КОНТУРАМ | 1992 |

|

RU2060551C1 |

| Устройство для сопряжения электрон-НыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809145A1 |

Изобретение относится к вычислительной технике и может найти применение для распознавания и синтеза сигналов, в частности речевых, и поиска справочной информадаи. Цель изобретения - расширение применения устройства за счет обеспечения вывода из устройства информационньк последовательностей, являющихся результатом сравнения признаковых последовательностей произвольной длины. Поступающая на вход устройства признаковая последовательность записывается в блок 1 памяти.В компараторе 5 проводится сравнение признаковых последовательностей, считываемых из блоков 1 и 2 памяти, по поступлению импульсов сравнения с элемента И 9. Работа триггеров 10 и 11 на этапе сравнения обеспечивает разрешение и запрет выработки импульсов сравнения элементом И 9 и выработку разрешающего сигнала элементом И 8 для вьздачи искомой информационной 5 последовательности на выходы устройства . Помимо указанных элементов устройство содержит счетчики 3 и 4 адресов, элементы И 6, 7, элемент ШШ 12 и группу элементов И 13, 3 ил. |аяжо

ковой последовательности А|, записанной в блок 1, с признаковыми последовательностями в блоке 2 и выдачи из блока 2 соответствующей информационной последовательности В- заканчиваются.

На этом процессы сравнения призна- 45 памяти, отличающееся тем,

что, с целью расширения области применения устройства за счет вьшода из устройства информационных последова- тельностей, являющихся результатом 50 сравнения признаковых последовательностей произвольной длины, в него введены второй триггер и группа элеФормула изобретенияментов И, первые входы которых подключены к выходам второго блока памяАссоциативное запоминающее устрой- g ти, вторые входы элементов И группы ство, содержащее первый и второй бло- соединены с выходом третьего элемен- ки памяти, кo mapaтop, первый и вто- та И, выходы элементов И группы яв- рой счетчики адресов, первьй триггер, ляются информационными выходами уст- с первого по четвертый элементы И,ройства, вход установки в О и вход

синхронизагрга второго триггера подключены соответственно к первому установочному входу устройства и выходу второго элемента И, прямой вы- :ход второго триггерн соединен с вторым входом третьего элемента И и |входом синхронизации первого тригге- ipa, выход которого подклктчен к перai

CLi

а

us индзор- 1

sX - Код нонца т

2

вому входу четвертого элемента И,второй и третий входы которого пощшюче- ны соответственно к инверсному выходу второго триггера и к второму тактовому входу устройства, выход четвертого элемента И соединен с управляющим входом компаратора.

dfi

Сиг

Sn

0.41

S if

t/7

SN

5 Размещение иншор- мации в o/fof c 2

вмдт

pjn nn unmpnn

Ъыкод j триггера 11

la (ихл j, nocfleoBOi Hocmu

атем

конца rfocfledoSafrj6J)bHocfrtu

ФагЗ

IP цакп cpajSne- 3 Вы Sod ния (coSnade ue) нас ионмои

последобатеАЬ

ности

| Кохонен Т | |||

| Ассоциативные запоминающие устройства | |||

| - М.: Мир, 1982, с | |||

| Джино-прядильная машина | 1922 |

|

SU173A1 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1174988A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-08—Подача