(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования телевизионного сигнала | 1988 |

|

SU1559409A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Устройство для вычисления порядковых статистик последовательностей из @ - @ -разрядных чисел | 1987 |

|

SU1434424A1 |

| Генератор квазиортогональных сигналов | 1989 |

|

SU1755270A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Генератор систем действительных базисных функций Аристова | 1988 |

|

SU1566334A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Устройство передачи телевизионного сигнала | 1988 |

|

SU1570028A1 |

| Демодулятор взаимоортогональных синусоидальных сигналов с фазоразностной модуляцией | 1985 |

|

SU1277423A1 |

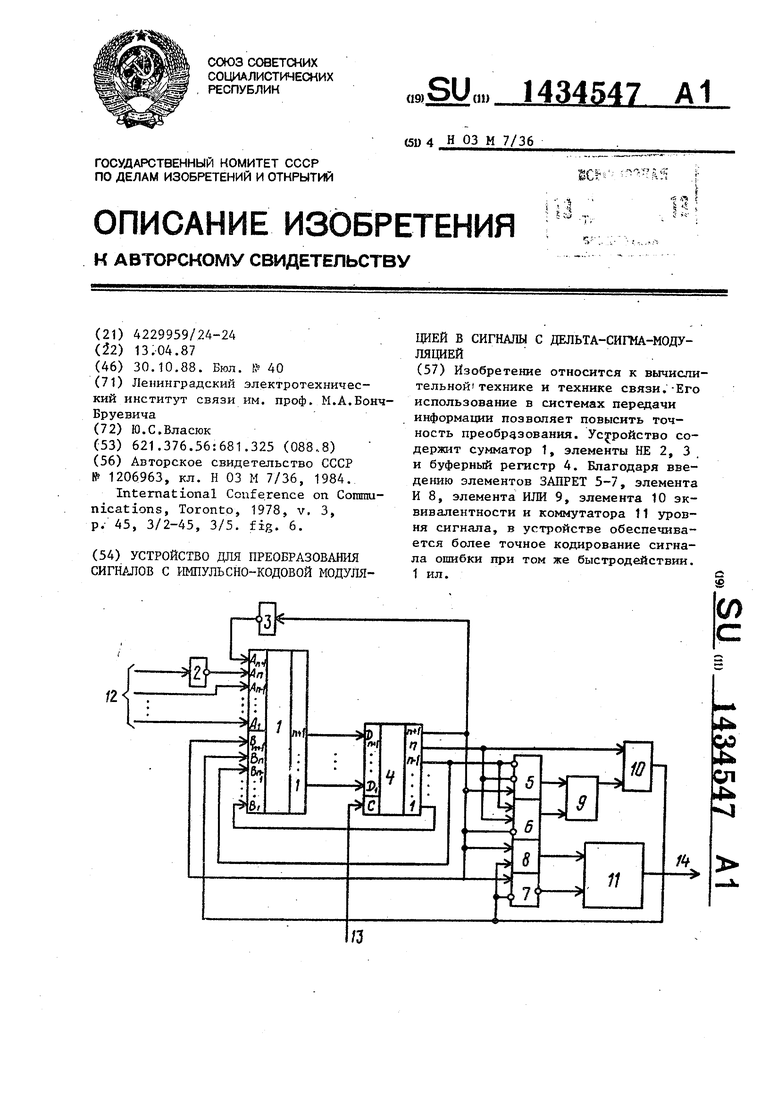

Изобретение относится к вычислительной технике и технике связи,-Его использование в системах передачи информации позволяет повысить точность преобразования. ycji-poftcTBO содержит сумматор 1, элементы НЕ 2, 3 . и буферньй регистр 4. Благодаря введению элементов ЗАПРЕТ 5-7, элемента И 8, элемента ИЛИ 9, элемента 10 эквивалентности и коммутатора 11 уровня сигнала, в устройстве обеспечивается более точное кодирование сигнала ошибки при том же быстродействии. 1 ил. с (О

ел

1U

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи информации.

Цель изобретения - повышение точности преобразования.

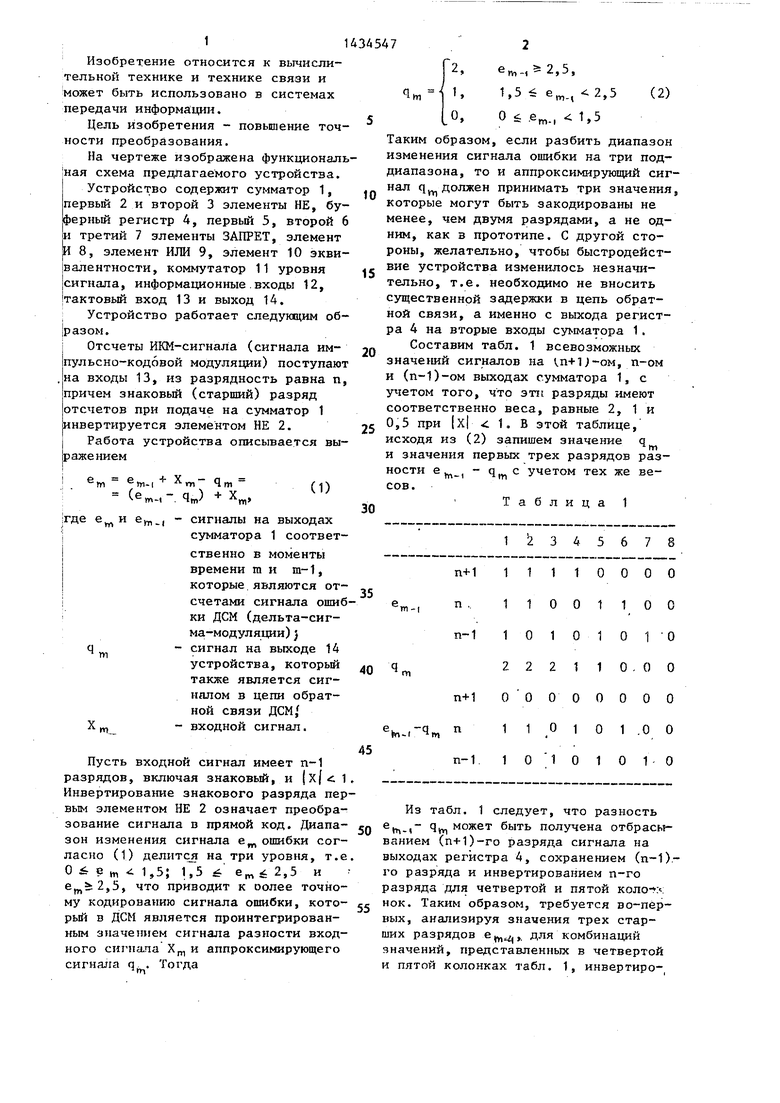

На чертеже изображена функциональ |ная схема предлагаемого устройства. I Устройство содержит сумматор 1, первый 2 и второй 3 элементы НЕ, бу- юерный регистр 4, первый 5, второй 6 и третий 7 элементы ЗАПРЕТ, элемент Р 8, элемент ИЛИ 9, элемент 10 экви- |валентности, коммутатор 11 уровня |сигнапа, информационные.входы 12, |тактовый вход 13 и выход 14. : Устройство работает следующим образом.

j Отсчеты ИКМ-сигнала (сигнала им- |пульсно-кодовой модуляции) поступают .|на входы 13, из разрядность равна п |причем знаковый (старший) разряд отс штов при подаче на сумматор 1 Инвертируется элементом НЕ 2. I Работа устройства описывается вы- |ражением

, +

(е, Чт 4j +Х

(1)

т

де е и е

w-i

X

t

сигналы на выходах сумматора 1 соответственно в моменты времени га и т-1, которые являются отсчетами сигнала ошибки ДСМ (дельта-сигма-модуляции) ) сигнал на выходе 14 устройства, которьй также является сигналом в цепи обратной связи ДСМ, входной сигнал.

Пусть входной сигнал имеет п-1 разрядов, включая знаковьй, и Х| 1, Инвертирование знакового разряда первым элементом НЕ 2 означает преобразование сигнала в прямой код. Диапазон изменения сигнала е„ ошибки согласно (1) делите на три уровня, т.е. О е tt, 1,5; 1,5 е 2,5 и ,5, что приводит к оолее точно50

Из табл. 1 следует, что разность tT,-( Чуп может быть получена отбрасыванием (п-«-1)-го разряда сигнала на выходах регистра 4, сохранением (п-1).- го разряда и инвертированием п-го разряда для четвертой и пятой коло- х

му кодированию сигнала ошибки, кото- нок. Таким образом, требуется во-пёррый в ДСМ является проинтегрированным значением сигнала разности вход X, Тогда

ного сигнала Х и аппроксимирующего

сигнала q.

m

вых, анализируя З1гачения трех старших разрядов е,. для комбинаций значений, представленных в четвертой и пятой колонках табл. 1, инвертирое 9 S i-

1м

1,5 6 е„., 2,5 О 6 .е„., 1,5

(2)

Q 5

5

0

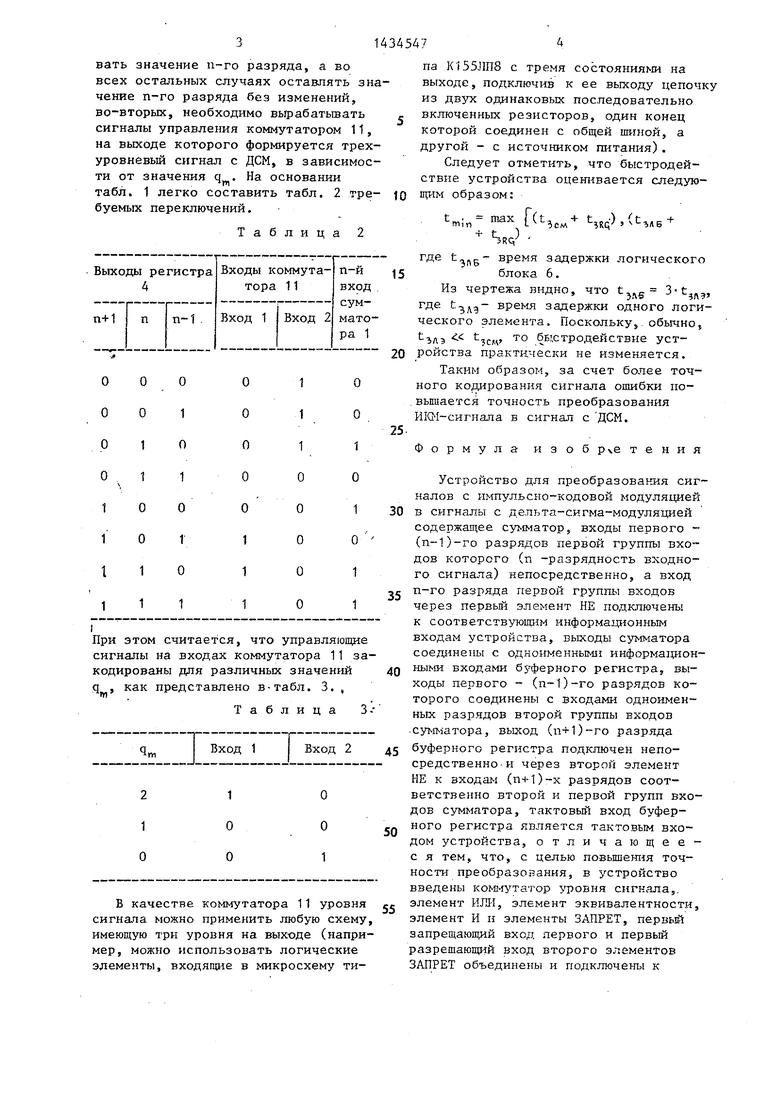

Таким образом, если разбить диапазон изменения сигнала ошибки на три поддиапазона, то и аппроксимирующий сигнал q должен принимать три значения, которые могут быть закодированы не менее, чем двумя разрядами, а не одним, как в прототипе. С другой стороны, желательно, чтобы быстродействие устройства изменилось незначительно, т.е. необходимо не вносить существенной задержки в цепь обратной связи, а именно с выхода регистра 4 на вторые входы сумматора 1. Составим табл. 1 всевозможных значе шй сигналов на .п+и-ом, п-ом и (п-1)-ом выходах сумматора 1, с учетом того, что 3Tit разряды имеют соответственно веса, равные 2, 1 и 0,5 при (х| 1, В этой таблице, исходя из (2) запишем значение q

fv

и значения первых трех разрядов разности е, - q с учетом тех же весов.

Из табл. 1 следует, что разность tT,-( Чуп может быть получена отбрасыванием (п-«-1)-го разряда сигнала на выходах регистра 4, сохранением (п-1).- го разряда и инвертированием п-го разряда для четвертой и пятой коло- х

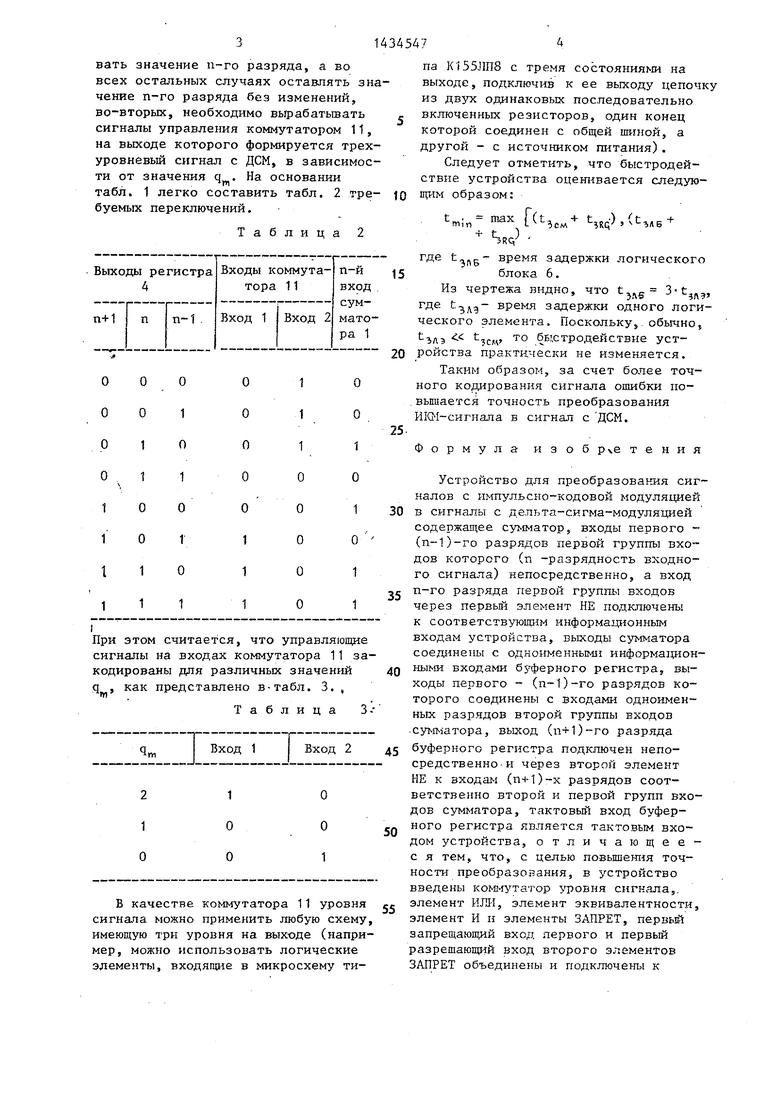

вых, анализируя З1гачения трех старших разрядов е,. для комбинаций значений, представленных в четвертой и пятой колонках табл. 1, инвертировать значение п-го разряда, а во всех остальных случаях оставлять значение п-го разряда без изменений, во-вторых, необходимо вырабатьшать сигналы управления коммутатором 11, на выходе которого формируется трехуровневый сигнал с ДСМ, в зависимости от значения q. На основании табл. 1 легко составить табл. 2 требуемых переключений.

Таблица 2

При этом считается, что управляющие сигналы на входах коммутатора 11 закодированы для различных значений q , как представлено в-табл. 3. ,

W

Таблица 3Вход 1

Вход 2

В качестве коммутатора 11 уровня сигнала можно применить любую схему, имеюп1ую три уровня на выходе (например, можно использовать логические элементы, входящие в микросхему ти0

па К155ЛП8 с тремя состояниями на выходе, подключив к ее выходу цепочку из двзтс одинаковых последовательно включенных резисторов, один конец которой соединен с общей шиной, а другой - с источником питания).

Следует отметить, что быстродействие устройства оценивается следующим образом:

f(. s,,.

где t,g- время задержки логического

блока 6.

Из чертежа видно, что С, , где время задержки одного логического элемента. Поскольку,. обьтно.

tmin

Эсм

;),(t

АБ

20

0

5

0

5

0

5

-злэ

« t

ТО бБг.стр о действие уст5

ройства практически не изменяется.

Таким образом, за счет более точного кодарования сигнала ошибки по- .вышается точность преобразования И1Ш-сигнала в сигнал с ДСМ.

Формула изобр етения

Устройство для преобразования сигналов с импульсно-кодовой модуляцией в сигналы с дельта-сигма-модуляцией содержащее сумматор, входы первого - (п-1)-го разрядов первой группы входов которого (п -разрядность входного сигнала) непосредственно, а вход п-го разряда первой группы входов через первьпЧ элемент НЕ подключены к соответствующим информационным входам устройства, выходы сумматора соединены с однонменнымл информационными входами буферного регистра, выходы первого - (n-l)-ro разрядов которого соединены с входами одноименных разрядов второй группы входов сумматора, выход (п+1)-го разряда буферного регистра подключен непосредственно- и через второй элемент НЕ к входам (п+1)-х разрядов соответственно второй и первой групп входов сумматора, тактовый вход буферного регистра является тактовым входом устройства, отличающее- с я тем, что, с целью повышенн я точности преобразования, в устройство введены ком.1утатор уровня сигнала,, элемент ИЛ1-1, элемент эквивалентности, элемент И и элементы ЗАПРЕТ, первый запрещающий вход первого и первый разрешающий вход второго элементов ЗАПРЕТ объединены и подключены к

5 14345476

в|ыходу (n-l)-ro разряда буферного ре-мента И и запрещакщему входу третье- rJHCTpa, выход п-го разряда которогого элемента ЗАПРЕТ, второй вход эле- фединен с первым входом элементамента И, разрешанщие входы первого Э|квивалентности, вторым запрещакяцим и третьего и запрещающий вход второ- 4ходом первого и вторым разрешающимго элементов ЗАПРЕТ объединены и под- входом второго элементов ЗАПРЕТ, вы-ключены к выходу (п+1)-го разряда бу- йоды которых соединены с входами эле-ферного регистра, выход элемента И и Цента ИЛИ, выход которого соединенинверсный выход третьего элемента Q вторым входом элемента эквивалент- ЗАПРЕТ соединены соответственно с юсти, выход которого подключен кпервым и вторым входами коммутатора 1ХОДУ п-го разряда второй группыуровня сигнала, вьщрд которого явля- ходов сумматора, первому входу эле-ется выходом устройства.

| Устройство цифрового преобразования сигналов импульсно-кодовой модуляцией в сигналы с дельта-сигма модуляцией | 1984 |

|

SU1206963A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| International Conference on Conmiu- nications, Toronto, 1978, v, 3, p.- 45, 3/2-45, 3/5 | |||

| fig | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-30—Публикация

1987-04-13—Подача