вого слагаемого сумматора, выходы суммы которого подключены соответственно к инфОЕ 4ац онным входам триггеров, выходы кототрых являются выходом блока, выход переноса сумматора соединен с информационным входом (k+l)-ro триггера,выход которого соединен с входом младшего разряда второго слагаемого сумматора, входы установки в нуль триггеров с первого по й-й ,и вход установки в единицу (k+D-ro триггера подключены к третьему входу блока.

3. Устройствб по п. 1, отличающееся тем, что коммутатор

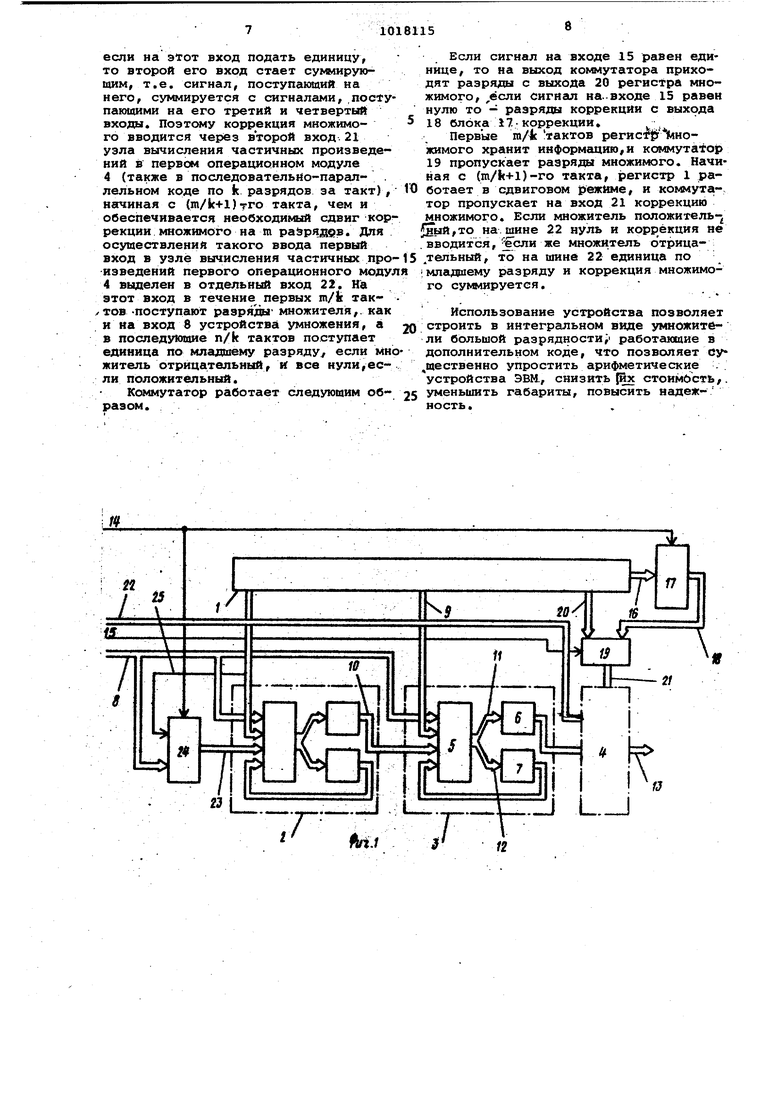

содержит 1с элементов И, k элементов , -ЗАПРЕТА и k элементов ИЛИ, причем информационные входы элементов ЗАПРЕТА соединены с первым информационным входом коммутатора, первые входы элементов И соединены с вторым информационным входом коммутатсфа, вторые входы элементов И и управляющие входы элементов ЗАПРЕТА соединены с управляющим входом коммутатора, выходы i-x элемента И и элемента ЗАПРЕТА соединены соответственно с первым и вторым входами i-ro элемента ИЛИ,выходы которых являются выходами коммутатора (),

| название | год | авторы | номер документа |

|---|---|---|---|

| Отказоустойчивое устройство для умножения чисел | 1990 |

|

SU1777134A1 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

1. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее п-раэрядный сдвиговый регистр первого сомножителя, n/k операционных модулей (kaSn/2), каждый из которых содержит узел вычисления частичных произведений, первый и второй б,ферные регистры, причем в 1-м onepeiuHOHHOM модуле (,...n/k) первый, второй, -третий и четвертый входы узла вычисления частичных произведений соединены соответственно с входом k разрядов второго сомножителя устройства, с шиной значений соотЬетствующих 4с разрядов регистра первого сомножителя с выходом первого буферного регистра (i+l)-ro операционного модуля и с выходом второго буферного регистра i-ro операционного модуля, вход которого соединен с выходом значения k ста1яиих разрядов результата узла выч11сления частичных произведений, вход первого буферного регистра соединен с выходом значения k младших разрядов результата узла вычисления астичных произведений, причем в первом операционном модуле третий и четвертый входы узла вычисления частичных произведений соединены соот ветственно с выходом первого буферного регистра второго операционного модуля и с выходом ВТОРОГО буферного регистра первогЬ операционного модуля, выход первого буферного регистра первого операционного модуля является выходом устройства, о тл и чающее с я тем, что, с целью расширения области применения устройства за счет работы с числами, представленными в дополнительном коде, устройство содержит два блока коррекции, коммутатор, причем после- довательный выход регистра первого сомножителя соединен с первым входе Первого блока коррекции, выход которого соединен с первым информационным входом коммутатора, второй информационный вход которого соеди|нен с цщной значений k младших разурядов регистра первого сомножителя, управляюптй вход коммутатора сое(Л динен с входом разрешения ввода коррекции устройства, а выход соедис нен с вторым входом узла вычисления ;частичных произведений первого опе-рационного модуля, первый вход узла вычисления частичных произведений первого операционного модуля соединей с входом знака второго сомножителя устройства, третий вход узла вычисления частичные; произведений n/k-ro операционного модуля соединен с выходом второго блока коррек00 ции, первый и второй входы которого соединены соответственно с шиной значения стаЕЯиего разряда регистра первого сомножителя и с входом k сл разрядов второго сомножителя устройства, третьи входы первого и второго блоков коррекции соединены с входст начальной установки устройства 2, Устройство по п. If о т л ич а ю U е е с я тем, что блок коррекции содержит k-разрядный сумматор, k элементов И,(k+1) триггеров, причем;первые входы элементов И со- единены с первым входом блока, вторые их входа соединены с вторым вхо- р дом блока, а инверсные выходы подключены соответственно к входам пер

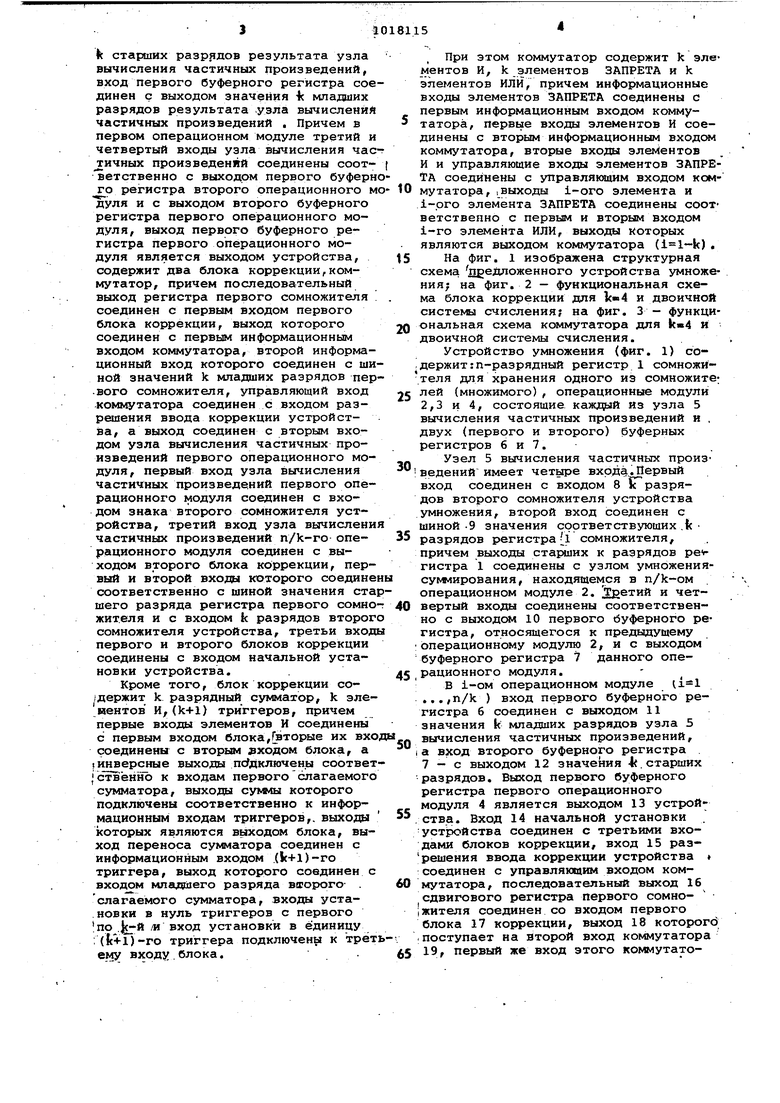

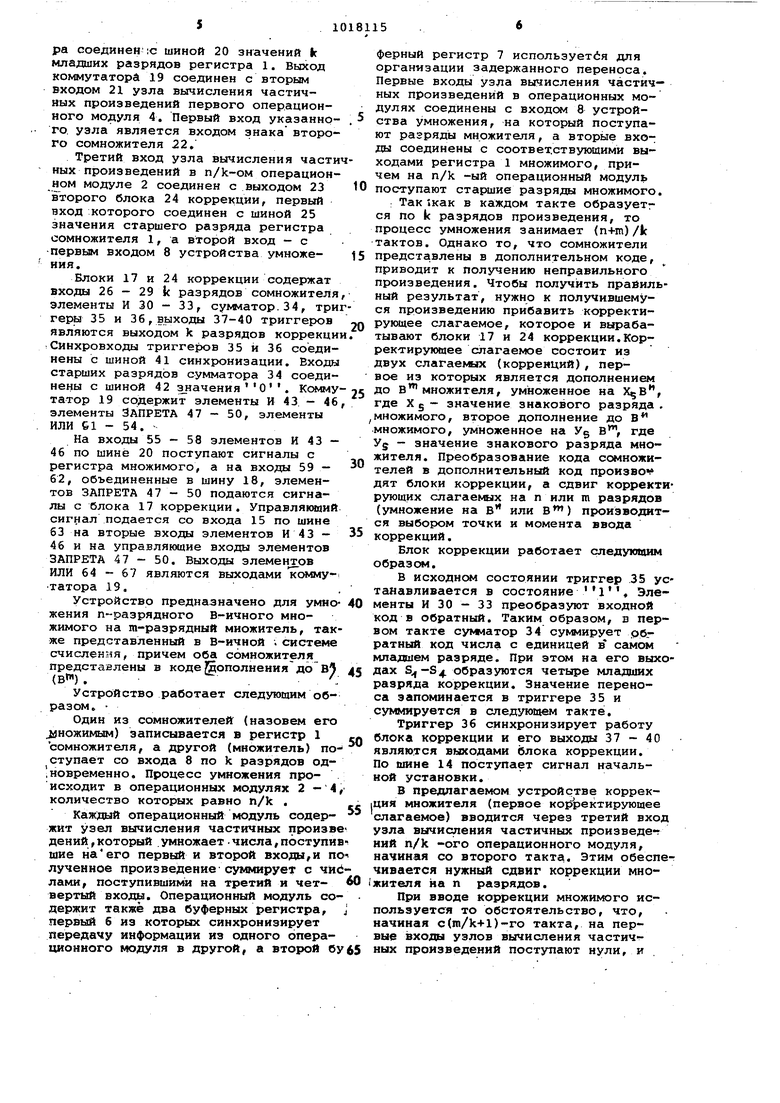

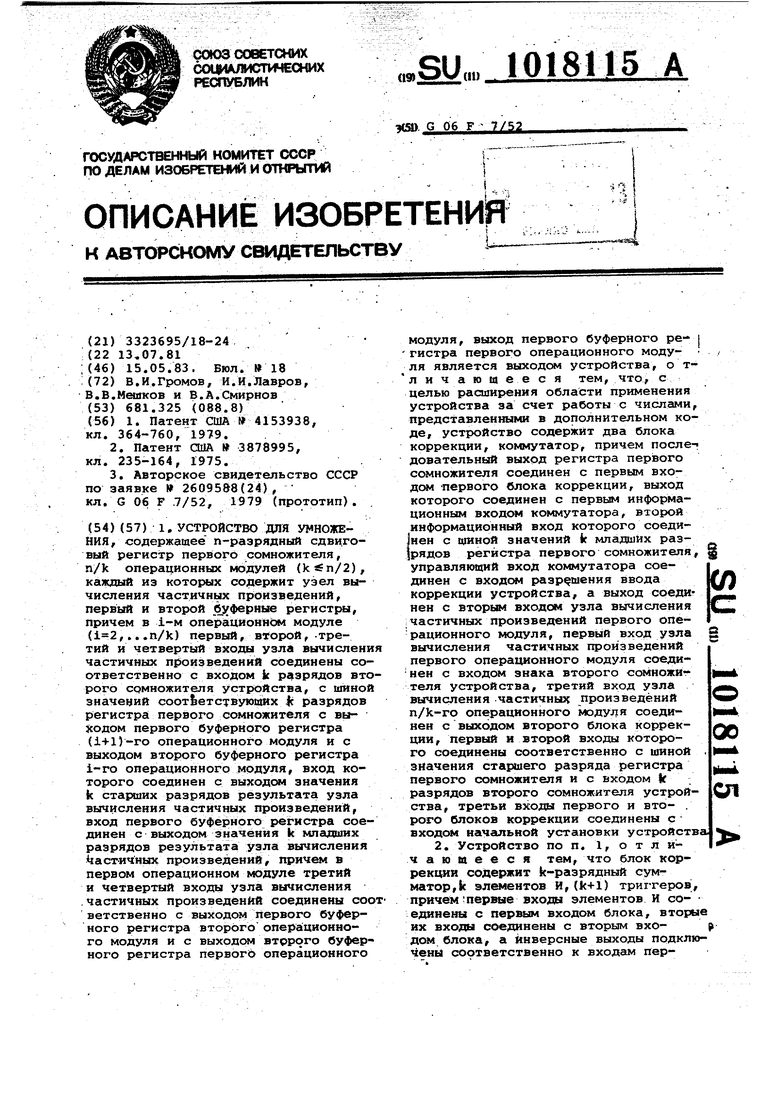

Изобретение относится к вычислительной технике и микроэлектронике, предназначено для умножения чисел, представленных как в прямом, так и в дополнительном, и может быть ис:польэовано в.ЭВК, в системах обра|ботки информэ ии, в цифровой фильтрации. Известен умножитель параллельного типа, содержащий дешифратор, мультиплексор, сумматоры с задержанным и ускоренным переносом. В умножителе ио пользуется модифицированный алгоритм Бута с анализом по I разрядов множите . Умножители подобного типа имеют высокое быстродействие,но чрезвычайно громоздки и при изготовлении их в интегральном виде не могут умножать чис ла большой разрядности. Известен также умножитель последовательно-параллельного типа,содержащий, вентильные схемл, сумматоры по модулю два, триггеры 2 Указанные умножители при изготовле НИИ их в виде интегральной микросхемы могут умножать двоичные числа большой разрядности, но они имеют невысокое быстродействие, связанное со значительными затратами времени на запись и считывание информации в триг герах. Наиболее близким к изобретению по технической сущности является устройство для умножения, содержащее п-раэрядный регистр первого, сомножителя, n/k операционных модулей (), каждый из которых содержит узел вычисления частичных произведений, nepвый и второй буферные регистры,причем в 1-ом операционном модулeCi l«M .,..n/k), первый, второй, третий и четвертый входы узла вычисления частичных произведений соединены соответственно с входом k разрядов второго сомножителя устройства, с шиной значений соответствующих k разрядов регистра первог.о сомножителя, с выходом первого буферного регистра (i+l)-oro операционного модуля и с выходом второго буферного регистра i-ro операционного модуля, вход которого соединен с выходом значения k старших разрядов результата узла вычисления частичных произведений, вход, первого буферного регистра соединен с выходом значений k младших разрядов результата узла вьгаисления частичных произведений, выход первого буферного регистра первого операционного модуля является выходом устройства Недостатком прототипа является невозможность его работы с числами,представленными в дополнительном коде. Цель изобретения - обеспечение работы умножителя с числгиии, представленными в дополнительном коде, что позволит расширить область его применения. Поставленная цель достигается тем, что устройство для умножения, содердащее п-разрядный сдвиговый регистр ( Т ервого сомножителя,n/k операционные .модули (), каждый из которых содержит узел вычисления частичных произведений первый и второй буферные регистры, причем в i-ом операционном модуле (...n/k), первый, второй,третий и четвертый входы узла вычисления частичных произведений соединены соответственно с входом k разрядов второго сомножителя устройства с шиной значения соответствующих }( . разрядов регистра первого сомножителя, с выходе первого буферного регистра (1+1).-го операционного модуля и с выходом второго буферного регистра i-ro операционного модуля, вход которого соединен с выходом значения fe старших разрядов результата узла вычисления частичных произведений, вход первого буферного регистра сое динен с выходом значения -k младших разрядов результата .узла вычислений частичных произведений . Причем в первом операционном модуле третий и четвертый входы узла вычисления час ичных произведений соединены соот ветственно с выходом первого буфер го регистра второго операционного м дуля и с выходом второго буферного регистра первого операционного модуля, выход первого буферного регистра первого операционного модуля является выходом устройства, содержит два блока коррекции,коммутатор, причем последовательный выход регистра первого сомножителя соединен с первым входом первого блока коррекции, выход которого соединен с первым информационньли входом коммутатора, второй информационный вход которого соединен с ши ной значений k младших разрядов пер вого сомножителя, управляющий вход коммутатора соединен с входом разрешения ввода коррекции устройства, а выход соединен с вторым входом узла вычисления частичных произведений первого операционного модуля, первый вход узла вычисления частичных произведений первого операционного модуля соединен с входом знака второго сомножителя устройства, третий вход узла вычислени частичных произведений n/k-ro операционного модуля соединен с выходом второго блока коррекции, первый и второй входы которого соедине соответственно с шиной значения ста шего разряда регистра первого сомно жителя и с входом k разрядов второг сомножителя устройства, третьи вход первого и второго блоков коррекции соединены с входом начальной установки устройства. Кроме того, блок коррекции со/держит k разрядный сумматор, k эленентов Kf (k+1) триггеров, причем первые входы элементов И соединены с первым входом блока,(вторые их вхо соединены с вторым зходом блока, а инверсные выходы подключены соответ ствённо к входам первого слагаемого сумматора, выходы суммы которого подключены соответственно к информационным входам триггеров,, выходы которых являются выходом блока, выход переноса сумматора соединен с информационным входом .(Ь+1)го триггера, выход которого соединен с входом млал 11его разряда ВЕСорого- . слагаемого сумматора, входы установки в нуль триггеров с первого по .й /и вход установки в единицу ; (Ic+D-ro триггера подключены к трёт ему входу.блока.. При этом коммутатор содержит k элементов И, k элементов ЗАПРЕТА и k элементов ИЛИ, причем информационные входы элементов ЗАПРЕТА соединены с первым информационным входом коммутатора, первые входы элементов И соединены с вторым информационным входом коммутатора, входы элементов И и управляющие входа элементов ЗАПРЕТА соединены с управлякяцим входом коммутатора, .выходы i-oro элемента и i-pro элемента ЗАПРЕТА соединены соответственно с первым и вторым входом i-ro элемента ИЛИ, выходы которых являются выходом коммутатора (). На фиг. 1 изображена структурная схема п едложенного устройства умножения; на фиг. 2 - функциональная схема блока коррекции для и двоичной систеьФл счисления; на фиг. 3 - функциональная схема коммутатора для km4 И двоичной системы счисления. Устройство умножения (фиг. 1) содержит:п-разрядный регистр 1 сомножителя для хранения одного из сомножите; лей (множимого), операционные модули 2,3 и 4, состоящие, каждый из узла 5 вычисления частичных произведений и , двух (первого и второго) буферных регистров 6 и 7. Узел 5 вычисления частичных произведений имеет четьире входа.Первый вход соединен с входом 8 к разрядов второго сомножителя устройства умножения, второй вход соединен с шиной -9 значения соответствующих ,{с разрядов регистра (i сомножителя, причем выходы старших к разрядов ре-г гистра 1 соединены с узлом умножениясулфлирования, находящемся в n/k-ом операционном модуле 2. третий и четвертый входы соединены соответственно с выходом 10 первого буферного регистра, относящегося к предыдущему операционному модулю 2, и с выходом буферного регистра 7 данного операционного модуля. В i-oM операционном модуле li-1 ...,n/k ) вход первого буферного регистра б соединен с выходом 11 значения k младших разрядов узла 5 вычисления частичных произведений, а вход второго буферного регистра . 7 - с выходом 12 значения 4{. старших разрядов. Выход первого буферного регистра первого операционного модуля 4 является выходом 13 устройства. Вход 14 начальной установки . устройства соединен с третьими входами блоков коррекции, вход 15 разрешения ввода коррекции устройства соединен с управляющим входом коммутатора, последовательный выход 16 сдвигового регистра первого сомножителя соединен со входом первого блока 17 коррекции, выход 18 которого поступает на Второй вход коммутатора 19, первый же вход этого коммутатоpa соединен-;c шиной 20 значений k младших разрядов регистра 1. Выход коммутатора 19 соединен с вторым входом 21 узла вычисления частичных произведений первого операционного модуля 4. Первый вход указанного узла является входом знака второго сомножителя 22,

Третий вход узла вычисления частичных произведений в n/k-oM операционном модуле 2 соединен с выходом 23 второго блока 24 коррекции, первый вход которого соединен с шиной 25 значения старшего разряда регистра сомножителя 1, а второй вход - с первым входом 8 устройства умножения.

Блоки 17 и 24 коррекции содержат входы 26 - 29 k разрядов сомножителя, элементы И 30 - 33, сумматор.34, триггера 35 и 36,выходы 37-40 триггеров являются выходом k разрядов коррекции Синхровходы триггеров 35 и 36 соединены с шиной 41 синхронизации. Входы старших разрядов сумматора 34 соединены с шиной 42 значения О. Коммутатор 19 содержит элементы И 43 - 46, элементы ЗАПРЕТА 47 - 50, элементы ИЛИ 61-54.

На входы 55-58 элементов И 43 - 46 по шине 20 поступают сигналы с регистра множимого, а на входы 59 - 62, объединенные в шину 18, элементов ЗАПРЕТА 47 - 50 Подаются сигналы с блока 17 коррекции. Управляющий сигнал подается со входа 15 по шине 63 на вторые входы элементов И 43 46 и на управляющие входы элементов ЗАПРЕТА 47 - 50. Выходы элементов ИЛИ 64 - 67 являются выходами коммутатора 19.

Устройство предназначено для умножения п-разрядного В-нчного множимого на т-разрядный множитель, также представленный в В-ичной . системе счисления, причем оба сомножителя представлены в кодейополнення до В

(.. V:

Устройство работает следующим образом.

Один из сомножителей (назовем его |9ножимым) записывается в регистр 1 сомножителя, а другой (множитель) поступает со входа 8 по k разрядов од новременно. Процесс умножения происходит в операционных модулях 2 -4, количество которых равно n/k ,

Каж;цый операционный модуль содержИт узел вычисления частичных произведений , который . умножает числа, поступившие наего первый и второй входной по лученное произведение суммирует с чйЬлами, поступившикм на третий и четвертый входы. Операционный модуль содержит также два буферных регистра, первый б из которых синхронизирует передачу информации из одного операционного модуля в другой, а второй бу

ферный регистр 7 используется для организации задержанного переноса. Первые входы узла вычисления частичных произведений в операционных модулях соединены с входом 8 устройства умножения, на который поступают разряды множителя, а вторые входы соединены с соответствующими выходами регистра 1 множимого, причем на n/k -ый операционный модуль поступают старшие разряды множимого. ; Так «как в каждом такте образуетг ся по k разрядов произведения, то процесс умножения занимает (n+in)/k тактов. Однако то, что сомножители представлены в дополнительном коде, приводит к получению неправильного произведения. Чтобы получить правильный результат нужно к получившемуся произведению прибавить корректирующее слагаемое, которое и вырабатывают блоки 17 и 24 коррекции.Корректирующее слагаемое состоит из двух слагаемых (коррекций), первое из которых является дополнением до В множителя, умноженное на , где X 5 значение знакового разряда , множимого, второе дополнение до В МНОЖИМОГО, умноженное на Уд В, где УЗ - значение знакового разряда множителя. Преобразование кода сомножителей в дополнительный код произво дят блоки коррекции, а сдвиг корректрующих слагаемых на п или m разрядов (умножение на в или В) производится выбором точки и момента ввода коррекций.

Блок коррекции работает следующим образом.

В исходном состоянии триггер 35 утанавливается в состояние , Элементы И 30 - 33 преобразуют входной код в обратный. Таким образом, в первом такте cyt iaTop 34 суммирует рб.ратный код числа с единицей в сгибом младшем разряде. При этом на его выхдах S -84. образуются четыре младших разряда коррекции. Значение переноса запоминается в триггере 35 и суммируется в следующем такта.

Триггер 36 синхронизирует работу блока коррекции и его выходы 37-40 являются выходами блока коррекции. По шине 14 поступает сигнал начальной установки.

В предлагаемом устройстве коррек|ция множителя (первое корректирующее слагаемое) вводится через третий вхо узла вычисления частичных произведет НИИ n/k -ого операционного модуля, начиная со второго такта. Этим обеспчивается нужный сдвиг коррекции мно1жителя на п разрядов.

При вводе коррекции множимого используется то обстоятельство, что, начиная c(m/k+l)-ro такта, на первые входы узлов вычисления частичных произведений поступают нули, и если на этот вход подать единицу, то второй его вход стает суммирующим, т.е. сигнал, поступаюший на него, суммируется с сигналами,,посту паюишми на его третий и четвертый входы. ПОЭТСЛ1У коррекция множимого вводится через второй вход.21 узла вычисления частичных произведений в первом операционном модуле 4 (также в последовательйо-парал- . лельиом коде по k разрядов за такт), начиная с {m/k-H)Tro такта, чем и обеспечивается необходимый сдвиг кор рекции множимого на m ра ряярв. Для осуществления такого ввода первый вход в узле вычисления частичных про изведений первого операционного моду 4 выделен в отдельный вход 22. На этот вход в течение первых m/k таку тон -поступают разряды множителя,, как и на вход 8 устройства умножения, а в последующие n/k тактов поступает единица по младшему разряду если мн житель отрицательный, и все нули,если положительный. Коммутатор работает следующим образом. Если сигнал на входе 15 равен единице, то на выход коммутатора приходят разряды с выхода 20 регистра множимого, ,если сигнал на.-входе 15 равен нулю то- разряды коррекции с выхода 18блока 17-коррекции. Первые т/4с тактов регистру Тйножимого хранит информгщию,и коммутато|) 19пропускает разряды множимого. Начиная с (m/k+l)-ro такта, регистр 1 работает в сдвиговом )режиме, и коммутатор пропускает на вход 21 коррекцию множимого. Если множитель положительлый,то на. шине 22 нуль и корр ёкция не вводится,;«сли же множитель отрицательный, то на шине 22 единица по млащщему разряду и коррекция множимого суммируется. Использование устройства позволяет строить в интегральном виде умножители большой разрядностиJI работающие в дополнительном коде, что позволяет су щественно упростить арифметические устройства ЭВМ., снизить рйх стоимость,, уменьшить габариты, повысить надежность..

27

J7

Зв

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США №4153938, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-15—Публикация

1981-07-13—Подача