Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля интегральных схем.

Цель изобретения - расширение функциональных возможностей устройства за счет автоматического определения типа контролируемых интегральных схем.

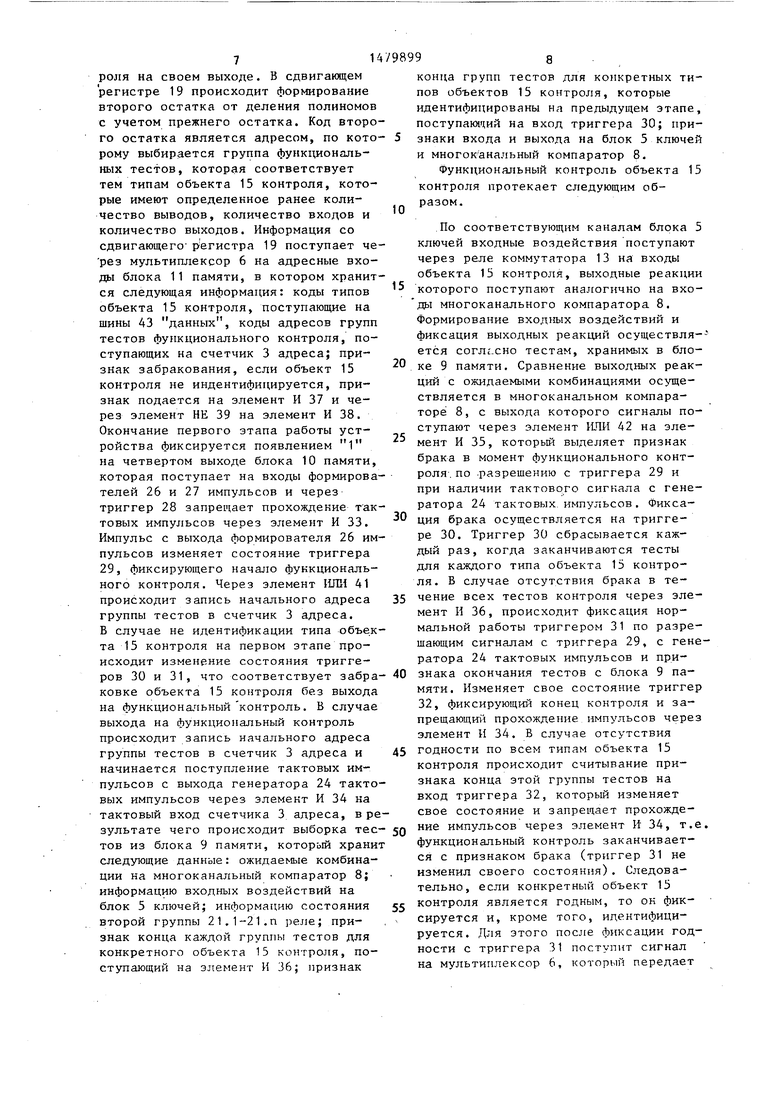

На чертеже представлена функциональная схема предлагаемого устройства.

На чертеже изображены программируемый генератор 1 тока, программируемый источник 2 напряжения, первый 3, второй 4 счетчики адреса, блок 5 ключей, мультиплексор 6, измеритель 7, многоканальный компаратор 8, первый 9, второй 10, третий 11 блоки памяти, блок 12 сжатия информации, коммутатор 13, блок 14 управления, объект 15 контроля, формирователь 16 импульсов, источник 17 опорного напряжения. Блок 12 сжатия информации содержит полусумматор 18, сдвигающий регистр 19. Коммутатор 13 содержит первую 20.1-20.ri, вторую 21.1-21.П группы реле, общую шину 22. Блок 14 управления содержит блок 23 индикации, генератор 24 тактовых импульсов, первый 25, второй 26, третий 27 формирователи импульсов, первый 28, второй 29, третий 30, четвертый 31, пятый 32 триггеры, пер- вый 33, второй 341-, третий 35, четвертый 36, пятый 37, шестой 38 элементы И, элемент НЕ 39, шину 40 Пуск, первый 41, второй 42 элементы ИЛИ, шины 43 данных. Первые, вторые вы- ходы блока 14 управления соединены соответственно с первым, вторым входами счетчика 3 адреса, выходы которого соединены с соответствующими входами блока 9 памяти и с соответствующими первыми входами мультиплексора 6, выходы которого соединены с соответствующими входами блока 11 памяти, первые выходы которого соединены с соответствующими третьими входами счетчика 3 адреса, вторые выходы - с соответствующими первыми входами блока 14 управления, а третий выход - с вторым входом блока 14 управления, третий выход которого соединен с пеР вым входом счетчика 4 адреса и через формирователь 16 импульсов - с первым входом блока 12 сжатия информации выходы которого соединены с соответ0

5

0

5

0 5 0 5 Q

ствующими вторыми входами мультиплексора 6, третий вход которого соединен с четвертым выходом блока 14 управления, пятый выход которого соединен с вторыми входами блока 12 сжатия информации и счетчика 4 адреса, выходы которого соединены с соответствующими входами блока 10 памяти, первые выходы которого соединены с соответствующими первыми входами коммутатора 13, первый вывод которого соединен с первым выходом программируемого источника 2 напряжения, входы которого соединены с соответствующими вторыми выходами блока 10 памяти, третьи выходы которого соединены с соответствующими входами программируемого генератора 1 тока, выход которого соединен с первым входом измери- ателя 7 и с вторым выводом коммутатора 13, третьи выводы которого соединены с соответствующими выходами блока 5 ключей и с соответствующими первыми входами многоканального компаратора 8, выходы которого соединены с соответствующими третьими входами блока 14 управления, четвертый вход которого соединен с четвертым выходом блока 10 памяти, второй выход программируемого источника 2 напряжения соединен с вторым входом измерителя 7, выход которого соединен с третьим входом блока 12 сжатия информации, пятый, шестой, седьмой, восьмой входы блока 14 управления соединены соответственно с первым, вторым, третьим, четвертым выходами блока 9 памяти, пятые выходы которого соединены с соответствующими вторыми входами коммутатора 13, четвертые выводы которого соединены с соответствующими выводами объекта 15 контроля, шестые выходы блока 9 памяти соединены с соответствующими первыми входами блока 5 ключей и с соответствующими BTO-I рыми входами многоканального компаратора 8, третьи входы которого соединены с соответствующими седьмыми выходами блока 9 памяти и с соответствующими вторыми входами блока 5 ключей, третий и четвертый входы которого соединены соответственно с первым и вторым выходами источника 17 опорного напряжения, третий, четвертый выходы которого соединены соответственно с третьим и четвертым входами блока 5 ключей.

3147

Первый, второй входы блока 12 сжатия информации соединены соответственно с первым, вторым входами адвит тающего регистра 19, выходы которого соединены с соответствующими первыми входами полусумматора 18 и с соответствующими выходами блока 12 сжатия информации, информационный вход которого соединен с вторым входом полусумматора 18, выход которого соединен с информационным входом сдвигающего регистра 19. Первый вывод коммутатора 13 соединен с первыми кон

ход которого соединен с первым входов элемента И ЗЬ, второй вход которого «соединен с. вторым входом элемента И 35 и с первым выходом генератора 4 тактовых импульсов, второй выход которого соединен с первым входом элемента И 33, второй вход которого соединен с первым входом элемента И 33, втпрой вход которого соединен с вторым выходом триггера 28, а выход - с третьим выходом блока 14 управления, четвертый вход которого соединен с вторым входом триггера 24, с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Устройство параметрического контроля интегральных схем | 1985 |

|

SU1287060A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля электрических цепей | 1985 |

|

SU1270729A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля интегральных схем (ИС). Цель изобретения - расширение функциональных возможностей устройства - достигается путем автоматического определения типа контролируемых ИС. Устройство содержит программируемые генератор 1 тока и источник 2 напряжения, счетчики 3, 4 адреса, блок 5 ключей, мультиплексор 6, измеритель 7, многоканальный компаратор 8, блоки 9-11 памяти, блок 12 сжатия информации, коммутатор 13, блок 14 управления, объект 15 контроля ИС, формирователь 16 импульсов, источник 17 опорного напряжения. Устройство идентифицирует тип объекта 15 контроля при фиксации его годности по счетчику 3 адресов, хранимых в блоке 9 памяти. Идентификация осуществляется в момент фиксации годности объекта. 3 з.п. ф-лы, 1 ил.

тактами реле группы 20.2-20.п, вторые 15 входом -формирователя 26 импульсов и

через формирователь 27 импульсов с вторыми входами элемента И 38 и элемента И 3/, выход которого соединен с третьим входом триггера 30 и с вто рым входом триггера 31, второй выход которого соединен с первым входом элемента И 34, с вторым входом триггера 32 и с четвертым выходом блока 14 управления, пятый вход которого соединен с вторым входом триггера 29 третий вход которого соединен с выхо дом формирователя 26 импульсов, а второй выход - с третьими входами элементов И 35 и 3b и с вторым входо элемента И 34, третий вход которого соединен с третьим выходом генератора 24 тактовых импульсов, шестой и седьмой входы блока 14 управления соединены соответственно с четвертым входом триггера 30 и с четвертым вхо дом элемента И 36, выход которого со единен с третьим входом триггера 31, восьмой входы блока управления соеди нен с третьим входом триггера 32, второй выход которого соединен с чет вертым входом элемента И 34, шина 40 Пуск соединена с пятым выходом бло ка 14 управления.

контакты которых соединены с соответствующими первыми контактами реле группы 21.1-21.п, вторые контакты которых соединены с общей шиной 22, а третьи - с соответствующими вторыми выводами-коммутатора 13, третьи выводы которого соединены с соответствующими третьими выводами реле группы 20.1-20.П, первый контакт реле группы 20.1. соединен с четвертым выводом коммутатора 13, первые управляющие входы которого соединены с соответствующими управляющими входами реле группы 20.1-20.П, а вторые управляющие входы - с соответствующими управляющими входами реле группы 21.1-21.п. Шина 40 Пуск блока 14 управления соединена с первым входом элемента ИЛИ 41 и через формирователь 25 импульсов - с первыми входами триггеров 28 - 32, первые выходы которых соединены соответственно с первым, вторым, третьим, четвертым, пятым входами блока 23 индикации и соответственно с первым, вторым, третьим, четвертым, пятым выводами шины 43 данных, остальные выводы которой Соединены с соответствующими шестыми

входами блока 23 индикации и с соответствующими первыми входами блока 14 управления, первый выход которого соединен с выходом элемента И 34, а второй вход - с первым в-ходом элемента И 37 и через элемент НЕ 39 - с первым входом элемента И 38, выход которого соединен с вторым входом элемента ИЛИ 41, выход которого соединен с вторым выходом блока 14 управления, третьи входы которого соединены с соответствующими входами элемента ИЛИ 42, выход которого соединен с первым входом элемента И 35, выход которого соединен с вторым входом триггера 30, второй вы

15 входом -формирователя 26 импульсов и

30

2Q 25

35

0

5

0

5

через формирователь 27 импульсов с вторыми входами элемента И 38 и элемента И 3/, выход которого соединен с третьим входом триггера 30 и с вторым входом триггера 31, второй выход которого соединен с первым входом элемента И 34, с вторым входом триггера 32 и с четвертым выходом блока 14 управления, пятый вход которого соединен с вторым входом триггера 29, третий вход которого соединен с выходом формирователя 26 импульсов, а второй выход - с третьими входами элементов И 35 и 3b и с вторым входом элемента И 34, третий вход которого соединен с третьим выходом генератора 24 тактовых импульсов, шестой и седьмой входы блока 14 управления соединены соответственно с четвертым входом триггера 30 и с четвертым входом элемента И 36, выход которого соединен с третьим входом триггера 31, восьмой входы блока управления соединен с третьим входом триггера 32, второй выход которого соединен с четвертым входом элемента И 34, шина 40 Пуск соединена с пятым выходом блока 14 управления.

Устройство работает следующим образом.

Определение типа объект контроля осуществляется в три этапа: нахождение используемых выводов объекта 15 контроля; определение выводов объекта 15 контроля, которые .являются входами; окончательное определение типа объекта 15 контроля по тестам функционирования.

Первый этап осуществляется проверкой наличия проводимости между выводами объекта 15 контроля и подложкой, т.е. аналогично проверке контактирования. При наличии контакта каждого вывода производится его учет с запомкнанием последовательности этих событий. Затем осуществляется определение выводов, которые являются входами. При этом поиск осуществляется на принципе фиксации величины напряжения на выводе при заданном смещении На входах объекта 15 контроля величина падения напряжения полная, а на выходах равна выходному напряжению нуля или единицы, которое ниже напряжения, образовавшегося от смещения на входах. Этот этап необходим для того, чтобы при проведении функционального контроля не возникло ситуации, когда выход подключается на выход устройства контроля, т.е. возможности внесения неисправности в объект 15 контроля. Окончательное определение типа происходит при функциональном контроле, при котором проверка ведется по тестам. Фиксация годности по одной из групп тестов со ответствует определению типа объекта 15 контроля и одновременно годности на функционирование.

В исходном состоянии счетчики 3 и 4 адреса, сдвигающий регистр 19 обнулены, триггеры 28 и 29 запрещают прохождение тактовых импульсов через элементы И 33 и 34 с генератора 24 тактовых импульсов. Кроме того, триггеры 28-31 гасят индикаторы в блоке 23 индикации. Исходное состояние подтверждается сигналом с шины 40 Пуск на счетчики 3 и 4 адреса, сдвигающий регистр 19 и через формирватель 25 импульсов с некоторой за- держкой на триггеры 28 - 31. Триггер 28 разрешает прохождение тактовы импульсов через элемент И 33 на вход счетчика 4 адреса и сдвигающего регистра 19. Счетчик 4 адреса задает нмер теста при контроле наличия выводов объекта 15 контроля на блок 10 памяти, который хранит следующую информацию: состояния первой группы 20.1-20.П реле; коды значений тока программируемого генератора 1 тока; коды напряжений программируемого источника 2 напряжений. .

Ток с программируемого генератора тока через соответствующее реле первой группы 20.1-20.П реле поступает на соответствующий вывод объекта 15 контроля, остальные выводы которого подключаются через остальные реле первой 20.1-20.П и второй 21.1-21.П групп реле к общей шине 22. Величина падения напряжения на выводе объекта

0

5

0

5

15 контроля выделяется на измерителе 7, который фиксирует превышение напряжения на его измерительном входе по отношению к напряжению с программируемого источника 2 напряжения. В случае выделения полного напряжения с программируемого генератора 1 тока на измеритель 7 на выходе измерителя 7 нуль. Эта ситуация соответствует отсутствию входа или выхода у объекта 15 контроля по данному выводу. В случае наличия входа или выхода у объекта 15 контроля по данному выводу возникает ток между выводами его через охранные диоды, т.е. уменьшается величина падения напряжения на входе измерителя 7. Напряжение на входе измерителя 7 становится меньше опорного напряжения с выхода программируемого источника 2 напряжения. На выходе измерителя 7 единица. Выходная информация с измерителя 7 через полусумматор 18 поступает на информационный вход сдвигающего регистра 19, в котором информация запоминается и сдвигается по сигналу через формирователь 16 импульсов, который обеспечивает задержку по отношению к сигналу, поступающему на счетный вход счетчика 4 адреса. В сдвигающем регистре 19 образуется остаток от деления двух полиномов. Один полином - это входная информация на полусумматоре 18, а второй определяется наличием связей с выходов соответствующих разрядов сдвигающего регистра 19 на входы полусумматора 18.

После окончания определения наличия контактов с выводами объекта 15 контроля происходит определение его выходов. В этом случае отличие входа от выхода определяется путем подачи тока противоположного по знаку к предыдущей проверке. В отличие от первой

5 проверки при второй проверке ток протекает через выходной буфер объекта 15 контроля, а через входной буфер ток практически не проходит (сопротивление входа по сравнению с выходом

0 больше во много раз). Отсюда перенапряжение на измерительном входе измерителя 7 соответствует входу объекта 15 контроля либо обрыву (отсутствию контакта). Меньшее значение напряже5 ния на измерительном входе измерителя 7 соответствует выходному буферу. Соответственно при сравнении с опорным напряжением измеритель 7 различает эти группы выводов объекта 15 кокт0

5

0

714

роля на своем выходе. В сдвигающем регистре 19 происходит формирование второго остатка от деления полиномов с учетом прежнего остатка. Код второго остатка является адресом, по которому выбирается группа функциональных тестов, которая соответствует тем типам объекта 15 контроля, которые имеют определенное ранее количество выводов, количество входов и количество выходов. Информация со сдвигающего регистра 19 поступает че- рез мультиплексор 6 на адресные входы блока 11 памяти, в котором хранится следующая информация: коды типов объекта 15 контроля, поступающие на шины 43 данных, коды адресов групп тестов функционального контроля, поступающих на счетчик 3 адреса; признак забракования, если объект 15 контроля не индентифицируется, признак подается на элемент И 37 и через элемент НЕ 39 на элемент И 38. Окончание первого этапа работы устройства фиксируется появлением 1 на четвертом выходе блока 10 памяти, которая поступает на входы формирователей 26 и 27 импульсов и через триггер 28 запрещает прохождение так- товых импульсов через элемент И 33. Импульс с выхода формирователя 26 импульсов изменяет состояние триггера 29, фиксирующего начало функционального контроля. Через элемент ИЛИ 41 происходит запись начального адреса группы тестов в счетчик 3 адреса. Б случае не идентификации типа объекта 15 контроля на первом этапе происходит изменение состояния триггеров 30 и 31, что соответствует эабра- ковке объекта 15 контроля без выхода на функциональный контроль. В случае выхода на функциональный контроль происходит запись начального адреса группы тестов в счетчик 3 адреса и начинается поступление тактовых импульсов с выхода генератора 24 тактовых импульсов через элемент И 34 на тактовый вход счетчика 3 адреса, в результате чего происходит выборка тестов из блока 9 памяти, который хранит следующие данные: ожидаемые комбинации на многоканальный компаратор 8; информацию входных воздействий на блок 5 ключей; информацию состояния второй группы 21.1-21.П реле; признак конца каждой группы тестов для конкретного объекта 15 контроля, поступающий на элемент И 36; признак

9899а

конца групп тестов для конкретных типов объектов 15 контроля, которые идентифицированы на предыдущем этапе, поступающий на вход триггера 30; признаки входа и выхода на блок 5 ключей и многок анальный компаратор 8.

Функциональный контроль объекта 15 контроля протекает следующим образом.

10

5

0

5

0

5

0

5

0

5

По соответствующим каналам блока 5 ключей входные воздействия поступают через реле коммутатора 13 на входы объекта 15 контроля, выходные реакции которого поступают аналогично на вхо- ды многоканального компаратора 8. Формирование входных воздействий и фиксация выходных реакций осуществля-- ется согласно тестам, хранимых в блоке 9 памяти. Сравнение выходных реакций с ожидаемыми комбинациями осуществляется в многоканальном компараторе 8, с выхода которого сигналы поступают через элемент ИЛИ 42 на элемент И 35, который выделяет признак брака в момент функционального контроля, по .разрешению с триггера 29 и при наличии тактового сигнала с генератора 24 тактовых импульсов. Фиксация брака осуществляется на триггере 30. Триггер 30 сбрасывается каждый раз, когда заканчиваются тесты для каждого типа объекта 15 контроля. В случае отсутствия брака в течение всех тестов контроля через элемент И 36, происходит фиксация нормальной работы триггером 31 по разрешающим сигналам с триггера 29, с генератора 24 тактовых импульсов и признака окончания тестов с блока 9 памяти. Изменяет свое состояние триггер 32, фиксирующий конец контроля и запрещающий прохождение импульсов через элемент И 34. В случае отсутствия годности по всем типам объекта 15 контроля происходит считывание признака конца этой группы тестов на вход триггера 32, который изменяет свое состояние и запрещает прохождение импульсов через элемент И 34, т.е. функциональный контроль заканчивается с признаком брака (триггер 31 не изменил своего состояния). Следовательно, если конкретный объект 15 контроля является годным, то он фиксируется и, кроме того, идентифицируется. Для этого после фиксации годности с триггера 31 поступит сигнал на мультиплексор 6, который передает

адрес счетчика 3 адреса на адресные входы блока 11 памяти, с выходов которого снимается код объекта 15- контроля на блок 14 управления для передачи

рыми входами мультиплексора, третий вход которого соединен с третьим выходом блока управления, четвертый вход которого соединен с вторым выхока внешнее устройство (например, мани- дом второго блока памяти, третьи выхо10

20

25

30

пулятор). Идентификация типа объекта 15 контроля при фиксации годности его обеспечивается знанием конкретного адреса тестов по счетчику 3 адреса, хранимых в блоке 9 памяти, в момент фиксации годности.

Формула изобретения

{Устройство контроля интегральных 15 схем, содержащее программируемый источник напряжения, многоканальный компаратор, первые входы которого соединены с соответствующими выходами блока ключей, клеммы для подключения объекта контроля, отличающее с я тем, что, с целью расширения функциональных возможностей, в него введены измеритель, блок управления, первый, второй, третий блоки памяти, коммутатор, первый, второй счетчики адреса, программируемый генератор тока, источник опорного напряжения, формирователь импульсов, мультиплексор, блок сжатия информации, причем первый выход программируемого источника напряжений соединен с первым зходом измерителя, выход которого соединен с первым входом блока сжатия информации, выходы которого соединены с соответствующими первыми входами мультиплексора, первый вход блока управления соединен с первым выходом первого блока памяти, вторые выходы которого соединены с соответст-40 вующими первыми входами коммутатора, первые выводы которого соединены с соответствующими первыми входами многоканального компаратора, выходы которого соединены с соответствующими вто-45 рыми входами блока управления, вторые выводы коммутатора соединены с соответствующими клеммами для подключения объекта контроля, выходы мультиплексора соединены с соответствующими Q входами второго блока памяти, первые выходы которого соединены с соответствующими третьими входами блока управления, первый, второй выходы которого соединены соответственно с пер- 55 вым, вторым входами первого сче,тчи- ка адреса, выходы которого соединены с соответствующими входами третьего блока памяти и с соответствующими вто35

ды которого соединены с -соответствующими третьими входами первого счетчика адреса, четвертый выход блока управления соединен с первым входом второго счетчика адреса и через формирователь импульсов - с вторым входом блока сжатия информации, третий вход которого соединен с пятым выходом блока управления иас вторым входом второго счетчика адреса, выходы которого соединены с соответствующими входами первого блока памяти, третьи выходы которого соединены с соответствующими входами программируемого источника напряжения, второй выход которого, соединен с третьим выводом коммутатора, четвертый вцвод которого соединен с вторым входом измерителя и с выходом программируемого генератора тока, входы которого соединены с соответствующими четвертыми выходами первого блока памяти, вторые входы коммутатора соединены с соответствующими первыми выходами третьего блока памяти, вторые выходы которого соединены с соответствующими первыми входами блока ключей и с соответствующими вторыми входами многоканального компаратора, третьи входы которого соединены с соответствующими вторыми входами блока ключей и с соответствующими третьими выходами третьего блока па-, мяти, четвертый, пятый, шестой, седьмой выходы которого соединены соответственно с пятым, шестым, седьмым восьмым входами блока управления, третий, четвертый входы блока ключей соединены соответственно с первым, вторым выходами источника опорного напряжения, третий, четвертый выходы которого соединены соответственно с четвертым, пятым входами многоканального компаратора.

0

5

0

5 0 5 Q5 5

ды которого соединены с -соответствующими третьими входами первого счетчика адреса, четвертый выход блока управления соединен с первым входом второго счетчика адреса и через формирователь импульсов - с вторым входом блока сжатия информации, третий вход которого соединен с пятым выходом блока управления иас вторым входом второго счетчика адреса, выходы которого соединены с соответствующими входами первого блока памяти, третьи выходы которого соединены с соответствующими входами программируемого источника напряжения, второй выход которого, соединен с третьим выводом коммутатора, четвертый вцвод которого соединен с вторым входом измерителя и с выходом программируемого генератора тока, входы которого соединены с соответствующими четвертыми выходами первого блока памяти, вторые входы коммутатора соединены с соответствующими первыми выходами третьего блока памяти, вторые выходы которого соединены с соответствующими первыми входами блока ключей и с соответствующими вторыми входами многоканального компаратора, третьи входы которого соединены с соответствующими вторыми входами блока ключей и с соответствующими третьими выходами третьего блока па-, мяти, четвертый, пятый, шестой, седьмой выходы которого соединены соответственно с пятым, шестым, седьмым восьмым входами блока управления, третий, четвертый входы блока ключей соединены соответственно с первым, вторым выходами источника опорного напряжения, третий, четвертый выходы которого соединены соответственно с четвертым, пятым входами многоканального компаратора.

и с соответствующими выходами блока, первый вход которого соединен с вторым входом полусумматора, выход которого соединен с первым входом сдвигающего регистра, второй и третий входы которого соединены соответственно с вторым и третьим входами

блока.

генератора тактовых импульсов, перво- зд с первым входом второго элемента ШП1,

го, второго, третьего формирователей импульсов, первого, второго, третьего, четвертого, пятого триггеров, первого, второго, третьего, четвертого, пятого и шестого элементов И, элемента НЕ, первого, второго элементов ИЛИ, шины данных и шины Пуск, первый вход блока соединен с первым входом первого триггера, через первый формирователь импульсов - с первым входом второго триггера и через второй формирователь импульсов - с первыми входами первого, второго элементов И, выход первого элемента И соединен с первым входом третьего триггера и с первым входом четвертого триггера, первый выход которого соединен с первым входом пятого триггера и с первым входом третьего элемента И, выход которого соединен с первым выходом блока, вторые входы которого соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, второй

0

0

5

вход которого соединен с первым выходом второго триггера, с вторым входом третьего элемента И и с первым входом пятого элемента И, второй вход кото- оого соединен с первым выходом третьего, первый выход пятого триггера соединен с третьим входом третьего элемента И, четвертый вход которого соединен с первым выходом генератора тактовых импульсов, второй выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с первым выходом первого триггера, вторые выходы первого, второго, третьего, четвертого, пятого триггеров соединены соответственно с первым вторым, третьим, четвертым пятым входами блока индикации и соответственно с первым, вторым, третьим, четвертым, пятым выводами шикы данных, другие выводы которой соединены с соответствующими шестыми входами блока индикации и с соответствующими третьими входами блока, четвертый вход которого соединен с вторым входом первого элемента И и через элемент НЕ - с вторым входом второго элемента И, выход которого соединен

5

0

0

5

выход которого соединен с вторым выходом блока, третий выход которого соединен с первым выходом четвертого триггера, выход шестого элемента И соединен с четвертым выходом блока, пятый выход которого соединен с шиной Пуск, с вторым входом второго элемента ИЛИ и через третий формирователь импульсов - с вторыми входами первого, второго, третьего, четвертого, пятого триггеров, третий вход второго триггера соединен с пятым входом блока, шестой вход которого соединен с третьим входом третьего триггера, четвертый вход которого соединен с выходом четвертого элемента И, третий вход которого соединен с третьим выходом генератора тактовых импульсов и с третьим входом пятого элемента И, четвертый вход которого соединен с седьмым входом блока, восьмой вход которого соединен с третьим входом пятого триггера, выход пятого элемента И соединен с третьим входом четвертого триггера.

| Устройство для контроля интегральных схем | 1984 |

|

SU1208555A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство контроля интегральных схем | 1982 |

|

SU1049838A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-05-15—Публикация

1987-01-06—Подача