ства, выход элемента И группы

триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1278845A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти, дешифратор, регистр адреса, регистр микрокоманд, мультиплексор, коммутатор, генератор тактовых импульсов, триггер и элемент ИЛИ, причем группа информационных входов мультиплексора является группой входов логических условий устройства, группа управляющих входов мультиплексора соединена с группой выходов кода логических условий регистра микрокоманд, группа выходов кода немодифицируемых разрядов адреса которого соединены с первой группой (п-1}-информационных входов коммутатора (где П 2), п -и информационный вход первой группы которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом модифицируемого разряда регистра микрокоманд, группа информационных входов которого соединена с группой выходов блока памяти, группа адресных входов которого соединена с группой выходов дешифратора, группа входов которого соединена с группой выходов регистра адреса, группа информационных входов которого соединена с группой выходов коммутатора, вторая группа информационных входов которого является группой входов кода команды устройства, второй вход элемента ИЛИ соединен с выходом мультиплексора, входы синхронизации регистра адреса и регистра микрокоманды соединены соответственно с первым и вторым выходами генератора тактовых импульсов, вход запуска которого i соединен с выходом триггера, вход установки в единицу которого является входом пуска устройства, о тличающееся тем, что, с целью уменьшения объема оборудования, дополнительно содержит сумматор, группу m элементов И (, 2 ...), шифратор преобразования кодов модулей и шифратор преобразования остатков, причем группа выходов 00 4 4 СО кода операций регистра микрокоманд и группа выходов регистра адреса соединены соответственно с группами входов шифратора преобразования кодов модулей и шифратора преобразования остатков, группы выходов которых соединены соответственно с первым и вторым входами сумматора, m выходов которого соединены соответственно с первыми входами элементов И группы, вторые входы которых соединены с третьим выходом генератора тактовых импульсов, Оп+1)-й выход сумматора соединен с управляющим входом коммутатора, выходы i -х ( -i 1, 2,...,m -1) элементов И группы яв

Изобретение относится к автомати ке и вычислительной технике и может j6biTb использовано в ЭВМ, вычислительных и управляющих системах с микропрограммным управлением. Известно микропрограммное устрой ство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, генератор тактовых импульсов, блок проверки логи ческих условий, элементы И C.J Недостатком этого устройства является большой объем блока памяти. Известно также микропрограммное устройство управления, содержащее регистр адреса, регистр микрокоманд блок памяти микропрограмм, формиров тель адреса, генератор тактовых импульсов, триггер 2 . Недостатком этого устройства является низкая экономичность,обусловленная избыточностью блока памят Наиболее близким к предлагаемому по технической сущности и достигаемому результату является микропрограммное устройство управления, содержащее блок памяти, дешифратор, регистр адреса, регистр микрокоманд мультиплексор, коммутатор, генерато тактовых импульсов, триггер пуска, элемент ИЛИ, причем вход логических условий устройства и выход кода логических условий регистра микрокоманд соединены с информационным и управляющим входами мультиплексора соответственно, выход которого соед нен с первым входом элемента ИЛИ, в ходы немодифицируемьга: разрядов выхода адреса регистра микрокоманд соединены с входами немодифицируемы разрядов первого информационного входа коммутатора, выход модифицируемого разряда выхбда адреса ре- , гистра микрокоманд соединен с вторы входом элемента ИЛИ, выход которого соединен с входом модифицируемого разряда информационного входа комму татора, эход кода операции устройства соединен с вторым информационным входом коммутатора, выход которого соединен с информационным входом регистра адреса, вход пуска устройства соединен с 5 -входом триггера пуска, выход которого соединен с входом генератора тактовых импульсов, первый и второй выходы генератора тактовых импульсов соединены с синхровходами регистра адреса и регистра микрокоманд соответственно, выход регистра адреса соединен с входом дешифратора, выход которого соединен с входом блока памяти, выход блока памяти соединен с информационным входом регистра микрокоманд, выход операционной части которого является выходом микроопераций устройства, выход конца микрокоманды выхода операционной части регистра микрокоманд соединен с управляющим входом коммутатора, выход конца работы выхода операционной части регистра микрокоманд соединен с R -входом триггера пуска ГЗ. Недостатком этого устройства является большой объем блока памяти, обусловленный избыточностью операционных частей микрокоманд. Эта избыточность появляется в результате неэффективного использования методов кодирования и записи информации.. В устройстве используется двоичньй код записи операционных частей микрокоманд, который является громоздким. Избыточность блока памяти составляет ( где - количество микрокоманд, хранимых в блоке памяти; п - основание кода, используемого для записи операционной части микрокоманды. Таким образом, в известном устройстве не реализована возможность кодирования операционных частей с использованием кодов с основанием п 2, что существенно увеличивает разрядность

микрокоманд. Как следует из формулы (1), увеличения основания кодов операционных частей в 2 раза уменьшает объем блока памяти на Ф ячеек. Избыточный объем блока памяти ведет к увеличению затрат на производство микропрограммных управляющих устройств, так как основные затраты (до 90%) приходятся на блок памяти.

Цель изобретения - уменьшение объема оборудования устройства.

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти, дешифратор, регистр адреса, регистр микрокоманд, мультиплексор, коммутатор, генератор тактовых импульсов, триггер и элемент ИЛИ,причем группа информационных входов мультиплексора является группой входов логических условий устройства группа управляющих входов мульти- плексора соединена с группой выходов кода логических условий регистра микрокоманд, группа выходов кода немодифицируемых разрядов адреса которого соединена с первой группой (n-1j информационных входов коммутатора (где п 2), и-и информационный вход первой группы которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом модифицируемого разряда регистра микрокоманд, группа информационных входов которого соединена с группой выходов блока памяти, группа адресных входов которого соединена с группой выходов дешифратора, группа входов которого соединена с группой выходов регистра адреса, группа информационных входов которого соединена с группой выходов коммутатора, вторая группа информационных входов которого являетс группой входов кода команды устройства, второй вход элемента ИЛИ соединен с выходом мультиплексора, входы синхронизации регистра адреса и регистра микрокоманды соединены соответственно с первым и вторым выходами генератора тактовых импульсов, вход запуска которого соединен с выходом триггера, вход установки в единицу которого является входом пуска устройства/ введены сумматор, группа т-элементов И (т 1,2....) пшфратор преобразования кодов модулей и шифратор преобразования остатков, причем группа выходов кода

операций регистра микрокоманд и группа выходов регистра адреса соединены соответственно с группами входов шифратора преобразования кодов моду-

лей и шифратора преобразования остатков, группы выходов которых соединены соответственно с первым и вторым входами сумматора, выходов которого соединены соответственно с первыми входами m элементов И группы, вторые входы которых соединены с третьим выходом генератора импульсов, (т + 1)-й выход сумматора соединен с управляющим входом коммутатора, выходы i -х

(i 1,2,...,tn-1) элементов И группы являются управляющими выходами устройства, выход т-го элемента И группы соединен с входом установки в ноль триггера .

Любое число можно представить в виде

I D ,

где п - основание кода,

с - остаток,

k-h - ричный код числа 3)ч При этом величина . Следовательно, для задания операционной части микрокоманды необходимо иметь только код k который в двоичной форме хранится в блоке памяти предлагаемого устройства. Величину остатка с можно задавать по адресу микрокоманды в блоке памяти. Таким образом, уменьшается количество-разрядность информации, кранимой в блоке памяти.

Например, используя основание кода 5 число too (в двоичной форме записи 1100100) можно представить в виде , где 20 (10100) хранится в блоке памяти. В этом случае вели-

чина с 0. Объем блока памяти уменьшается на 3 разряда. Так для записи числа 130 в блоке памяти достаточно вместо 8 разрядов хранить 5 разрядов с использованием кода с п 5 или 4

разряда при п 10. В этих случаях остаток с 0.

Остаток формируется по адресу микрокоманды в блоке памяти шифратором преобразования остатков, причем

каждому адресу микрокоманды поставлен соответственно один оста- ок.

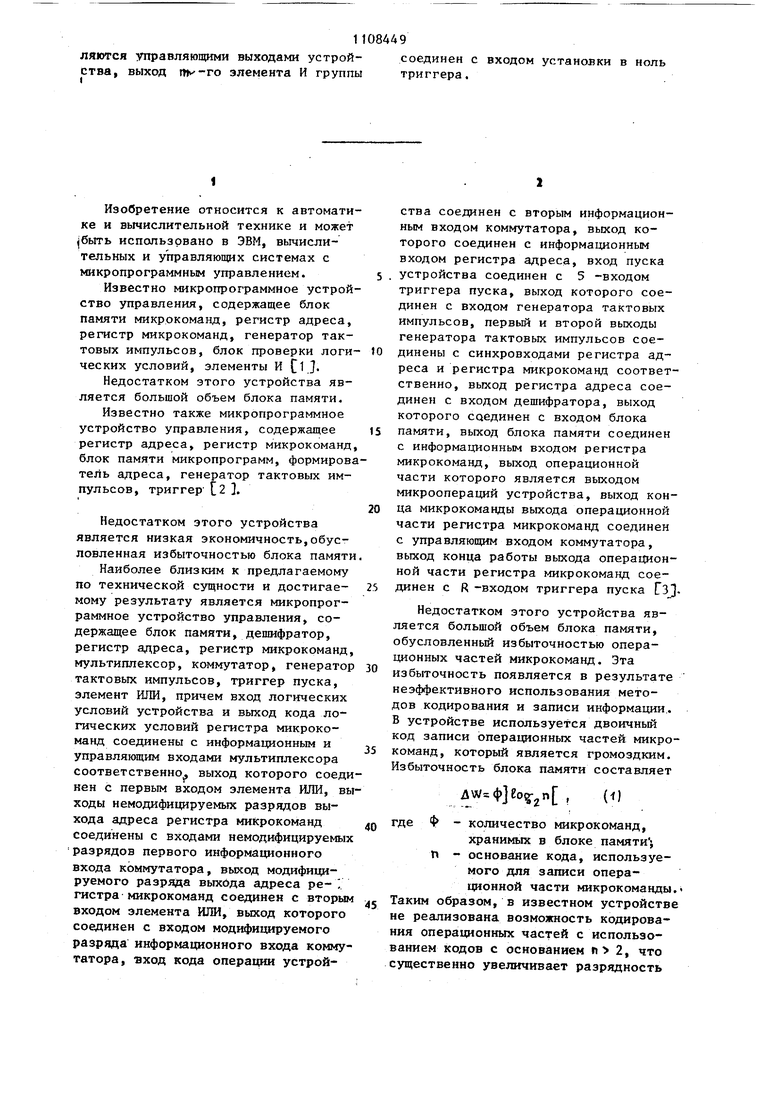

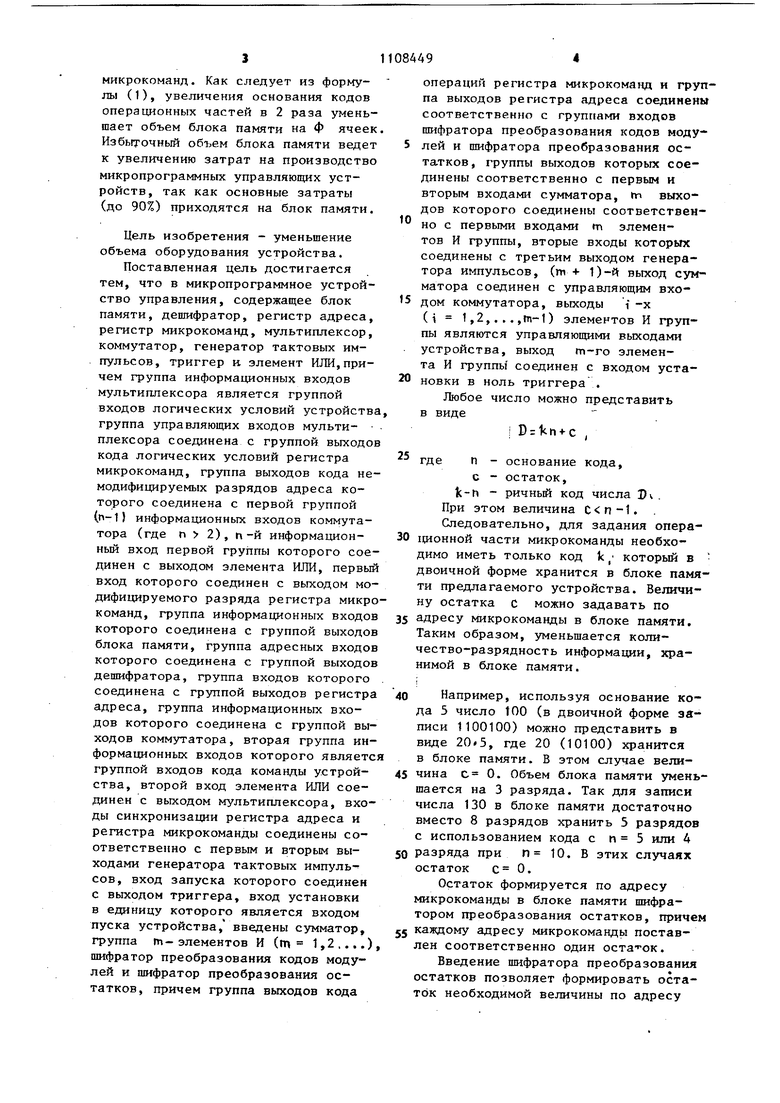

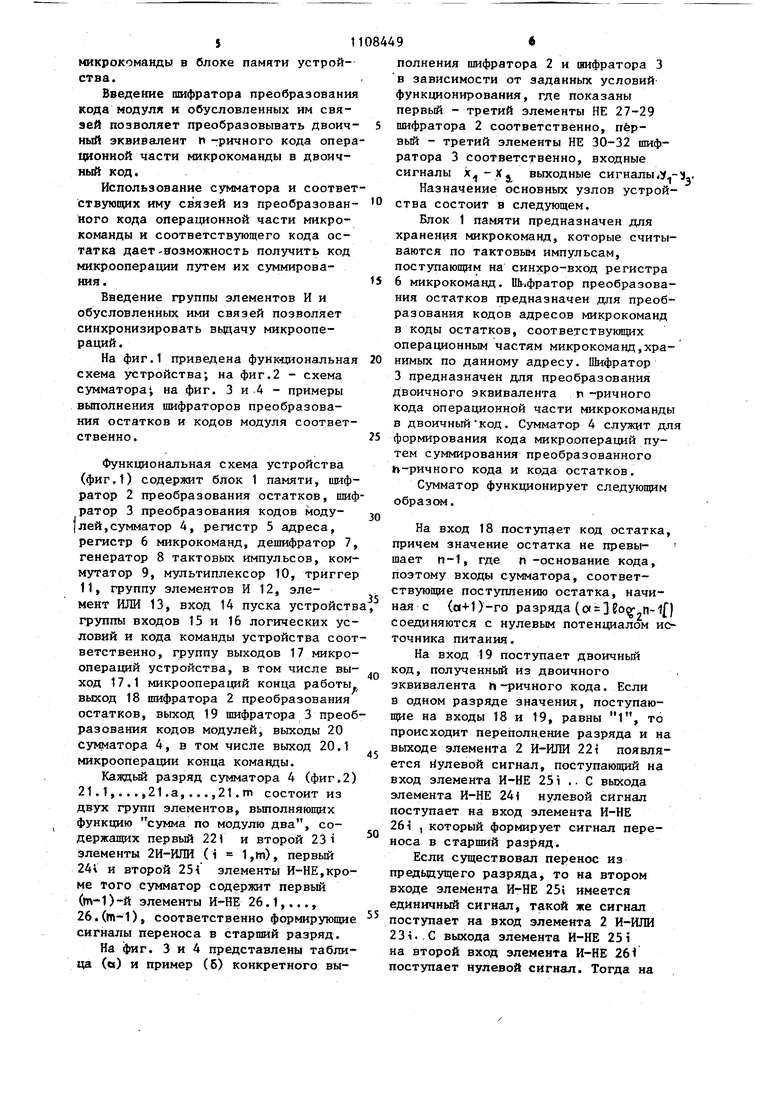

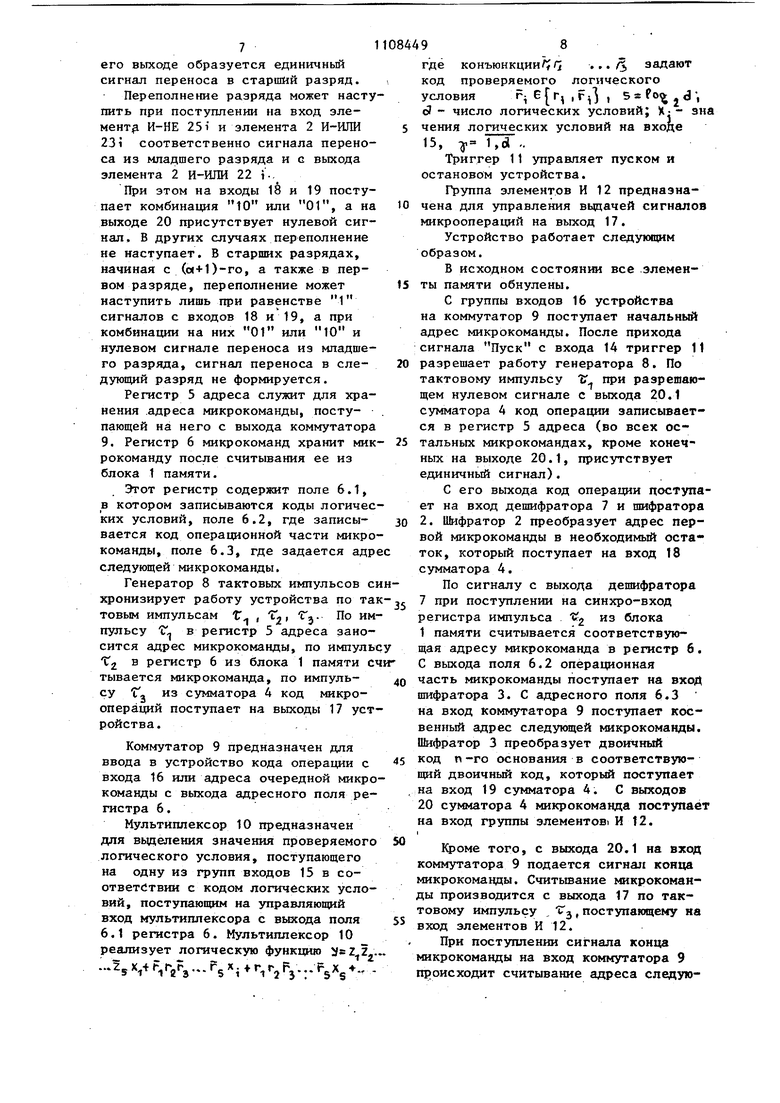

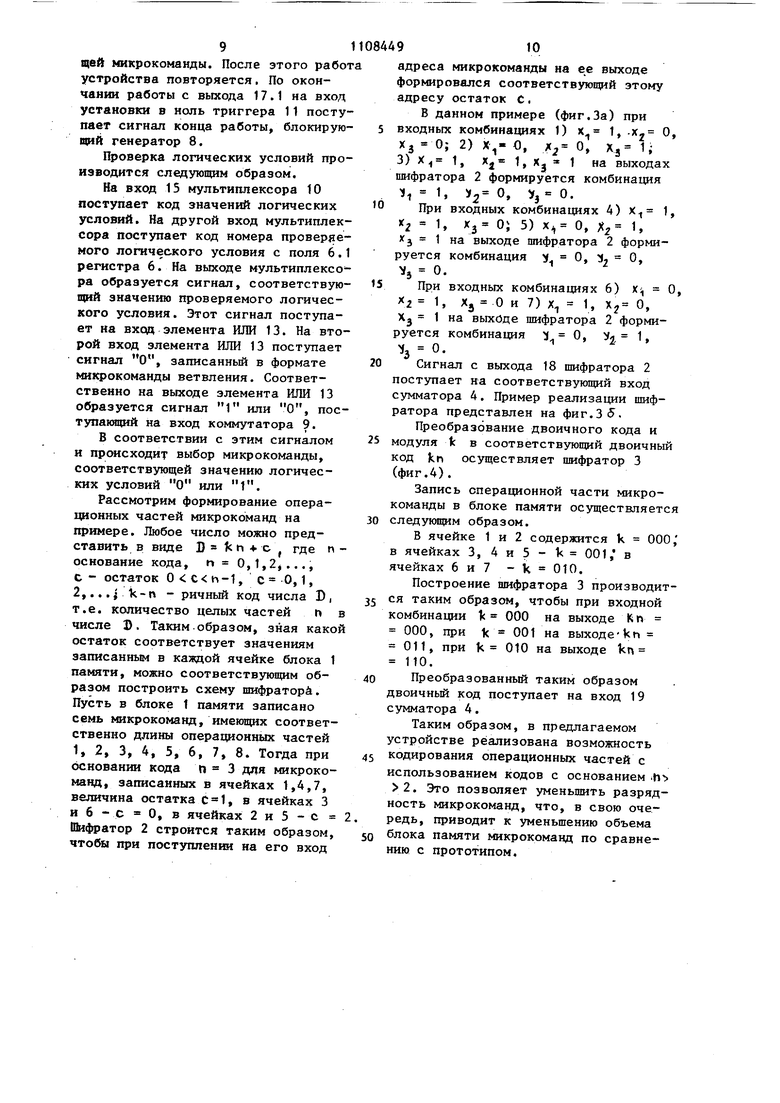

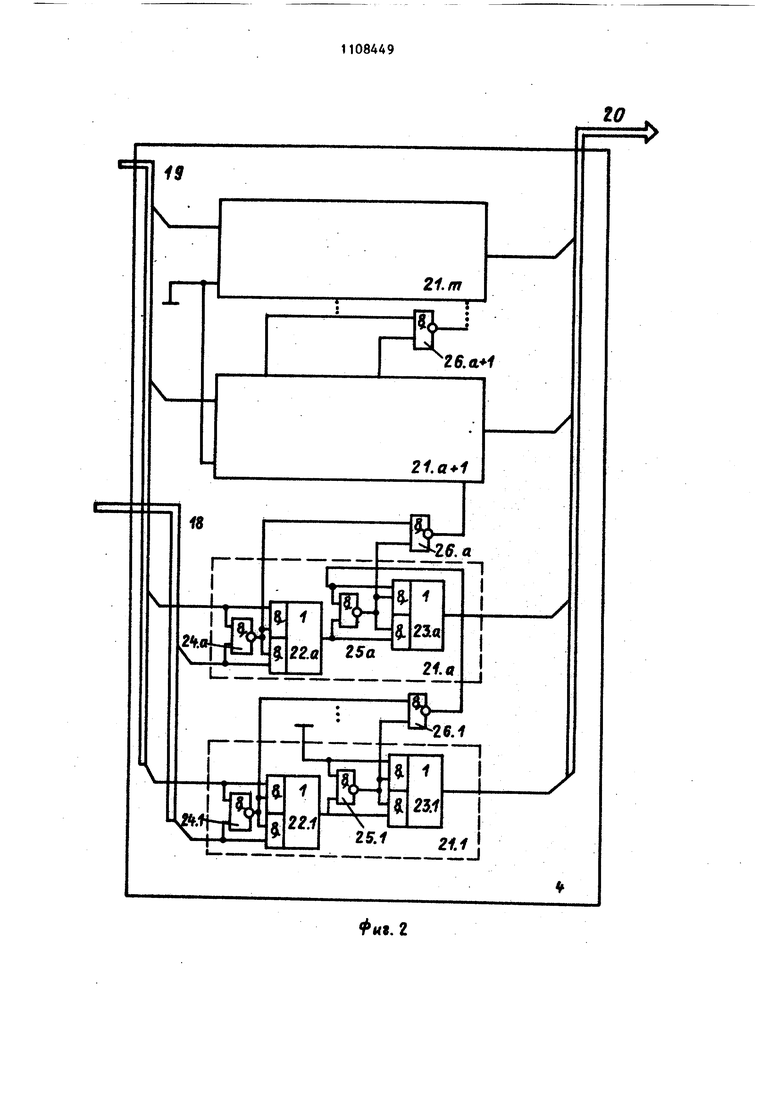

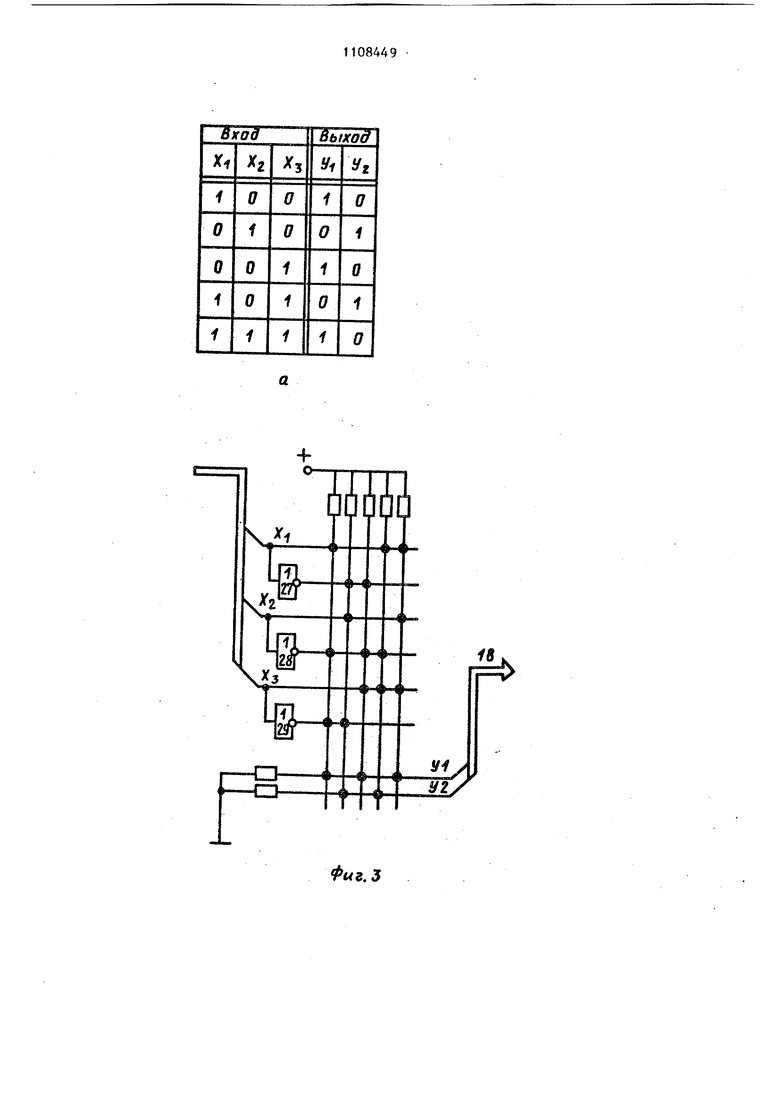

Введение шифратора преобразования остатков позволяет формировать остаток необходимой величины по адресу микрокоманды в блоке памяти устройства. Введение шифратора преобразования кода модуля и обусловленных им связей позволяет преобразовывать двоичный эквивалент h -рнчного кода операционной части микрокоманды в двоичный код. Использование сумматора и соответствуюищх иму связей из преобразованного кода операционной части микрокоманды и соответствующего кода остатка дает-вгозможность получить код микрооперации путем их суммирования. Введение группы элементов И и обусловленных ими связей позволяет синхронизировать вьщачу микроопераций . На фиг. 1 приведена функ иональная схема устройства; на фиг.2 - схема сумматора, на фиг. 3 и 4 - примеры выполнения шифраторов преобразования остатков и кодов модуля соответственно. Функциональная схема устройства (фиг.1) содержит блок 1 памяти, шифратор 2 преобразования остатков, шиф ратор 3 преобразования кодов модуjлей,сумматор 4, регистр 5 адреса, регистр 6 микрокоманд, дешифратор 7, генератор 8 тактовых импульсов, коммутатор 9, мультиплексор 10, триггер 11, группу элементов И 12, элемент ИЖ 13, вход 14 пуска устройств группы входов 15 и 16 логических условий и кода команды устройства соот ветственно, группу выходов 17 микроопераций устройства, в том числе выход 17.1 микроопераций конца работы. выход 18 шифратора 2 преобразования остатков, выход 19 шифратора 3 преоб разования кодов модулей, выходы 20 сумматора 4, в том числе выход 20.1 микрооперации конца команды. Каждый разряд сумматора 4 (фиг.2) 21.1,...,21.а,...,21.ш состоит из двух групп элементов, вьтолняющих функцию сумма по модулю два. Содержащих первый 22Г и второй 23i :элементы 2И-ИЛИ (i 1 ,№), первый 24V и второй 25-1 элементы И-НЕ,кроме того сумматор содержит первый (т-1)-й элементы И-НЕ 26.1,..., 26.(ш-1), соответственно формирующие сигналы переноса в старший разряд. На фиг. 3 и 4 представлены таблица (в) и пример (Б) конкретного выполнения шифратора 2 и шифратора 3 в зависимости от заданных условий функционирования, где показаны первый - третий элементы НЕ 27-29 шифратора 2 соответственно, первый - третий элементы НЕ 30-32 шифратора 3 соответственно, входные сигналы выходные сигналы -ч,. Назначение основных узлов устройства состоит в следующем. Блок 1 памяти предназначен для хранения микрокоманд, которые считываются по тактовым импульсам, постздтающим на синхро-вход регистра 6 микрокоманд. ПЬ фратор преобразования остатков предназначен для преобразования кодов адресов микрокоманд в коды остатков, соответствующих операционным частям микрокоманд,хранимых по данному адресу. Шифратор 3 предназначен для преобразования двоичного эквивалента п -ричного кода операционной части микрокоманды в двоичныйкод. Сумматор 4 служит для формирования кода микроопераций путем суммирования преобразованного П-ричного кода и кода остатков. Сумматор функционирует следующим образом. На вход 18 поступает код остатка, причем значение остатка не превышает п-1, где п -основание кода, поэтому входы сумматора, соответствующие поступлению остатка, начиная с (a+D-ro разряда (а ) соединяются с нулевым потенциалом источника питания. На вход 19 поступает двоичный код, полученный из двоичного эквивалента П-ричного кода. Если и одном разряде значения, поступающие на входы 18 и 19, равны 1, то происходит переполнение разряда и на выходе элемента 2 И-ИЛИ 22t появляется Нулевой сигнал, поступающий на вход элемента И-НЕ 25 i .. С выхода элемента И-НЕ 24 нулевой сигнал поступает на вход элемента И-НЕ 261 , который формирует сигнал переноса в старший разряд. Если существовал перенос из предьдущего разряда, то на втором входе элемента И-НЕ 25i имеется единичный сигнал, такой же сигнал поступает на вход элемента 2 И-ИЛИ 23i..C выхода элемента И-НЕ 25i на второй вход элемента И-НЕ 261 поступает нулевой сигнал. Тогда на его выходе образуется единичный сигнал переноса в старший разряд. Переполнение разряда может насту пить при поступлении на вход элементу И-НЕ 25i и элемента 2 И-ИЛИ 23i соответственно сигнала переноса из младшего разряда и с выхода элемента 2 И-ИЛИ 22 iПри этом на входы 18 и 19 поступает комбинация 10 или 01, а на выходе 20 присутствует нулевой сигнал. В других случаях переполнение не наступает. В старших разрядах, начиная с («+1)-го, а также в первом разряде, переполнение может наступить лишь при равенстве 1 сигналов с входов 18 и 19, а при комбинации на них 01 или 10 и нулевом сигнале переноса из младшего разряда, сигнал переноса в еледующий разряд не формируется. Регистр 5 адреса служит для хранения адреса микрокоманды, поступающей на него с выхода коммутатора 9. Регистр 6 микрокоманд хранит мик рокоманду после считывания ее из блока 1 памяти. Этот регистр содержит поле 6.1, в котором записываются коды логичес ких условий, поле 6.2, где записывается код операционной части микро команды, поле 6.3, где задается адр следующей микрокоманды. Генератор 8 тактовых импульсов с хронизирует работу устройства по та товым импульсам 1Г , f.j, Tj. По им пульсу V, в регистр 5 адреса заносится адрес микрокоманды, по импуль 2 в регистр 6 из блока 1 памяти C тывается микрокоманда, по импульсу t, из сумматора 4 код микроопераций поступает на выходы 17 уст ройства. Коммутатор 9 предназначен для ввода в устройство кода операции с входа 16 или адреса очередной микро команды с выхода адресного поля регистра 6. Мультиплексор 10 предназначен для вьщеления значения проверяемого логического условия, поступающего на одну из групп входов 15 в соответствии с кодом логических условий, поступающим на управляющий вход мультиплексора с выхода поля 6.1 регистра 6. Мультиплексор 10 реализует логическую функцию ys , :.Л5 Х,+ - i Pj-:- где конъюнкции/ rj ,../ задают код проверяемого логического условия i il .d, ol - число логических условий; Х-- зна чения логических условий на входе 15, -у 1.(3 .. Триггер 11 управляет пуском и остановом устройства. Группа элементов И 12 предназначена для управления вьщачей сигналов микроопераций на выход 17. Устройство работает следующим образом. В исходном состоянии все .элементы памяти обнулены. С группы входов 16 устройства на коммутатор 9 поступает начальный адрес микрокоманды. После прихода сигнала Пуск с входа 14 триггер 11 разрешает работу генератора 8. По 7 при разрешаютактовому импульсу щем нулевом сигнале с выхода 20.1 сумматора 4 код операции записывается в регистр 5 адреса (во всех остальньпс микрокомандах, кроме конечных на выходе 20.1, присутствует единичный сигнал). С его выхода код операции поступает на вход дешифратора 7 и шифратора 2. Шифратор 2 преобразует адрес первой микрокоманды в необходимый остаток, который поступает на вход 18 сумматора 4. По сигналу с выхода дешифратора 7 при поступлении на синхро-вход регистра импульса 2 блока 1 памяти считывается соответствующая адресу микрокоманда в регистр 6. С выхода поля 6.2 операционная часть микрокоманды поступает на вход шифратора 3. С адресного поля 6.3 на вход коммутатора 9 поступает косвенный адрес следующей микрокоманды. Шифратор 3 преобразует двоичный код п-го основания в соответствующий двоичный код, который поступает на вход 19 сумматора 4. С выходов 20 су№1атора 4 микрокоманда поступает на вход группы элементов И 12. 1фоме того, с выхода 20.1 на вход коммутатора 9 подается сигнал конца микрокомавды. Считьшание микрокоманды производится с выхода 17 по тактовому импульсу , Тз поступающему на вход элементов И 12. При поступлении сигнала конца микрокоманды на вход коммутатора 9 происходит считывание адреса следую9щей микрокоманды. После этого рабо устройства повторяется, По окончании работы с выхода 17.1 на вход установки в ноль триггера 11 посту пает сигнал конца работы, блокирую щий генератор 8. Проверка логических условий про изводится следующим образом. На вход 15 мультиплексора 10 поступает код значений логических условий. На другой вход мультиплек сора поступает код номера проверяе мого логического условия с поля 6. регистра 6. На выходе мультиплексо ра образуется сигнал, соответствую щий значению проверяемого логического условия. Этот сигнал поступает на BXQ4 элемента ИЛИ 13. На вто рой вход элемента ИЛИ 13 поступает сигнал О, записанный в формате микрокоманды ветвления. Соответственно на выходе элемента ШШ 13 образуется сигнал 1 или О, пос тупакяиий на вход коммутатора 9. В соответствии с этим сигналом и прсжсходит выбор микрокоманды, соответствующей значению логических условий О или 1. Рассмотрим формирование операционных частей микрокоманд на примере. Любое число можно представить в виде + Cj где п основание кода, п 0,1,2,..., с - остаток О : С h-1, с О, 1, 2,... k-п - ричный код числа D , т.е. количество целых частей h числе D. Таким образом, зная како остаток соответствует значениям записанным в каждой ячейке блока 1 памяти, можно соответствующим образом построить схему шифратор. Пусть в блоке 1 памяти записано семь микрокоманд, имеющих соответственно длины операционных частей 1, 2, 3, 4, 5, 6, 7, 8. Тогда при основании кода г 3 дпя микрокоманд, записанных в ячейках 1,4,7, величина остатка , в ячейках 3 и 6 - с О, в ячейках 2 и 5 - с Шифратор 2 строится таким образом, чтобы при поступлении на его вход 9 адреса микрокоманды на е.е выходе формировался соответствующий этому адресу остаток С, В данном примере (фиг.За) при входных комбинациях 1) Х- 1, .х- О, 0; 2) X - О, х, О, х, 1; 3) X 1 на выходах шифратора 2 формируется комбинация 1, Ь 0. При входных комбинациях 4) х 1, Кг 1, f3 0; 5) Х;| О, Х2 1. Xj 1 на выходе шифратора 2 формируется комбинация V О, О, 3 ОПри входных комбинациях 6) Х; О, г 1, Хд о и 7) х 1, о. Xj 1 на выходе шифратора 2 формируется комбинация 0, , 3 0. Сигнал с выхода 18 шифратора 2 поступает на соответствующий вход сумматора 4. Пример реализации шифратора представлен на фиг.3|5. Преобразование двоичного кода и модуля fc в соответствующий двоичный код Кп осуществляет шифратор 3 (фиг.4). Запись операционной части микрокоманды в блоке памяти осуществляется следуюпр м образом. В ячейке 1 и 2 содержится К 000, в ячейках 3, 4и5-1 001,в ячейках 6и7 . Построение шифратора 3 производится таким образом, чтобы при входной комбинации 1 000 на выходе К п 000, при 1с 001 на выходе-kn 011, при k 010 на выходе kn 110. Преобразованный таким образом двоичньй код поступает на вход 19 сумматора 4. Таким образом, в предлагаемом устройстве реализована возможность кодирования операционных частей с использованием кодов с основанием Иъ 2. Это позволяет уменьшить разрядность микрокоманд, что, в свою очередь, приводит к уменьшению объема блока памяти микрокоманд по сравнению с прототипом.

19

Itf

a

8

20

i8

Фиг,1

Фн9. 2

18 П

4 Н

I-О21/

.11/

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство микропрограммного управления | 1972 |

|

SU482744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Структура электронных вычислительных машин | |||

| Л., Машиностроение, 1979, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1984-08-15—Публикация

1983-03-29—Подача