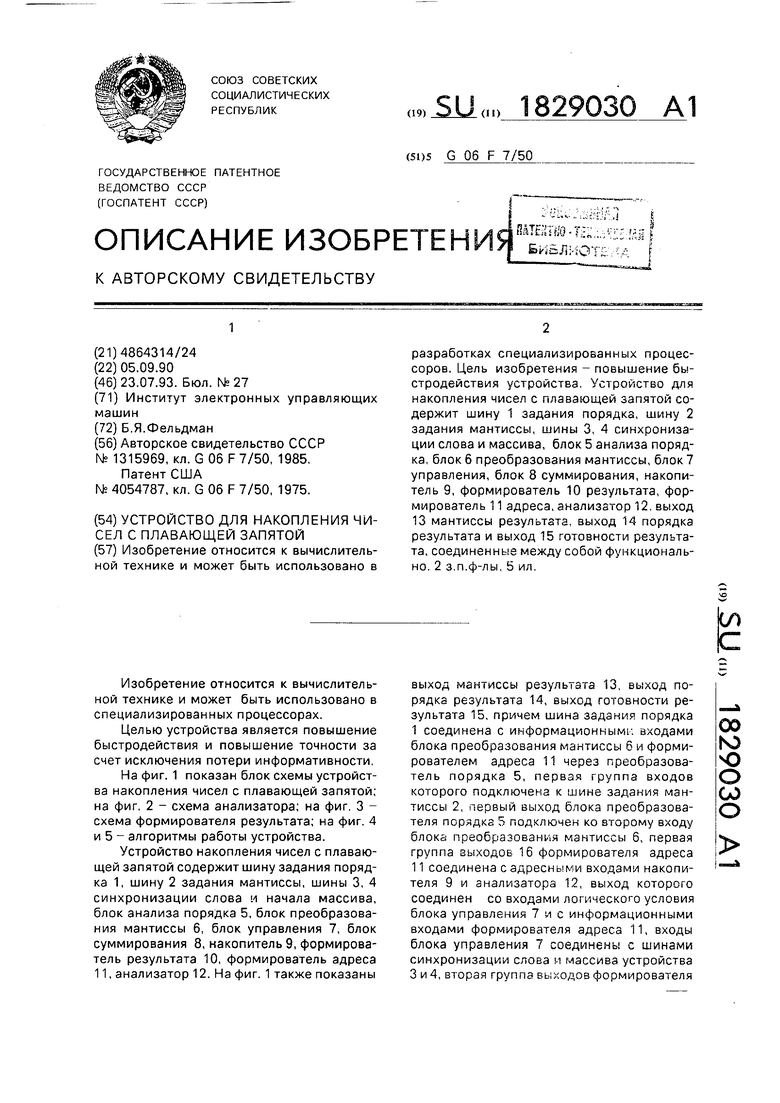

Изобретение относится к вычислительной технике и может быть использовано в специализированных процессорах.

Целью устройства является повышение быстродействия и повышение точности за счет исключения потери информативности.

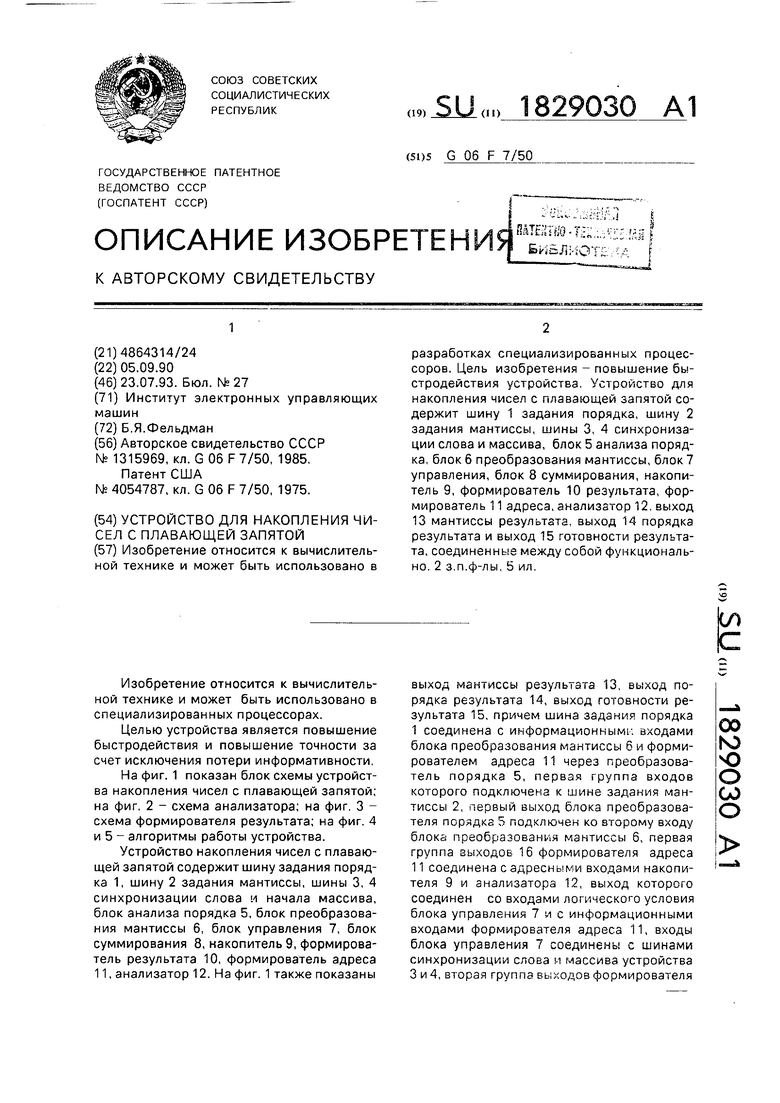

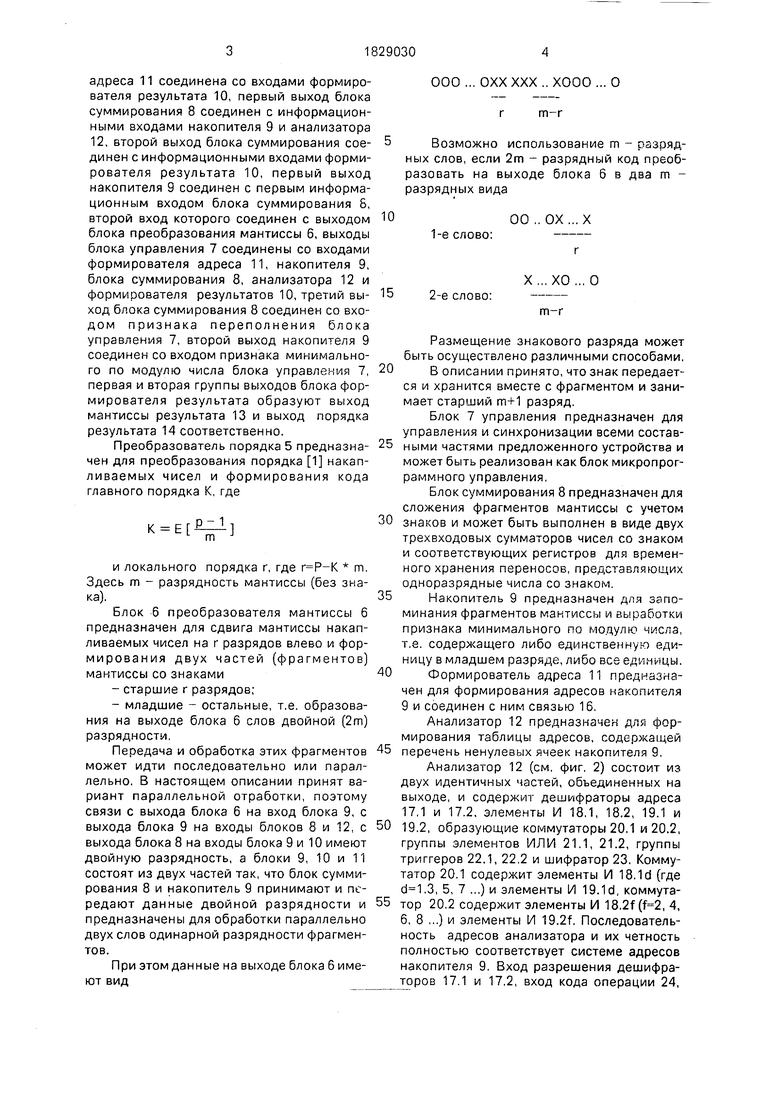

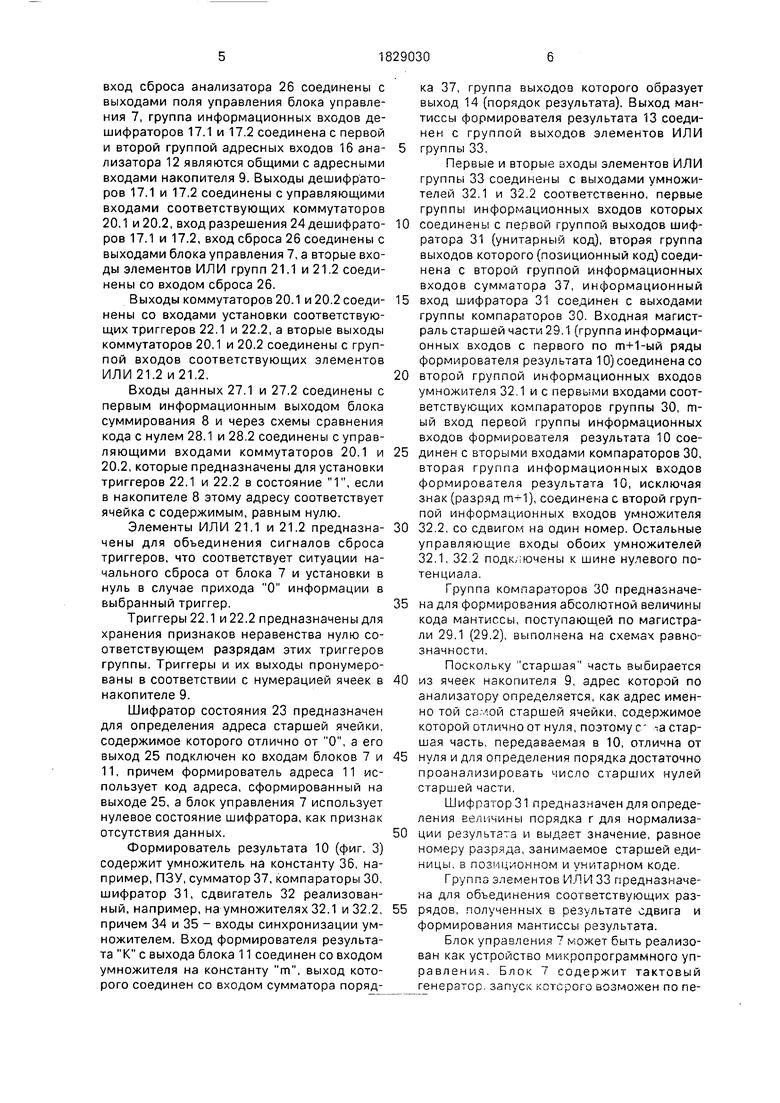

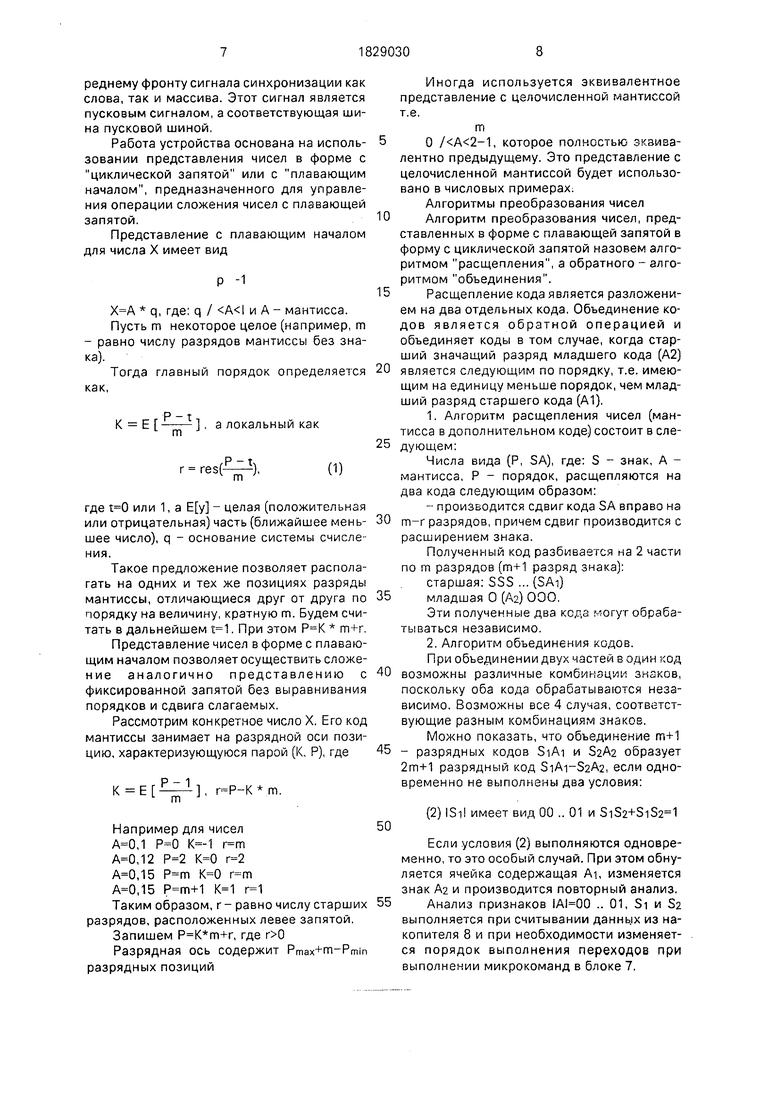

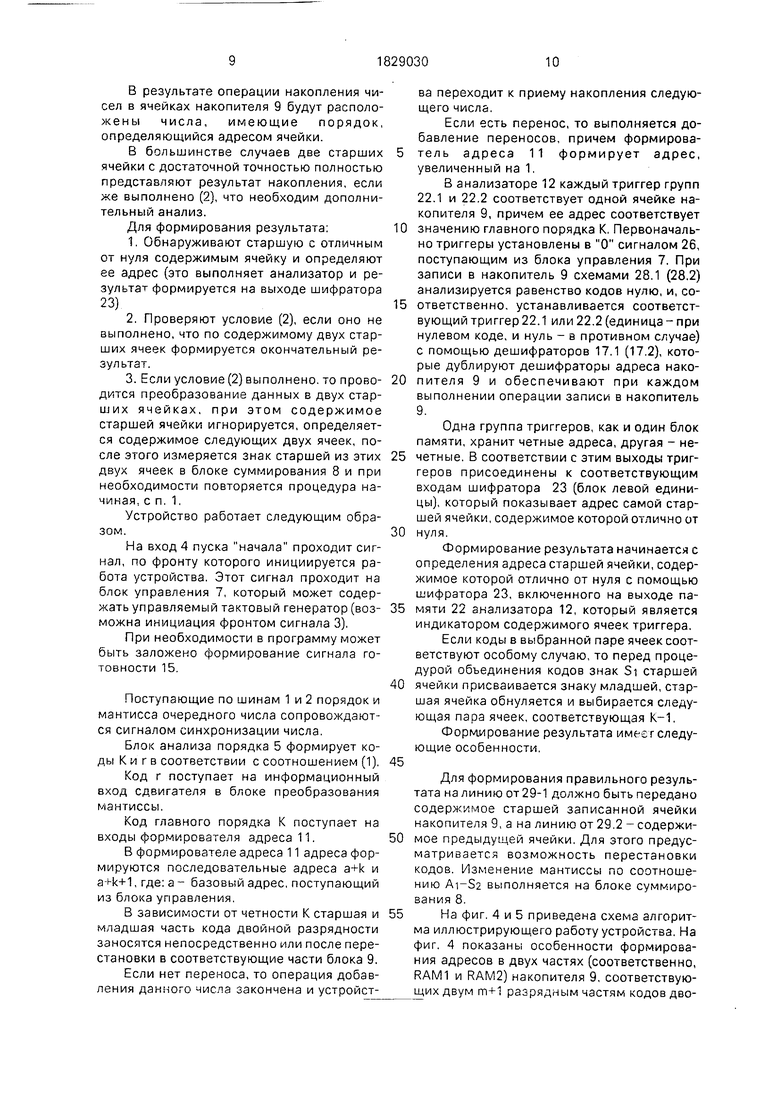

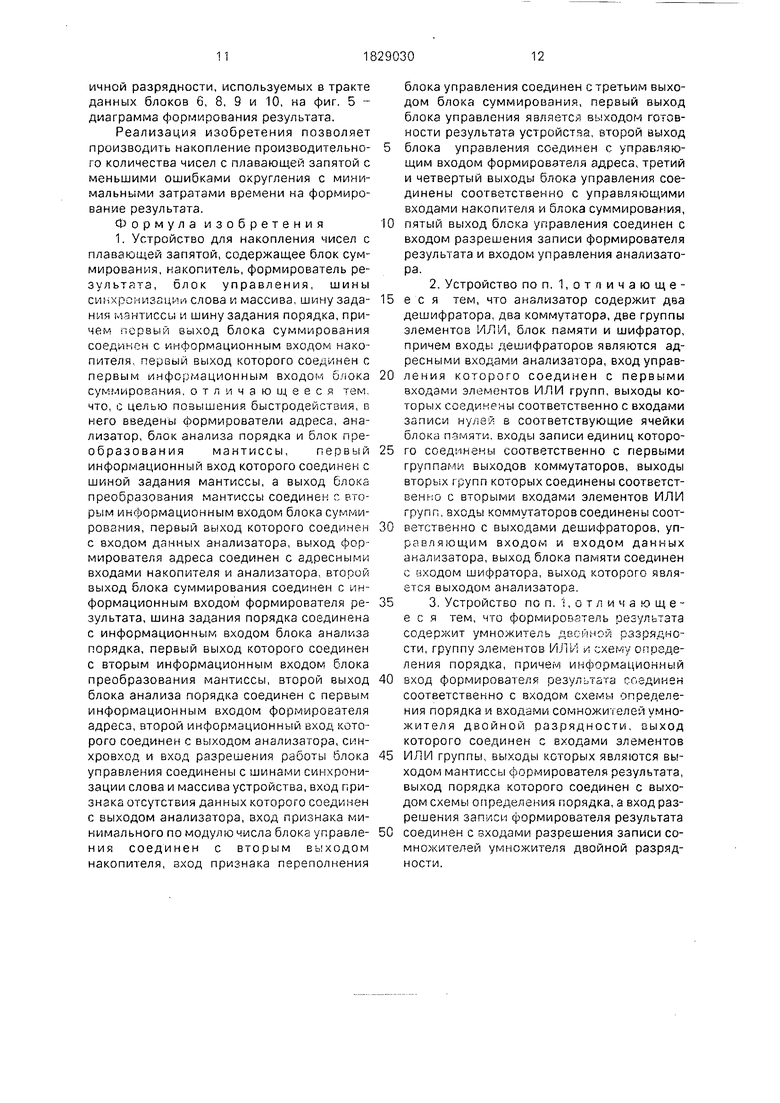

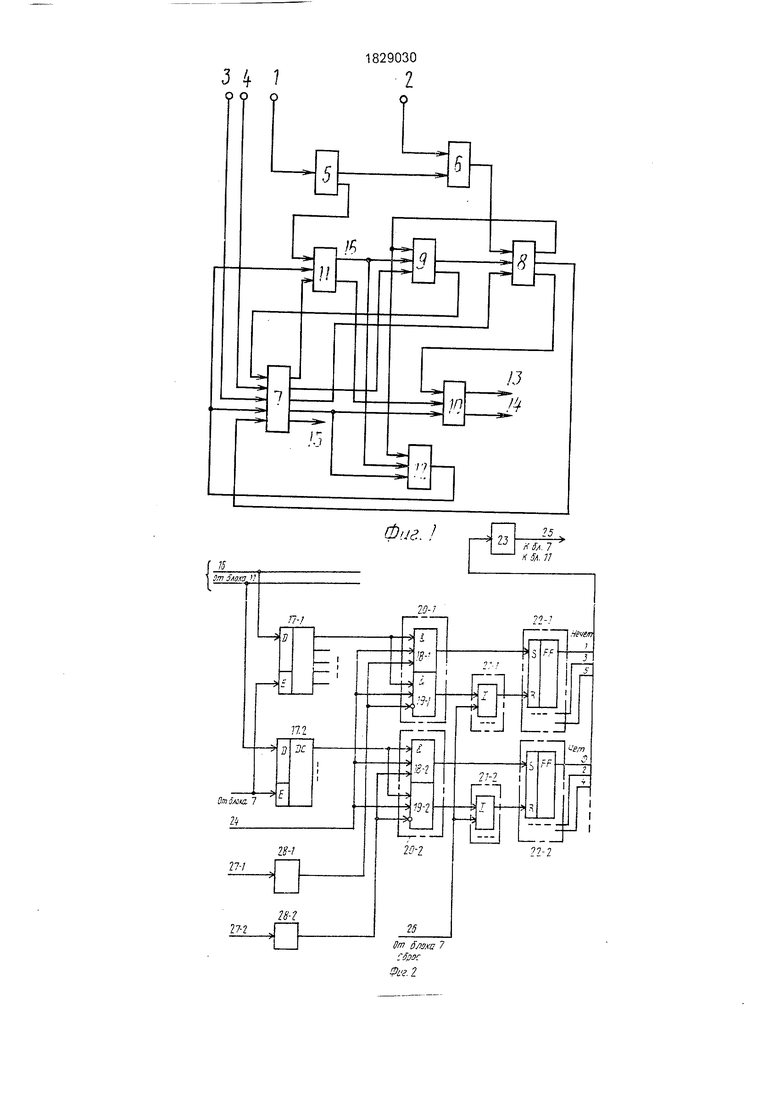

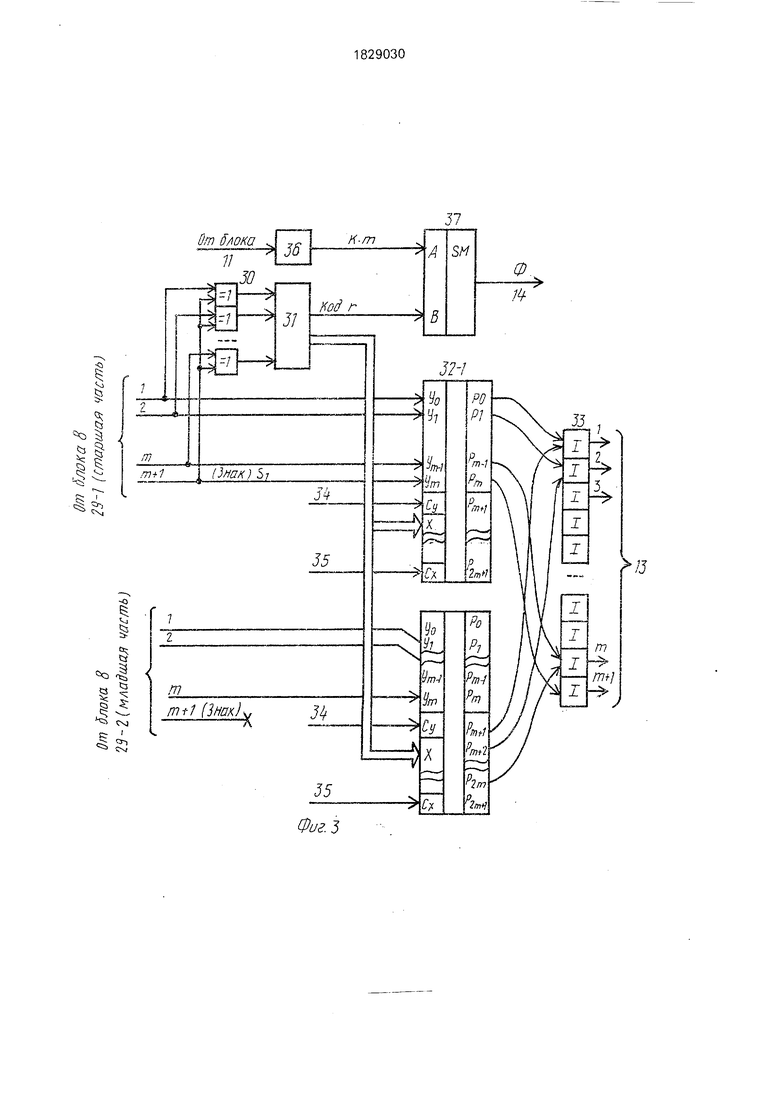

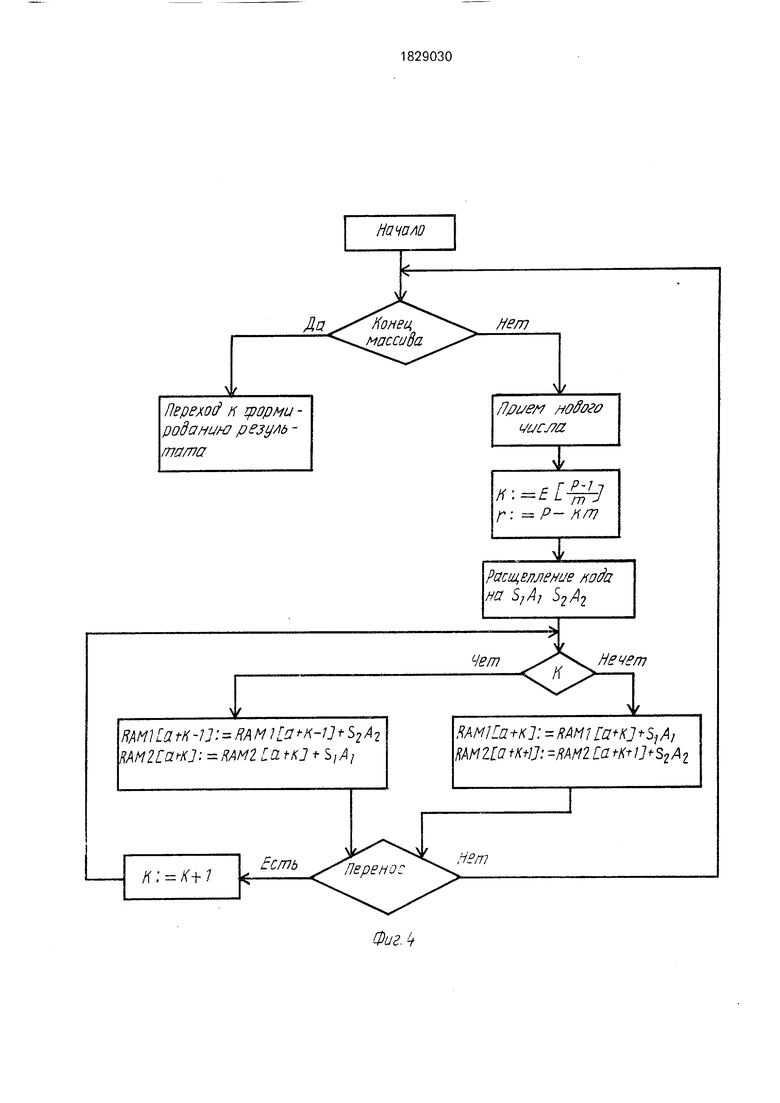

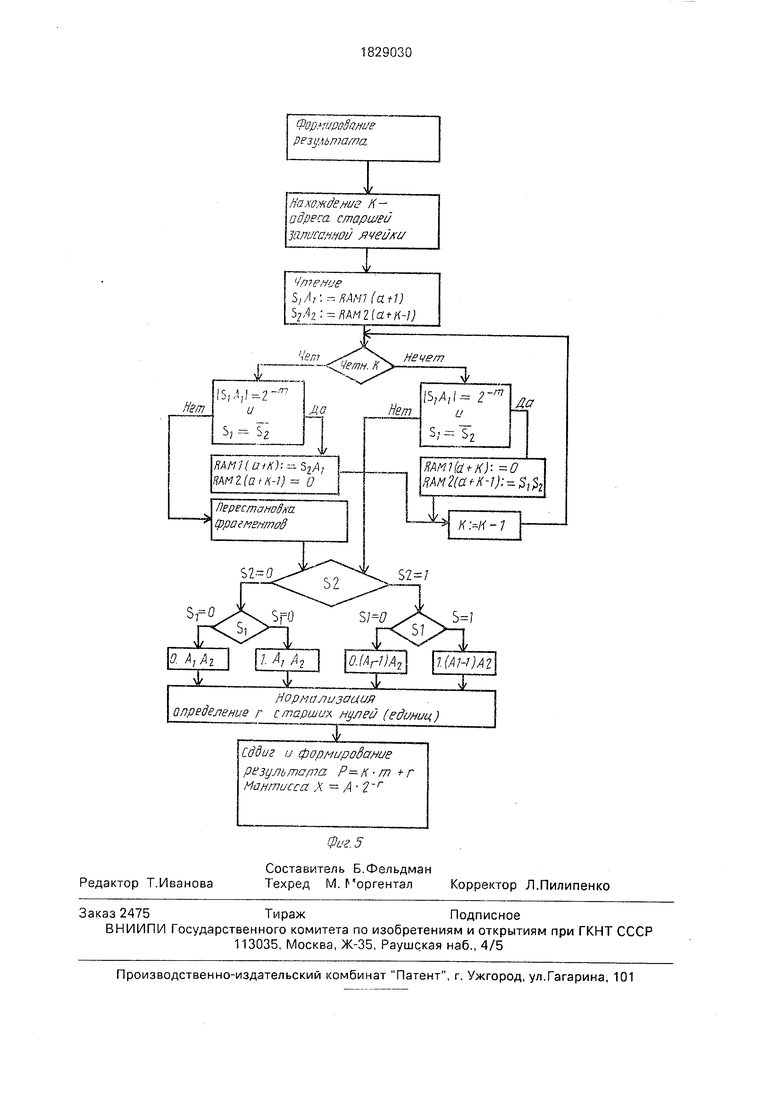

На фиг. 1 показан блок схемы устройства накопления чисел с плавающей запятой; на фиг. 2 - схема анализатора; на фиг. 3 - схема формирователя результата; на фиг. 4 и 5 - алгоритмы работы устройства.

Устройство накопления чисел с плавающей запятой содержит шину задания порядка 1, шину 2 задания мантиссы, шины 3, 4 синхронизации слова и начала массива, блок анализа порядка 5, блок преобразования мантиссы 6, блок управления 7, блок суммирования 8, накопитель 9, формирователь результата 10, формирователь адреса 11, анализатор 12. На фиг. 1 также показаны

выход мантиссы результата 13, выход порядка результата 14, выход готовности результата 15, причем шина задания порядка

Iсоединена с информационным --, входами блока преобразования мантиссы 6 и формирователем адреса 11 через преобразователь порядка 5, первая группа входов которого подключена к шине задания мантиссы 2, первый выход блока преобразователя порядка 5 подключен ко второму входу блока преобразования мантиссы 6, первая группа выходов 16 формирователя адреса

I1соединена с адресными входами накопителя 9 и анализатора 12, выход которого соединен со входами логического условия блока управления 7 и с информационными входами формирователя адреса 11, входы блока управления 7 соединены с шинами синхронизации слова и массива устройства 3 и 4, вторая группа выходов формирователя

00

ю ю о

СА

О

адреса 11 соединена со входами формирователя результата 10, первый выход блока суммирования 8 соединен с информационными входами накопителя 9 и анализатора 12, второй выход блока суммирования соединен с информационными входами формирователя результата 10, первый выход накопителя 9 соединен с первым информационным входом блока суммирования 8, второй вход которого соединен с выходом блока преобразования мантиссы 6, выходы блока управления 7 соединены со входами формирователя адреса 11, накопителя 9, блока суммирования 8, анализатора 12 и формирователя результатов 10, третий выход блока суммирования 8 соединен со входом признака переполнения блока управления 7, второй выход накопителя 9 соединен со входом признака минимального по модулю числа блока управления 7, первая и вторая группы выходов блока формирователя результата образуют выход мантиссы результата 13 и выход порядка результата 14 соответственно.

Преобразователь порядка 5 предназначен для преобразования порядка 1 накапливаемых чисел и формирования кода главного порядка К, где

к

и локального порядка г, где гл. Здесь m - разрядность мантиссы (без знака).

Блок 6 преобразователя мантиссы 6 предназначен для сдвига мантиссы накапливаемых чисел на г разрядов влево и формирования двух частей (фрагментов) мантиссы со знаками

-старшие г разрядов;

-младшие - остальные, т.е. образования на выходе блока 6 слов двойной (2т) разрядности.

Передача и обработка этих фрагментов может идти последовательно или параллельно. В настоящем описании принят вариант параллельной отработки, поэтому связи с выхода блока 6 на вход блока 9, с выхода блока 9 на входы блоков 8 и 12, с выхода блока 8 на входы блока 9 и 10 имеют двойную разрядность, а блоки 9, 10 и 11 состоят из двух частей так, что блок суммирования 8 и накопитель 9 принимают и передают данные двойной разрядности и предназначены для обработки параллельно двух слов одинарной разрядности фрагментов.

При этом данные на выходе блока 6 имеют вид

000 ... ОХХХХХ..ХООО... О г m-r

5Возможно использование m - разрядных слов, если 2т - разрядный код преобразовать на выходе блока 6 в два m - разрядных вида

10

00 .. ОХ ... X

1-е слово:

15 2-е слово:

Х...ХО...О

m-r

Размещение знакового разряда может быть осуществлено различными способами.

в описании принято, что знак передается и хранится вместе с фрагментом и занимает старший т+1 разряд.

Блок 7 управления предназначен для управления и синхронизации всеми составными частями предложенного устройства и может быть реализован как блок микропрограммного управления,

Блок суммирования 8 предназначен для сложения фрагментов мантиссы с учетом

знаков и может быть выполнен в виде двух трехвходовых сумматоров чисел со знаком и соответствующих регистров для временного хранения переносов, представляющих одноразрядные числа со знаком.

Накопитель 9 предназначен для запоминания фрагментов мантиссы и выработки признака минимального по модулю числа, т.е. содержащего либо единственную единицу в младшем разряде, либо все единицы.

Формирователь адреса 11 предназначен для формирования адресов накопителя 9 и соединен с ним связью 16.

Анализатор 12 предназначен для формирования таблицы адресов, содержащей

перечень ненулевых ячеек накопителя 9.

Анализатор 12 (см. фиг. 2) состоит из двух идентичных частей, объединенных на выходе, и содержит дешифраторы адреса 17.1 и 17.2. элементы И 18.1, 18.2, 19.1 и

19.2, образующие коммутаторы 20.1 и 20.2, группы элементов ИЛИ 21.1, 21.2, группы триггеров 22.1, 22.2 и шифратор 23. Коммутатор 20.1 содержит элементы И 18.1d (где .3, 5, 7 ...) и элементы И 19.1d, коммутатор 20.2 содержит элементы И 18,2f (, 4, б, 8 ...) и элементы И 19.2f. Последовательность адресов анализатора и их четность полностью соответствует системе адресов накопителя 9. Вход разрешения дешифраторов 17.1 и 17.2, вход кода операции 24,

вход сброса анализатора 26 соединены с выходами поля управления блока управления 7, группа информационных входов дешифраторов 17.1 и 17.2 соединена с первой и второй группой адресных входов 16 анализатора 12 являются общими с адресными входами накопителя 9. Выходы дешифраторов 17.1 и 17.2 соединены с управляющими входами соответствующих коммутаторов 20.1 и 20.2, вход разрешения 24 дешифраторов 17.1 и 17.2, вход сброса 26 соединены с выходами блока управления 7, а вторые входы элементов ИЛИ групп 21.1 и 21.2 соединены со входом сброса 26.

Выходы коммутаторов 20.1 и 20.2 соединены со входами установки соответствующих триггеров 22.1 и 22.2, а вторые выходы коммутаторов 20.1 и 20.2 соединены с группой входов соответствующих элементов ИЛИ 21.2 и 21.2.

Входы данных 27.1 и 27.2 соединены с первым информационным выходом блока суммирования 8 и через схемы сравнения кода с нулем 28.1 и 28.2 соединены с управляющими входами коммутаторов 20.1 и 20.2, которые предназначены для установки триггеров 22.1 и 22.2 в состояние 1, если в накопителе 8 этому адресу соответствует ячейка с содержимым, равным нулю.

Элементы ИЛИ 21.1 и 21.2 предназначены для объединения сигналов сброса триггеров, что соответствует ситуации начального сброса от блока 7 и установки в нуль в случае прихода О информации в выбранный триггер.

Триггеры 22,1 и 22.2 предназначены для хранения признаков неравенства нулю соответствующем разрядам этих триггеров группы. Триггеры и их выходы пронумерованы в соответствии с нумерацией ячеек в накопителе 9.

Шифратор состояния 23 предназначен для определения адреса старшей ячейки, содержимое которого отлично от О, а его выход 25 подключен ко входам блоков 7 и 11, причем формирователь адреса 11 использует код адреса, сформированный на выходе 25, а блок управления 7 использует нулевое состояние шифратора, как признак отсутствия данных.

Формирователь результата 10 (фиг. 3) содержит умножитель на константу 36, например, ПЗУ, сумматор 37, компараторы 30, шифратор 31, сдвигатель 32 реализованный, например, на умножителях 32.1 и 32.2, причем 34 и 35 - входы синхронизации умножителем. Вход формирователя результата К с выхода блока 11 соединен со входом умножителя на константу т, выход которого соединен со входом сумматора порядка 37, группа выходов которого образует выход 14 (порядок результата). Выход мантиссы формирователя результата 13 соединен с группой выходов элементов ИЛИ

группы 33.

Первые и вторые входы злементов ИЛИ группы 33 соединены с выходами умножителей 32.1 и 32.2 соответственно, первые группы информационных входов которых

0 соединены с первой группой выходов шифратора 31 (унитарный код), вторая группа выходов которого (позиционный код) соединена с второй группой информационных входов сумматора 37, информационный

5 вход шифратора 31 соединен с выходами группы компараторов 30. Входная магистраль старшей части 29.1 (группа информационных входов с первого по m+1-ый ряды формирователя результата 10)соединена со

0 второй группой информационных входов умножителя 32,1 и с первыми входами соответствующих компараторов группы 30, т- ый вход первой группы информационных входов формирователя результата 10 сое5 динен с вторыми входами компараторов 30, вторая группа информационных входов формирователя результата 10, исключая знак (разряд т-Н), соединена с второй группой информационных входов умножителя

0 32.2, со сдвигом на один номер. Остальные управляющие входы обоих умножителей 32.1, 32.2 подключены к шине нулевого потенциала.

Группа компараторов 30 предназначе5 на для формирования абсолютной величины кода мантиссы, поступающей по магистрали 29.1 (29.2), выполнена на схемах равнозначности.

Поскольку старшая часть выбирается

0 из ячеек накопителя 9, адрес которой по анализатору определяется, как адрес именно той самой старшей ячейки, содержимое которой отлично от нуля, поэтому с ,а старшая часть, передаваемая в 10, отлична от

5 нуля и для определения порядка достаточно проанализировать число старших нулей старшей части,

Шифратор 31 предназначен для определения величины порядка г для нормализа0 ции результата и выдает значение, разное номеру разряда, занимаемое старшей единицы, в позиционном и унитарном коде.

Группа элементов ИЛИ 33 предназначена для объединения соответствующих раз5 рядов, полученных в результате сдвига и формирования мантиссы результата.

Блок управления 7 может быть реализован как устройство микропрограммного управления. Блок 7 содержит тактовый генератор запуск которого возможен по переднему фронту сигнала синхронизации как слова, так и массива. Этот сигнал является пусковым сигналом, а соответствующая шина пусковой шиной,

Работа устройства основана на исполь- зовании представления чисел в форме с циклической запятой или с плавающим началом, предназначенного для управления операции сложения чисел с плавающей запятой.

Представление с плавающим началом для числа X имеет вид

Р -1

q, где: q / и А - мантисса.

Пусть m некоторое целое (например, m - равно числу разрядов мантиссы без знака).

Тогда главный порядок определяется как,

Р -1 К Е , а локальный как

r res(),(1)

m

где или 1, а - целая (положительная или отрицательная) часть (ближайшее мень- шее число), q - основание системы счисления.

Такое предложение позволяет располагать на одних и тех же позициях разряды мантиссы, отличающиеся друг от друга по порядку на величину, кратную т. Будем считать в дальнейшем . При этом m+r.

Представление чисел в форме с плавающим началом позволяет осуществить сложе- ние аналогично представлению с фиксированной запятой без выравнивания порядков и сдвига слагаемых.

Рассмотрим конкретное число X. Его код мантиссы занимает на разрядной оси позицию, характеризующуюся парой (К, Р), где

К , .

Например для чисел

,1

,12

,15

,15

Таким образом, г - равно числу старших разрядов, расположенных левее запятой.

Запишем , где

Разрядная ось содержит Pmax+m-Pmin разрядных позиций

5 0

5

0

5

0

5

0

5

0

5

Иногда используется эквивалентное представление с целочисленной мантиссой т.е.

m

О , которое полностью эквивалентно предыдущему. Это представление с целочисленной мантиссой будет использовано в числовых примерах;

Алгоритмы преобразования чисел

Алгоритм преобразования чисел, представленных в форме с плавающей запятой в форму с циклической запятой назовем алгоритмом расщепления, а обратного - алгоритмом объединения.

Расщепление кода является разложением на два отдельных кода, Объединение кодов является обратной операцией и объединяет коды в том случае, когда старший значащий разряд младшего кода (А2) является следующим по порядку, т.е. имеющим на единицу меньше порядок, чем младший разряд старшего кода (А1).

1.Алгоритм расщепления чисел (мантисса в дополнительном коде) состоит в следующем:

Числа вида (Р, SA), где: S - знак, А - мантисса, Р - порядок, расщепляются на два кода следующим образом:

- производится сдвиг кода SA вправо на m-r разрядов, причем сдвиг производится с расширением знака.

Полученный код разбивается на 2 части по гп разрядов (т+1 разряд знака):

старшая: SSS ... (ЗАч)

младшая О (А2) 000.

Эти полученные два кода могут обрабатываться независимо.

2.Алгоритм объединения кодов.

При объединении двух частей в один код возможны различные комбинации знаков, поскольку оба кода обрабатываются независимо. Возможны все 4 случая, соответствующие разным комбинациям знаков.

Можно показать, что объединение т+1 - разрядных кодов SiAi и $2А2 образует 2т+1 разрядный код , если одновременно не выполнены два условия:

(2) ISi имеет вид 00 .. 01 и SiS2+SiS2 1

Если условия (2) выполняются одновременно, то это особый случай. При этом обнуляется ячейка содержащая Аь изменяется знак Аа и производится повторный анализ.

Анализ признаков .. 01, Si и S2 выполняется при считывании данных из накопителя 8 и при необходимости изменяется порядок выполнения переходов при выполнении микрокоманд в блоке 7.

В результате операции накопления чисел в ячейках накопителя 9 будут расположены числа, имеющие порядок, определяющийся адресом ячейки.

В большинстве случаев две старших ячейки с достаточной точностью полностью представляют результат накопления, если же выполнено (2), что необходим дополнительный анализ.

Для формирования результата:

1.Обнаруживают старшую с отличным от нуля содержимым ячейку и определяют ее адрес (это выполняет анализатор и результат формируется на выходе шифратора 23)

2.Проверяют условие (2), если оно не выполнено, что по содержимому двух старших ячеек формируется окончательный результат.

3.Если условие (2) выполнено, то проводится преобразование данных в двух старших ячейках, при этом содержимое старшей ячейки игнорируется, определяется содержимое следующих двух ячеек, после этого измеряется знак старшей из этих двух ячеек в блоке суммирования 8 и при необходимости повторяется процедура начиная, с п. 1.

Устройство работает следующим образом.

На вход 4 пуска начала проходит сигнал, по фронту которого инициируется работа устройства. Этот сигнал проходит на блок управления 7, который может содержать управляемый тактовый генератор (возможна инициация фронтом сигнала 3).

При необходимости в программу может быть заложено формирование сигнала готовности 15.

Поступающие по шинам 1 и 2 порядок и мантисса очередного числа сопровождаются сигналом синхронизации числа.

Блок анализа порядка 5 формирует коды К и г в соответствии с соотношением (1).

Код г поступает на информационный вход сдвигателя в блоке преобразования мантиссы.

Код главного порядка К поступает на входы формирователя адреса 11.

В формирователе адреса 11 адреса формируются последовательные адреса a+k и a+k+1, где: а - базовый адрес, поступающий из блока управления.

В зависимости от четности К старшая и младшая часть кода двойной разрядности заносятся непосредственно или после перестановки в соответствующие части блока 9.

Если нет переноса, то операция добавления данного числа закончена и устройства переходит к приему накопления следующего числа.

Если есть перенос, то выполняется добавление переносов, причем формирователь адреса 11 формирует адрес, увеличенный на 1,

В анализаторе 12 каждый триггер групп 22.1 и 22.2 соответствует одной ячейке накопителя 9, причем ее адрес соответствует

0 значению главного порядка К. Первоначально триггеры установлены в О сигналом 26, поступающим из блока управления 7. При записи в накопитель 9 схемами 28.1 (28.2) анализируется равенство кодов нулю, и, со5 ответственно, устанавливается соответствующий триггер 22.1 ил и 22.2 (единица-при нулевом коде, и нуль - а противном случае) с помощью дешифраторов 17.1 (17.2), которые дублируют дешифраторы адреса нако0 пителя 9 и обеспечивают при каждом выполнении операции записи в накопитель 9.

Одна группа триггеров, как и один блок памяти, хранит четные адреса, другая - не5 четные. В соответствии с этим выходы триггеров присоединены к соответствующим входам шифратора 23 (блок левой единицы), который показывает адрес самой старшей ячейки, содержимое которой отлично от

0 нуля.

Формирование результата начинается с определения адреса старшей ячейки, содержимое которой отлично от нуля с помощью шифратора 23, включенного на выходе па5 мяти 22 анализатора 12, который является индикатором содержимого ячеек триггера. Если коды в выбранной паре ячеек соответствуют особому случаю, то перед процедурой объединения кодов знак Si старшей

0 ячейки присваивается знаку младшей, старшая ячейка обнуляется и выбирается следующая пара ячеек, соответствующая К-1.

Формирование результата имеет следующие особенности.

5

Для формирования правильного результата на линию от 29-1 должно быть передано содержимое старшей записанной ячейки накопителя 9, а на линию от 29.2 - содержи0 мое предыдущей ячейки. Для этого предусматривается возможность перестановки кодов. Изменение мантиссы по соотношению выполняется на блоке суммирования 8.

5На фиг. 4 и 5 приведена схема алгоритма иллюстрирующего работу устройства. На фиг. 4 показаны особенности формирования адресов в двух частях (соответственно, RAM1 и RAM2) накопителя 9, соответствующих двум т+1 разрядным частям кодов двоичной разрядности, используемых в тракте данных блоков 6, 8, 9 и 10, на фиг. 5 - диаграмма формирования результата.

Реализация изобретения позволяет производить накопление производительного количества чисел с плавающей запятой с меньшими ошибками округления с минимальными затратами времени на формирование результата.

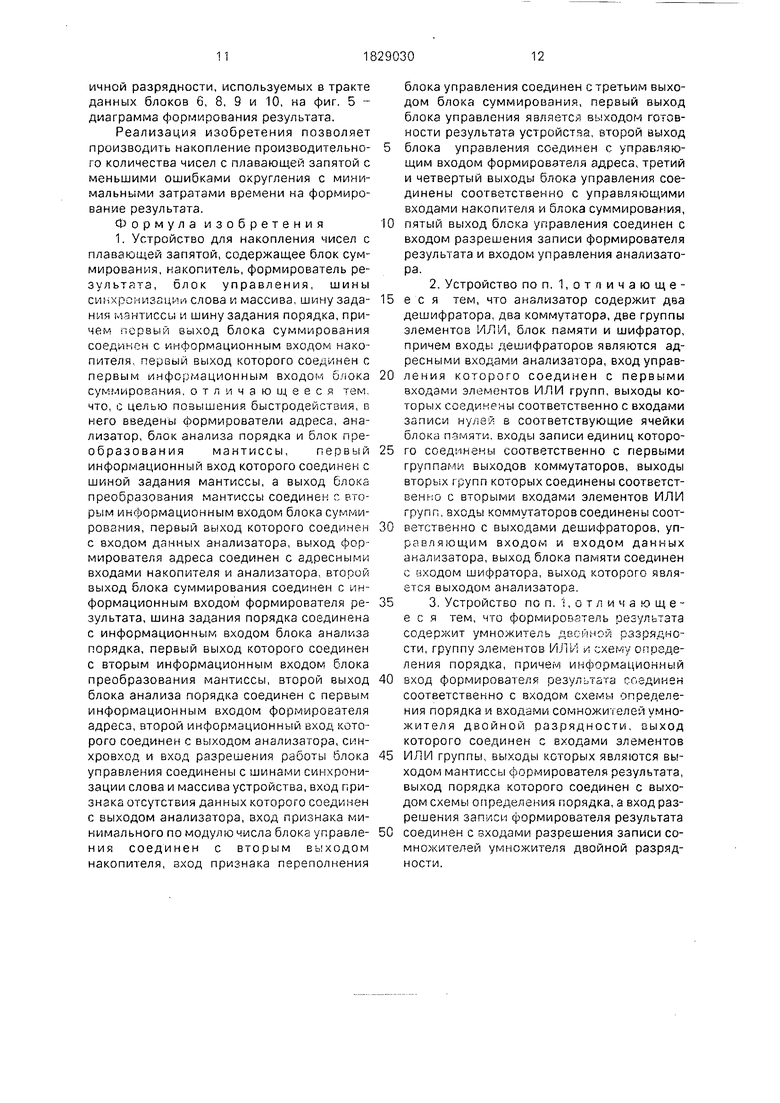

Формула изобретения 1. Устройство для накопления чисел с плавающей запятой, содержащее блок суммирования, накопитель, формирователь результата, блок управления, шины синхронизации слова и массива, шину задания мантиссы и шину задания порядка, причем первый выход блока суммирования соединен с информационным входом накопителя, первый выход которого соединен с первым информационным входом блока суммирования, отличающееся тем, что, с целью повышения быстродействия, в него введены формирователи адреса, анализатор, блок анализа порядка и блок преобразования мантиссы, первый информационный вход которого соединен с шиной задания мантиссы, а выход блока преобразования мантиссы соединен с вторым информационным входом блока суммирования, первый выход которого соединен с входом данных анализатора, выход формирователя адреса соединен с адресными входами накопителя и анализатора, второй выход блока суммирования соединен с информационным входом формирователя результата, шина задания порядка соединена с информационным входом блока анализа порядка, первый выход которого соединен с вторым информационным входом блока преобразования мантиссы, второй выход блока анализа порядка соединен с первым информационным входом формирователя адреса, второй информационный вход которого соединен с выходом анализатора, син- хровход и вход разрешения работы блока управления соединены с шинами синхронизации слова и массива устройства, вход признака отсутствия данных которого соединен с выходом анализатора, вход признака минимального по модулю числа блока управления соединен с вторым выходом накопителя, вход признака переполнения

блока управления соединен с третьим выходом блока суммирования, первый выход блока управления является выходом готовности результата устройства, второй выход

блока управления соединен с управляющим входом формирователя адреса, третий и четвертый выходы блока управления соединены соответственно с управляющими входами накопителя и блока суммирования,

пятый выход блока управления соединен с входом разрешения записи формирователя результата и входом управления анализатора.

2. Устройство по п. 1,отличающеее я тем, что анализатор содержит два дешифратора, два коммутатора, две группы элементов ИЛИ, блок памяти и шифратор, причем входы дешифраторов являются адресными входами анализатора, входуправления которого соединен с первыми входами элементов ИЛИ групп, выходы которых соединены соответственно с входами записи нулей в соответствующие ячейки блока памяти, входы записи единиц которого соединены соответственно с первыми группами выходов коммутаторов, выходы вторых групп которых соединены соответственно с вторыми входами элементов ИЛИ групп, входы коммутаторов соединены соответственно с выходами дешифраторов, управляющим входом л входом данных анализатора, выход блока памяти соединен с входом шифратора, выход которого является выходом анализатора.

3. Устройство поп. 1,отличающее с я тем, что формирователь результата содержит умножитель двойной разрядности, группу элементов ИЛИ -л схему определения порядка, причем информационный

вход формирователя результата соединен соответственно с входом схемы определения порядка и входами сомножителей умножителя двойной разрядности, выход которого соединен с входами элементов

ИЛИ группы, выходы которых являются выходом мантиссы формирователя результата, выход порядка которого соединен с выходом схемы определения порядка, а вход разрешения записи формирователя результата

соединен с входами разрешения записи сомножителей умножителя двойной разрядности.

о

со о

О) (N

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Устройство для нормализации многоразрядных чисел | 1975 |

|

SU549807A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

Изобретение относится к вычислительной технике и может быть использовано в разработках специализированных процессоров. Цель изобретения - повышение быстродействия устройства. Устройство для накопления чисел с плавающей запятой содержит шину 1 задания порядка, шину 2 задания мантиссы, шины 3, 4 синхронизации слова и массива, блок 5 анализа порядка, блок6 преобразования мантиссы,блок управления, блок 8 суммирования, накопитель 9, формирователь 10 результата, формирователь 11 адреса, анализатор 12, выход 13 мантиссы результата, выход 14 порядка результата и выход 15 готовности результата, соединенные между собой функционально. 2 з.п.ф-лы, 5 ил.

Фиг.З

Переход к грорми - роданию резуль тата

R№lLatK-i : tiAMi ai-K-i +S2A i RAM2Јa - KAM2 La tKj t s//4/

flpt/ем яоЯогя

4UCJ7U

С Г /Р-/7 Ј LjfrJ

Р- к т

РащЕпление кода на $2A2

Чет

Нечет

MMira+Kli RAMifo+V+SiA, mild MJ: -8АН2 La Ф1 +32Аг

Фиг. -f

Фор.чиродание результата

Нахождение К адрвса старшей записанной ячейхи

Чтение

S//V. -KAMI (art)

52Аг: ЯАМ2(а + К-1)

JL

SfO

SfO

RAMIkttK): 0 tiAM2(atX-l),$i

S2 /

5

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4054787, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-07-23—Публикация

1990-09-05—Подача