Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределенных систем программного управления и многопроцессорных систем широкого класса.

Известна микроконтроллерная сеть, содержащая М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, каждый модуль которой включает блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, группу блоков модулей управления синхронизацией, мультиплексор каналов синхронизации, регистр конфигурации, первый и второй мультиплексоры, дешифратор каналов синхронизации, генератор сигналов управления синхронизацией, первую и вторую группы элементов И (патент РФ №2336556, МПК9 G06F 9/28, G06F 15/173, G06F 1/10; заявл. 17.04.2007, опубл. 20.10.2008. Бюл. №29).

Недостатком данной сети является невысокая скорость выполнения барьерной синхронизации (и, как следствие, недостаточное ее быстродействие при реализации параллельных алгоритмов управления) из-за последовательного характера активизации групп блоков модулей управления синхронизацией (групп барьеров).

Наиболее близкой к предлагаемому параллельному логическому мультиконтроллеру по технической сущности является логический мультиконтроллер с распределенным параллельно-конвейерным барьерным синхронизатором, содержащий М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры, М - число строк, включающий блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, первый элемент задержки, первую и вторую группы элементов И, группу блоков управления синхронизацией (патент РФ №2450328, МКП9 G06F 9/00; заявл. 15.02.2010, опубл. 10.05.2012. Бюл. №13).

Недостатком данного устройства является невысокое число синхронизируемых параллельных барьеров, а также низкая скорость барьерной синхронизации участков параллельных программ.

Технической задачей заявляемого изобретения является расширения области целесообразного применения устройства, за счет увеличения максимально возможного числа синхронизируемых параллельных барьеров, а также повышение скорости выполнения барьерной синхронизации участков параллельных программ, выполняющихся в различных модулях логического мультиконтроллера (контроллерах), за счет сокращения времени переключения между слоями синхронизации путем параллельного распространения «волн» тактовых импульсов от одного углового модуля через всю структуру к другому угловому модулю и одновременно в обратном направлении.

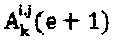

Техническая задача решается тем, что в каждый модуль параллельного логического мультиконтроллера, содержащей М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры параллельного логического мультиконтроллера, М - число строк, включающий блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, первый и второй элементы ИЛИ, буферный регистр, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, модуль синхронизатора, причем вход кода операции модуля соединен с первым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого соединен с адресным входом блока памяти программ, выход которого подключен к информационному входу регистра команд, первый выход которого соединен с адресным входом мультиплексора логических условий, а второй выход со вторым информационным выходом мультиплексора логических условий, первый информационный выход которого подключен к входу логических условий модуля, третий выход регистра команд объединен с выходом мультиплексора логических условий и подключен к первому входу блока элементов ИЛИ и к информационному входу буферного регистра, выход которого подключен ко второму входу блока элементов ИЛИ, выход которого соединен со вторым информационным входом коммутатора адреса, четвертый выход регистра команд подключен к выходу микроопераций модуля, пятый, шестой, седьмой и восьмой выходы регистра команд подключены к восьмому, двенадцатому, девятому и пятнадцатому входам модуля синхронизатора соответственно, девятый выход регистра команд подключен к третьему входу модуля синхронизатора, а также к входу первого одновибратора, выход которого соединен с третьим входом блока синхронизации, первый выход которого подключен к первому входу первого элемента ИЛИ, выход которого соединен с синхровходом регистра адреса, второй выход блока синхронизации подключен к входу сброса буферного регистра и второму входу второго элемента ИЛИ, выход которого соединен с синхровходом регистра команд, десятый выход регистра команд подключен к управляющим входам коммутатора адреса, первые информационные входы с первого по d-й (d - количество измерений контроллера) модуля синхронизатора соединены первыми выходами модулей синхронизаторов соседних модулей с первого по d-й, вторые тактовые входы с первого по d-й подключены к пятым выходам модулей синхронизаторов соседних модулей с первого по d-й, пятый и шестой вход модуля синхронизатора подключены к координатным входам модуля, седьмые информационные входы модуля синхронизатора с первого по d-й подключены к третьим выходам модулей синхронизаторов соседних модулей с первого по d-й, десятый информационный вход соединен со входом вектора соответствия модуля, одиннадцатый информационный вход подключен к входу максимального количества барьеров модуля, тринадцатые управляющие входы модуля синхронизатора с первого по d-й подключены к четвертым выходам модулей синхронизаторов соседних модулей с первого по d-й, четырнадцатый вход модуля синхронизатора соединен со входом тактовых импульсов модуля, первые выходы модуля синхронизатора с первого по d-й подключены к первым информационным входам модулей синхронизаторов соседних модулей с первого по d-й, второй выход модуля синхронизатора подключен к входу второго одновибратора и синхровходу буферного регистра, выход которого соединен с входом сброса регистра команд и вторым входам блока синхронизации, третьи выходы модуля синхронизатора с первого по d-й подключены к седьмым информационным входам модулей синхронизаторов соседних модулей с первого по d-й, пятые выходы модуля синхронизатора с первого по d-й соединены со вторыми входами модулей синхронизаторов соседних модулей с первого по d-й, четвертые выходы модуля синхронизатора с первого по d-й соединены с тринадцатыми входами модулей синхронизаторов соседних модулей с первого по d-й, первый вход блока синхронизации подключен к входу пуска модуля, вход настройки модуля соединен со вторым входом первого элемента ИЛИ, четвертым входом модуля синхронизатора, а также со входом элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ, модуль синхронизатора содержит с первого по четвертый блоки элементов И, группу блоков элементов ИЛИ-НЕ с первого по d-й, первый и второй блок элементов ИЛИ-НЕ, первый и второй блок элементов ИЛИ, блок элементов И-НЕ, с первого по шестой элемент И, с первого по четвертый элемент ИЛИ, группа блоков буферных элементов с первого по р-й (р=q/n, где q - максимальное число барьеров в реализуемых программах, а n - число физических разрядов параллельного логического мультиконтроллера), блок буферных элементов, с первого по третий триггер, первый и второй блок мультиплексоров, первый и второй блок демультиплексоров, с первого по третий дешифраторы, первый и второй одновибраторы, первый и второй регистр текущего физического разряда параллельного логического мультиконтроллера, регистр максимального количества барьеров в одном физическом разряде, первый и второй регистр текущего барьера, первый и второй счетчики, регистр вектора соответствия, первый и второй компараторы, блок монтажного ИЛИ с первого по р-й, первая и вторая группа регистров значений функций, причем любой блок содержит с первого по n-й элемент, кроме блоков демультиплексоров, которые содержат с первого по n+1 демультиплексоров, первые входы элементов И из первого блока подключены к первым входам модуля синхронизатора таким образом, что первый разряд первого входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов первого элемента И в первом блоке, второй разряд первого входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов второго элемента И в первом блоке, и так далее до n-ого разряда первого входа из группы первых входов модуля синхронизатора, который подключен к первому входу из группы первых входов n-ого элемента И в первом блоке, аналогично подключены остальные разряды по n-й с первого по n-й вход группы первых входов модуля синхронизатора, который подключен к n-м входам из группы первых входов блока элементов И, выходы которого соединены с информационными входами первого блока демультиплексоров таким образом, что выход первого элемента И из первого блока подключен к информационному входу первого демультиплексора из первого блока, выход второго элемента И из первого блока подключен к информационному входу второго демультиплексора из первого блока, а выход n-ого элемента И из первого блока подключен к информационному входу n-ого демультиплексора из первого блока, первые разряды выходов демультиплексоров из первого блока подключены к информационному входу первого регистра из первой группы регистров значений функций, вторые разряды выходов демультиплексоров из первого блока подключены к информационному входу второго регистра из первой группы регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из первого блока, который подключен к информационному входу р-ого регистра из первой группы регистров значений функций, первый разряд n+1-ого демультиплексора из первого блока подключен к синхровходу первого регистра из первой группы регистров значений функций, второй выход n+1-ого демультиплексора из первого блока подключен к синхровходу второго регистра из первой группы регистров значений функций и так далее до р-ого разряда n+1-ого демультиплексора из первого блока, который подключен к синхровходу р-ого регистра из первой группы регистров значений функций, с первого по n-й разряды выхода первого регистра первой группы регистров значений функций соединены с первыми разрядами информационных входов с первого по n-й мультиплексоров первого блока соответственно, с первого по n-й разряды выхода второго регистра первой группы регистров значений функций соединены со вторыми разрядами информационных входов с первого по n-й мультиплексоров первого блока соответственно и так далее до с первого по n-й разряды выхода р-ого регистра первой группы регистров значений функций, которые соединены с р-ми разрядами информационных входов с первого по n-й мультиплексоров первого блока соответственно, выходы с первого по n-й мультиплексоров подключены к первым входам с первого по n-й элементов И второго блока соответственно, а также к первому и второму входам с первого по n-й элементов ИЛИ-НЕ первого блока соответственно, выходы которых подключены к информационным входам с первого по n-й буферных элементов первого блока, выходы которого подключены к первым и вторым входам всех элементов ИЛИ-НЕ из группы блоков элементов ИЛИ-НЕ, группа вторых входов третьего элемента И соединена с группой вторых входов модуля синхронизатора, выход третьего элемента И подключен к входу первого одновибратора, выход которого подключен к информационному входу n+1-ого демультиплексора первого блока демультиплексоров, к входу инкремента первого счетчика, а также к второму входу третьего элемента ИЛИ, выход которого подключен ко всем выходам пятой группы выходов модуля синхронизатора, третий вход модуля синхронизатора подключен к синхровходу третьего триггера, четвертый вход модуля синхронизатора подключен ко всем входам сброса первой и второй группы всех регистров значений функций, первого триггера, второго триггера, первого и второго регистра текущего физического разряда параллельного логического мультиконтроллера, регистра максимального количества барьеров в одном физическом разряде, первого и второго регистра текущего барьера, первого и второго счетчика, регистра вектора соответствия, а также к первому входу первого элемента ИЛИ, выход которого подключен к входу сброса третьего триггера, прямой выход которого подключен к первым входам всех элементов И третьего блока элементов И, к первому входу второго элемента И, а также к первому входу первого элемента И, выход которого подключен к управляющему входу второго дешифратора, вход установки первого триггера подключен к пятому входу модуля синхронизатора, прямой выход первого триггера соединен со всеми управляющими входами буферных элементов блока буферных элементов, а также с первым входом шестого элемента И, выход которого подключен к первому входу четвертого ИЛИ, выход которого подключен ко всем четвертым выходам модуля синхронизатора, вход установки второго триггера подключен к шестому входу модуля синхронизатора, прямой выход второго триггера соединен с вторыми входами всех элементов И четвертого блока элементов И, а также первого входа пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, группа блоков элементов ИЛИ-НЕ подключена к группе седьмых входов таким образом, что первый блок в группе блоков элементов ИЛИ-НЕ подключен к первому входу из группы седьмых входов, причем первый разряд входа подключен к первому и второму входу первого элемента в первом блоке группы блоков элементов ИЛИ-НЕ, второй разряд входа подключен к первому и второму входу второго элемента в первом блоке группы блоков элементов ИЛИ-НЕ, и так далее до n-ого разряда входа, который подключен к первому и второму входу n-ого элемента в первом блоке группы блоков элементов ИЛИ-НЕ, остальные входы блоков по n-й блок элементов ИЛИ-НЕ подключаются аналогично, выходы группы блоков элементов ИЛИ-НЕ соединяются с блоком элементов И-НЕ таким образом, что выходы с первого по n-й первого блока в группе блоков элементов ИЛИ-НЕ подключены к первым входам с первого по n-й элементов И-НЕ в блоке элементов И-НЕ, выходы с первого по n-й второго блока в группе блоков элементов ИЛИ-НЕ подключены ко вторым входам с первого по n-й элементов И-НЕ в блоке элементов И-НЕ и так далее, до n-ого блока в группе блоков элементов ИЛИ-НЕ, у которого выходы с первого по n-й подключены к n-м входам с первого по n-й элементов И-НЕ в блоке элементов И-НЕ, выходы которого соединены с информационными входами второго блока демультиплексоров таким образом, что выход первого элемента И-НЕ из блока подключен к информационному входу первого демультиплексора из блока, выход второго элемента И-НЕ из блока подключен к информационному входу второго демультиплексора из второго блока, а выход n-ого элемента И-НЕ из блока подключен к информационному входу n-ого демультиплексора из блока, первые разряды выходов демультиплексоров из второго блока подключены к информационным входам первого регистра из второй группы регистров значений. функций, вторые разряды выходов демультиплексоров из второго блока подключены к информационным входам второго регистра из второй группы регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из второго блока, который подключен к информационным входам р-ого регистра из второй группы регистров значений функций, первый разряд n+1-ого демультиплексора из второго блока подключен к синхровходу первого регистра из второй группы регистров значений функций, второй n+1-ого демультиплексора из второго блока подключен к синхровходу второго регистра из второй группы регистров значений функций и так далее до р-ого разряда n+1-ого демультиплексора из второго блока, который подключен к синхровходу р-ого регистра из второй группы регистров значений функций, с первого по n-й разряды выхода первого регистра второй группы регистров значений функций соединены с первыми разрядами информационных входов с первого по n-й мультиплексоров второго блока соответственно, с первого по n-й разряды выхода второго регистра второй группы регистров значений функций соединены со вторыми разрядами информационных входов с первого по n-й мультиплексоров второго блока соответственно и так далее до с первого по n-й разряды выхода р-ого регистра второй группы регистров значений функций, которые соединены с р-ми разрядами информационных входов с первого по n-й мультиплексоров второго блока соответственно, выходы с первого по n-й мультиплексоров второго блока мультиплексоров подключены ко вторым входам с первого по n-й элементов третьего блока элементов И, ко всем третьим выходам модуля синхронизатора, к первым и вторым входам с первого по n-й элементов второго блока элементов ИЛИ-НЕ, выходы которых подключены к первым входам с первого по n-й элементов четвертого блока элементов И, выходы которых подключены к первым входам с первого по n-й элементов первого блока элементов ИЛИ, выходы которого подключены к третьим входам с первого по n-й элементов первого блока элементов И, инверсный выход второго триггера соединен со вторыми входами с первого по n-й элементов первого блока элементов ИЛИ, а также к первому входу третьего элемента И, информационный вход первого регистра текущего физического разряда параллельного логического мультиконтроллера соединен с восьмым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу первого регистра текущего физического разряда параллельного логического мультиконтроллера, выход которого подключен к информационному входу второго дешифратора, выходы которого с первого по n-й соединены со вторыми входами с первого по n-й элементов второго блока элементов ИЛИ, выходы которого подключены к вторым входам с первого по n-й элементов первого блока элементов И, информационный вход второго регистра текущего физического разряда параллельного логического мультиконтроллера соединен с девятым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу второго регистра текущего физического разряда параллельного логического мультиконтроллера, выход которого подключен к информационному входу третьего дешифратора, выходы которого с первого по n-й соединены с третьими входами с первого по n-й элементов третьего блока элементов И, выходы которого соединены со входами второго элемента ИЛИ, выход которого подключен к второму выходу модуля синхронизатора, а также к входу первого элемента ИЛИ, информационный вход регистра вектора соответствия соединен с десятым входом модуля синхронизатора, причем старший разряд десятого входа модуля синхронизатора подключен к синхровходу регистра вектора соответствия, выходы которого подключены к информационным входам группы блоков буферных элементов таким образом, что с первого по n-й разряд первого выхода регистра вектора соответствия подключается к информационным входам с первого по n-й буферным элементам первого блока группы блоков буферных элементов, с второго по р-й выходы регистра вектора соответствия подключаются к информационным входам с второго по р-й блоков группы блоков буферных элементов аналогично, выходы группы блоков буферных элементов коммутируются блоком монтажного ИЛИ, выходы которого с первого по n-й подключаются ко вторым входам с первого по n-й элемент первого блока элементов И, информационный вход регистра максимального количества барьеров в одном физическом разряде соединен с одиннадцатым входом модуля синхронизатора, причем старший разряд одиннадцатого входа модуля синхронизатора подключен к синхровходу регистра максимального количества барьеров в одном физическом разряде, выход которого подключен к информационному входу второго счетчика, а также информационному входу первого счетчика, выход которого подключен к информационному входу первого дешифратора, управляющим входам с первого по n+1-й демультиплексоров первого блока демультиплексоров, к управляющим входам с первого по n-й мультиплексоров первого блока мультиплексоров, а также к первому информационному входу первого компаратора, выход которого подключен ко второму входу первого элемента И, с первого по р-й выход первого дешифратора соединены с управляющими входами с первого по р-й блоков группы блоков буферных элементов, выход второго счетчика подключен к управляющим входам с первого по n+1-й демультиплексоров второго блока демультиплексоров, к управляющим входам с первого по n-й мультиплексоров второго блока мультиплексоров, а также к второму информационному входу второго компаратора, выход которого подключен ко второму входу второго элемента И, выход которого подключен к управляющему входу третьего дешифратора, информационный вход первого регистра текущего барьера соединен с двенадцатым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу первого регистра текущего барьера, выход которого подключен к второму информационному входу первого компаратора, группа вторых входов четвертого элемента И соединена с группой тринадцатых входов модуля синхронизатора, выход четвертого элемента И подключен к входу второго одновибратора, выход которого подключен к информационному входу n+1-ого демультиплексора второго блока демультиплексоров, к входу инкремента второго счетчика, а также к второму входу четвертого элемента ИЛИ, инверсный выход первого триггера подключен к первому входу четвертого элемента И, а также к вторым входам с первого по n-й элемент второго блока элементов И, выходы которого подключены ко всем первым выходам модуля синхронизатора, вторые входы пятого и шестого элемента И подключены к четырнадцатому входу модуля синхронизатора, информационный вход второго регистра текущего барьера соединен с пятнадцатым входом модуля синхронизатора, причем старший разряд пятнадцатого входа модуля синхронизатора подключен к синхровходу второго регистра текущего барьера, выход которого подключен первому информационному входу второго компаратора, к информационному входу третьего триггера подключен сигнал логической единицы.

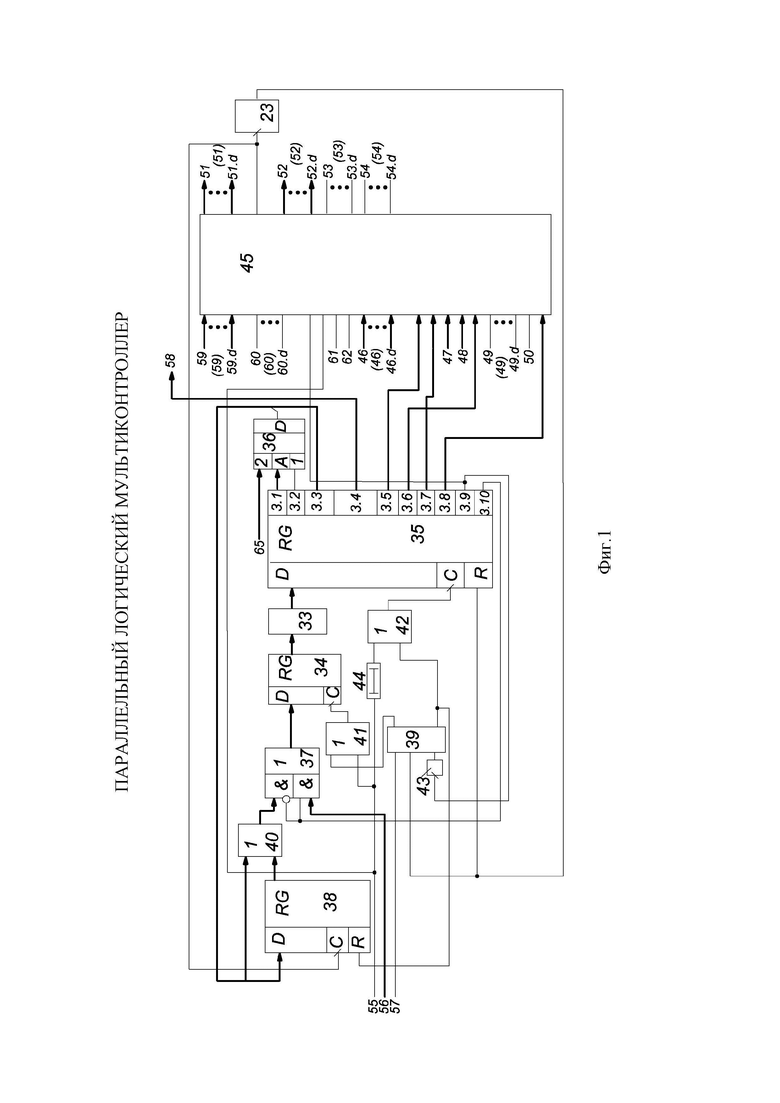

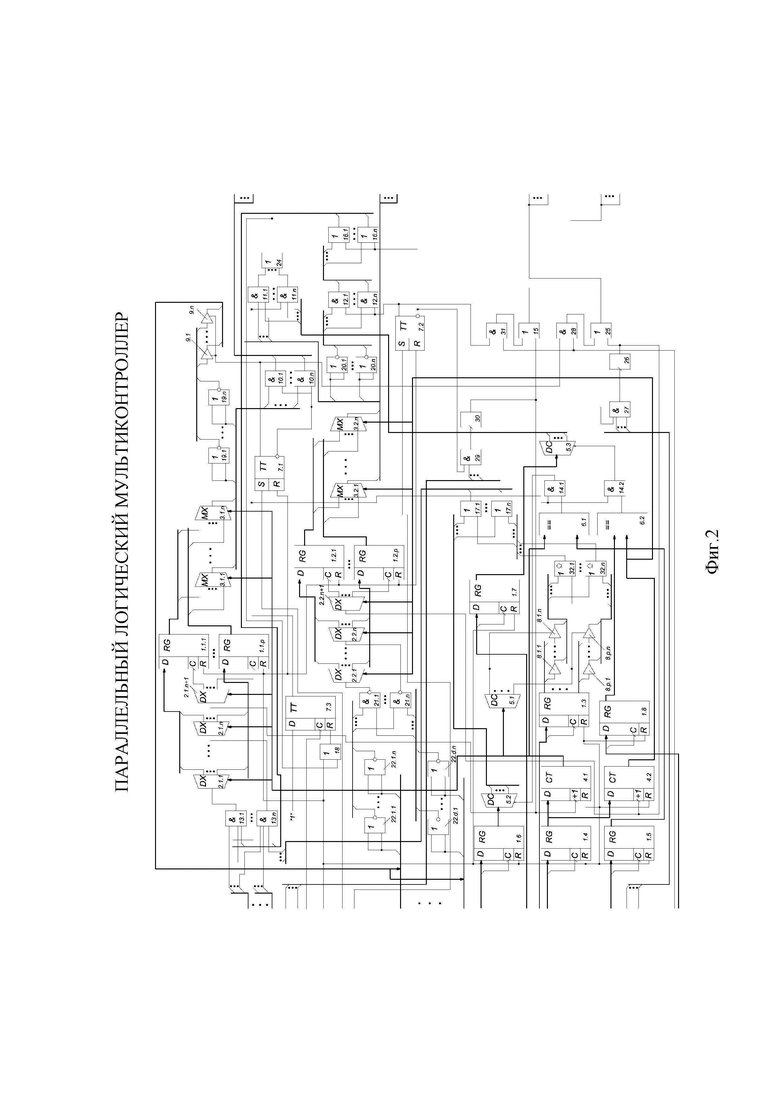

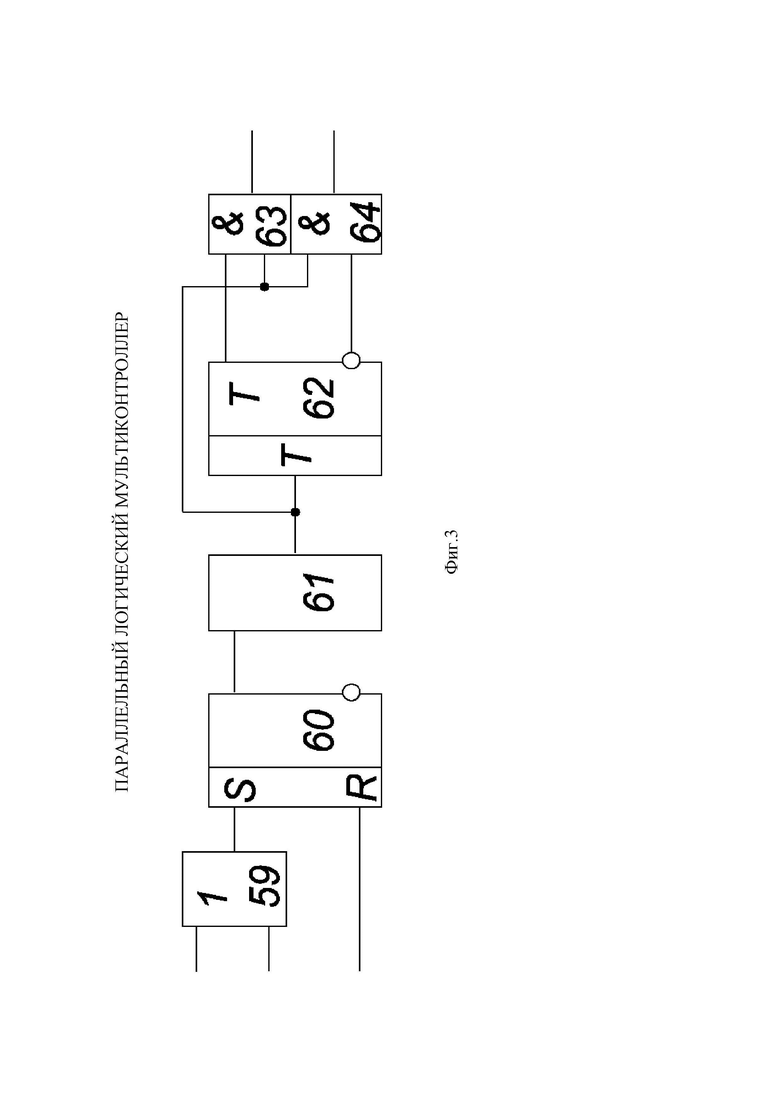

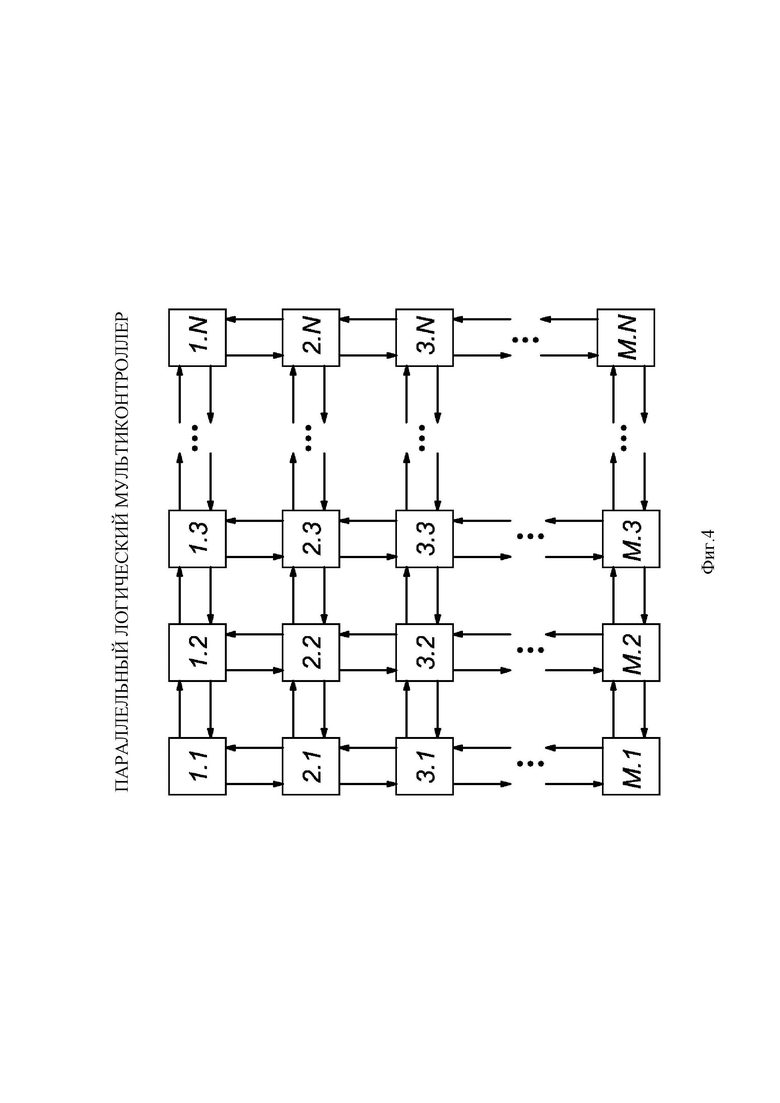

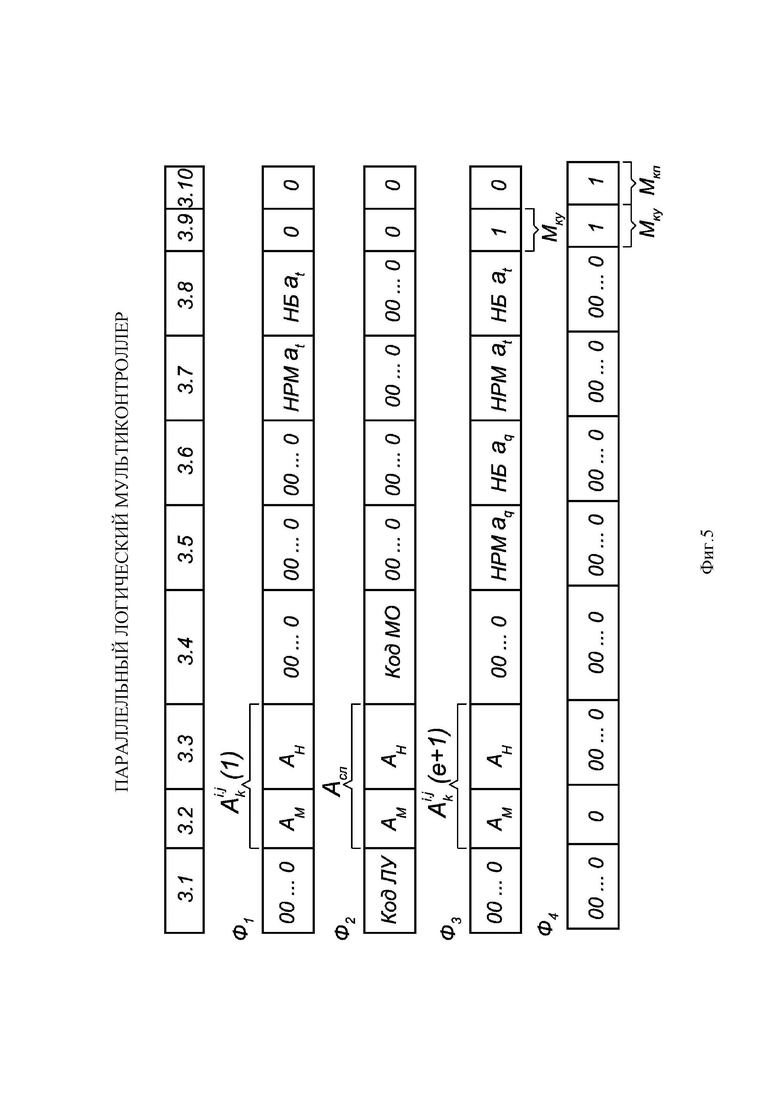

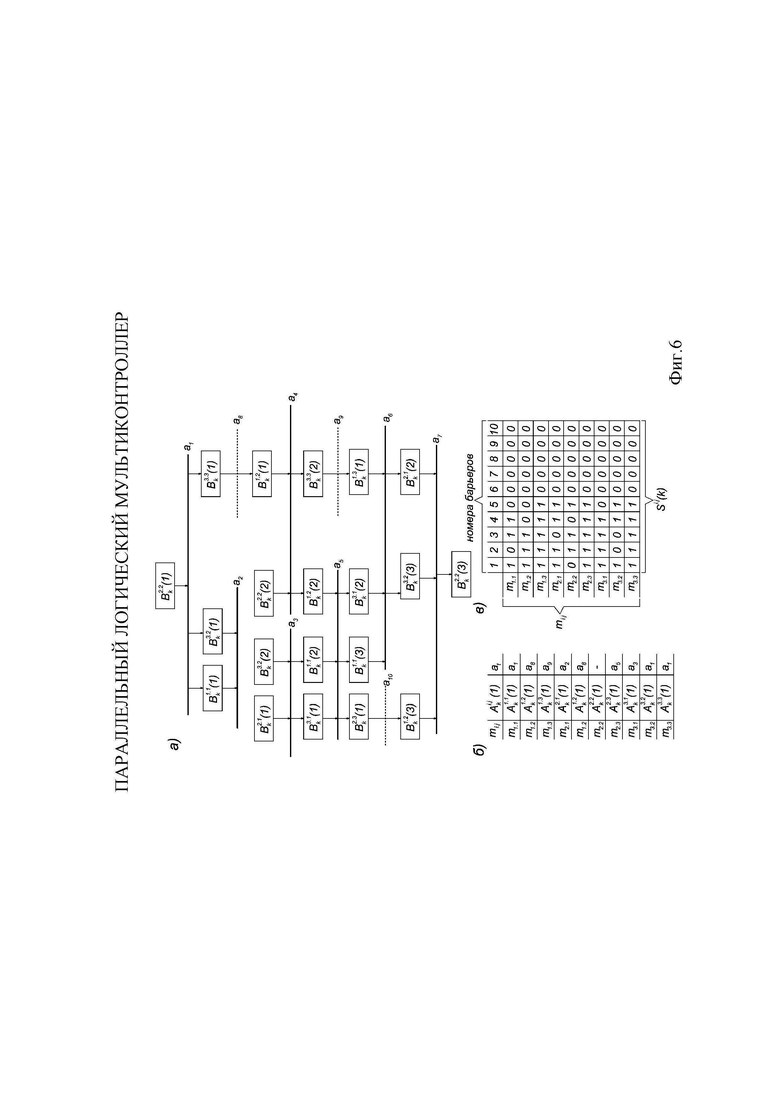

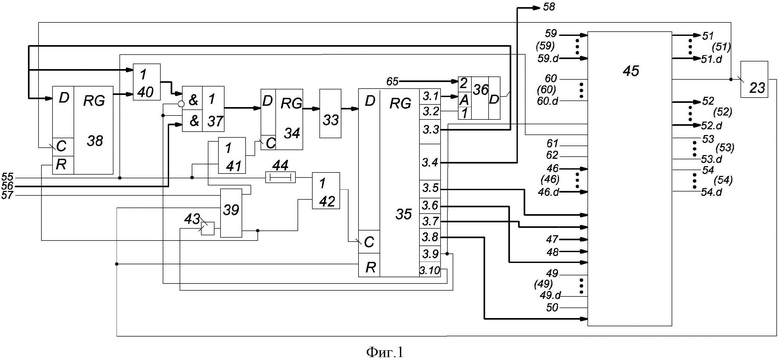

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема модуля параллельного логического мультиконтроллера (ПЛМК), на фиг. 2 изображена функциональная схема модуля синхронизатора, на фиг 3 представлена схема блока синхронизации, на фиг. 4 дана структурная схема ПЛМК, на фиг. 5 приведены форматы (микро)команд, реализуемые ПЛМК, на фиг. 6 представлен иллюстративный пример, поясняющий принципы реализации параллельных алгоритмов (программ) в ПЛМК.

Модуль ПЛМК (фиг. 1) включает блок 33 памяти программ, регистр 34 адреса, регистр 35 команд, мультиплексор 36 логических условий, коммутатор 37 адреса, блок 39 синхронизации, первый 41, второй 42 элементы ИЛИ, буферный регистр 38, блок элементов ИЛИ 40, первый 43 и второй 23 одновибраторы, элемент 44 задержки, модуль 45 синхронизатора, причем вход 56 кода операции модуля соединен с первым информационным входом коммутатора 37 адреса, выход которого подключен к информационному входу регистра 34 адреса, выход которого подключен к адресному входу блока 33 памяти программ, выход которого соединен с информационным входом регистра 35 команд, выходы 3.1 кода логического условия и 3.2 модифицируемого разряда адреса регистра 35 команд подключены к адресному и первому информационному входам мультиплексора 36 логических условий, второй информационный вход которого соединен со входом 65 логических условий модуля, выход 3.3 регистра 35 команд объединен с выходом мультиплексора 36 логических условий и подключен к первому входу блока элементов ИЛИ 40 и к информационному входу буферного регистра 38, выход которого подключен ко второму входу блока элементов ИЛИ 40. выход которого соединен со вторым информационным входом коммутатора 37 адреса, выход 3.4 регистра команд подключен к выходу 58 микроопераций модуля, выходы 3.5, 3.6, 3.7 и 3.8 регистра 35 команд подключены к восьмому, двенадцатому, девятому и пятнадцатому входам модуля 45 синхронизатора соответственно, выход 3.9 регистра команд подключен к третьему входу модуля 45 синхронизатора, а также к входу одновибратора 43, выход которого соединен с третьим входом блока 39 синхронизации, первый выход которого подключен к первому входу элемента ИЛИ 41, выход которого соединен с синхровходом регистра 34 адреса, второй выход блока 39 синхронизации подключен к входу сброса буферного регистра 38 и второму входу элемента ИЛИ 42, выход которого соединен с синхровходом регистра 35 команд, выход 3.10 регистра 35 команд подключен к управляющим входам коммутатора 37 адреса, информационные входы 59 с первого по d-й модуля 45 синхронизатора соединены выходами 51 модулей синхронизаторов соседних модулей с первого по d-й, тактовые входы 60 с первого по d-й подключены к выходам 54 модулей синхронизаторов соседних модулей с первого по d-й, входы 61 и 62 модуля 45 синхронизатора подключены к координатным входам модуля, информационные входы 46 модуля 45 синхронизатора с первого по d-й подключены к выходам 52 модулей синхронизаторов соседних модулей с первого по d-й, информационный вход 47 модуля 45 синхронизатора соединен со входом вектора соответствия модуля, информационный вход 48 модуля 45 синхронизатора подключен к входу максимального количества барьеров модуля, управляющие входы 49 модуля 45 синхронизатора с первого по d-й подключены к выходам 53 модулей синхронизаторов соседних модулей с первого по d-й, вход 50 модуля синхронизатора соединен со входом тактовых импульсов модуля, выходы 52 модуля 45 синхронизатора с первого по d-й подключены к информационным входам 59 модулей синхронизаторов соседних модулей с первого по d-й, второй выход модуля 45 синхронизатора подключен к входу одновибратора 23, выход которого соединен с входом сброса регистра 35 команд и вторым входам блока 39 синхронизации, и синхровходу буферного регистра 38, выходы 52 модуля 45 синхронизатора с первого по d-й подключены к информационным входам 46 модулей синхронизаторов соседних модулей с первого по d-й, выходы 54 модуля 45 синхронизатора с первого по d-й соединены со входами 60 модулей 45 синхронизаторов соседних модулей с первого по d-й, выходы 53 модуля 45 синхронизатора с первого по d-й соединены со входами 49 модулей синхронизаторов соседних модулей с первого по d-й, первый вход блока 39 синхронизации подключен к входу 57 пуска модуля, вход 55 настройки модуля соединен со вторым входом элемента ИЛИ 41, четвертым входом модуля 45 синхронизатора, а также со входом элемента задержки 44, выход которого подключен к второму входу элемента ИЛИ 42.

Модуль синхронизатора (фиг. 2) содержит блоки 13, 10, 11, 12 элементов И, блок 21 элементов И-НЕ, элементов группу 22 блоков элементов ИЛИ-НЕ, блоки 19, 20 элементов ИЛИ-НЕ, блоки 11, 16 элементов ИЛИ, элементы 14.1, 14.2, 29, 27, 31, 28 И, элементы 18, 24, 15, 25 ИЛИ, группа 8 блоков буферных элементов, блок 9 буферных элементов, триггеры 7.1, 7.2, 7.3, блоки 3.1, 3.2 мультиплексоров, блоки 2.1, 2.2 демультиплексоров, дешифраторы 5.1, 5.2, 5.3, одновибраторы 30, 26, регистры 1.6, 1.7 текущего физического разряда ПЛМК, регистр 1.4 максимального количества барьеров в одном физическом разряде, регистры 1.5, 1.8 текущего барьера, счетчики 4.1, 4.2, регистр 1.3 вектора соответствия, компараторы 6.1, 6.2, блок 32 монтажного ИЛИ, группы 1.1, 1.2 регистров значений функций, первые входы элементов И из первого блока 13 элементов И подключены к первым входам модуля синхронизатора таким образом, что первый разряд входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов элемента И 13.1 в блоке 13, второй разряд первого входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов элемента И 13.2 в блоке 13, и так далее до n-ого разряда первого входа из группы первых входов модуля синхронизатора, который подключен к первому входу из группы первых входов элемента И 13.n в блоке 13, аналогично подключены остальные разряды по n-й с первого по d-й вход группы первых входов модуля синхронизатора, который подключен к d-м входам из группы первых входов блока 13 элементов И, выходы которого соединены с информационными входами блока 2.1 демультиплексоров таким образом, что выход элемента И 13.1 из блока 13 подключен к информационному входу демультиплексора 2.1.1 из блока 2.1, выход элемента И 13.2 из блока 13 подключен к информационному входу демультиплексора 2.1.2 из блока 2.1, а выход элемента И 13.п из блока 13 подключен к информационному входу демультиплексора 2.1.п из блока 2.1, первые разряды выходов демультиплексоров из блока 2.1 подключены к информационному входу регистра 1.1.1 из группы 1.1 регистров значений функций, вторые разряды выходов демультиплексоров из блока 2.1 подключены к информационному входу регистра 1.1.2 из группы 1.1 регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из блока 2.1, который подключен к информационному входу регистра 1.1.р из группы 1.1 регистров значений функций, первый разряд демультиплексора 2.1.n+1 из блока 2.1 подключен к синхровходу регистра 1.1.1 из группы 1.1 регистров значений функций, второй выход демультиплексора 2.1.n+1 из блока 2.1 подключен к синхровходу регистра 1.1.2 из группы 1.1 регистров значений функций и так далее до р-ого разряда демультиплексора 2.1.n+1 из блока 2.1, который подключен к синхровходу регистра 1.1.р из группы 1.1 регистров значений функций, с первого по n-й разряды выхода регистра 1.1.1 группы 1.1 регистров значений функций соединены с первыми разрядами информационных входов с 3.1.1 по 3.1.п мультиплексоров блока 3.1 соответственно, с первого по n-й разряды выхода регистра 1.1.2 группы 1.1 регистров значений функций соединены со вторыми разрядами информационных входов с 3.1.1 по 3.1.п мультиплексоров блока 3.1 соответственно и так далее до с первого по n-й разряды выхода регистра 1.1.р группы 1.1 регистров значений функций, которые соединены с р-ми разрядами информационных входов с 3.1.1 по 3.1.п мультиплексоров блока 3.1 соответственно, выходы с 3.1.1 по 3.1.п мультиплексоров подключены к первым входам элементов И с 10.1 по 10.п блока 10 соответственно, а также к первому и второму входам элементов ИЛИ-НЕ с 19.1 по 19.п блока 19 соответственно, выходы которых подключены к информационным входам буферных элементов с 9.1 по 9.п блока 9, выходы которого подключены к первым и вторым входам всех элементов ИЛИ-НЕ из группы 22 блоков элементов ИЛИ-НЕ, группа вторых входов элемента И 29 соединена с группой вторых входов модуля синхронизатора, выход элемента И 29 подключен к входу одновибратора 30, выход которого подключен к информационному входу демультиплексора 2.1.п блока 2.1 демультиплексоров, к входу инкремента счетчика 4.1, а также к второму входу элемента ИЛИ 15, выход которого подключен ко всем выходам пятой группы выходов модуля синхронизатора, третий вход модуля синхронизатора подключен к синхровходу триггера 7.3, четвертый вход модуля синхронизатора подключен ко всем входам сброса группы 1.1, 1.2 регистров значений функций, триггера 7.1, триггера 7.2, регистров 1.6, 1.7 текущего физического разряда ПЛМК, регистра 1.4 максимального количества барьеров в одном физическом разряде, регистров 1.5, 1.8 текущего барьера, счетчиков 4.1, 4.2, регистра 1.3 вектора соответствия, а также к первому входу элемента ИЛИ 18, выход которого подключен к входу сброса триггера 7.3, прямой выход которого подключен к первым входам всех элементов И блока 11 элементов И, первому входу элемента И 14.2, а также к первому входу элемента И 14.1, выход которого подключен к управляющему входу дешифратора 5.2, вход установки триггера 7.1 подключен к пятому входу модуля синхронизатора, прямой выход триггера 7.1 соединен со всеми управляющими входами буферных элементов блока 9 буферных элементов, а также с первым входом элемента И 28, выход которого подключен к первому входу элемента ИЛИ 25, выход которого подключен ко всем четвертым выходам модуля синхронизатора, вход установки триггера 7.2 подключен к шестому входу модуля синхронизатора, прямой выход триггера 7.2 соединен с вторыми входами всех элементов И блока 12 элементов И, а также первого входа элемента И 31, выход которого соединен с первым входом элемента ИЛИ 15, группа 22 блоков элементов ИЛИ-НЕ подключена к группе седьмых входов таким образом, что блок 22.1 в группе 22 блоков элементов ИЛИ-НЕ подключен к первому входу из группы седьмых входов, причем первый разряд входа подключен к первому и второму входу элемента 22.1.1 в блоке 22.1 группы 22 блоков элементов ИЛИ-НЕ, второй разряд входа подключен к первому и второму входу элемента 22.1.2 в блоке 22.1 группы 22 блоков элементов ИЛИ-НЕ, и так далее до n-ого разряда входа, который подключен к первому и второму входу элемента 22.1.n в первом блоке 22.1 группы 22 блоков элементов ИЛИ-НЕ, остальные входы блоков по блок 22.а1 элементов ИЛИ-НЕ подключаются аналогично, выходы группы 22 блоков элементов ИЛИ-НЕ соединяются с блоком 21 элементов И-НЕ таким образом, что выходы с первого по n-й блока 22.1 в группе 22 блоков элементов ИЛИ-НЕ подключены к первым входам элементов И-НЕ в блоке 21 элементов И-НЕ с 21.1 по 21.n, выходы с первого по n-й блока 22.2 в группе блоков элементов ИЛИ-НЕ подключены к вторым входам элементов И-НЕ в блоке 21 элементов И-НЕ с 21.1 по 21.п и так далее, до блока 22.й в группе 22 блоков элементов ИЛИ-НЕ, у которого выходы с первого по n-й подключены к d-м входам элементов И-НЕ с 21.1 по 21.n в блоке 21 элементов И-НЕ, выходы которого соединены с информационными входами блока 2.2 демультиплексора таким образом, что выход элемента И-НЕ 21.1 из блока 21 подключен к информационному входу демультиплексора 2.2.1 из блока 2.2, выход элемента И-НЕ 21.2 из блока подключен к информационному входу демультиплексора 2.2.2 из блока 2.2, а выход элемента И-НЕ 21.n из блока 21 подключен к информационному входу демультиплексора 2.2.n из блока 2.2, первые разряды выходов демультиплексоров из блока 2.2 подключены к информационным входам регистра 1.2.1 из группы 1.2 регистров значений функций, вторые разряды выходов демультиплексоров из блока 2.2 подключены к информационным входам регистра 1.2.2 из группы 1.2 регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из блока 2.2, который подключен к информационным входам регистра 1.2.р из группы 1.2 регистров значений функций, первый разряд демультиплексора 2.2.n+1 из блока 2.2 подключен к синхровходу регистра 1.2.1 из группы 1.2 регистров значений функций, второй демультиплексора 2.1.n+1 из блока 2.1 подключен к синхровходу регистра 1.2.2 из группы 1.2 регистров значений функций и так далее до р-ого разряда демультиплексора 2.2.n из блока 2.2, который подключен к синхровходу регистра 1.2.р из группы 1.2 регистров значений функций, с первого по n-й разряды выхода регистра 1.2.1 группы 1.2 регистров значений функций соединены с первыми разрядами информационных входов мультиплексоров с 3.2.1 по 3.2.n блока 3.2 соответственно, с первого по n-й разряды выхода регистра 1.2.2 группы 1.2 регистров значений функций соединены со вторыми разрядами информационных входов мультиплексоров с 3.2.1 по 3.2.п блока 3.2 соответственно и так далее до с первого по n-й разряды выхода регистра 1.2.р группы 1.2 регистров значений функций, которые соединены с р-ми разрядами информационных входов мультиплексоров с 3.2.1 по 3.2.п второго блока соответственно, выходы мультиплексоров с 3.2.1 по 3.2.п подключены ко вторым входам элементов с 11.1 по 11.n блока 11 элементов И, ко всем третьим выходам модуля синхронизатора, к первым и вторым входам с элементов 20.1 по 20.n блока 20 элементов ИЛИ-НЕ, выходы которых подключены к первым входам элементов с 12.1 по 12.n блока 12 элементов И, выходы которых подключены к первым входам элементов с 16.1 по 16.n блока 16 элементов ИЛИ, выходы которого подключены к третьим входам с элементов с 13.1 по 13.n блока 13 элементов И, инверсный выход триггера 7.2 соединен со вторыми входами элементов с 16.1 по 16.n блока 16 элементов ИЛИ, а также к первому входу элемента И 31, информационный вход регистра 1.6 текущего физического разряда ПЛМК соединен с восьмым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу регистра 1.6 текущего физического разряда ПЛМК, выход которого подключен к информационному входу дешифратора 5.2, выходы которого с первого по n-й соединены cj вторыми входами элементов с 17.1 по 17.n блока 17 элементов ИЛИ, выходы которого подключены к вторым входам элементов с 13.1 по 13.n блока 13 элементов И, информационный вход регистра 1.7 текущего физического разряда ПЛМК соединен с девятым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу регистра 1.7 текущего физического разряда ПЛМК, выход которого подключен к информационному входу дешифратора 5.3, выходы которого с первого по n-й соединены с третьими входами элементов с 11.1 по 11.n блока 11 элементов И, выходы которого соединены с входами элемента ИЛИ 24, выход которого подключен к второму выходу модуля синхронизатора, а также к входу элемента ИЛИ 18, информационный вход регистра 1.3 вектора соответствия соединен с десятым входом модуля синхронизатора, причем старший разряд десятого входа модуля синхронизатора подключен к синхровходу регистра 1.3 вектора соответствия, выходы которого подключены к информационным входам группы 8 блоков буферных элементов таким образом, что с первого по n-й разряд первого выхода регистра 1.3 вектора соответствия подключается к информационным входам буферных элементов с 8.1.1 по 8.1.п блока 8.1 группы 8 блоков буферных элементов, с второго по р-й выходы регистра вектора соответствия подключаются к информационным входам группы 8 блоков с 8.2 по 8.р буферных элементов аналогично, выходы группы 8 блоков буферных элементов коммутируются блоком 32 монтажного ИЛИ, выходы которого подключаются к вторым входам элементов с 13.1 по 13.n блока 13 элементов И, информационный вход регистра 1.4 максимального количества барьеров в одном физическом разряде соединен с одиннадцатым входом модуля синхронизатора, причем старший разряд одиннадцатого входа модуля синхронизатора подключен к синхровходу регистра 1.4 максимального количества барьеров в одном физическом разряде, выход которого подключен к информационному входу счетчика 4.2, а также информационному входу счетчика 4.1, выход которого подключен к информационному входу дешифратора 5.1, управляющим входам демультиплексоров с 2.1.1 по 2.1.n блока 2.1 демультиплексоров, к управляющим входам мультиплексоров с 3.1.1 по 3.1.n блока 3.1 мультиплексоров, а также к первому информационному входу компаратора 6.1, выход которого подключен ко второму входу элемента И 14.1, с первого по р-й выход дешифратора 5.1 соединены с управляющими входами блоков с 8.1 по 8.р группы 8 блоков буферных элементов, выход счетчика 4.2 подключен к управляющим входам демультиплексоров с 2.2.1 по 2.2.n блока 2.2 демультиплексоров, к управляющим входам мультиплексоров с 3.2.1 по 3.2.n блока 3.2 мультиплексоров, а также к второму информационному входу компаратора 6.2, выход которого подключен к второму входу элемента И 14.2, выход которого подключен к управляющему входу дешифратора 5.3, информационный вход регистра 1.5 текущего барьера соединен с двенадцатым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу регистра 1.5 текущего барьера, выход которого подключен к второму информационному входу компаратора 6.1, группа вторых входов элемента И 27 соединена с группой тринадцатых входов модуля синхронизатора, выход элемента И 27 подключен к входу одновибратора 26, выход которого подключен к информационному входу демультиплексора 2.2.n+1 блока 2.2 демультиплексоров, к входу инкремента счетчика 4.2, а также к второму входу элемента ИЛИ 25, инверсный выход триггера 7.1 подключен к первому входу элемента И, а также к вторым входам с первого по n-й элемент второго блока элементов И 29, выходы которого подключены ко всем первым выходам модуля синхронизатора, вторые входы элементов И 15 и 25 подключены к четырнадцатому входу модуля синхронизатора, информационный вход регистра 1.8 текущего барьера соединен с пятнадцатым входом модуля синхронизатора, причем старший разряд пятнадцатого входа модуля синхронизатора подключен к синхровходу регистра 1.8 текущего барьера, выход которого подключен первому информационному входу компаратора 6.2, к информационному входу триггера 7.3 подключен сигнал логической единицы.

Структура блока 39 синхронизации (фиг. 3) не отличается от прототипа.

Общие особенности функциональной организации предлагаемого ПЛМК состоят в следующем.

ПЛМК формируется из множества однотипных модулей (контроллеров), объединенных в матричную структуру (фиг. 4). Каждый модуль ПЛМК содержит перепрограммируемую память программ и имеет множество входных и выходных каналов, предназначенных для подключения к другим аналогичным модулям и обмена управляющей информацией. Модули идентифицируются координатными номерами вида i.j, где i и j имеют смысл соответственно номера строки и номера столбца матричной структуры (в дальнейшем модуль с номером i.j именуется как i.j-й модуль или модуль mi.j).

ПЛМК служит для управления сложными объектами, поведение которых описывается комплексом программ и предполагает параллельное протекание процессов. Комплекс программ, реализуемый ПЛМК, разбивается на множество параллельных и последовательных участков (ветвей), которые распределяются между различными модулями. Каждый модуль реализует некоторое подмножество участков.

В процессе выполнения участков программ модули ПЛМК обрабатывают команды двух типов: операционные и коммуникационные. Операционные команды, которые имеют формат Ф2, (см. фиг. 5) обеспечивают выдачу управляющих воздействий на объект управления и инициируют выполнение требуемых микроопераций. Коммуникационные команды, имеющие формат Ф3, (см. фиг. 5) используются для организации взаимодействия и координации различных модулей, включая запуск ветвей, закрепленных за другими модулями (межмодульную передачу управления), и барьерную синхронизацию.

Как и в прототипе, в рассматриваемом ПЛМК межмодульная передача управления отсутствует в явном виде, фактически выполняется только процедура синхронизации. При этом запуск участков программ, выполняемыми различными модулями, происходит при соблюдении соответствующих правил синхронизации. Например, запуск участков, непосредственно следующих за множеством других (параллельных) участков, невозможен без завершения всех участков данного множества (условие достижения барьера). При запуске участков, следующих за только одним участком, в качестве условия выступает завершение этого участка. Для задания момента активизации некоторого участка  (где е - порядковый номер этого участка для i.j-ого модуля, а k - номер программы) этому участку ставится в соответствие номер предшествующему ему барьера at; а если активизируемому участку предшествует только один участок программы, то барьер at считается фиктивным. Запуск участка

(где е - порядковый номер этого участка для i.j-ого модуля, а k - номер программы) этому участку ставится в соответствие номер предшествующему ему барьера at; а если активизируемому участку предшествует только один участок программы, то барьер at считается фиктивным. Запуск участка  происходит после достижения барьера всеми модулями, т.е. когда модули завершили выполнение предшествующих барьеру участков программы.

происходит после достижения барьера всеми модулями, т.е. когда модули завершили выполнение предшествующих барьеру участков программы.

Как и в прототипе, в предлагаемом ПЛМК адреса приема управления формируются непосредственно модулями, реализующими запускаемые участки (модулями -приемниками управления), в результате самонастройки. Адрес  начала следующего (е+1-ого) участка, закрепленным за модулем mi.j, указывается в последней команде предыдущего участка программы, закрепленным за этим же модулем mi.j. Для задания адресов начальных участков модулей

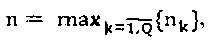

начала следующего (е+1-ого) участка, закрепленным за модулем mi.j, указывается в последней команде предыдущего участка программы, закрепленным за этим же модулем mi.j. Для задания адресов начальных участков модулей  используются команды настройки формата Ф1 (фиг. 5), где «НРМ» означает номер разряда модуля, т.е. номер физического разряда модуля ПЛМК, в котором находится барьер, а «НБ» - непосредственно номер барьера. Таким образом номер барьера задается двумя значениями: номером разряда и номером барьера. Это происходит потому, что модуль может выполнять несколько барьеров одновременно. За каждым модулем ПЛМК закрепляется Q таких команд, Q - число программ реализуемых ПЛМК(число программ в реализуемом комплексе). Каждая из q команд настройки определяет адрес

используются команды настройки формата Ф1 (фиг. 5), где «НРМ» означает номер разряда модуля, т.е. номер физического разряда модуля ПЛМК, в котором находится барьер, а «НБ» - непосредственно номер барьера. Таким образом номер барьера задается двумя значениями: номером разряда и номером барьера. Это происходит потому, что модуль может выполнять несколько барьеров одновременно. За каждым модулем ПЛМК закрепляется Q таких команд, Q - число программ реализуемых ПЛМК(число программ в реализуемом комплексе). Каждая из q команд настройки определяет адрес  первый команды, т.е. адрес первого участка, закрепленного за модулем mi.j. Следует заметить, что если mi.j не участвует в процессе выполнения k-й программы, то команда Ф1 полностью состоит их нулей. Команды Ф1 размещаются в блоке 1 памяти программ (фиг. 1) по начальным адресам от 1 до Q включительно. Команда настройки, а следовательно, и реализуемая программа однозначно задается адресом при обращении к блоку 1.

первый команды, т.е. адрес первого участка, закрепленного за модулем mi.j. Следует заметить, что если mi.j не участвует в процессе выполнения k-й программы, то команда Ф1 полностью состоит их нулей. Команды Ф1 размещаются в блоке 1 памяти программ (фиг. 1) по начальным адресам от 1 до Q включительно. Команда настройки, а следовательно, и реализуемая программа однозначно задается адресом при обращении к блоку 1.

Процесс синхронизации параллельных участков в предлагаемом ПЛМК заключается в распространении и опросе сигналов завершения множества параллельных участков. Каждый такой сигнал распространяется в отдельном канале синхронизации, который соответствует одному барьеру. Канал синхронизации представляет собой совокупность элементов (модулей синхронизатора) различных модулей ПЛМК и соответствующих связей, обеспечивающих протекание процесса синхронизации определенного множества параллельных участков.

Как и в прототипе, в рассматриваемом ПЛМК каналы синхронизации разбиты на группы. Однако, в отличие от прототипа, в котором в один момент времени активна только одна группа каналов, внутри которой сигналы распространяются независимо и параллельно, в предлагаемом техническом решении в один момент времени могут работать сразу две группы каналов. Смена групп каналов происходит циклически.

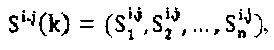

Для обеспечения синхронизации произвольных множеств параллельных участков за каждым модулем ПЛМК закрепляется вектор, задающий соответствие между множеством барьеров программы и данным модулем. Модулю мультиконтроллера mi.j, в общем случае соответствует Q различных векторов, каждый из которых отвечает определенной программе. Вектор соответствия для модуля mi.j и k-й программы имеет вид  где

где  nk - число барьеров в k-й программе.

nk - число барьеров в k-й программе.

Значение компоненты вектора Sij(k) определяется следующим образом:  , если за модулем mi.j закреплен некоторый участок программы, завершающийся q-м барьером;

, если за модулем mi.j закреплен некоторый участок программы, завершающийся q-м барьером;  если модуль mi.j не реализует ни одного участка, завершающегося q-м барьером, или q-й барьер отсутствует в k-й программе (что возможно при nk<q)

если модуль mi.j не реализует ни одного участка, завершающегося q-м барьером, или q-й барьер отсутствует в k-й программе (что возможно при nk<q)

Синхронизация множества участков  , завершающихся q-м барьером, осуществляется на основе распространения сигнала dq в q-м канале синхронизации. Сигнал dq формируется модулем m1.1 (левым верхним). В исходном состоянии dq=0 (параллельные участки не завершены) и, следовательно,

, завершающихся q-м барьером, осуществляется на основе распространения сигнала dq в q-м канале синхронизации. Сигнал dq формируется модулем m1.1 (левым верхним). В исходном состоянии dq=0 (параллельные участки не завершены) и, следовательно,

Процесс барьерной синхронизации включает в себя две фазы, формирование признака завершения синхронизируемых участков и передачу этого признака всем модулям ПЛМК.

Первая из указанных фаз начинается с распространения сигнала  от модуля m1.1 вниз вправо через все модули ко всем крайним правым и крайним нижним модулям вплоть до модуля mM.N (см. фиг. 3).

от модуля m1.1 вниз вправо через все модули ко всем крайним правым и крайним нижним модулям вплоть до модуля mM.N (см. фиг. 3).

Распространение сигнала  через модуль mi.j происходит следующим образом. Если

через модуль mi.j происходит следующим образом. Если  то появление единичных сигналов

то появление единичных сигналов  на верхнем и левом входах модуля mi.j обуславливает формирование единичного сигнала на его выходе. Если

на верхнем и левом входах модуля mi.j обуславливает формирование единичного сигнала на его выходе. Если  , то формирование сигнала

, то формирование сигнала  на выходе модуля mi.j происходит только при условии завершения участка

на выходе модуля mi.j происходит только при условии завершения участка  , сходящегося в q-м барьере и реализуемого модулем mi.j.

, сходящегося в q-м барьере и реализуемого модулем mi.j.

Состояние участка  определяется значением сигнала

определяется значением сигнала  если участок

если участок  завершен;

завершен;  в противном случае. В случае если участок

в противном случае. В случае если участок  не завершен, на выходе модуля mi.j устанавливается нулевой сигнал. Данный сигнал формирует нулевые сигналы на выходах всех модулей, расположенных не выше и не левее модуля mi.j. На входе модуля mM.N (правого нижнего, см. фиг. 3), соответственно, также будет нулевой сигнал. Как только происходит завершение участка

не завершен, на выходе модуля mi.j устанавливается нулевой сигнал. Данный сигнал формирует нулевые сигналы на выходах всех модулей, расположенных не выше и не левее модуля mi.j. На входе модуля mM.N (правого нижнего, см. фиг. 3), соответственно, также будет нулевой сигнал. Как только происходит завершение участка  единичный сигнал

единичный сигнал  передается на выход модуля mi.j и поступает в модули mi+1.j и mi.j+1.

передается на выход модуля mi.j и поступает в модули mi+1.j и mi.j+1.

После завершения всех параллельных участков множества Bq единичный сигнал  пройдет на входы модуля mM.N и будет передан в остальные модули, расположенные выше правее. Таким образом, формируется сигнал dq=1, сообщающий об окончании синхронизируемых параллельных участков. На этом первая фаза завершается.

пройдет на входы модуля mM.N и будет передан в остальные модули, расположенные выше правее. Таким образом, формируется сигнал dq=1, сообщающий об окончании синхронизируемых параллельных участков. На этом первая фаза завершается.

Вторая фаза синхронизации начинается с появления на выходе модуля mM.N единичного сигнала dq. Этот сигнал распространяется (фиг. 3) от модуля mM.N вверх и влево через ПЛМК ко всем крайним левым и крайним левым и крайним верхним модулям до модуля m1.1. В процессе распространения сигнал dq=1 запускает модули, ожидающие завершения множества Bq. Вторая фаза и процесс синхронизации в целом заврешаются после появления нулевого сигнала на выходе модуля m1.1.

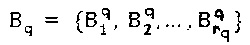

Принципы организации межмодульной передачи управления и синхронизации в предлагаемом ПЛМК поясняются примером реализации параллельного алгоритма логического управления, представленного на фиг. 5а. Алгоритм включает в себя 20 параллельных и последовательных участков  принадлежность которых определенному модулю задается верхним индексом i.j. В рассматриваемый алгоритм входят барьеры а1, а2, …, а10; барьеры а8, а9, а10 являются фиктивными, поскольку им предшествует только один участок программы. Пары барьеров а2 и а8, а3 и а4, а5 и а9, а10 и а6 являются параллельными и синхронизируются независимо. ПЛМК, реализующий данный алгоритм, имеет вид матрицы с конфигурацией 3×3 модуля.

принадлежность которых определенному модулю задается верхним индексом i.j. В рассматриваемый алгоритм входят барьеры а1, а2, …, а10; барьеры а8, а9, а10 являются фиктивными, поскольку им предшествует только один участок программы. Пары барьеров а2 и а8, а3 и а4, а5 и а9, а10 и а6 являются параллельными и синхронизируются независимо. ПЛМК, реализующий данный алгоритм, имеет вид матрицы с конфигурацией 3×3 модуля.

Таблица настройки модулей, определяющая адреса начальных участков  а также номера барьеров at, после достижения которых должен быть обеспечен запуск соответствующих модулей, представлены на фиг. 6б. В соответствии с данной таблицей запуск модулей m1.1, m3.2 и m3.3 происходит после выполнения барьера а1, т.е. после завершения участка

а также номера барьеров at, после достижения которых должен быть обеспечен запуск соответствующих модулей, представлены на фиг. 6б. В соответствии с данной таблицей запуск модулей m1.1, m3.2 и m3.3 происходит после выполнения барьера а1, т.е. после завершения участка  запуск модуля m1.2 осуществляется после достижения барьера а8, т.е. после завершения участка

запуск модуля m1.2 осуществляется после достижения барьера а8, т.е. после завершения участка  и т.д. Модуль m2.2 активизируется непосредственно в момент запуска ПЛМК независимо от состояния других модулей, поскольку реализует начальный последовательный участок алгоритма

и т.д. Модуль m2.2 активизируется непосредственно в момент запуска ПЛМК независимо от состояния других модулей, поскольку реализует начальный последовательный участок алгоритма

Таблица векторов соответствия для рассматриваемого алгоритма показана на фиг. 6в. Согласно данной таблице модуль m1.1 реализует участки, завершающиеся в барьерах а2, а5 и  модуль m1.2 - участки, сходящиеся в барьерах a2, a5 и а6

модуль m1.2 - участки, сходящиеся в барьерах a2, a5 и а6  и т.д.

и т.д.

Более подробно процессы синхронизации и запуска параллельных участков описываются далее при рассмотрении функционирования ПЛМК.

Назначение элементов и блоков модуля логического мультиконтроллера (фиг. 1) 38, 40, 37,41, 34, 35, 33, 36, 42, 44, 39, 43, 23 не отличается от прототипа.

Назначение остальных элементов и блоков сводится к следующему.

Модуль 45 синхронизатора служит для реализации синхронизации параллельных участков.

Назначение элементов модуля 45 синхронизатора состоит в следующем.

Триггеры 7.1 и 7.2 предназначены для хранения значений координатных признаков. Состояние этих триггеров определяется во время инициализации модулей и сохраняется в течение всего времени.

Триггер 7.3 служит для фиксации признака состояния параллельной ветви, выполняемой текущим модулем. Триггер 7.3 устанавливается в единицу всякий раз, когда завершается ветвь, и сбрасывается в ноль момент активизации текущего модуля после ожидания завершения барьера.

Регистр 1.3 вектора соответствия бит служит для хранения вектора соответствия. Содержимое регистра 1.3 сохраняется неизменным в течение всего времени выполнения программ.

Регистр 1.4 максимального количества барьеров в одном физическом разряде предназначен для хранения максимального количества барьеров в одном физическом разряде ПЛМК.

Регистры 1.5 и 1.8 текущего барьера предназначены для хранения номеров барьеров в первой и второй фазе синхронизации соответственно.

Блоки демультиплексоров 2.1 и мультиплексоров 3.1 обеспечивают подключение определенных разрядов блока регистров 1.1 на время записи/чтения значения соответствующей функции в первой фазе синхронизации.

Блоки демультиплексоров 2.2 и мультиплексоров 3.2 аналогичным образом коммутируют разряды блока регистров 2.2 с целью записи/чтения значения соответствующей функции во второй фазе.

Счетчики 4.1 и 4.2 с программируемым коэффициентом пересчета введены для организации последовательного перебора всех возможных номеров барьеров и хранения их текущих номеров в первой и второй фазах синхронизации соответственно.

Дешифратор 5.1 вместе с группой 8 блоков буферных элементов и блоком 32 элементов «монтажное ИЛИ» позволяет сформировать значение компонент вектора соответствия.

Компаратор 6.1 служит для сравнения номера выполняемого барьера с номером проверяемого барьера в первой фазе синхронизации.

Компаратор 6.2 служит для сравнения номера выполняемого барьера с номером проверяемого барьера во второй фазе синхронизации.

Элемент И 11 вместе с одновибратором 23 и элементом ИЛИ 24 служат для формирования признака завершения участка программы.

Группа регистров 1.1 служит для хранения текущих значений сигналов  в первой фазе синхронизации.

в первой фазе синхронизации.

Группа регистров 1.2 служит для хранения текущих значений сигналов dq во второй фазе синхронизации.

Регистры 1.6, 1.7 текущего физического разряда предназначен для фиксации номера физического разряда ПЛМК, в котором находится барьер в первой и второй фазах синхронизации соответственно.

Дешифратор 5.2 служит для преобразования номера текущего физического разряда в первой фазе синхронизации.

Дешифратор 5.3 служит для преобразования номера текущего физического разряда во второй фазе синхронизации.

Блок 9 буферных элементов предназначен для коммутации выхода блока 19 элементов ИЛИ-НЕ с седьмыми входами модуля синхронизатора.

Блок 10 элементов И служит для формирования выходных значений сигналов dq.

Блок 13 элементов И, элемент ИЛИ 17 предназначены для организации распространения сигналов опроса состояния множеств параллельных участков от соседних модулей сверху и слева от текущего.

Элемент И 14.1 служит для управления работой дешифратора 5.2. Элемент И 14.2 служит для управления работой дешифратора 5.3.

Блок 20 элементов ИЛИ-НЕ вместе с блоком 12 элементов И, блоком 16 элементов ИЛИ предназначены для исключения начала первой фаза синхронизации до завершения второй на предыдущем участке программы.

Элемент ИЛИ 18 используется для формирования сигнала сброса триггера 7.3.

Группа 22 блоков элементов ИЛИ-НЕ совместно с блоком 21 элементов И-НЕ для организации распространения сигналов запуска модулей, ожидающих завершения соответствующих множеств параллельных участков, от соседних модулей справа и снизу от текущего.

Элемент ИЛИ 15, элементы И 29, 31 и одновибратор 30 предназначены для формирования тактовых импульсов, распространяющиеся в первой фазе синхронизации.

Элемент ИЛИ 25, элементы И 27, 28 и одновибратор 26 служат для формирования тактовых импульсов, распространяющиеся во второй фазе синхронизации.

Рассмотрим процесс функционирования ПЛМК подробно.

Первоначально элементы памяти (регистры, триггеры и счетчики) всех модулей ЛМК находятся в состоянии логического нуля. Исключение составляет только регистр 35,на выходе 3.10 которого находится единичный уровень сигнала, и триггер 62 блока 39 синхронизации (фиг. 4). Исходя из указанного состояния элементов памяти, блоки 39 синхронизации всех модулей выключены, коммутаторы 37 настроены на прием информации с входов 56, а на всех выходах модулей находятся сигналы логического нуля.

Перед началом работы происходит конфигурирование ПЛМК. Для этого на вход 61 модуля mM.N (фиг. 1) подается сигнал логической единицы. Этот сигнал записвывается по заднему фронту в триггер 7.1 (фиг. 2). Нулевой сигнал с прямого выхода триггера 7.1 во всех остальных модулях выключает блок 9 буферных элементов, отключая выход блока 19 элементов ИЛИ-НЕ от группы входов 46 модуля (фиг. 1). В модуле mM.N, наоборот, блок 9 (фиг. 2) включается единичным сигналом с прямого входа триггера 7.1 и выход блока 19 коммутируется с группой входов 46 модуля (фиг. 1). Благодаря этому (и так как все регистры группы 1.1 (фиг. 2) находятся в нулевом состоянии) в модуле mM.N на группу входов 46 (фиг. 1) проходят единицы с блока 19 элементов ИЛИ-НЕ (фиг. 2), чем обеспечивается появление единиц на выходе блока 21 элементов И-НЕ. В свою очередь единичный сигнал с инверсного выхода триггера 7.1 во всех модулях, кроме модуля mM.N, открывает блок 10 элементов И, обеспечивая возможность передачи значений функций состояния от блока 3.1 мультиплексоров на группу выходов 51 модуля (фиг. 1). Поскольку все регистры группы 1.1 (фиг. 2) находятся в нулевом состоянии, открытие блока 10 элементов И на данном этапе не влияет на состояние выходов 1 модулей (фиг. 1). Нулевой сигнал с инверсного выхода триггера 7.1 (фиг. 2) в модуле mM.N, закрывает блок 10 элементов И, блокируя передачу значений функций состояния на группу 1 выходов модуля (фиг. 1). Поскольку на всех выходах группы 1 модуля присутствует нулевой уровень сигнала, блоки 13 элементов И во всех модулях выдают нули. Нулевой сигнал с прямого выхода триггера 7.3 блокирует элементы И 14.1, 14.2, отключая тем самым дешифраторы 5.2 и 5.3. Этот же нулевой сигнал закрывает все элементы блока 11 элементов И, в результате чего на выходе элемента ИЛИ 24 также формируется нулевой уровень сигнала.

Одновременно с описанными действиями единичный сигнал подается на вход 62 модуля m1.1 и записывается в триггер 7.2 (фиг. 2). Так как все регистры группы 1.2 пока установлены в нулевое состояние на выходах блока мультиплексоров 3.2 также будут нули; соответственно, на выходах блока 20 элементов ИЛИ-НЕ появятся единицы. Таким образом, независимо от состояния триггера 7.2 блок 16 элементов ИЛИ будет выдавать единицы (на данном этапе это состояние является несущественным).

На вход 48 подается код pk числа максимального количества барьеров в одном физическом разряде. Величина pk зависит от числа qk барьеров в реализуемых программах и от числа n физических разрядов ПЛМК (pk=qk/n). Значение pk записывается в регистр 1.4 числа максимального количества барьеров в одном физическом разряде (фиг. 2) по заднему фронту импульса старшего разряда входа 48 (фиг. 1). Из регистра 1.4 (фиг. 2) значение pk фиксируется в счетчиках 4.1 и 4.2.

По завершении конфигурирования начинается настройка модулей ПЛМК на выполнение требуемой (k-й) программы. Настройка модуля mi.j на выполнение k-й программы сводится к установлению адреса  (адреса первой команды), а также к определению номера барьера at, после достижения которой должен осуществляться запуск модуля mi.j.

(адреса первой команды), а также к определению номера барьера at, после достижения которой должен осуществляться запуск модуля mi.j.

Процесс настройки модулей на выполнение k-й программы начинается с подачи на вход 56 модуля mi.j (фиг. 1) кода операции (КОП). КОП, представляющий собой код номера выполняемой программы (k), через коммутатор 37 подается на информационный вход регистра 34. Одновременно на вход 55 модуля подается импульс настройки. Указанный импульс через элемент ИЛИ 41 поступает на синхровход регистра 34 и задним фронтом фиксирует КОП в данном регистре. Далее КОП с выхода регистра 34 подается на адресный вход блока 1 и формирует на его выходе команду настройки Ф1 (фиг. 5) соответствующую k-й программе.

В то же время импульс настройки через элемент задержки 44 и элемент ИЛИ 42 (фиг. 1) передается на синхровход регистра 35 и задним фронтом производит запись считанной из блока 1 команды в регистр 35. После фиксации команды на выходах 3.2 и 3.3 регистра 35 образуется адрес  а на выходах 3.7 и 3.8 формируется коды номеров физического разряда ПЛМК, в котором находится барьер, и барьера непосредственно at. На остальных выходах регистра 35 устанавливаются нулевые сигналы. Нулевой сигнал с выхода 3.10 регистра 35 перенастраивает коммутатор 37 на прием информации с выхода блока элементов ИЛИ 40. Поскольку на выходе 3.1 регистра 35 присутствует нулевой код (проверка логических условий в ходе настройки не производится) адрес

а на выходах 3.7 и 3.8 формируется коды номеров физического разряда ПЛМК, в котором находится барьер, и барьера непосредственно at. На остальных выходах регистра 35 устанавливаются нулевые сигналы. Нулевой сигнал с выхода 3.10 регистра 35 перенастраивает коммутатор 37 на прием информации с выхода блока элементов ИЛИ 40. Поскольку на выходе 3.1 регистра 35 присутствует нулевой код (проверка логических условий в ходе настройки не производится) адрес  без изменений проходит через блок элементов ИЛИ 40. Далее этот адрес передается через коммутатор 37 и устанавливается на информационном входе регистра 34.

без изменений проходит через блок элементов ИЛИ 40. Далее этот адрес передается через коммутатор 37 и устанавливается на информационном входе регистра 34.

В то же время код барьера с выходов 3.7 и 3.8 подается на информационные входы регистров 1.7 и 1.8 (фиг. 2), где фиксируются передним фронтом специального сигнала в старшем разряде кода. Для модуля ПЛМК, который реализует начальный участок k-й программы, задания кода номера барьера не требуется, поскольку этот модуль начинает выполнение программы непосредственно в момент запуска ПЛМК, не зависимо от условий синхронизации. Поэтому на выходах 3.7 и 3.8 регистра 35 (фиг. 1) рассматриваемого модуля устанавливается нулевой код.

Одновременно с описанными выше действиями осуществляется запись кода вектора соответствия  (устанавливается соответствия между модулем) mi.j и множеством барьеров k-й программы). Вектор подается на вход 47 модуля и заносится в регистр 1.3 (фиг. 2) по переднему фронту специального импульса старшего разряда входа 47 модуля. На этом процесс настройки модуля mi.j на выполнение k-й программы завершается.

(устанавливается соответствия между модулем) mi.j и множеством барьеров k-й программы). Вектор подается на вход 47 модуля и заносится в регистр 1.3 (фиг. 2) по переднему фронту специального импульса старшего разряда входа 47 модуля. На этом процесс настройки модуля mi.j на выполнение k-й программы завершается.

Аналогичным образом протекает процесс настройки остальных модулей ПЛМК, причем настройка различных модулей выполняется одновременно. На входы 56 всех модулей подается один и тот же КОП; векторы соответствия для разных модулей в общем случае различны. В результате настройки каждого модуля определяется момент его запуска при выполнении сетью k-й программы, задается соответствующий адрес (адрес первой команды) и, кроме того, устанавливается подмножество барьеров k-й программы, в которых завершаются участки, реализуемые модулем.

После завершения настройки осуществляется запуск ПЛМК. Для запуска сети на вход 57 модуля, реализующего начальный участок k-й программы, подается импульс пуска (фиг. 1). Допустим, что указанный модуль имеет номер i.j (в примере на фиг. 6 это модуль m2.2). Импульс пуска с входа 57 модуля mi.j передается на первый вход блока 39 синхронизации.

Далее этот импульс проходит через элемент ИЛИ 59 (фиг. 3), воздействуя на вход установки триггера 60, переводит его в единичное состояние. Единичный сигнал с прямого входа триггера 60 поступает на вход генератора 61 и разрешает на его входе формирование последовательности импульсов.

Первый импульс с выхода генератора 61 проходит через элемент И 63 на первый выход блока синхронизации (элемент 63 открыт единичным сигналом с прямого выхода триггера 62). По заднему фронту этого же импульса триггер 62 переключается в нулевое состояние и, как следствие, блокирует элемент И 63, при этом открывая элемент И 64. Следующий импульс с выхода генератора 61 проходит через элемент И 64 на второй выход блока синхронизации. Третий импульс снова проходит на первый выход блока синхронизации, четвертый - на второй и т.д. Таким образом, на выходах блока 39 синхронизации происходит генерация двух сдвинутых относительно друг друга последовательностей сигналов синхронизации t1 и t2.

Первый импульс t1 с первого выхода блока 39 синхронизации (фиг. 1) через элемент ИЛИ 41 воздействует на синхровход регистра 34 адреса, записывая тем самым в него адрес  поступающий с выхода коммутатора 37. Адрес

поступающий с выхода коммутатора 37. Адрес  с выхода регистра 34 адреса поступает на вход блока 33 памяти программ и формирует на его выходе первую команду k-й программы.

с выхода регистра 34 адреса поступает на вход блока 33 памяти программ и формирует на его выходе первую команду k-й программы.

Первый импульс t2 со второго выхода блока 39 синхронизации проходит через элемент ИЛИ 42, поступая на синхровход регистра 35 команд. Осуществляется запись команды с выхода блока 33 памяти программ в регистр 35 команд. Одновременно этот же импульс подается на вход сброса буферного регистра 38 и подтверждает его нулевое состояние. Таким образом, модуль mi.j и сеть в целом начинают исполнение k-й программы.

Дальнейшую работу ПЛМК будем рассматривать в предположении, что модуль mi.j выполняет некоторый (в общем случае не начальный) участок k-й программы  завершающийся барьером aq. Кроме того, будем считать, что одновременно с mi.j модулем могут функционировать и некоторые другие модули ПЛМК (остальные модули находятся в состоянии ожидания).

завершающийся барьером aq. Кроме того, будем считать, что одновременно с mi.j модулем могут функционировать и некоторые другие модули ПЛМК (остальные модули находятся в состоянии ожидания).

В процессе выполнения участка  модуль mi.j может обрабатывать команды форматов Ф2, Ф3 и Ф4 (фиг. 5). Обработка команды формата Ф2 соответствует собственно режим выполнения участка программы (Режим А), команда формата Ф3 определяет режим завершения участка (режим В), а команда Ф4 задает режим завершения программы в целом (режим С). Рассмотрим работу модуля в приведенных режимах.

модуль mi.j может обрабатывать команды форматов Ф2, Ф3 и Ф4 (фиг. 5). Обработка команды формата Ф2 соответствует собственно режим выполнения участка программы (Режим А), команда формата Ф3 определяет режим завершения участка (режим В), а команда Ф4 задает режим завершения программы в целом (режим С). Рассмотрим работу модуля в приведенных режимах.

Режим А. Записанная в регистр 3 команда имеет формат Ф2 (фиг. 5). В этом случае на выходе 3.4 регистра 35 (фиг. 1) формируется код микроопераций (МО), на выходах 3.2 и 3.3 образуется адрес следующий команды Аcл (на выходе 3.3 немодифицируемая часть, а на выходе 3.2 - модифицируемый разряд адреса следующей команды, изменяемый в точках ветвления программ), на выходе 3.1 устанавливается код опрашиваемого логического условия (ЛУ), а на выходах 3.5-3.10 сигналы логического нуля.

Код МО с выхода 3.4 регистра 35 передается на выход 58 модуля и, поступая далее на вход объекта управления, инициирует выполнение требуемых микрооопераций. Нулевые сигналы с выходов 3.5-3.8 записываются в соответствующие разряды регистров 1.6, 1.7, 1.5, 1.8 (фиг. 2) соответственно. Нулевой сигнал с выхода 3.9 регистра 35 (фиг. 1) поступает на управляющие входы коммутатора 37 и настраивает его на прием адреса следующей команды с выхода блока элементов ИЛИ 40.

Одновременно с описанными действиями происходит формирование исполнительного адреса следующей команды Указанный адрес образуется из адреса следующей команды Асл путем замещения модифицируемого (младшего) разряда значением опрашиваемого ЛУ. Новое значение младшего разряда формируется на выходе мультиплексора 36. Процесс формирования этого значения протекает следующим образом. Модифицируемый разряд (Ам) адреса Асл с выхода 3.2 регистра 35 подается на первый информационный вход мультиплексора 36, а код ЛУ с выхода 3.1 поступает на адресный вход мультиплексора 36. Если код ЛУ отличен от нулевого, то на выход мультиплексора 36 передается значение соответствующего ЛУ с входа 65 модуля. Если же код ЛУ нулевой, то на выход мультиплексора 36 поступает значение Ам с выхода 3.2 регистра 35. Значение с выхода мультиплексора 36 в объединении с немодифицируемой (старшей) частью адреса следующей команды (Ан) с выхода 3.3 регистра 35 образуют исполнительный адрес следующей команды

Адрес  через блок элементов ИЛИ 40 и открытый коммутатор 37 проходит на информационный вход регистра 34. Очередной импульс синхронизации t1 с первого выхода блока 39 синхронизации фиксирует адрес

через блок элементов ИЛИ 40 и открытый коммутатор 37 проходит на информационный вход регистра 34. Очередной импульс синхронизации t1 с первого выхода блока 39 синхронизации фиксирует адрес  в регистре 34. Адрес

в регистре 34. Адрес  с выхода регистра 34 поступает на адресный вход блока 33 и обеспечивает считывание из блока 33 очередной команды k-й программы. Следующий импульс t2 со второго выхода блока 29 синхронизации через элемент ИЛИ 42 полается на синхровход регистра 35 и записывает в регистр считанную команду.

с выхода регистра 34 поступает на адресный вход блока 33 и обеспечивает считывание из блока 33 очередной команды k-й программы. Следующий импульс t2 со второго выхода блока 29 синхронизации через элемент ИЛИ 42 полается на синхровход регистра 35 и записывает в регистр считанную команду.

На этом работа модуля mi.j в режиме А заканчивается. Считанная команда снова может иметь формат Ф2 либо может быть командой формата Ф3 или Ф4.

Режим В. Записанная в регистр 35 команда имеет формат Ф3 (фиг. 5). В этом случае модуль mi.j завершает выполнение некоторого участка  производит самонастройку на выполнение очередного участка k-й программы и переходит в состояние ожидания. В ходе самонастройки модуль mi.j устанавливает адрес

производит самонастройку на выполнение очередного участка k-й программы и переходит в состояние ожидания. В ходе самонастройки модуль mi.j устанавливает адрес  начала очередного ((е+1)-ого) участка

начала очередного ((е+1)-ого) участка  (здесь е - порядковый номер участка

(здесь е - порядковый номер участка  для модуля mi.j) и фиксирует номер (t) барьера at (после достижения которого должен осуществляться запуск модуля mi.j).

для модуля mi.j) и фиксирует номер (t) барьера at (после достижения которого должен осуществляться запуск модуля mi.j).

На выходе 3.9 регистра 35 появляется единичная метка конца участка программы (Мку), инициирующая формат считанной команды, на выходах 3.2 и 3.3 регистра 35 формируется адрес  на выходе 3.1 образуется код ЛУ, а на выходах 3.4 и 3.10 устанавливаются сигналы логического нуля. В тоже время на выходе 3.5 регистра 35 формируются номер физического разряда модуля, в котором находится барьер aq, а на выходе 3.6 регистра 35 номер (q) барьера aq, завершающий выполненный модулем участок программы

на выходе 3.1 образуется код ЛУ, а на выходах 3.4 и 3.10 устанавливаются сигналы логического нуля. В тоже время на выходе 3.5 регистра 35 формируются номер физического разряда модуля, в котором находится барьер aq, а на выходе 3.6 регистра 35 номер (q) барьера aq, завершающий выполненный модулем участок программы  На выходе 3.7 регистра 35 формируются номер физического разряда модуля, в котором находится барьер at, а на выходе 3.8 номер (t) барьера at, определяющий момент запуска модуля mi.j (допустимым является случай, когда t=q).

На выходе 3.7 регистра 35 формируются номер физического разряда модуля, в котором находится барьер at, а на выходе 3.8 номер (t) барьера at, определяющий момент запуска модуля mi.j (допустимым является случай, когда t=q).

В примере на фиг. 6 после выполнения участка  на выходе 3.6 регистра 35 модуля m2.2 будет установлен номер барьера а1, а на выходе 3.5 физический разряд модуля, в котором выполняется синхронизация барьера a1 На выходе 3.8 регистра 35 модуля m2.2 будет установлен номер барьера а2, за которым следует очередной участок

на выходе 3.6 регистра 35 модуля m2.2 будет установлен номер барьера а1, а на выходе 3.5 физический разряд модуля, в котором выполняется синхронизация барьера a1 На выходе 3.8 регистра 35 модуля m2.2 будет установлен номер барьера а2, за которым следует очередной участок  выполняемый модулем m2.2. На выходе 3.7 регистра 35 будет установлен физический разряд модуля, в котором выполняется синхронизация барьера а2. Адрес начала этого участка

выполняемый модулем m2.2. На выходе 3.7 регистра 35 будет установлен физический разряд модуля, в котором выполняется синхронизация барьера а2. Адрес начала этого участка  будет зафиксирован на выходах 3.2 и 3.3 регистра 35. После завершения участка

будет зафиксирован на выходах 3.2 и 3.3 регистра 35. После завершения участка  на выходе 3.6 регистра 35 модуля m2.2 будет установлен номер барьера а4, а на выходе 3.5 физический разряд модуля, в котором выполняется синхронизация барьера а4. На выходе 3.8 регистра 35 модуля m2.2 будет установлен номер барьера а7, за которым следует очередной участок

на выходе 3.6 регистра 35 модуля m2.2 будет установлен номер барьера а4, а на выходе 3.5 физический разряд модуля, в котором выполняется синхронизация барьера а4. На выходе 3.8 регистра 35 модуля m2.2 будет установлен номер барьера а7, за которым следует очередной участок  выполняемый модулем m2.2. На выходе 3.7 регистра 35 будет установлен физический разряд модуля, в котором выполняется синхронизация барьера а7. Аналогичным образом происходит самонастройка других модулей.

выполняемый модулем m2.2. На выходе 3.7 регистра 35 будет установлен физический разряд модуля, в котором выполняется синхронизация барьера а7. Аналогичным образом происходит самонастройка других модулей.

Код номера барьера а7 с выхода 3.6 регистра 35 поступает на информационный вход регистра 1.5 (фиг. 2), где фиксируется единичным сигналом специального старшего разряда этого кода по переднему фронту. В то же время код физического разряда модуля, в котором синхронизируется барьер aq, с выхода 3.5 регистра 35 (фиг. 1) подается на информационный вход регистра 1.6 (фиг. 2), где аналогично фиксируется единичным сигналом специального старшего разряда этого кода по переднему фронту. В свою очередь, код номера барьера at с выхода 3.8 регистра 35 (фиг. 1) поступает на информационный вход регистра 1.8 (фиг. 2), где фиксируется единичным сигналом специального старшего разряда этого кода по переднему фронту. В то же время код физического разряда модуля, в котором синхронизируется барьер at, с выхода 3.7 регистра 35 (фиг. 1) подается на информационный вход регистра 1.7 (фиг. 2), где аналогично фиксируется единичным сигналом специального старшего разряда этого кода по переднему фронту.