оо со

О)

оо

IfMkt

Изобретение отнвсится к области систем управления и измерительной техники и предназначено для интегрирования дискретных сигналов.

Целью изобретения является повы- шение точности интегрирования сигналов без уменьшения периода дискретности.

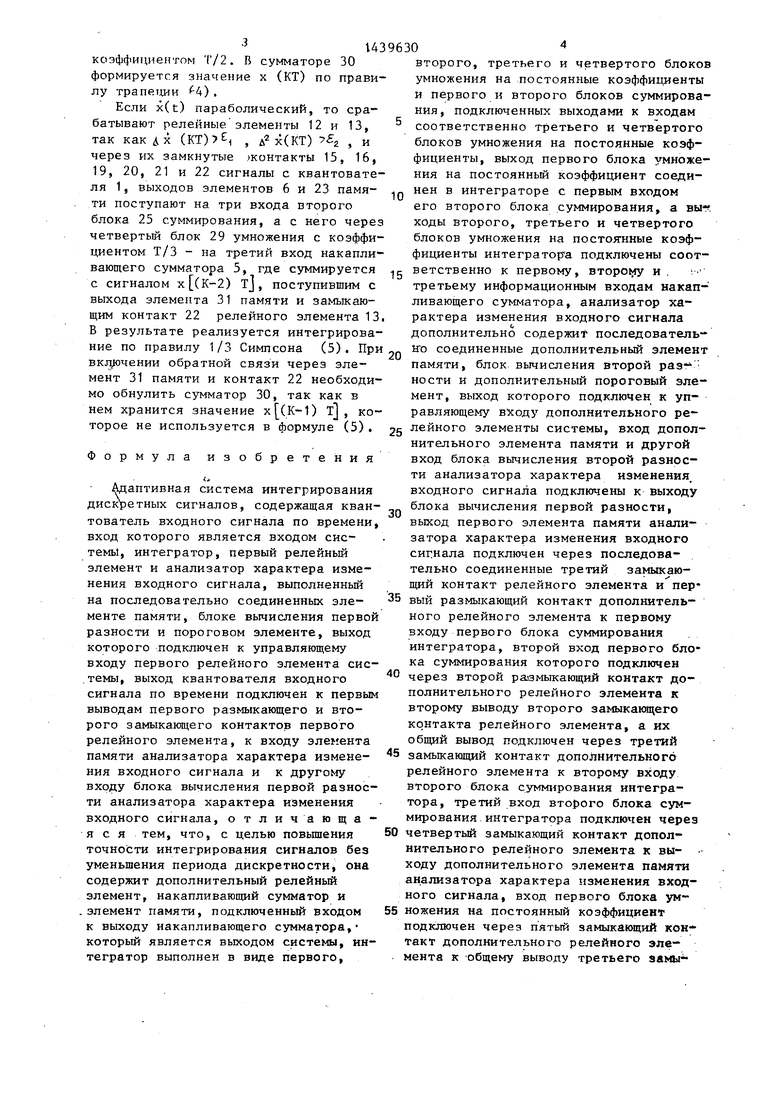

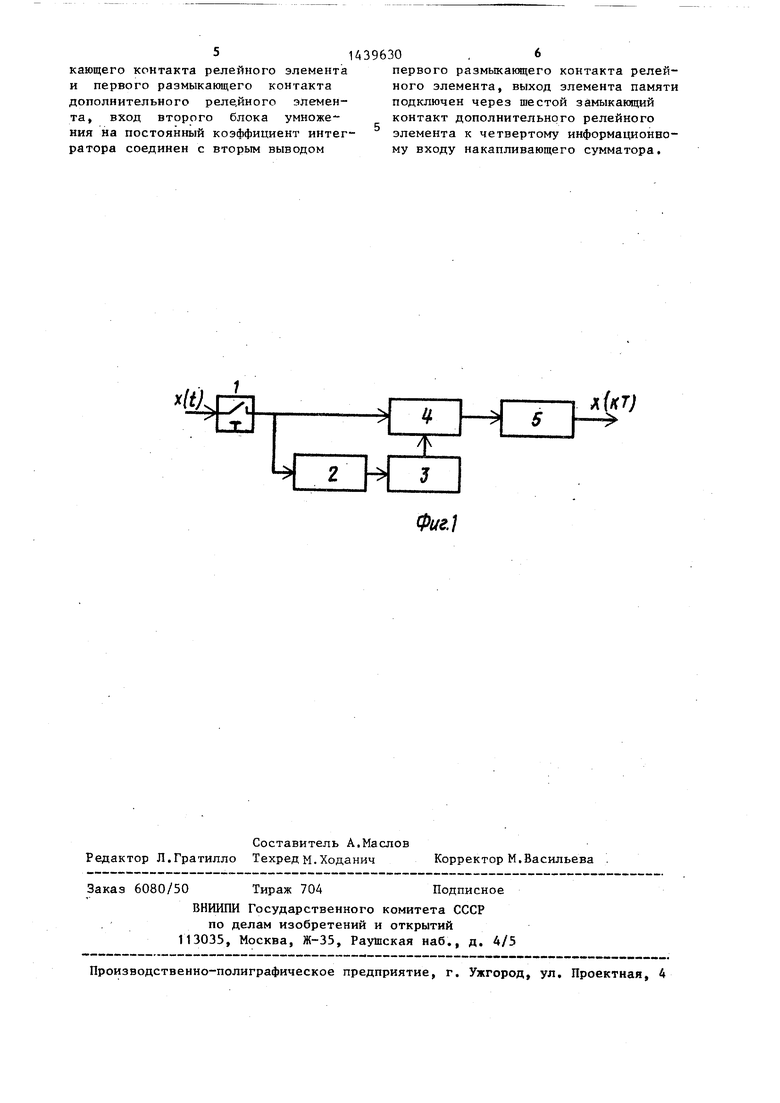

На фиг.1 представлена блочная схема системы; на фиг.,2 - структурная схема системы.

Система (фиг.1) содержит квантователь 1 входного сигнала по времени, анализатор 2 характера изменения входного сигнала, блок 3 коммутации, интегратор 4, накапливающий сумматор 5. Анализатор 2 (фиг.2) содержит основной элемент 6 памяти и допол- . нительный элемент 7 памяти на Т, каждый, блок 8 вычисления первой и блок 9 вычисления второй разностей, первый пороговый элемент 10 и дополнительный пороговый элемент 11, На выходе блоков вычисления разностей последовательно формируются разности

dx(KT)x(KT) - х(К-1) Tj; д2х(КТ)лх(КТ)-Лх(К-1) Tj, (1) а пороговые элементы 10 и 11 реализуют условия . (4х(КТ)|, ; |4i(KT)l f-, ;

|л2х(кт) ; (кт)|5 е , (2)

где 0« ,2, и выдают сигналы на блок 3 коммутации .

Блок 3 .коммутации содержит первый 12 и дополнительный 13 релейные элементы с замь кающими и размыкающими контактами, структурно расположенными в интеграторе 4.

Первый релейный элемент 12 имеет три контакта, из которых первый 14 размыкающий, второй 15 и третий 16 замыкающие.

Второй дополнительный релейный элемент имеет шесть контактов, из которых первый 17 и второй 18 размыкающие, а третий 19, четвертый 20, пятый 21, шестой.22 контакты замыкающие .

Интегратор 4 содержит элемент 23 памяти на Т, входом подключенный к выходу первого элемента памяти анализатора характера изменения входног сигнала, первый 24 и второй 25 блоки суммирования соответственно на два и три входа, четыре блока умножения, первый 26, второй 27, третий 28 и четвертьм 29 с постоянными коэффициентами, соответстве нно равными 4,

0

5

5

0

0

5

0

5

Q с

Т, Т/2, Т/3. Связи в интеграторе формируются замыкающими и размыкающими контактами релейных элементов 12 и 13, реализующих интеграторы по правилам прямоугольника, трапеции и 1/3 Симпсона, разностные уравнения которых имеют вид

X (КТ) х(К-1). т +Т X (КТ); (3)

X (КТ)х(К-1) (КТ) +

+i(K-1). -(4)

х(КТ)х(К-2) (КТ)+4х((К-1) Т +

+i(K-2) TjJ , (5) где Т - период дискретности, ,1., 2,... .

Накапливаюищй сумматор 30 хранит предьщущее значение интеграла, а через элемент 31 памяти и замыкающий контакт 22 формируется значения x(K-2)Tj для реализации соотношения (5) .

Адаптивная система интегрирования работает следующим образом.

Дискретный сигнал х (КТ) с квантователя 1 подается на вход анализатора 2 и интегратор 4.

Вначале срабатывает анализатор 2, а затем работает интегратор 4. В анализаторе 2 последовательно вычисляются первая лх (КТ) и вторая д х (КТ) разности, которые поступают соответственно на пороговые элементы 10 и,11, и проверяются условия (2), в зависимости от которьгх работают релейные элементы 12 и 13, контакты которых производят коммутацию связей в интеграторе 4. Напри бер, если сигнал X (t) постоянный, то первая разность Дх(КТ) и вторая разность Лх(КТ) равны нулю, релейные элементы 12 и 13 не срабатывают, входной сигнал X (КТ) .через размыкающий контакт 14 и второй блок 27 умножения на коэффициент Т поступает на первый вход накапливающего сумматора 5 и

реализуется состояние (3).

I

Если x(t) изменяется по линейному закону, то срабатывает только первый релейный элемент 12 и через его контакты 15 и 16, 17 и 18 сигналы с квантователя в виде х (КТ) и с элемента 6 памяти анализатора в виде х(К-1) TJ поступают на входы первого блока 24 суммирования, а с него - на второй вход накапливающего сумматора 30 через третий блок 28 умножения с

1439630

коэффициентом ( /2. В сумматоре 30 второго, третьего и четвертого блоков формируется значение х (КТ) по прави- умножения на постоянные коэффициенты лу трапетдаи 4).и первого н второго блоков суммироваЕсли x(t) параболический, то ера- ния, подключенных выходами к входам батывают релейные элементы 12 и 13, соответственно третьего и четвертого так как i X (KT)i , д х(КТ) 2 , и блоков умножения на постоянные коэф- через их замкнутые жонтакты 15, 16, фициенты, выход первого блока умноже- 19, 20, 21 и 22 сигналы с квантовате- ния на постоянный коэффициент соеди- ля 1, выходов элементов 6 и 23 памя- ,. иен в интеграторе с первым входом ти поступают на три входа второго его второго блока суммирования, а выг. блока 25 суммирования, а с него через ходы второго, третьего и четвертого четвертый блок 29 умножения с коэффи- блоков умножения на постоянные коэф- циентом Т/3 - на третий вход накапли- фициенты интегратор а подключены соот- вающего сумматора 5, где суммируется g ветственно к первому, второму и . ;. с сигналом х(К-2) TJ , поступившим с третьему информационным входам накап- выхода элемента 31 памяти и замыкаю- ливающего сумматора, анализатор ха- щим контакт 22 релейного элемента 13, рактера изменения входного сигнала В результате реализуется интегрирова- дополнительно содержит последователь- ние по правилу 1/3 Симпсона (5). При iro соединенные дополнительный элемент вктуочении обратной связи через эле- памяти, блок вычисления второй раз мент 31 памяти и контакт 22 необходи- ности и дополнительный пороговый эле- мо обнулить сут матор 30, так как в мент, выход которого подключен к уп- нем хранится значение х(К-1) т , ко- равляющему входу дополнительного ре- торое не используется в формуле (5). 25 лейного элементы системы, вход дополнительного элемента памяти и другой

Формула изобретения вход блока вычисления второй разнос- ти анализатора характера изменения

Адаптивная система интегрирования входного сигнала подключены к выходу дискретных сигналов, содержащая кван- . блока вычисления первой разности, тователь входного сигнала по времени, выход первого элемента памяти анали- вход которого является входом сие- . затора характера изменения входного темы, интегратор, первый релейный сигнала подключен через последова- элемент и анализатор характера изме- тельно соединенные третий замыкаю- нения входного сигнала, выполненный щий контакт релейного элемента и парна последовательно соединенных эле- 5 вый размыкающий контакт дополнитель- менте памяти, блоке вычисления первой ного релейного элемента к первому разности и пороговом элементе, выход входу первого блока суммирования которого подключен к управляющему интегратора, второй вход первого бло- входу первого релейного элемента сие- ка суммирования которого подключен .темы, выход квантователя входного через второй размыкающий контакт до- сигнала по времени подключен к первым полнительного релейного элемента к выводам первого размыкающего и вто- второму выводу второго замыкающего рого замыкакнцего контактов первого контакта релейного элемента, а их релейного элемента, к входу элемента общий вывод подключен через третий памяти анализатора характера измене- замыкающий контакт дополнительного ния входного сигнала и к другому релейного элемента к второму входу входу блока вычисления первой разнос- второго блока суммирования интегра- ти анализатора характера изменения тора, третий вход второго блока сум- входного сигнала, отличающа- мирования.интегратора подключен через я с я тем, что, с целью повьппения 50 четвертый замыкающий контакт допол- точности интегрирования сигналов без нительного релейного элемента к вы- уменьшения периода дискретности, она ходу дополнительного элемента памяти содержит дополнительный релейный анализатора характера изменения вход- элемент, накапливающий сумматор и ного сигнала, вход первого блока ум- .элемент памяти, подключенный входом 55 ножения на постоянный коэффициент к выходу накапливающего сумматора,- подключен через пятый замыкающий кон- который является выходом системы, ин- такт дополнительного релейного эле- тегратор выполнен в виде первого, мента к -общему выводу третьего замыкающего контакта релейного элемента и первого размыкающего контакта дополнительного реле,йного элемента, вход второго блока умноже - ния на постоянный коэффициент интегратора соединен с вторьм выводом

первого размыканзщего контакта релейного элемента, выход элемента памяти подключен через шестой замыкающий контакт дополнительного релейного элемента к четвертому информационному входу накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система интегрирования дискретных сигналов | 1984 |

|

SU1179383A1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ | 2012 |

|

RU2521305C2 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| Пневматический интегратор | 1975 |

|

SU547775A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| ЭЛЕКТРОГИДРАВЛИЧЕСКИЙ СЛЕДЯЩИЙ ПРИВОД | 1990 |

|

RU2015521C1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Анализатор спектра | 1977 |

|

SU669295A1 |

| Анализатор изображений | 1989 |

|

SU1755268A1 |

Изобретение относится к системам управления и измерительной технике, предназначено для интегрирования дискретных сигналов и может быть использовано, например, в системах навигации и управления летательными аппаратами. Целью изобретения является повьпиение точности интегрирования без уменьшения периода дискретности. Система содержит квантователь 1 входного сигнала по времени, анализатор 2 характера изменения входного сигнала с блоком вычисления первой и второй разности, блок коммутации 3,блок интегрирования 4 и накапливающий сумматор 5. Анализатор 2 характера изменения входного сигнала содержит два последовательно соединенных элемента памяти на Т, блоки вычисления первой и второй разностей и пороговые элементы с зоной нечувствительности . Блок интегрирования 4 построен на элементах памяти, блоках умножения с коэффициентами, соответ- . Т Т ственно равными 4, Т, -т -, двух блоках суммирования на два и три входа. 2 шт. (Л

xW.

л(кт}

Фиг.1

| Кузин А.Т | |||

| Расчет и проектирование дискретных систем управления | |||

| М.: Машиностроение, 1962, с.121-123 | |||

| Адаптивная система интегрирования дискретных сигналов | 1984 |

|

SU1179383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1986-06-12—Подача