(54) АНАЛИЗАТОР СНЕКТРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1981 |

|

SU1002977A2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для измерения параметров магнитных лент | 1986 |

|

SU1434376A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство формирования пакетов речевой информации | 1985 |

|

SU1282344A1 |

1

Изобретение относится к вычислительной технике и может иснользоваться для анализа спектра случайных сигналов.

Известно устройство для оиределения спектральной плотности с использованием знакового преобразования, содержащее знаковые нелинейные блоки, генераторы ортогональных прямоугольных функций, генератор треугольного сигнала, квадраторы, интеграторы и сумматор 1).

Однако такое устройство служит для анализа то;1ько нормальных процессов.

В тех случаях, когда к устройствам анализа спектра предъявляются специальные требования по точности при ограничениях па их габариты, сложность, а также дополпитс.чьпые требования, диктуемые применяемой технологией изготовления, используют методы анализа спектра, основанные на дискретном представлении перерабатываемых сигналов. Дискретный анализ сиектра случайных сигналов может производиться с помощью методов пифр(М5ой фпльтрации либо посредством дпскретного преобразования Фурье (ДПФ). Предлагаемый анализатор сиектра основан на иснользовании ДИФ.

Анализаторы спектра, в которых иснол1 зуется ДПФ, строятся на основе устройства, вычисляюпдего корреляционную функшю анализируемого сигнала, и цифрового устройства, реализующего собственно дискретное преобразование Фурье.

С целью экономии вычислений и упрощения анализаторов спектра на практике применяют некоторые искусственные П1)иемы ДПФ и специализированные устройства. )e;iлизуюн ие преобразования такого тина. К числу таких устройств относятся приборы, в которых реализуются быстрые преобразования Фурье (БПФ).

Известен анализатор спектра, в котор(П; ДПФ выполняется на основе устройства, реализующего алгоритм БПФ 2. Это устройство содержит регистр чиела, квантователь сигнала, первый вход которого является входом ана,1изатора, а выход подк.пючен к первым входам блоков умножения знаков сигналов, вторые входы которых подключены к соответствующим выходам блока задержки, вход которого соединен с выходом квантователя, блок управления, четыре выхода которого соответственно подключены к управляющим входам квантователя, счетчика адресов, постоянного запоминающего устройства и к первому входу арифметического блока, второй вход которого соединен с выходом постоянного запоминающего устройства, выходы блоков умножения знаков сигналов подключены к входам соответствующих счетчиков, каждый разрядный вход которых соединен с выходом соответствующего элемента И записи, а каждый разрядный выход счетчика подключен к первому входу соответствующего элемента И считывания, вторые входы элементов И считывания и первые входы элементов И записи подключены к соответствующему выходу дещифратора, соответствующему номеру счетчика, входы дещифратора соединены с соответствующими выходами счетчика адресов, выходы элементов И считывания каждого счетчика объединены и подключены к соответствующему входу элемента ИЛИ.

Однако такие анализаторы отличаются сложностью и значительным расходом оборудования.

Целью изобретения является упрощение анаотизатора спектра.

В качестве оперативной памяти устрой ства БПФ в анализаторе спектра используют канальные счетчики коррелятора. В этом случае все время анализа может быть разделено на два этапа. В течение одного из них (составляющего больщую часть общего времени) счетчики работают как накопители коррелятора, в течение другого (при вычислении спектра) счетчики используются в качестве оперативного запоминающего устройства (ОЗУ) для хранения промежуточных и конечного результатов реализации алгоритма БПФ. Поскольку вторая часть времени оказывается существенно меньщей, чем та, в течение которой канальные счетчики работают в качестве накопителей, то быстродействие анализатора спектра в целом практически не уменьщается. Однако можно отказаться от использования в анализаторе специального блока- ОЗУ, и, таким образом, уменьшить затраты оборудования и упростить схему анализатора.

В предлагаемый анализатор спектра дополнительно введены четыре элемента И и коммутаторы записи и считывания, входы которых подключены соответственно к четвертому и пято.му выходам блока управления, выходы коммутатора записи соединены соответственно с первыми входами первого и второго элементов И, второй вход первого элемента И подключен к выходу арифметического блока, а второй вход второго элемента И подключен к выходу э.лемента ИЛИ, выходы первого и второго эле.ментов И соединены соответственно с первыми и вторыми входами разрядов регистра числа, выходы которого объединены и

подключены к первым входам третьего и четвертого элементов И, вторые входы которых подключены соответственно к перво.му и второму выходам ком.мутатора считывания, выход третьего элемента И соединен со вторыми входами элементов И заниси, а выход четвертого элемента И подключен к третьему входу арифметического блока.

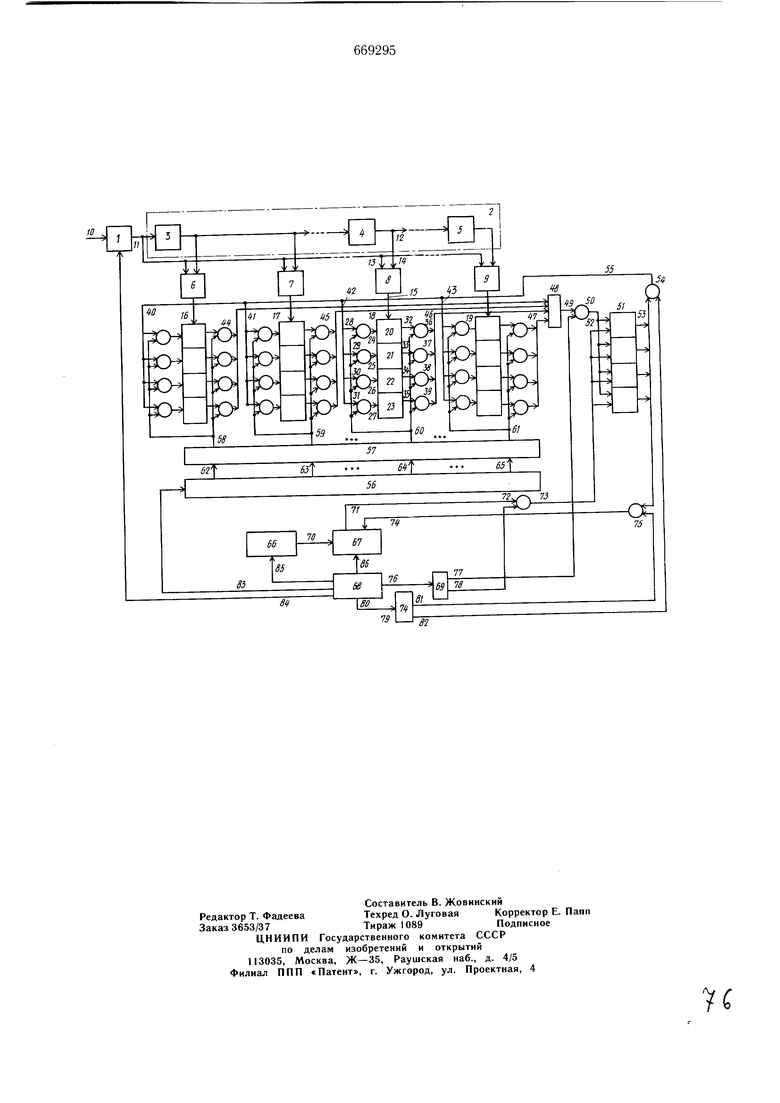

На чертеже дана структурная схе.ма описываемого анализатора спектра.

Он содержит квантователь 1 входного сигнала анализатора, блок задержки 2, элементы 3, 4 и 5 блока задержки, блоки умножения знаковых сигналов (БУЗС) 6-9, входную щину 10 квантователя 1 входного сигнала анализатора, выходную щину 11 квантователя 1 входного сигнала анализатора, выходную щину 12 линии задержки 4, входные щины 13 и 14 БУЗС, выходную щину 15 БУЗС. Устройство имеет также счетчики 16-19, разряды 20-23 счетчика 18, элементы И 24-27 записи соответствующих разрядов счетчика 18, управляющие входы 28-31 элементов И 24-27 соответственно, выходы 32-35 соответственно разрядов 20- 23 счетчика 18, э.тементы И считывания 36- 39 соответственно разрядов 20-23 счетчика 18, щины записи 40-43 информации в счетчики 16-19 соответственно, выходные щины 44-47 канальных счетчиков 16-19 соответственно, элемент ИЛИ 48, выходную щину 49 элемента ИЛИ 48, элемент И 50, регистр 51 числа, щину записи 52 в регистр 51 информации, считанной из канальных счетчиков, щину считывания 53 инфор.мации из регистра 51, элемент И 54, выходную щипу 55 элемента И, счетчик адресов 56. дешифратор 57, выходные щины 58-61 дешифратора 57, выходные щины 62-65 счетчика адресов 56. Кроме того, устройство содержит постоянное запоминающее устройство (ПЗУ) 66, арифметический блок (АБ), 67, блок управления (БУ) 68, коммутатор

69записи информации в регистр 51, щину

70связи ПЗУ 66 и АБ 67, щину 71 выдачи числовой инфор.мации из АБ 67, эле.мент И 72, шину 73 записи в регистр 51 информации, считанной из АБ 67, щину 74 записи числовой инфор.мации в АБ 67, элемент И 75, щину 76 связи БУ 68 и ко.м.мутатора записи 69, выходную щину 77 ком.мутатора 69 записи, по которой поступают сигналы управления перезаписью числа в регистр 51 из канальных счетчиков, выходную щину 78 коммутатора 69, по которой поступают сигналы управления перезаписью числа в регистр 51 числа из АБ, коммутатор 79 считывания числа из регистра 51, 80 связи БУ 68 и коммутатора 79, щину 81, по которой управляющие сигналы из БУ 68 поступают на элемент И 75, щину 82, но которой управляющие сигналы из БУ 68 поступают на элемент И 54, шину 83 связи БУ 68 и счетчика 56, шину 84 связи БУ 68 и квантователя 1 входных сигналов ана.гизатора спектра, шину 85 связи БУ 68 и ПЗУ 66, шину 86 связи БУ 68 и АБ 67. В анализаторе спектра регистр 51 нредназначен для хранения числа, считываемого с канального счетчика либо записываемого в него. Анализатор спектра работает следуюндим образом. Общий процесс переработки информации в анализаторе подразделяется на два этапа. На первом этапе вычисляется корреляционная функция в.ходного сигнала. На втором, в соответствии с алгоритмом БПФ, вычисляется энергетический спектр этого сигнала. Корреляционная функция вычисляется с помощью блока задержки 2, включающего элементы 3, 4 и 5, БУЗС 6-9 и канальных счетчиков 16-19. Энергетический спектр вычисляется на основе ПЗУ 66, АБ 67, БУ 68, коммутатора 69 записи, канальных счетчиков Гб-19, регистра 51 числа, счетчика 56 и дещифратора 57. Вычисление корреляционной функции на первом этапе осуществляется следующи.м образом. Входной сигнал анализатора по шине 10 поступает на квантователь 1. Не уменьщая общности рассмотрения, будем для определенности считать, что коррелятор анализатора работает по знаковому принципу. В этом случае квантователь осуществляет временную дискретизацию входного сигнала с шагом ЛТ и глубокое двустороннее ограничение, в результате чего на выходной -тине 11 квантователя получается случайная последовательность импульсов. Рассмотрим работу некоторого i-ro канала коррелятора. Каждый из элементов 3, 4 и 5 блока задержки 2 задерживает входной сигнал на время А Т. Поэтому на выходе элемента задержки с номером i (пусть на чертеже это будет элемент задержки 4) случайная последовательность и.мпульсов оказывается задержанной на время 1Дг. Эта последовательность поступает на входную шину 14 блока 8. На другую входную ншну 13 этого блока поступает последовательность случайных сигналов непосредственно с выходной щины 11 квантователя 1. На выходе 15 блока 8 формируется сигнал, пропорциональный произведению знаков прямого и задержанного сигналов, который поступает в счетчик 18, выполняющий функцию интегрирования и отвечаюн|ий каналу коррялятора с номером i. Число, накопленное счетчике, соответствует оценке i ординаты корре.чяционной функции. После заполнения канальных счетчиков режим вычисления корреляционной функции входного сигнала заканчивается. Начинается второй этап работы анализатора, непосредственно связанный с вычисление.м энергетического спектра входного сигнала на основе алгоритма БПФ. Особенностью второго этапа является то, что ,Ц:.ные счетчики при реализации алгоритма БПФ уже используются как блоки оперативной памяти. В соответствии с этим режимом управляющий сигнал, поступающий на квантователь 1 по шине 84 из БУ 68, отключает этот квантователь. Из БУ по щинам 76, 82, 81, 86, 85 и 83 поступают сигналы, синхронизирующие работу соответственно коммутатора 69, элементов И 54, 75, . 67, ПЗУ 66, счетчика адресов 56. Алгоритм БПФ на основе указанных узлов реализуется известным способом. Числа, представляюн ие значения коэффициентов ряда Фурье, подсчитанных в результате реализации алгоритма БПФ, накапливаются в канальных счетчиках. При реализации алгоритма БПФ информация из канальных счетчиков считывается в АБ 67 следующим образом. В соответстствии с сигналами, поступающими из БУ 68 по шине 83, устанавливаются требуемые состояния счетчика 56. Под действием сигнала, поступающего из БУ 68 по шине 76 на коммутатор 69, этот коммутатор устанавливается в такое состояние, при котором управляющий сигнал появляется на его выходной щине 77. Управляющий сигнал открывает элемент И 50. Состояния счетчика 56 деищфрируются дешифраторо.м 57. Под действием выходных сигналов дещифратора 57, появляющихся на его выходных щинах 58-61, канальные счетчики 1619 поочередно подключаются своими выходами через эле.мент Н 50 к соответстрмощим входам 52 регистра 51. В частности, ь; том случае, когда счетчик 56 находится п состоянии с номером i, в дешифраторе 57 появляется выходной сигнал на шине 60. Этот сигнал поступает на управляющие входы элементов И 24-27 п 36-39. В режиме считывания информации из АБ элемент И 54 заперт управляющим сигналом, поступающим из коммутатора 79 по щине 82. На информационные входы 28-31 элементов 24-27 по щине 42 в этом режиме информация не поступает. Зато обеспечика отся условия считывания информации из канального счетчика 18. При считывании информация из соответствующих разрядов счетчика по шинам32-35 поступает на входы элементов 36-39 соответственно. С выходов этих схем по щине 46 эта инфсфмация поступает на элемент ИЛИ 48, выход которого посредством шины 49 подсоединен к входу элемента И 50. Поскольку элемент И 50 в режиме считывания информации из АБ открыт (сигналом из коммутатора 69, поступающим по шине 77). происходит перезапись содержимого из счетчика 18 в регистр 51. Из регистра 51 под действием управляющего сигнала, поступающего из коммутатора 69 на элемент И 75 но тине 81, выполняется считывание информации из регистра 51 в АБ 67 (по шине 74). Перезапись информации из АБ в канальные счетчики выполняется так. Под действием сигнала, поступающего из БУ по шине 76, ко.ммутатор 69 устанавливается в такое состояние, при котором управляюший сигнал появляется на его вы.ходной шине 78. Этот сигнал открывает элемент П 72. Требуемое слово из АБ 67 по шине 71 переписывается в регистр 51. Сигналом, постунаюП1ИМ из БУ но 83, устанавливается в требуемое состояние счетчик 56. Его состояния дешифрируются дешифраторо.м 57. В результате оказывается нодключенным к выходу элемента И 54 тот канальный счетчик, в который должно быть переписапо слово из регистра 51. Перезапись выполняется под действие. управляющего сигна.ла, поступающего по шине 82 из ко.ммутатора 79 и открывающего э.лемент И 54. Таким образом, благодаря применению счетчиков коррелятора в качестве оператпвной памяти удается значительно упростить анализатор спектра. Формула изобретения Анализатор спектра, содержащий регистр числа, квантователь сигнала, первый в.ход которого является входом анализатора, а выход подключен к первым входам блоков ум1 ожения знаков сигналов, BTOpi ie входы которых подключены к соответствующи.м выходам блока задержки, вход которого соединен с выходо.м квантователя, б.лок управления, четыре выхода которого соответственно подключены к управляющим входам квантователя,счетчика адресов, постояиного запоминаюшего устройства и к иерBo.viy входу арифметического блока, второй вход которого соединен с выходом постоянного запоминающего устройства, выход) блоков умножения знаков сигналов подклюf

-V

чены к входа.м соответствующих счетчиков, каждый разрядный вход которых соединен с вь ходом соответствующего элемента И записи, а каждый разрядный выход счетчика нодключен к первому входу соответствующего эле.мента И считывания, вторые входы эле.ментов И считывания и первые входы элементов И записи подключены к соответствующему выходу дешифратора, входы дешифратора соединены с соответствующи.ми выходами счетчика адресов, вь ходы элементов И считывания каждого счетчика объединены и нодключены к соответствующему входу элемента ИЛИ, отличающийся тем, что, с упрощения, в него дополнительно введены четыре элеме та И и коммутаторь записи и считывания, jxoД)1 которых подключены соответственно к четвертому и пятому выхода.м блока управления, выходы коммутатора записи соединень соответственно с первыми входами первого и второго элементов И, второй вход 1ервого элемента И подключен к выход) ариф.метического блока, а второй вход второго эле.мента И подключен к выходу элемента ИЛИ, выходы первого и второго элементов И соединены соответственно с пер В)ми и входами разрядов регистра числа, выходы которого объединень и подключены к первым входа.м третьего и четвертого элементов И, вторые вход которь х подключены соответствеш о к первому и второму выхода.м коммутатора считыва ия, В з1ход третье о элемента И соединен со вторыми входами э.че.ментов И , а четвертого элемента И подключе) к .му входу арпф.метического б.юка. Источники информации, принятые во внима 1не 1ри экспертизе 1.Мирский Г. Я. Аппаратурное опреде. характеристик случайных процессов. М., «Энергия, 1972, с. 276. 2.Патент США Х 3808412, кл. 324 68. 1970. 15 «

Авторы

Даты

1979-06-25—Публикация

1977-04-11—Подача