11

Изобретение относится к измерительной регистрирующей технике и может быть использовано ;для регистрац быстропротекающих процессов (например, переходных процессов) с преобразованием масштаба времени с помощью многоканальных самопишущих приборов;

Целъ изобретения - пов ;1шение надежности устройства.

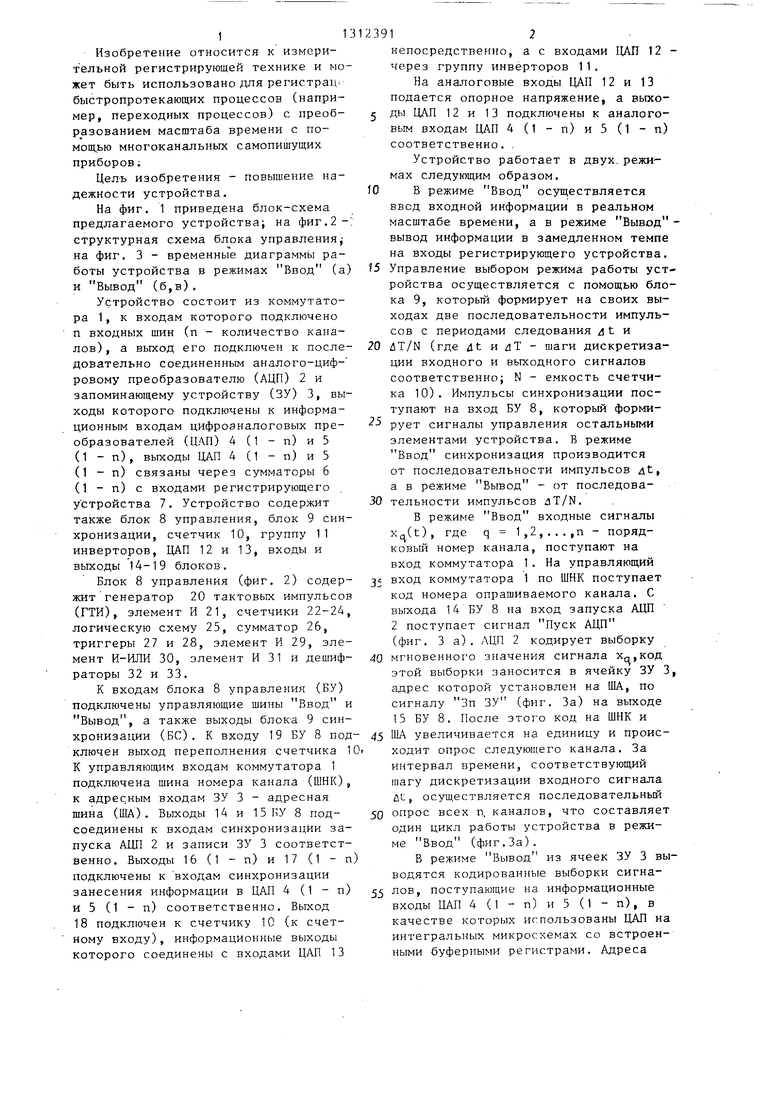

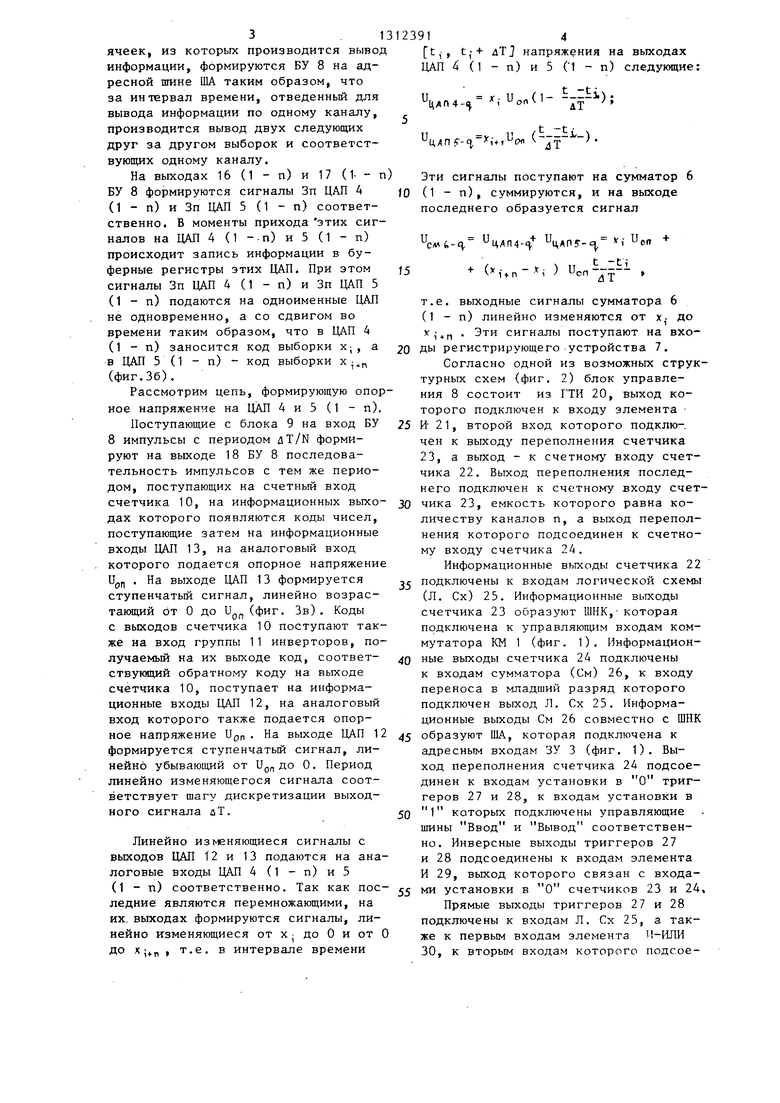

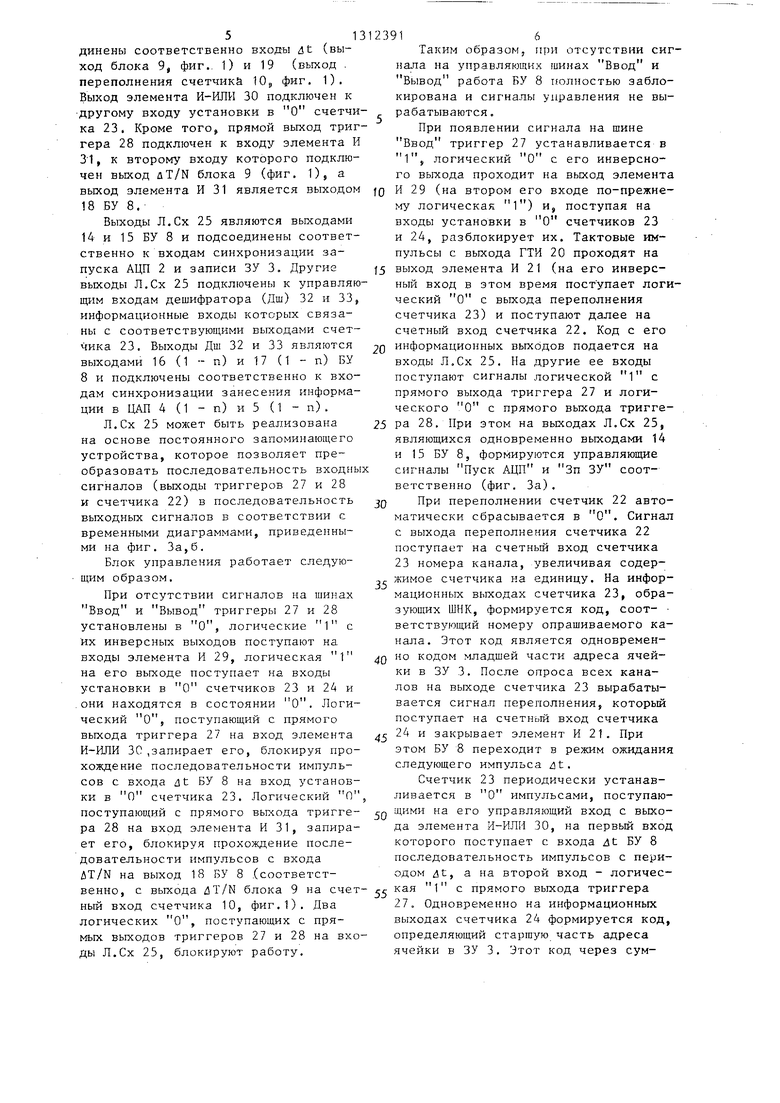

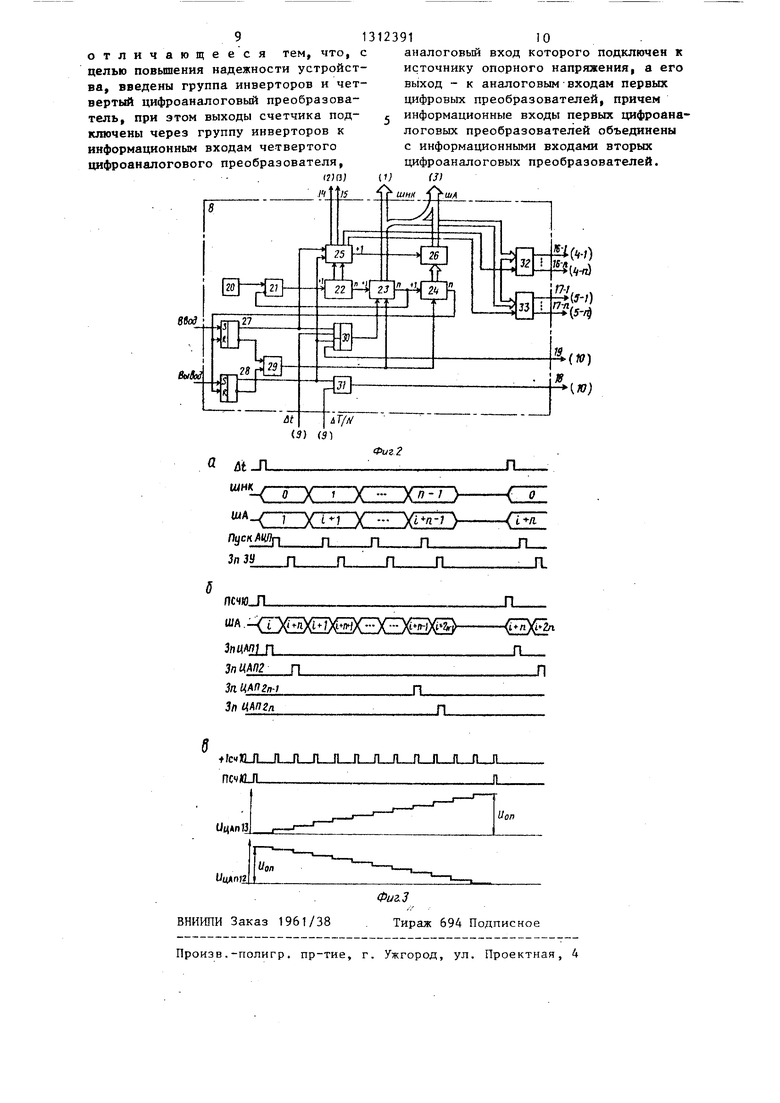

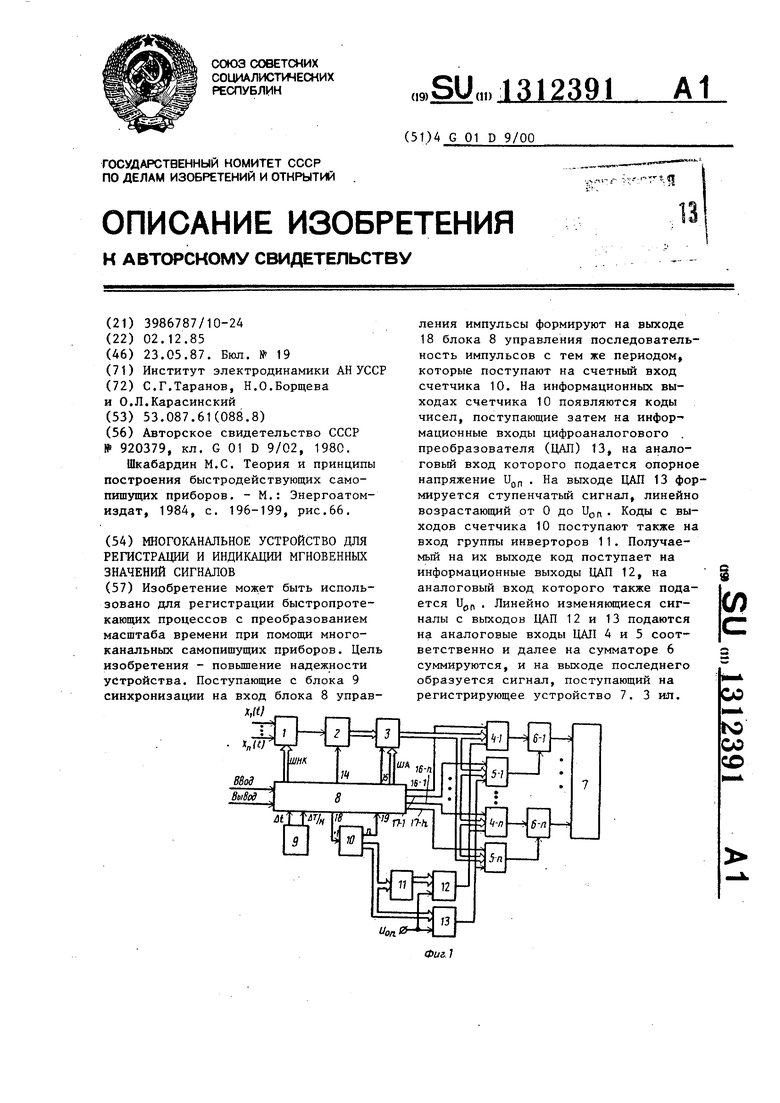

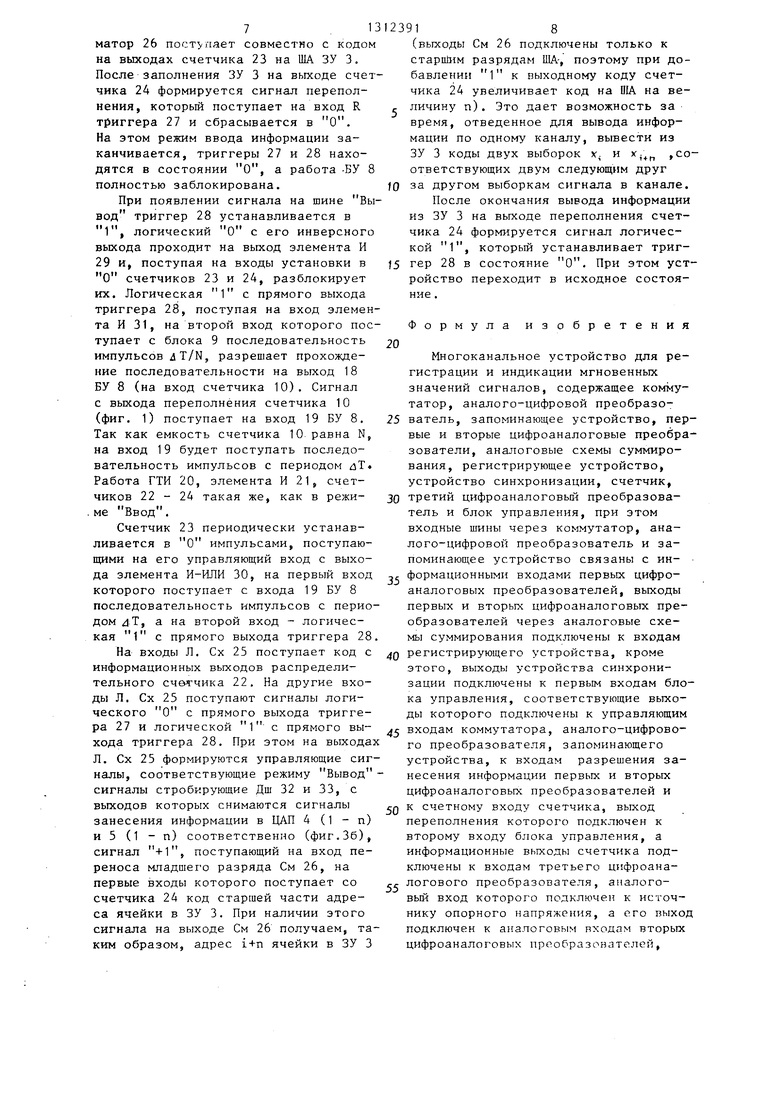

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2структурная схема блока управления на фиг. 3 - временные диаграммы работы устройства в режимах Ввод (а) и Вывод (б,в).

Устройство состоит из коммутатора 1 , к входам которого подключено п входных щин (п - количество каналов), а выход его подключен к последовательно соединенным аналого-циф- ровому преобразователю (АЦП) 2 и запоминающему устройству (ЗУ) 3, выходы которого подключены к информационным входам цифроаналоговых преобразователей (ЦЛП) 4 (1 - п) и 5 (1 - п), выходы ЦАП 4 (1 - п) и 5 (1 - п) связаны через сумматоры 6 (1 - п) с входами регистрирующего устройства 7. Устройство содержит также блок 8 управления, блок 9 синхронизации, счетчик 10, группу 11 инверторов, ЦАП 12 и 13, входы и выходы 14-19 блоков.

Блок 8 управления (фиг. 2) содержит генератор 20 тактовых импульсов (ГТИ), элемент И 21, счетчики 22-24, логическую схему 25, сумматор 26, триггеры 27 и 28, элемент И 29, элемент И-ИЛИ 30, элемент И 31 и дешифраторы 32 и 33.

К входам блока 8 управления (БУ) подключены управляющие шины Ввод и Вывод, а также выходы блока 9 синхронизации (ВС). К входу 19 БУ 8 подключен выход переполнения счетчика Ю К управляющим входам коммутатора 1 подключена шина номера канала (ШНК), к адресным входам ЗУ 3 - адресная шина (I1A). Выходы 14 и 15 БУ 8 подсоединены к входам синхронизации запуска АЦП 2 и записи ЗУ 3 соответственно. Выходы 16 (1 -п) и 17 (1 -п подключены к входам синхронизации занесения информации в ЦАП 4 (1 - п) и 5 (1 - п) соответственно. Выход 18 подключен к счетчику 10 (к счетному входу), информационные выходы которого соединены с входами ЦАП 13

12

непосредстпенно, а с входами ЦАП 12 - через группу инверторов 11.

На аналоговые входы ЦАП 12 и 13 подается опорное напряжение, а выхо- ды ЦАП 12 и 13 подключены к аналоговым входам ЦАП 4 (1 - п) и 5 (1 - п) соответственно. .

Устройство работает в двух, режимах следующим образом.

В режиме Ввод осуществляется ввод входной информации в реальном масштабе времени, а в режиме Вывод - вывод информации в замедленном темпе на входы регистрирующего устройства.

Управление выбором режима работы устройства осуществляется с помощью блока 9, который формирует на своих выходах две последовательности импульсов с периодами следования /з t и

йТ/N (где ль и аТ - шаги дискретизации входного и выходного сигналов соответственно; N - емкость счетчика 10). Импульсы синхронизации поступают на вход БУ 8, который формирует сигналы управления остальными элементами устройства, В режиме Ввод синхронизация производится от последовательности импульсов t, а в режиме Вывод - от последовательности импульсов лТ/N.

В режиме Ввод входные сигналы (t), где q 1,2,...,п - порядковый номер канала, поступают на вход коммутатора 1. На управляющий

вход коммутатора 1 по ШНК поступает код номера опрашиваемого канала. С выхода 14 БУ 8 на вход запуска АДП 2 поступает сигнал Пуск АЦП (фиг. 3 а). АЦП 2 кодирует выборку

мгновенного значения сигнала Хп,код этой выборки заносится в ячейку ЗУ 3, адрес которой установлен на ША, по сигналу Зп ЗУ (фиг. За) на выходе 15 БУ 8. После этого код на ШНК и

ША увеличивается на единицу и происходит опрос следующего канала. За интервал времени, соответствующий шагу дискретизации входного сигнала flt, осуществляется последовательный

опрос всех п. каналов, что составляет один цикл работы устройства в режиме Ввод (фиг.За).

В режиме Вывод из ячеек ЗУ 3 выводятся кодированные выборки сигналов, поступающие на информационные входы ЦАП 4 (1 - п) и 5 (1 - п), в качестве которых использованы ЦАЛ на интегральных микросхемах со встроенными буфер 1ыми регистрами. Адреса

3 . 1

ячеек, из которых производится вывод информации, формируются БУ 8 на адресной шине ША таким образом, что за интервал времени, отведенный для вывода информации по одному каналу, производится вывод двух следуюгцих друг за другом выборок и соответствующих одному каналу.

На выходах 16 (1 - п) и 17 (1- - п БУ 8 формируются сигналы Зп ЦАП 4 (1 - п) и Зп ЦАП 5 (1 - п) соответственно. В моменты прихода зтих сигналов на ЦАП 4 (1 -.п) и5 (1 -п) происходит запись информации в буферные регистры этих ЦАП. При этом сигналы Зп ЦАП 4 (1 - п) и Зп ЦАП 5 (1 - п) подаются на одноименные ЦАП не одновременно, а со сдвигом во времени таким образом, что в ЦАП 4 (1 - п) заносится код выборки Х;, а в ЦАП 5 (1 - п) - код выборки х (фиг.36).

Рассмотрим цепь, формирующую опорное напряжение на ЦАП 4 и 5 (1 - п).

Поступающие с блока 9 на вход БУ 8 импульсы с периодом лТ/N формируют на вьгходе 18 БУ 8 последовательность импульсов с тем же периодом, поступающих на счетный вход счетчика 10, на информационных выходах которого появляются коды чисел, поступающие затем на информационные входы ЦАП 13, на аналоговый вход которого подается опорное напряжение j . На выходе ЦАП 13 формируется ступенчатый сигнал, линейно возрастающий от О до Ug (фиг. Зв) . Коды с выходов счетчика 10 поступают также на вход группы 11 инверторов, получаемый на их выходе код, соответствующий обратному коду на выходе счетчика 10, поступает на информационные входы ЦАП 12, на аналоговый вход которого также подается опорное напряжение На выходе ЦАП 12 формируется ступенчатый сигнал, линейно убывающий от Ugr, до О. Период линейно изменяющегося сигнала соответствует шагу дискретизации выходного сигнала дТ.

Линейно изменяющиеся сигналы с выходов ЦАП 12 и 13 подаются на аналоговые входы ЦАП 4 (1 - п) и 5 (1 - п) соответственно. Так как последние являются перемножающими, на их. выходах формируются сигналы, линейно изменяющиеся от х до О и от О Д° т.е. в интервале времени

123914

t,-, t;+ dTj напряжения на выходах ЦАП 4 (1 -п) и5 ( 1 -п) следукицие:

HAfl4-(J. Uon(1 дТ 5

uAnf-c{, JT

Эти сигналы поступают на сумматор 6 10 (1 - п), суммируются, и на выходе последнего образуется сигнал

ЧЛП4- V ЦАПГ-с i

t -ti

СП

(i.n-- ) .е. выходные сигналы сумматора 6 (1 - п) линейно изменяются от х,- до , . Эти сигналы поступают на вхоДЬ1 регистрирующего устройства 7.

Согласно одной из возможных структурных схем (фиг. 2) блок управления 8 состоит из ГТИ 20, выход которого подключен к входу элемента

И 21, второй вход которого подклю-. чён к выходу переполнения счетчика 23, а выход - к счетному входу счетчика 22. Выход переполнения последнего подключен к счетному входу счетчика 23, емкость которого равна количеству каналов п, а выход переполнения которого подсоединен к счетному входу счетчика 24.

Информационные выходы счетчика 22

подключены к входам логической схемы (Л. Сх) 25. Информационные выходы счетчика 23 образуют ШНК,- которая подключена к управляющим входам коммутатора КМ 1 (фиг. 1). Информационные выходы счетчика 24 подключены к входам сумматора (См) 26, к входу переноса в младший разряд которого подключен выход Л. Сх 25. Информационные выходы См 26 совместно с ШНК

образуют ША, которая подключена к адресным входам ЗУ 3 (фиг. 1). Выход переполнения счетчика 24 подсоединен к входам установки в О триггеров 27 и 28, к входам установки в

1 которых подключены управляющие шины Ввод и Вывод соответственно. Инверсные выходы триггеров 27 и 28 подсоединены к входам элемента И 29, вькод которого связан с входами установки в О счетчиков 23 и 24,

Прямые выходы триггеров 27 и 28 подключены к входам Л. Сх 25, а также к первым входам элемента 30, к вторым входам которого подсое51

динены соответственно входы dt (выход блока 9, фиг., 1) и 19 (выход . переполнения счетчика Юр фиг. 1). Выход элемента И-ИЛИ 30 подключен к другому входу установки в О счетчика 23. Кроме TorOj, прямой выход триггера 28 подключен к входу элемента И 31, к второму входу которого подключен выход дТ/N блока 9 (фиг. 1)j а выход элемента И 31 является выходом 18 БУ 8.

Выходы Л.Сх 25 являются выходами 14 и 15 БУ 8 и подсоединены соответственно к входам синхронизации запуска АЦП 2 и записи ЗУ 3. Другие выходы Л.Сх 25 подключены к управляющим входам дешифратора (Дш) 32 и 33, информационные входы которых связаны с соответствующими выходами счетчика 23. Выходы Дш 32 и 33 являются выходами 16 (1 - п) и 17 (1 - п) БУ 8 и подключены соответственно к входам синхронизации занесения информации в ЦАП А (1 - п) и 5 (1 - п) .

Л.Сх 25 может быть реализована на основе постоянного запоминающего устройства, которое позволяет преобразовать последовательность входны сигналов (выходы триггеров 27 и 28 и счетчика 22) в последовательность выходных сигналов в соответствии с временными диаграммами, приведенными на фиг. За,б.

Блок управления работает следующим образом.

При отсутствии сигналов на шинах Ввод и Вывод триггеры 27 и 28 установлены в О, логические 1 с их инверсных выходов поступают на входы элемента И 29, логическая 1 на его выходе поступает на входы установки в О счетчиков 23 и 24 и .они находятся в состоянии О. Логический О, поступающий с прямого выхода триггера 27 на вход элемента И-ИЛИ 30 ,запирает его, блокируя прохождение последовательности импульсов с входа dt БУ 8 на вход установки в О счетчика 23. Логический П поступающий с прямого выхода триггера 28 на вход элемента И 31, запирает его, блокируя прохождение последовательности импульсов с входа iT/N на выход 18 БУ 8 Хсоответст- венно, с выхода 4T/N блока 9 на счетный вход счетчика 10, фиг.1). Два логических О, поступающих с прямых выходов триггеров 27 и 28 на входы Л.Сх 25, блокируют работу.

916

Таким образом, при отсутствии сигнала на управляющих шинах Ввод и Вывод работа БУ 8 полностью заблокирована и сигналы управления не вы- рабатываются.

При появлении сигнала на шине Ввод триггер 27 устанавливается в 1, логический О с его инверсного выхода проходит на выход элемента

И 29 (на втором его входе по-прежнему логическая 1) и, поступая на входы установки в О счетчиков 23 и 24, разблокирует их. Тактовые импульсы с выхода ГТИ 20 проходят на

выход элемента И 21 (на его инверсный вход в этом время поступает логический о с выхода переполнения счетчика 23) и поступалот далее на счетный вход счетчика 22. Код с его

информационных выходов подается на входы Л.Сх 25. На другие ее входы поступают сигналы логической 1 с прямого выхода триггера 27 и логического О с прямого выхода триггера 28. При этом на выходах Л.Сх 25, являющихся одновременно выходами 14 и 15 БУ 8, формируются управляющие сигналы Пуск АЦП и Зп ЗУ соответственно (фиг. За).

При переполнении счетчик 22 автоматически сбрасывается в О. Сигнал с выхода переполнения счетчика 22 поступает на счетный вход счетчика 23 номера канала, увеличивая содержимое счетчика на единицу. На информационных выходах счетчика 23, образующих ШНК, формируется код, соот- ветствующий номеру опрашиваемого канала. Этот код является одновременно кодом младшей части адреса ячейки в ЗУ 3. После опроса всех каналов на выходе счетчика 23 вырабатывается сигнал переполнения, который поступает на счетный вход счетчика

24 и закрывает элемент И 21. При

этом БУ 8 переходит в режим ожидания следующего импульса t.

Счетчик 23 периодически устанавливается в О импульсами, поступающими на его управляющий вход с выко- да элемента И-ИЛИ 30, на первый вход которого поступает с входа At БУ 8 последовательность импульсов с периодом t, а на второй вход - логическая 1 с прямого выхода триггера 27. Одновременно на информационных выходах счетчика 24 формируется код, определяющий старшую часть адреса ячейки в ЗУ 3. Этот код через сум

7 . 1

матор 26 поступает совместно с кодом на выходах счетчика 23 на ША ЗУ 3. После заполнения ЗУ 3 на выходе счетчика 24 формируется сигнал переполнения, которьй поступает на вход R триггера 27 и сбрасывается в О. На этом режим ввода информации заканчивается, триггеры 27 и 28 находятся в состоянии О, а работа -БУ 8 полностью заблокирована.

При появлении сигнала на шине Вывод триггер 28 устанавливается в 1, логический О с его инверсного выхода проходит на выход элемента И 29 и, поступая на входы установки в О счетчиков 23 и 24, разблокирует их. Логическая 1 с прямого выхода триггера 28, поступая на вход элемента И 31, на второй вход которого поступает с блока 9 последовательность импульсов 4T/N, разрешает прохождение последовательности на выход 18 БУ 8 (на вход счетчика 10), Сигнал с выхода переполнения счетчика 10 (фиг. 1) поступает на вход 19 БУ 8. Так как емкость счетчика 10 равна N, на вход 19 будет поступать последовательность импульсов с периодом ,дТ Работа ГТИ 20, элемента И 21, счетчиков 22 - 24 такая же, как в режи- .ме Ввод.

Счетчик 23 периодически устанавливается в О импульсами, поступающими на его управляющий вход с выхода элемента И-ИЛИ 30, на первый вход которого поступает с входа 19 БУ 8 последовательность импульсов с периодом 4Т, а на второй вход - логическая 1 с прямого выхода триггера 28

На входы Л. Сх 25 поступает код с информационных выходов распределительного счетчика 22. На другие входы Л. Сх 25 поступают сигналы логического О с прямого выхода триггера 27 и логической 1 с прямого выхода триггера 28. При этом на выходах Л. Сх 25 формируются управляющие сигналы, соответствующие режиму Вывод сигналы стробирующие Дш 32 и 33, с выходов которых снимаются сигналы занесения информации в ЦАП 4 (1 - п) и 5 (1 - п) соответственно (фиг.Зб), сигнал +1, поступающий на вход переноса младшего разряда См 26, на первые входы которого поступает со счетчика 24 код старшей части адреса ячейки в ЗУ 3. При наличии этого сигнала на выходе См 26 получаем, таким образом, адрес i+n ячейки в ЗУ 3

918

(выходы См 26 подключены только к старгиим разрядам ША-, поэтому при добавлении 1 к выходному коду счетчика 24 увеличивает код на IIIA на величину п). Это дает возможность за время, отведенное для вывода информации по одному каналу, вывести из ЗУ 3 коды двух выборок . и „ ,соответствующих двум следующим друг

за другом выборкам сигнала в канале. После окончания вывода информации из ЗУ 3 на выходе переполнения счетчика 24 формируется сигнал логической 1, который устанавливает триггер 28 в состояние О. При этом устройство переходит в исходное состояние .

Формула изобретения

Многоканальное устройство для регистрации и индикации мгновенных значений сигналов, содержащее коммутатор, аналого-цифровой преобразователь, запоминающее устройство, первые и вторые цифроаналоговые преобразователи, аналоговые схемы суммирования, регистрирующее устройство, устройство синхронизации, счетчик,

третий цифроаналоговьш преобразователь и блок управления, при этом входные шины через коммутатор, аналого-цифровой преобразователь и запоминающее устройство связаны с ин-

формационными входами первых цифро- аналоговых преобразователей, выходы первых и вторых цифроаналоговых преобразователей через аналоговые схемы суммирования подключены к входам

регистрирующего устройства, кроме этого, выходы устройства синхронизации подключены к первым входам блока управления, соответствующие выходы которого подключены к управляющим

входам коммутатора, аналого-цифрового преобразователя, запоминающего устройства, к входам разрешения занесения информации первых и вторых цифроаналоговых преобразователей и

к счетному входу счетчика, выход переполнения которого подключен к второму входу блока управления, а информационные выходы счетчика подключены к входам третьего цифроаналогового преобразователя, аналоговый вход которого подключен к источнику опорного напряжения, а его выход подключен к аналоговым входам вторых цифроаналоговых преобразователей.

91

отличающее ся тем, что, с целью повышения надежности устройства, введены группа инверторов и четвертый цифроаналоговый преобразователь, при этом выходы счетчика подключены через группу инверторов к информационным входам четвертого цифроаналогового преобразователя,

(г;гз;

1239110

аналоговый вход которого подключен к источнику опорного напряжения, а его выход - к аналоговым входам первых цифровых преобразователей, причем с информационные входы первых цифроана- логовых преобразователей объединены с информационными входами вторых цифроаналоговых преобразователей. (S

Ci l}

(Ю)

(5) (5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1543232A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для регистрации сигналов | 1986 |

|

SU1323856A1 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1990 |

|

SU1758576A1 |

| Измеритель параметров качества электроэнергии трехфазной сети | 1979 |

|

SU1164616A1 |

| Многоканальное устройство для регистрации сигналов | 1987 |

|

SU1439675A1 |

| Адаптивный аналого-цифровой преобразователь | 1987 |

|

SU1495991A1 |

| Устройство для формирования аналогового сигнала рассогласования | 1983 |

|

SU1104462A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

Изобретение может быть использовано для регистрации быстропроте- кающих процессов с преобразованием масштаба времени при помощи многоканальных самопишущих приборов. Цель изобретения - повышение надежности устройства. Поступающие с блока 9 синхронизации на вход блока 8 управ)i,tif nlt) ления импульсы формируют на выходе 18 блока 8 управления последовательность импульсов с тем же периодом, которые поступают на счетный вход счетчика 10. На информационных выходах счетчика 10 появляются коды чисел, поступающие затем на информационные входы цифроаналогового . преобразователя (ЦАП) 13, на аналоговый вход которого подается опорное напряжение U На выходе ЦАП 13 формируется ступенчатый сигнал, линейно возрастающий от О до Коды с выходов счетчика 10 поступают также на вход группы инверторов 11. Получае- Nbm на их выходе код поступает на информационные выходы ЦАП 12, на аналоговый вход которого также подается Uj,p . Линейно изменяющиеся сигналы с выходов ЦАП 12 и 13 подаются на аналоговые входы ЦАП 4 и 5 соответственно и далее на сумматоре 6 суммируются, и на выходе последнего образуется сигнал, поступающий на регистрирующее устройство 7. 3 ил. (Л ф

+1сч «ULJL JLJl JLJ JLJLJl JL JL

ПСч Ю .П

ицАП)

ищп)2

Фиг.3 винили Заказ 1961/38 . Тираж 694 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

| Цифровой регистратор | 1980 |

|

SU920379A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шкабардин М.С | |||

| Теория и принципы построения быстродействующих самопишущих приборов | |||

| - М.: Энергоатом- издат, 1984, с | |||

| Пылеочистительное устройство к трепальным машинам | 1923 |

|

SU196A1 |

Авторы

Даты

1987-05-23—Публикация

1985-12-02—Подача