Изобретение относится к приборостроению и может быть использовано для регистрации быстропротекающих (например, переходных) процессов с преобразованием масштаба времени при помощи многоканальных самопишущих приборов.

Целью изобретения является повышение точности и расширение частотного диапазона устройства.

На фиг. 1 приведена структурная схема предлагаемого устройства для регистрации сигналов; на фиг . 2 - один из вариантов реализации блока синхронизации; на фиг. 3 и 4 - временные диаграммы, поясняющие работу устройства регистрации; на фиг. 5 и 6 - то же, поясняющие работу блока синхронизации.

Многоканальное устройство для регистрации сигналов содержит входной преобразователь (ВхП) 1, запоминающие устройства (ЗУ) 2 и 3, мультиплексоры (Мл) 4 и 5, арифметико- логическое устройство (АЛУ) 6, регистр 7, выходной преобразователь (Вых.П) 8, регистрирующее устройство (РУ) 9, блок 10 управления (.НУ) и блок 11 синхронизации (БС).

В качестве входного преобразователя использованы последовательно соединенные коммутатор 12, на входы которого поступают входные сигналы преобразователя 1 и АЦП 13, выход которого является информационным выходом преобразователя 1.

Информационный вход преобразователя 8, выходы которого подключены

к входам многоканального РУ 9, соединен с выходом регистра 7, информационным входом ЗУ 3 и первым входом АЛУ b (фиг.1). Второй вход АЛУ 6 подключен к выходу мультиплексора 4, а выход соединен с входом регистра 7.

Первый вход мультиплексора 4 соединен с выходом ЗУ 4, а 1-е разряды второго - шестого входов первого мульти- плексора 4 соединены соответственно с выходами i, i+1, i+3, i+m+1, i+2m разрядов второго ЗУ 3 (1s1,2,..., UF log-N, где - число циклов суммирования). Информационный вход ЗУ 2 соединен с выходом преобразователя 1. Вина адреса (ША) связывает выход адреса БУ 10 с адресными входами коммутатора 12, ЗУ 2 и первым входом мультиплексора 5, причем адресные входы мультиплексора 12 и мультиплексора 5 соединены только с несколькими младшими разрядами ША. Первый (С,) и второй (С) выходы управления БУ 10 подключены соответственно к входам за- пуска АЦП 13 и синхронизации занесения информации в ЗУ 2, а третий (С) к. входу управления БС 11. Выходы БС 13, С4, С5,С6,С7 связаны соответственно с входами синхронизации зане- сения информации в ЗУ 3, управления мультиплексором 5, синхронизации записи в регистр 7 и входом управления преобразователя 8. Первый выход адреса БС 1t соединен с младшими разряда- ми ЗУ 3, второй подключен к адресным входам преобразователя 8 и к второму входу мультиплексора 5, а третий связан с адресными входами мультиплексора 4. Выход управления БС 11 подклю- чен к управляющим входам АЛУ 6. Выход мультиплексора 5 подключен к старшим разрядам адреса ЗУ 3.

Блок 10 управления содержит таймер 14, блок 15 синхронизации, счет- чик 16 адреса, триггеры 17 и 18 и элемент И 19. Выходы Т, Тй таймера 14 соединены с входами запуска БС 15. Выходы БС 15 подключены: + 1Сч к счетному входу счетчика 16; С,Са и C-j к входам управления АЦП 13; ЗУ 2, БС 11 подключены соответственно, как это описано выше. Выход переполнения счетчика 16 соединен с входом установки в О триггеров 17 и 18, прямые выходы которых подключены к входам управления БС 15, а их инверсные выходы через элемент И 19 связаны с входом установки в О счетчика 16,

входы установки в 1 триггеров 17 и 18 соответственно. Ввод и Вывод являются входами управления режимами работы устройства.

Выходной преобразователь 8 содержит п цифроаналоговых преобразователей (ЦАП) 20 - 1 ,. .. ,20-п, где п - число каналов и дешифратор 21. Адресный вход преобразователя 8 является входом дешифратора 21, выходы которого подключены к входам синхронизации занесения информации в ЦАП 20-120-п.

Входу управления преобразователя 8 соответствует выход С7 БС 11 с выходом стробирования дешифратора 21. Информационные входы ЦАП 20-1,...,20-п, объединенные между собой, подключены к выходу регистра 7, а выходы ЦАП 20-1,...,20-п являются выходами преобразователя 8.

Один из возможных вариантов реализации блока 11 синхронизации, когда общее число каналов , приведен на фиг. 2. БС 11 содержит генератор

22импульсов, счетчик 23, логическую схему 24, а также элементы И 25 - 27.

Выход генератора 22 соединен со счетным входом счетчика 23 и первыми входами элементов И 25 - 27. К входам А,В,С,Е схемы 24 подключены соответственно выходы первого, второго, третьего, четвертого и седьмого разрядов счетчика 23, вход записи которого является входом управления БС 11 и соединен с выходом Сэ БС 15. Инверсный выход переполнения счетчика

23соединен с входом разрешения счета этого счетчика, а на его входах установки постоянно установлен код X (00110000). Выходы четвертого, пятого и шестого разрядов счетчика 23 являются вторым выходом адреса БС 11 и подключены к адресному входу преобразователя 8 и второму входу мультиплексора 5, вход управления которого соединен с выходом седьмого разряда счетчика 23 (С5). Первый F , второйG и третий Н выходы схемы 24 соответственно подключены к вторым входам элементов 25 - 27, выходы которых С, С 7 и С6 подключены к входам синхронизации записи ЗУ 3, входу управления преобразователя 8 и входу синхронизации записи регистра 7. Четвертая (I), пятая (К) и шестая (L) группы выходов схемы 24 соединены соответственно с младшими разрядами адреса ЗУ 3 (первый выход адреса БС 11),

адресными входами мультиплексора 4 (третий выход адреса ЬС 11) и управляющим входом ЛЛУ 6 (выход управления ЬС 11).

В работе устройство можно выделить два режима: вгода и вывода информации.

В исходном состоянии, когда триггеры 17 и 18 находятся в состоянии О, элемент 19 открыт и счетчик 1Ь установлен в состояние О.

В режиме ввода информации в ЗУ 2 заносятся коды выбора мгновенных

значений сигналов U

1

.«Импульсом на входе Ввод триггер 17 устанавливается в 1. В этом случае БС 15 запускается только импульсами Т таймера 14 с периодом следования &t/n, где ut - шаг дискретизации входных сигналов.. После каждого импульса Т, БС 15 вырабатывает сигналы С о С Ј и + 1Сч, поступающие на входы запуска АЦП 13, синхронизации занесения информации в ЗУ 2 и на счетны вход счетчика 16 (см. временную дна- грамму на фиг. 3).

Выходной код счетчика 16 по ША поступает на адресные входы ЗУ 2 и коммутатора 12. Взаимодействие блоков устройства в режиме ввода при исполь- зовании преобразователя 1, реализованного посредством коммутатора 12 и АЦП 13, следующее. При помощи коммутатора 12 на вход АЦП 13 подается один из входных сигналов Uk(k 1,...,п). Номер входа устройства, подключаемого к АЦП 3, определяется кодом младших разрядов счетчика 16 (например, при коммутатор 12 подключен только к трем самым младшим разрядам счетчика 16). После запуска сигналом С, АЦП 13 входной сигнал UK преобразуется в код , где j - номер выборки сигнала в k-м канале. По окончании преобразования сигнала Uk в код через время tH, определяемое быстродействием АЦП 13, код х,: заносится в соответствующую ячейку ЗУ 2 в момент поступления на его вход синхронизации сигнала Сг. Затем сигнал +1Сч поступает на счетный вход счетчика 16 и он увеличивает свое состояние на единицу, а на вход АЦП 13 через коммутатор 12 поступает следующий сигнал U

к-м

и т.д.

Описанная последовательность продолжается до наступления переполнения счетчика 16. В этом случае сигнал на выходе переполнения счетчика 16 сбрасывает триггер 17 в О и устройство переходит в исходное состояние. В результате в ЗУ 2 будут занесены коды выборок мгновенных значений входных сигналов в следующем порядке:

10

5 0 5

0

5

0

(О

X

X

21

4 К-1

ПО

X

1 п

X

J

X

П К 1

где

,

х « х п

х nj

величина К зависит от емкости ЗУ

равной пК. Младшая часть адреса ячейки, в которой хранится код хKj, определяет номер канала К, а старшая - номер выборки j.

В режиме вывода информации коды выборок мгновенных значений сигналов U,, ..., им из ЗУ 2 последовательно поступают на первый вход мультиплексора 4 и после преобразования в бпаках 3-7 при помощи выходного преобразователя 8 выводится в виде непрерывных функций, регистрируемых устройством 9.

Импульсом на входе Вывод триггер 18 устанавливается в 1. В этом случае БГ 15 запускается только импульсами т таймера 14, период следования которых равен ДТ/n, где UT - шаг дискретизации выходных сигналов. Обычно Л Т ut. После каждого импульса ТЈ БС 15 вырабатывает сигналы С и через время Тп, необходимое для

3-7.

П О

х„ .. . . которые поступают первый вход мультиплексора 4 и

выполнения операций в блоках 20, + 1Сч (фиг. 4). Сигнал С3 поступает на вход управления БС 11. Код с младших разрядов адреса счетчика 16 поступает на первый вход мультиплексора 5.

Из ЗУ 2 последовательно выводятся коды выборок х,„ , х,,,,. .... х,

X

на

5 после преобразования в блоках 3-7 поступают на вход выходного преобразователя 8. Распределение преобразованных выборок по каналам осуществляется при помощи выходных сигналов

О дешифратора 21. После преобразования с помощью ЦАП 20 - к выборки хк в напряжение восстановленный сигнал канала передается на РУ 9.

Для расширения частотного диапаэо5 на интерполируемых сигналов необходимо выборку у; формировать в виде

1

8 Xi+

+ IXJ

(1)

где х-( , xj,

х - следующие друг за другом выборки интерполируемогоL .сигнала.

Для получения величины yj в соответствии с формулой (1) могут быть использованы рекуррентные соотношения

xi У2 - Уз;

Уг

+ у5;

I УЭ этом у у (

Уо

У2 + У,

(2) (3)

(4) (5)

Учитывая, что выборка , поступающая на вход мультиплексора 4, преобразуется согласно формулам (2)-(5), а затем интерполируется в соответствии с алгоритмом (1-3) введем обозначения S0 y S, 2y y, yj , S2 y2, S, хэ, St, z, , S5 z2 и запишем общий алгоритм преобразования в блоках 3-7 для выборки k-ro канала

SQ хк - SiK- ,

S«K Q Son 2N

№85К J

Мк

0 + гк

SЈK + S.,K ,

S4n. S1K+ S4K

; - с - - ч + Q Э5К а4К 2 IK 5К

(6)

(7)

(8)

(9)

(10)

(10

Величина S5k код интерполированной выборки, поступающей на вход преобразователя 8, SOK 7 S4K вспомогательные величины. Значения SOK- SJK вычисляются при поступлении из ЗУ 2 выборки х к для выбранного k-ro кана- ла, а затем для всех п-1 каналов вычисляются величины 84, Ss в общей сложности N раз.

Синхронизация работы блоков 3-7 осуществляется выходными сигналами БС 11. На структурной схеме БС 11 (фиг. 2), цифры в скобках над соответствующими выходами БС 11 обозначают номер блока, управляемого по данной шине. Запуск БС 11 осуществляется импульсом С, поступающим с БС 15, по которому в счетчик 23 записывается код, установленный на входе

0

5

0

50

5

0

5 05

данных. С этого момента счетчик 23 начинает счет выходных импульсов генератора 22, который продолжается до тех пор, пока сигнал на выходе П переполнения не запретит счет. Выходной код счетчика 23 преобразуется при помощи логической схемы 24 в сигналы управления. Сигналы на первых трех выходах (F, G, Н) схемы 24 разрешают прохождение выходных импульсов генератора 22 через элементы И 25-27.

Седьмой разряд выхода счетчика 23 подключен к входу управления мультиплексором 5, а также к входу Е схемы 24, сигнал на его выходе определяет в режиме вычисления каких величин находится БС 11. Если этот сигнал равен логическому О, то вычисляются значения S0-S 3 для канала, номер которого определяется кодом на младших разрядах счетчика адреса, если 1, то производится вычисление S., S5 для всех каналов. Так как 1-е разряды второго-шестого входов мультиплексора 4 подключены соответственно к выходам i, i+ 1,i+3, i+m+1, i + 2m разрядов ЗУ З, то прохождение кода через эти входы мультиплексора 4 соответствует его умножению на константы 1, 1/2, 1/8, 1/2N, 1/2N2 , АЛУ 6 реализует при операции над двумя операндами у и х, которые подаются соответственно на первый и второй входы АЛУ 6: z у + х, z у - х, z х, где z - результат на выходе АЛУ 6. Последняя операция z х соответствует пропусканию операнда на выход АЛУ 6 без изменений.

В соответствии с алгоритмом преобразования (формулы (6)-(11)) значения SQK- S-jK последовательно определяются для выборки обрабатываемого канала, когда на седьмом разряде выхода счетчика 23 логический О. Текущие значения S и Sg. для всех каналов вычисляются при логической 1 на выходе Е схемы 24. На временных диаграммах (фиг. 5) представлены импульсы С, поступающие на вход БС 11 (фиг. 5а) вычисляемые величины (фиг. 56), выходной код младших разрядов счетчика 16, определяющего номер канала, для которого вычисляются величины S0-S 5 интерполируемой выборки (фиг. 5в), выходной код четвертого, пятого и шестого разрядов счетчика 23 при логической 1 в седьмом разряде выхода этого счетчика, определяющий номер

канала, для которого вычисляются величины Јх, S (фиг. 5г) .

Общая для всех каналов последовательность формирования сигналов на выходах БС 11 при вычислении значеS, S5,

SS

приведений S0, S, ,

ны на фиг. 6 для одного цикла. Эти сигналы могут быть представлены также в виде таблицы, в которой принята следующая кодировка адресов и сигналов управления: 1 на выходе F есть сигнал синхронизации записи в ЗУ 3; 1 на выходе G есть сигнал строби- рования дешифратора 21, который с его выхода поступает на вход синхронизации одного из ЦАП 20; 1 на выходе Н есть сигнал синхронизации записи регистра 7. Кодами 000, 001, 010, , 100, 101 на группе выходов I, формируется младшая часть адреса на адресных входах ЗУ 3, в которых хранятся величины SQ, S, ,

Ss соответственно. Стар10

15

20

с с с 3 2. s ,

шая часть адреса на адресных входах 25 ЗУ 3, поступающая с выхода мультиплексора 5, определяет номер канала, для которого вычисляются указанные вели- - чины. Кодам 000, 001, 010, 011, 100, 101, на группе выходов К схе-30 второе запоминающее устройство, перФормула изобретения

Многоканальное устройство для регистрации сигналов, содержащее после довательно соединенные входной преобразователь и первое запоминающее устройство, а также выходной преобразователь, выходы которого подключены к регистрирующему устройству, и блок управления, первый и второй управляющие выходы которого соединены соответственно с входами управления входного преобразователя и входом синхронизации занесения информации первого запоминающего устройства, к адресным входам которого подключен выход адреса блока управления, соединенный также младшими разрядами с адресным входом входного преобразователя, отличающееся тем, что, с целью повышения точности и расширения частотного диапазона, в него введены

мы 24 задается вход, по которому код из ЗУ 3 поступает через мультиплексор 6 на вход X АЛУ 6. Для 000 это значение выборки х. k-го канала, поступающей с выхода ЗУ 2 на первый вход мультиплексора 4, для 001, 010, 011, 100, 101 - это код, поступающий с выхода ЗУ 2 и умноженный в результате монтажного сдвига на константу: 1, 1/2, 1/23, 1/2N, 1/N2 соответственно. Коды 00, 01, 10 на группе выходов L определяют операцию АЛУ , , z у - х соответственно. Значком х обозначено произвольное состояние сигналов.

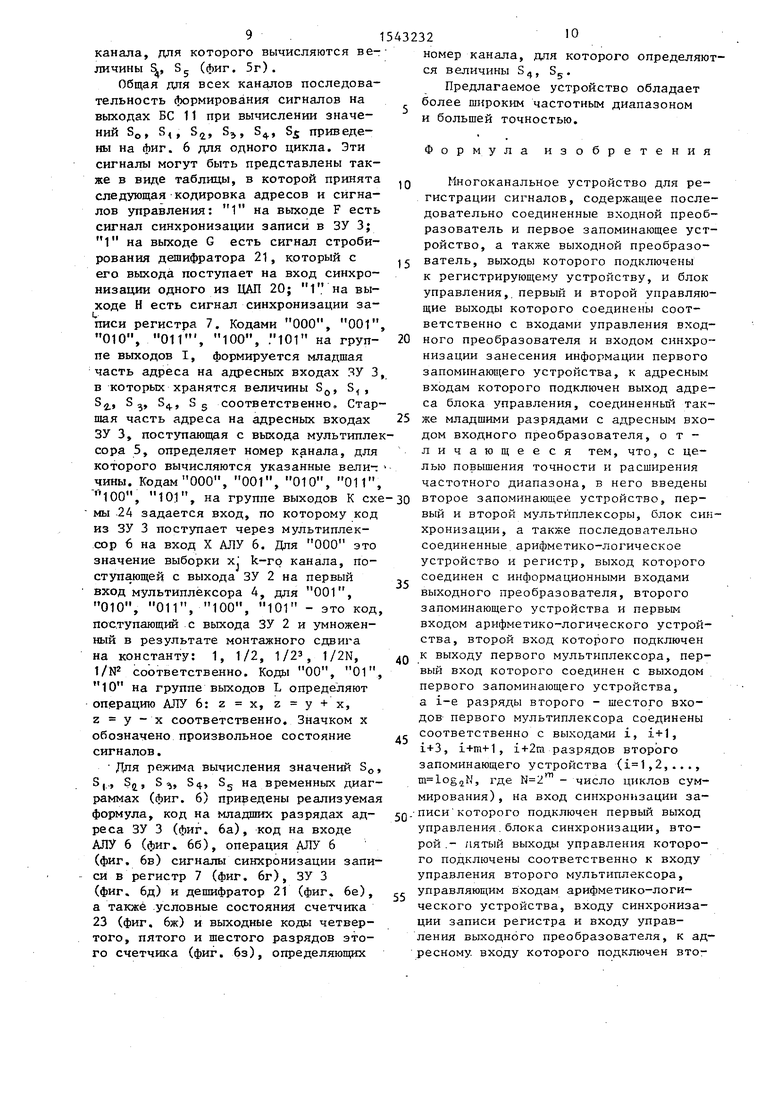

Для режима вычисления значений S0, S(, Su, S , 84., S5 на временных диаграммах (фиг. 6) приведены реализуемая формула, код на младших разрядах адреса ЗУ 3 (фиг. 6а), код на входе АЛУ 6 (фиг. 66), операция АЛУ 6 (фиг. 6в) сигналы синхронизации записи в регистр 7 (фиг. 6г), ЗУ 3 (фиг. 6д) и дешифратор 21 (фиг. бе), а также условные состояния счетчика 23 (фиг. 6ж) и выходные коды четвертого, пятого и шестого разрядов этого счетчика (фиг. 6з), определяющих

35

40

45

5С

55

вый и второй мультиплексоры, блок син хронизации, а также последовательно соединенные арифметико-логическое устройство и регистр, выход которого соединен с информационными входами выходного преобразователя, второго запоминающего устройства и первым входом арифметико-логического устройства, второй вход которого подключен к выходу первого мультиплексора, первый вход которого соединен с выходом первого запоминающего устройства, a i-e разряды второго - шестого входов первого мультиплексора соединены соответственно с выходами i, i+1, i+3, i+m+1, i+2m разрядов второго запоминающего устройства (,2,..., m log2N, где - число циклон суммирования), на вход синхронизации записи которого подключен первый выход управления блока синхронизации, второй - пятый выходы управления которого подключены соответственно к входу управления второго мультиплексора, управляющим входам арифметико-логического устройства, входу синхронизации записи регистра и входу управления выходного преобразователя, к адресному входу которого подключен вто0

5

0

5 0 второе запоминающее устройство, перномер канала, для которого определяются величины S4, S5 .

Предлагаемое устройство обладает более широким частотным диапазоном и большей точностью.

Формула изобретения

Многоканальное устройство для регистрации сигналов, содержащее последовательно соединенные входной преобразователь и первое запоминающее устройство, а также выходной преобразователь, выходы которого подключены к регистрирующему устройству, и блок управления, первый и второй управляющие выходы которого соединены соответственно с входами управления входного преобразователя и входом синхронизации занесения информации первого запоминающего устройства, к адресным входам которого подключен выход адреса блока управления, соединенный также младшими разрядами с адресным входом входного преобразователя, отличающееся тем, что, с целью повышения точности и расширения частотного диапазона, в него введены

5

0

5

С

5

вый и второй мультиплексоры, блок синхронизации, а также последовательно соединенные арифметико-логическое устройство и регистр, выход которого соединен с информационными входами выходного преобразователя, второго запоминающего устройства и первым входом арифметико-логического устройства, второй вход которого подключен к выходу первого мультиплексора, первый вход которого соединен с выходом первого запоминающего устройства, a i-e разряды второго - шестого входов первого мультиплексора соединены соответственно с выходами i, i+1, i+3, i+m+1, i+2m разрядов второго запоминающего устройства (,2,..., m log2N, где - число циклон суммирования), на вход синхронизации записи которого подключен первый выход управления блока синхронизации, второй - пятый выходы управления которого подключены соответственно к входу управления второго мультиплексора, управляющим входам арифметико-логического устройства, входу синхронизации записи регистра и входу управления выходного преобразователя, к адресному входу которого подключен второй выход адреса блока синхронизации, соединенный также с вторым входом второго мультиплексора, на первый вход которого подключены младшие разряди выхода адреса блока управления, третий управляющий выход которого соединен с входом управления блока синхронизации, третий и первый выходы

адреса которого подключены соответст венно к адресному входу первого мультиплексора и младшим разрядам адреса второго запоминающего устройства, старшие разряды адреса которого соединены с выходом второго мультиплексора.

фиг. 2

«Ч

1л1

(t$l (Hi

ГЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Устройство для вычисления параметров трехфазной сети | 1986 |

|

SU1376104A1 |

| Устройство для регистрации сигналов | 1986 |

|

SU1323856A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| Многоканальное устройство для регистрации сигналов | 1987 |

|

SU1439675A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Устройство для обработки и регистрации сигналов | 1987 |

|

SU1458845A1 |

Изобретение относится к приборостроению и может быть использовано для регистрации быстропротекающих (например, переходных) процессов с преобразованием масштаба времени при помощи многоканальных самопишуших приборов. Цель изобретения - повышение точности и расширение частотного диапазона устройства. В устройство, содержащее последовательно соединенные входной преобразователь и первое запоминающее устройство, а также выходной преобразователь, дополнительно введены второе запоминающее устройство, первый и второй мультиплексоры, блок синхронизации, а также последовательно соединенные арифметико-логическое устройство и регистр.6 ил.

I

1э

1

el

« OJ

4

| Многоканальное устройство для регистрации и индикации мгновенных значений сигналов | 1985 |

|

SU1312391A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для регистрации сигналов | 1986 |

|

SU1323856A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-02-15—Публикация

1988-04-18—Подача