Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки частотной информации.

Целью изобретения является расширение области применения за счет возможности одновременной коррекции характеристик преобразования первичных и вторичных измерительных преобраэо- вателей.

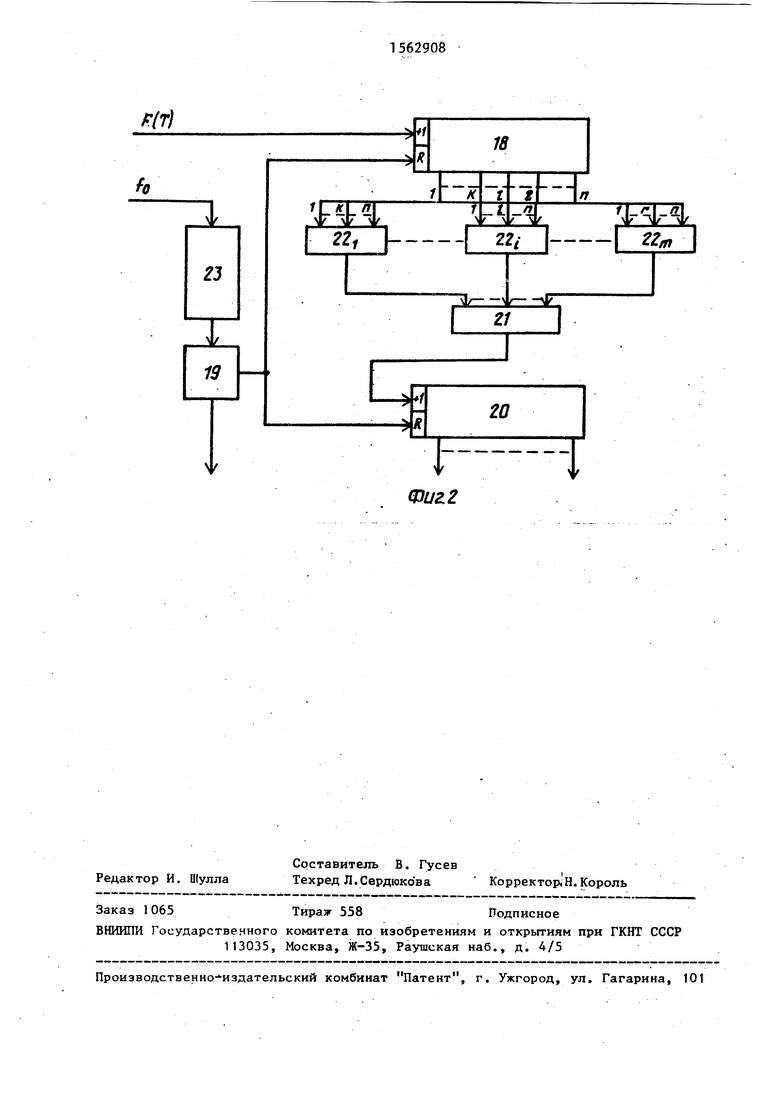

На фиг. 1 представлена функциональная схема умножителя частоты-, на фиг„ 2 - функциональная схема блока формирования кода коррекции.

Умножитель содержит узел 1 управления, первый счетчик 2, первый регистр 39 сумматор 4, второй счетчик 5, элемент 6 задержки, генератор 7 тактовых импульсов, делитель 8 час™ тоты, блок 9 формирования кода коррекции, второй регистр 10 и блок И памяти, соединенные между собой функционально 9 причем узел 1 управления содержит первый 12 к второй 13 фор™ мирователи импульсов, первый 14 и второй 15 элементы И, элемент 16 задержки и элемент ИЛИ 17 с соответствующими функциональными связями.

- Блок 9 формирования кода коррекции

содержит первый счетчик J8, формиро- ватель J9 импульсов, второй счетчик 20, элемент ИЛИ 21, m дешифраторов 22 и делитель 23 частоты, соединенные между собой функционально,

Умножитель частоты работает следующим образом.

Импульсы входной последовательности FK приходят на первый вход узла 3 управления, где подаются на вход формирователя 12 импульсов ,-который формирует импульсы по переднему Фронту импульсоз входной последовательности F. Формирователь 13 импульсов обес- печивает формирование импульсов на его выходе с некоторой задержкой .,, относительно импульсов с выхода Формирователя 12 импульсов, т.е. импульсы на выходах формирователей сдвинуты один относительно другого на интервал времени, равныйц,. Это необходимо для того, чтобы к моменту формирования второго управляющего импульса успел закончиться переходный процесс

в соответствующих элементах и узлах, т.е. для обеспечения надежной работы устройства (исключение гонок в цепях управления).

Элементы И 14 и 15, элемент 16 задержки, а также элемент ИЛИ 17 обеспечивают синхронизацию управляющих импульсных последовательностей с выхода Формирователя 12 импульсов с импульсами блока 9 Формирования кода коррекции, поступающими на второй вход узла 1 управления. Такая синхронизация необходима для того, чтобы исключить возможность нарушения работы умножителя. В том случае, когда импульсы с выхода формирователя 12 импульсов и выхода синхронизации блока 9 формирования кода коррекции формируются одновременно, элемент 14 закрыт (по инверсному входу), а элемент И 15 открыт. При этом импульс, который формируется на выходе элемента И 15, проходит через элемент 16 задержки и далее через элемент ИЛИ 17 на выход узла 1 управления. В любых других случаях открыт элемент И 4S а элемент И 15 закрыт и, следовательно, сигнал с выхода Формирователя 12 импульсов проходит через элементы И 14 и ИЛИ 17 на выход. узла 1 управления„

Задержка обеспечиваемая элементом 16 задержки, и временной интервал С, выбираются исходя из условий

jr Л /IN

2 СЭ( СЪ °а ) С1)

5

где ( Јen« ) суммарное время переключения регистра 1 0 и блока 11 памяти

Когда условия (1) выполняются, сигнал на управляющем входе сумматора 4 появляется лишь после того, как закончится переходный процесс (время переключения соответствующих элементов) в дополнительном регистре 10 и блоке 11 памяти.

В счетчике 2 (числа импульсов) в течение интервала времени, равного периоду Т к следования импульсов последовательности Fje, Формируется код, определяемый как

и

N

т«

T«-Fn.M

где FQ частота на выходе генератора 7 тактовых импульсов; М - коэффициент деления делителя 8 частоты.

Сигнал с второго выхода узла 1 управления поступает на управляющий вход сумматора 4, ив сумматоре формируется сумма М двух кодов - кодового эквивалента NT периода следования импульсов входного сигнала и кода коррекции М, поступающего на сумматор с выходов блока 11 памяти, т.е.

NЈ

NT + тх

N.

Затем импульсом с первого выхода узла 1 управления содержимое сумма - тора 4 переписывается в регистр 3. Код из регистра 3 переписывается в счетчик 5 каждым импульсом, формирующимся на выходе старшего разряда счетчика. Период появления импульсов на выходе счетчика 5 определяется как

Т.- (NT + NK)-T0.

Импульсы с выхода счетчика 5 поступают на выход умножителя, а также проходят через элемент 6 задержки и обеспечивают перепись содержимого регистра 3 в счетчик 5. Таким образом, частота следования импульсов на выходе умножителя определяется выражением

г,F0

1М N + N,

Так как N.

НТ

N,

(где

N откорректированное значение кодового эквивалента периода Тх следования импульсов входного сигнала), то справедлива запись

-i

где Т

Nze

XK

Тх -F М ,

Ч о /

откорректированный с заданной точностью период следования импульсов (без систематической погрешности) входной последовательности F при заданном значении входной влияющей величины (температуры).

Таким образом, частота следования импульсов на выходе умножителя равна

М

Я

Т -F KK о

F M УК х ч

Коды коррекции формируются следующим образом.

Частотно-импульсный сигнал, несущий информацию о дестабилизирующей величине (например, температуре), вляние которой необходимо скомпенсировать, поступает от соответствующего датчика на вход блока 9 формирования кода коррекции. В течение заданного интервала времени Тц, определяемого

5629086

коэффициентом пересчета делителя 23 частоты, импульсы входного сигнала поступают на вход счетчика 18 (числа импульсов). Состояние счетчика 18 контролируется рядом дешифраторов 221...22 , каждый из которых настроен на соответствующий участок зависимости датчика температуры (температу«0 ра - частота следования импульсов). Егпи в течение заданного TU срабатывают i дешифраторов, то на вход счетчика 20 (импульсов) через элемент ИЛИ 2 поступают i импульсов. Код,

15 Формирующийся в счетчике 20 (импульсов) в течение Тц, определяет номер участка коррекции. Данный код поступает на выходы блока 9 Формирователя кода коррекции, которые подключены к

20 информационным входам регистра 10. Первый импульс, Формирующийся на выходе формирователя 19, в момент окон

чания Т у обеспечивает перепись содержимого счетчика 20 (импульсов) в ре25 гистр 10 умножителя. Второй импульс, появляющийся на выходе формирователя 19 с некоторой задержкой Ј , выбираемой из условия надежной переписи информации из счетчика 20 (им30 пульсов) в регистр 10 умножителя,

устанавливает счетчики 18 и 20 импульсов в нулевое состояние, т.е. подготавливает их к очередному циклу работы.

Выходы регистра 10 подключены к адресным входам блока 1I памяти, в ячейки которого записаны соответствующие коды коррекции Nk. Каждому i-му участку соответствует свой код

35

N

к;

рассчитываемый из условия обеспечения минимальной (допустимой) погрешности умножения внутри каждого из участков коррекции. Следовательно, коррекция выполняется на основе ме- тода кусочно-ступенчатой аппроксимации. Объем V блока 11 памяти зависит

от числа т участков коррекции и кодов

m

коррекции N4 , т.е. V 21-N. Вводя

поправки,- можно обеспечить высокую точность умножения в широком диапазоне влияющих величин (температуры). Таким образом, умножитель частоты выполняет коррекцию характеристики преобразования первичных и вторичных измерительных преобразователей, выходным сигналом которых является частота следования импульсов. Это существенно расширяет область применения

редлагаемого умножителя по сравнению известным. Умножитель выполняет редпроцессорную обработку информаии, что определяет его более высоие технико-экономические показатели.

ормула изобретения

I. Умножитель частоты, содержащий д генератор тактовых импульсов, дели- те#ь частоты, первый и второй счетчики, первый регистр, элемент задержки и блок памяти, причем выход генератора тактовых импульсов соединен с ин- j формационным входом делителя частоты и счетным входом второго счетчика, упаковочные входы которого соединены соответственно с разрядными выходами первого регистра, выход второго счет-2Q чика соединен с выходом умножителя и входом элемента задержки, выход которого соединен с входом разрешения параллельной записи второго счетчика, выход делителя частоты соединен со 25 счетным входом первого счетчика, о т- личающийся тем, что, с целью расширения области применения за счет возможности одновременной коррекции характеристики преобразования 30 первичных и вторичных измерительных преобразователей, в него введены блок Формирования кода коррекции, второй регистр, сумматор и узел управления, содержащий первый формирователь им- , пульсов, вход которого соединен с информационным входом узла управления, выход первого формирователя импульсов соединен с входом второго формирователя импульсов и первыми входами пер- дд вого и второго элементов И, вторые входы которых соединены с управляющим входом узла управления, выход второго формирователя импульсов соединен с первым выходом узла управле- 45 ния, выход первого элемента И соединен с первым входом элемента ИЛИ, выход второго элемента И соединен с входом элемента задержки, выход которого соединен с вторым входом эле- CQ мента ИЛИ, выход которого соединен с вторым выходом узла управления, при- . чем информационный вход узла управле- ния соединен с первым информационным входом умножителя, второй информаци-

онный вход которого соединен с информационным входом блока формирования кода коррекции, разрядные выходы которого соединены соответственно с информационными входами второго регистра, разрядные выходы которого соединены соответственно с адресными входами блока памяти, выходы которого соединены соответственно с входами первой группы сумматора, входы второй группы которого соединены соответственно с разрядными выходами первого счетчика, разрядные выходы сумматора соединены соответственно с информационными входами первого регистра, вход разрешения записи которого соединен с входами установки в О первого счетчика и делителя частоты и с первым выходом узла управления, второй выход которого соединен с управляющим входом сумматора, выход генератора тактовых импульсов соединен с тактовым входом блока формирования кода коррекции, выход синхронизации которого соединен с входом разрешения записи второго регистра и управляющим входом узла управления,

2. Умножитель по п. I , о т л и - чающийс я тем, что блок формирования кода коррекции содержит первый и второй счетчики, m дешифраторов (где m 1,2,3,...), элемент ИЛИ, делитель частоты и формирователь импульсов, причем счетный вход первого счетчика соединен с информационным входом блока формирования кода коррекции, тактовый вход которого соединен с входом делителя частоты, выход которого соединен с входом формирователя импульсов, первый выход которого соединен с выходом синхронизации блока формирования кода коррекции, второй выход формирователя импульсов соединен с входами установки в О первого и второго счетчиков, разрядные выходы первого счетчика соединены соответственно с входами m дешифраторов, выходы которых соединены с входами элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, разрядные выходы которого являются разрядными выходами блока формирования кода коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство формирования сигнала сдвинутой частоты | 1986 |

|

SU1394426A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Устройство для контроля аппарата магнитной записи | 1985 |

|

SU1283848A1 |

| Оптическое устройство для вычисления корреляционной функции | 1988 |

|

SU1520541A1 |

| Умножитель частоты | 1985 |

|

SU1305822A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки частотной информации. Целью изобретения является расширение области применения за счет обеспечения возможности одновременной коррекции характеристик преобразования первичных и вторичных измерительных преобразователей. Умножитель частоты содержит узел 1 управления, первый счетчик 2, первый регистр 3, сумматор 4, второй счетчик 5, элемент 6 задержки, генератор 7 тактовых импульсов, делитель 8 частоты, блок 9 формирования кода коррекции, второй регистр 10 и блок 11 памяти, соединенные между собой функционально. Узел 1 управления содержит два формирователя 12, 13 импульсов, два элемента И 14, 15, элемент 16 задержки и элемент ИЛИ 17 с соответствующими функциональными связями. 1 з.п. ф-лы, 2 ил.

| Умножитель частоты | 1978 |

|

SU781832A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения частоты следования импульсов | 1986 |

|

SU1410027A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-29—Подача