2S

СО

00 О1

о©

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации неисправностей | 1986 |

|

SU1429116A1 |

| Устройство для регистрации состояний контролируемого блока | 1984 |

|

SU1236488A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1989 |

|

SU1679492A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

.3}

t 2 . Счетчик 18 подсчитывает количество переполнений счетчика 13, измеряя интервал tit 2 ъ единицах, равных 2 тактам, элементы И 9, 19 и триггер 17 сбрасывают счетчики 13 и 18 в конце каждого измерения, эле1

Изобретение относится к вычислительной технике и автоматике и может быть использовано в устройствах контроля блоков.

Цель изобретения - увеличение информативности о регистрируемой информации.

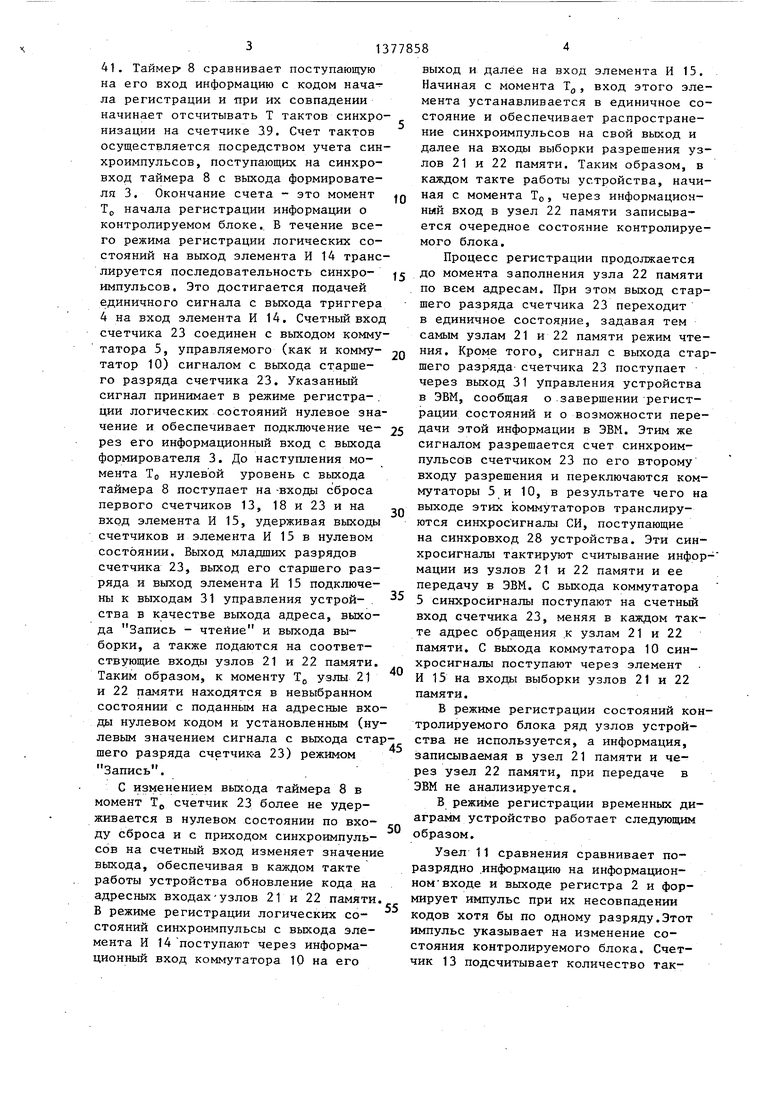

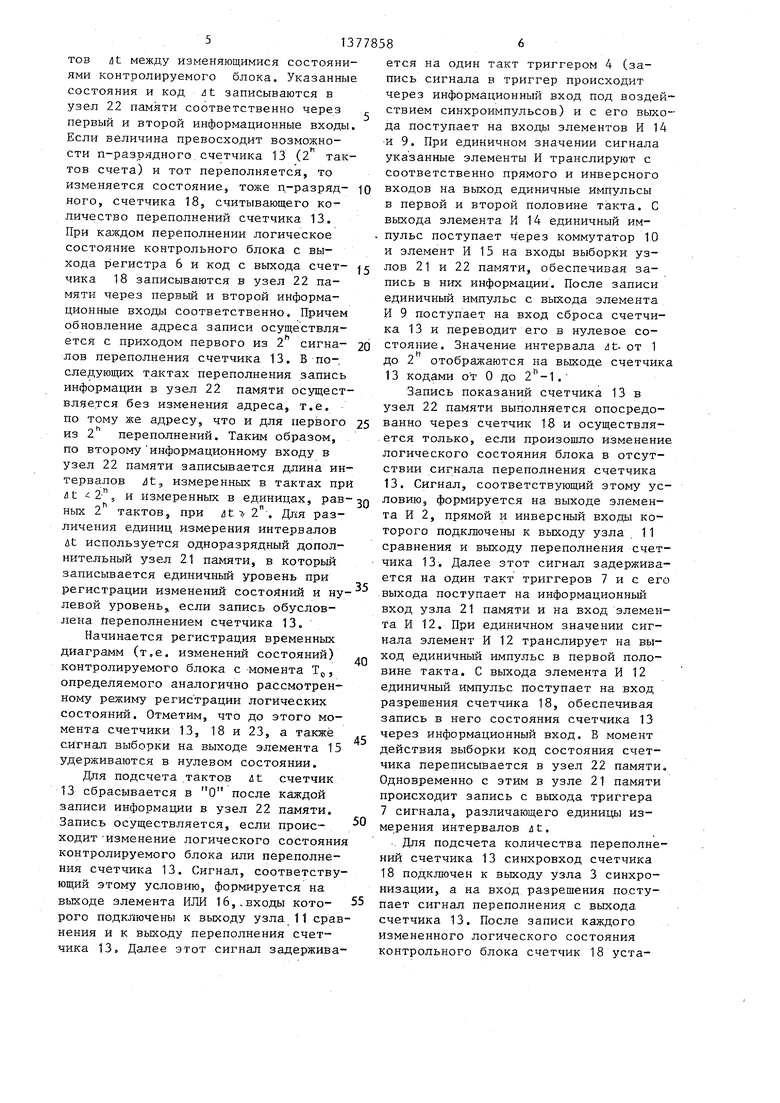

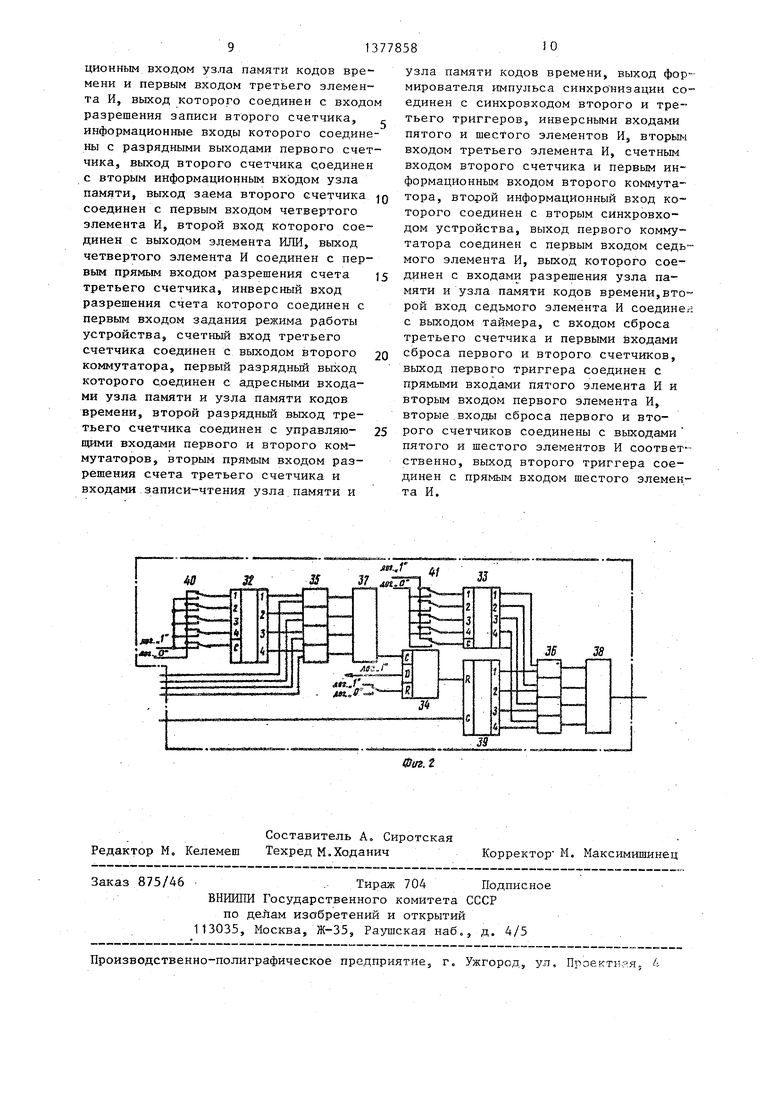

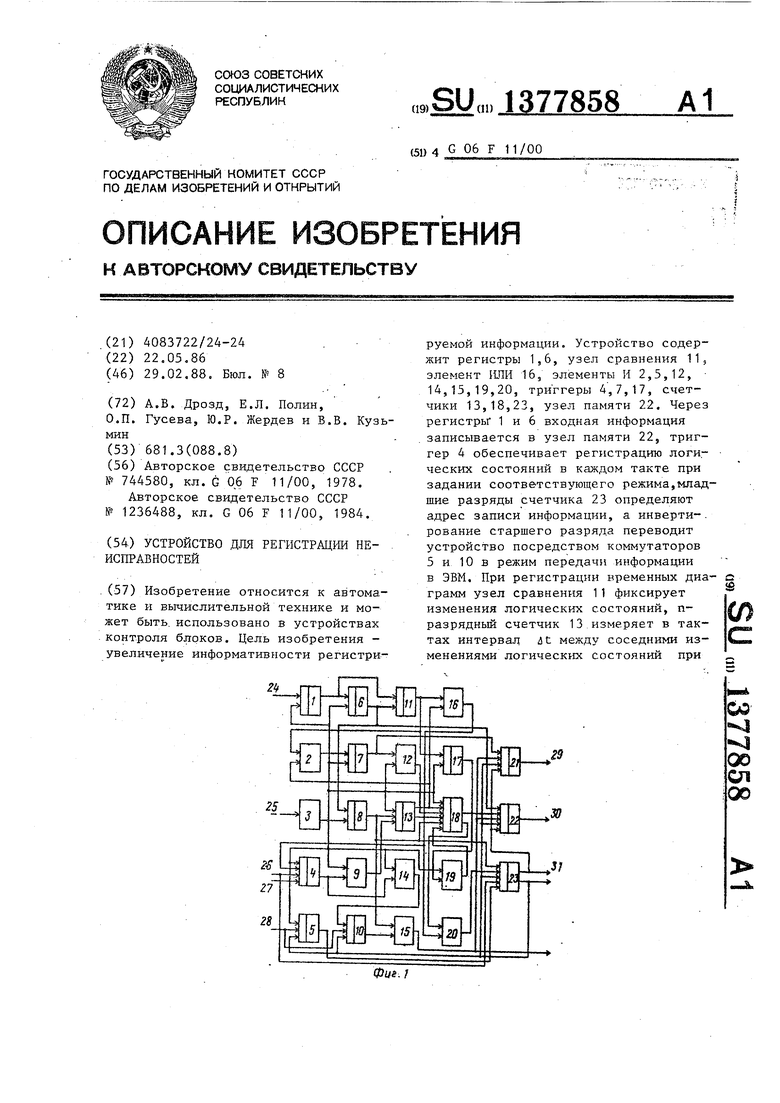

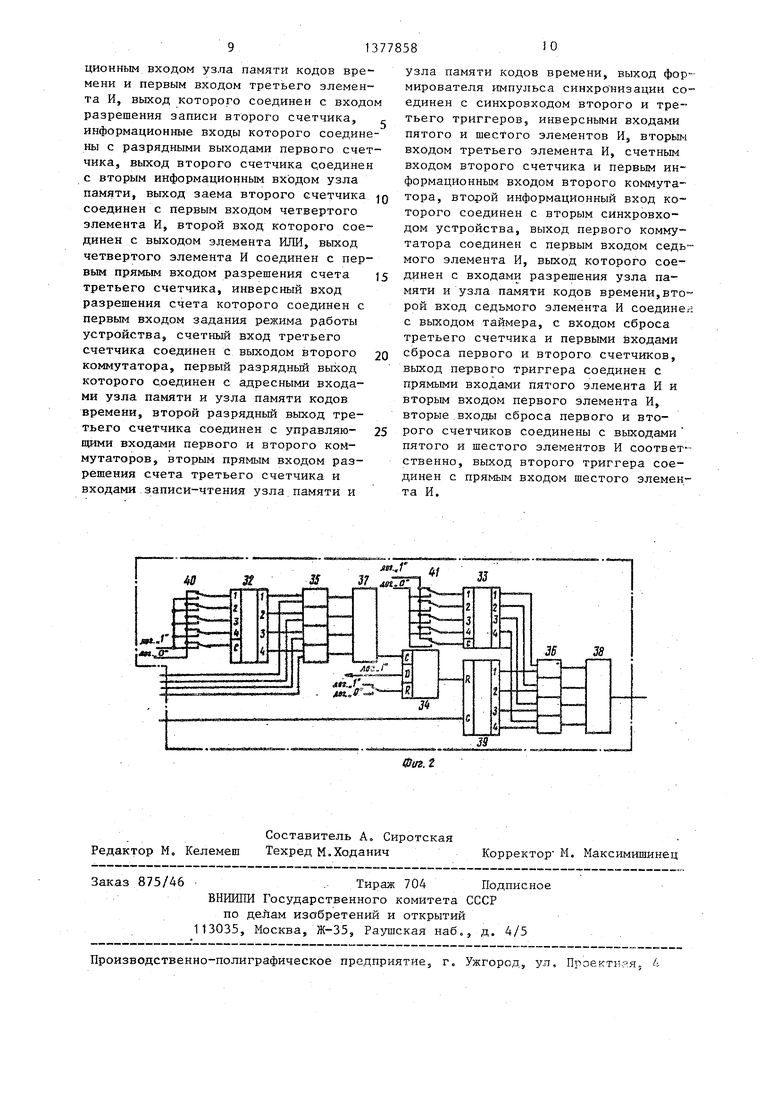

На фиг. 1 показано предложенное устройство регистрации; на фиг. 2 - схема таймера.

Уст ройство содержит регистр 1, элемент И 2, формирователь 3 импульсов синхронизации, триггер 4, коммутатор 5, регистр 6, второй триггер 7, таймер 8, элемент И 9, коммутатор 10, узел 11 сравнения, элемент И 12,счетчик 13, элемента К 14 и 15, элемент ИЛИ 16, триггер 17, счетчик 18, элементы И 19, 20, узел 21 памяти кодов времени, узел 22 памяти, счетчик 23, информационнЕ 1й вход 24 устройства, синхровкод 25 устройства вход 26 режима работы устройства, вход 27 запуска устройства, синхровход 28 устройства, второй 29 и первый 30 информационные выходы устройства, выходы

31управления устройства (выход адреса, выход Запись - чтение, выход выборки) 31.

Таймер (фиг.2) содержит регистры

32и 33, триггер 34, элементы сравнения 35 и 36, элементы ИЛИ 37, 38, счетчик 39, шину 40 задания начального кода регистрации, шину 41 задания кода задержки регистрации.

Устройство обеспечивает регистрацию логических состояний или регистрацию временных диаграмм контролируемого блока и последующую пересылку информации в ЭВМ.

Начало и состояние работы устройства задается единичным значением сиг- нала Пуск, поступающим через вход

менты И 2,12,14,15, И.ПИ 16, И 20 и триггер 7 обеспечивают запись соответствующего измерения в узел памяти 22, при этом в узел памяти 21 заносится информация о том, в какой единице был измерен интервал ut, 2 ил.

27 запуска устройства на вход сброса триггера 4. Предыдущее нулевое значение сигнала Пуск обеспечивает нулевое исходное состояние триггера 4.

В режиме регистрации логических состояний триггер 4 переводится в единичное состояние сигналом Режим, поступающим на установочный вход триггера 4 через вход 26 режима устрой-0 ства. Кроме того, сигнал Режим поступает на инверсный первый вход разрешения счета счетчика 23, что обеспечивает беспрепятственное восприятие счетчиком 23 синхроимпульсов в режиме

5 регистрации логических состояний контролируемого устройства. Синхронизация устройства в этом режиме осуществляется посредством синхроимпульсов (СИ), поступающих вместе с сигналом

разрешения на вход формирователя 3 через синхровход 25 устройства. Синхроимпульсы транслируются на выход формирователя 3 и далее на синхровхо- ды регистров 1 и 6, синхровходы триг-5 геров 4, 7 и 17 на. синхровход узла запуска таймера 8 и на счетные входы счетчиков 13 и 18, а также на вход элемента И 12, не инверсные входы . элементов И 9 и 19 и на вход элемен30 та И 14. Посредством этих синхроимпульсов выполняется тактирование работы устройства. В каждом такте син хронизации значение входных сигналов, поступающих на информационный вход

5 24 устройства, запоминается в регистре 1, затем переписывается в регистр 6. С выхода последнего информация поступает на информационный вход узла 22 памяти и на вход таймера 8.Тай40 мер 8 хранит код начала регистрации

и код задержки регистрации, устанав- ливаемые в нем, например, с помощью тумблерных переключателей (шин) 40,

С изменением выхода таймера 8 в момент TO счетчик 23 более не удерживается в нулевом состоянии по входу сброса и с приходом синхроимпульсов на счетный вход изменяет значени выхода, обеспечивая в каждом такте работы устройства обновление кода на адресных входах-узлов 21 и 22 памяти В режиме регистрации логических состояний синхроимпульсы с выхода элемента И 14 поступают через информационный вход коммутатора 10 на его

с выхода ста 23) режимом

0

Q

5

0

5

0

0

5

выход и далее на вход элемента И 13. Начиная с момента Т, вход этого элемента устанавливается в единичное состояние и обеспечивает распространение синхроимпульсов на свой вькод и далее на входы выборки разрешения узлов 21 и 22 памяти. Таким образом, в каждом такте работы устройства, начиная с момента TO, через информационный вход в узел 22 памяти записывается очередное состояние контролируемого блока.

Процесс регистрации продолжается до момента заполнения узла 22 памяти по всем адресам. При этом выход старшего разряда счетчика 23 переходит в единичное состояние, задавая тем самым узлам 21 и 22 памяти режим чтения. Кроме того, сигнал с выхода старшего разряда счетчика 23 поступает через выход 31 управления устройства в ЭВМ, сообщая о .завершении регистрации состояний и о возможности передачи этой информации в ЭВМ. Этим же сигналом разрешается счет синхроимпульсов счетчиком 23 по его второму входу разрешения и переключаются коммутаторы 5 и 10, в результате чего на выходе этих коммутаторов транслируются синхросигналы СИ, поступающие на синхровход 28 устройства. Эти синхросигналы тактируют считывание инфор- мации из узлов 21 и 22 памяти и ее передачу в ЭВМ. С выхода коммутатора 5 синхросигналы поступают на счетный вход счетчика 23, меняя в каждом такте адрес обращения .к узлам 21 и 22 памяти, С выхода коммутатора 10 синхросигналы поступают через элемент И 15 на входы выборки узлов 21 и 22 памяти.

В режиме регистрации состояний контролируемого блока ряд узлов устройства не используется, а информация, записываемая в узел 21 памяти и через узел 22 памяти, при передаче в ЭВМ не анализируется.

В режиме регистрации временных диаграмм устройство работает следующим образом.

Узел 11 сравнения сравнивает поразрядно информацию на информационном входе и выходе регистра 2 и формирует импульс при их несовпадении кодов хотя бы по одному разряду.Этот импульс указывает на изменение состояния контролируемого блока. Счетчик 13 подсчитывает количество тактов ut между изменяющимися состояниями контролируемого блока. Указанны состояния и код 4t записываются в узел 22 памяти соответственно через первый и второй информационные входы Если величина превосходит возможности п-разрядного.счетчика 13 (2 тактов счета) и тот переполняется, то изменяется состояние, тоже п-разряд- ного, счетчика 18, считывающего количество переполнений счетчика 13. При каждом переполнении логическое состояние контрольного блока с выхода регистра 6 и код с выхода счет- чика 18 записываются в узел 22 памяти через первый и второй информационные входы соответственно. Причем обновление адреса записи осущеЪтвля- ется с приходом первого из 2 сигна- лов переполнения счетчика 13. В последующих тактах переполнения запись информации в узел 22 памяти осуществляется без изменения адреса, т.е. - по тому же адресу, что и для первого из 2 переполнений. Таким образом, по второму информационному входу в узел 22 памяти записывается длина интервалов t,j измеренных в тактах пр at Z, и измеренных в единицах, рав ных 2 тактов, при it -г, . Для различения единиц измерения интервалов &t используется одноразрядный дополнительный узел 2,1 памяти, в который записывается единичный уровень при регистрации изменений состояний и ну левой уровень,, если запись обусловлена переполнением счетчика 13.

Начинается регистрация временных диаграмм (т.е. изменений состояний) контролируемого блока с -момента Т, определяемого аналогично рассмотренному режиму регис трации логических состояний. Отметим, что до этого момента счетчики 13, 18 и 23, а также сигнал выборки на выходе элемента 15 удерживаются в нулевом состоянии.

Для подсчета ,тактов ut счетчик 13 сбрасывается в О после каждой записи информации в узел 22 памяти. Запись осуществляется, если проис- ходит изменение логического состояния контролируемого блока или переполнения счетчика 13. Сигнал, соответствующий этому условию, формируется на выходе элемента ИЛИ 16,.входы кото- рого подключены к выходу узла 11 сравнения и к выхаду переполнения счетчика 13. Далее этот сигнал задержива

0 5 n

5

0

5

ется на один такт триггером 4 (запись сигнала в триггер происходит через информационный вход под воздействием синхроимпульсов) и с его выхода поступает на входы элементов И 14 -и 9. При единичном значении сигнала указанные элементы И транслируют с соответственно прямого и инверсного входов на выход единичные имцульсы в первой и второй половине такта. С выхода элемента И 14 единичный импульс поступает через коммутатор 10 и элемент И 15 на входы выборки узлов 21 и 22 памяти, обеспечивая запись в них информации. После записи единичный импульс с выхода элемента И 9 поступает на вход сброса счетчика 13 и переводит его в нулевое состояние. Значение интервала лt. от 1 до 2 отображаются на выходе счетчика 13 кодами от О до .

Запись показаний счетчика 13 в узел 22 памяти выполняется опосредованно через счетчик 18 и осуществляется только, если произошло изменение логического состояния блока в отсутствии сигнала переполнения счетчика 13. Сигнал, соответствующий этому условию, формируется на выходе элемента И 2, прямой и инверсный входы которого подключены к выходу узла , 11 сравнения и выходу переполнения счетчика 13-. Далее этот сигнал задерживается на один такт триггеров 7 и с его .выхода поступает на информационный вход узла 21 памяти и на вход элемента И 12, При единичном значении сигнала элемент И 12 транслирует на выход единичный импульс в первой половине такта. С выхода элемента И 12 единичный импульс поступает на вход разрешения счетчика 18, обеспечивая запись в него состояния счетчика 13 через информационный вход. В момент действия выборки код состояния счетчика перецисывается в узел 22 памяти. Одновременно с этим в узле 21 памяти происходит запись с выхода триггера 7 сигнала, различающего единицы измерения интервалов it.

-. Для подсчета количества переполнений счетчика 13 синхровход счетчика 18 подключен к выходу узла 3 синхронизации, а на вход разрешения поступает сигнал переполнения с выхода счетчика 13. После записи каждого измененного логического состояния контрольного блока счетчик 18 устанавливается в О. Для этого сигнал с выхода узла 11 сравнения задерживается на один таКт на триггере 7 и с его выхода поступает на вход эле- мента И 19. При единичном значении сигнала элемент И 19 транслирует на выход единичный импульс во второй половине такта. Этот импульс поступает на вход сброса счетчика 18, ус- танавливая его в нулевое состояние. Счетчик 18 измеряет величину в пределах от 1 до 2, принимая при этом значение 1,..., , 0. Сигнал, указывающий на нулевое состояние счет- чика 18 поступает с его выхода на вход элемента И 20. На другой вход этого элемента приходит сигнал с выхода элемента ИЛИ 16. Элемент И 20 формирует сигнал, поступающий на вхо разрешения счета счетчика 23. Этот сигнал разрешает изменять состояние счетяика 23 под действием синхроимпульсов в моменты перед записью изменившегося логического состояния кон- тролируемого блока или при первом из 2 переполнений счетчика 13. Та- КИМ образом, все последующие переполнения (из множества 2) регистрируются в узлах 21 и 22 памяти по тем же адресам, что и первое. После заполнения узлов памяти выход старшего разряда счетчика 23 инвертируется, и начинается процесс пересьшки информации в ЭВМ. .

Устройство в режиме регистрации временных диаграмм измеряет и за- письгоает в память интерв.алы и t между изменениями логических состояний контролируемого блока в двух едини- цах: в тактах работы устройства, если at 2, и единицах, равных 2, если 4t 7 2. Это позволяет экономно использовать память при больших интервалах /Jt.

Предложенное устройство може г эфт фективно использоваться при анализе контролируемой информации на возникновении в ней запрещенных кодов и дальнейшего изменения информации. Это важно, например, при исследовании (с целью корректировки) генераторов псевдослучайных последовательностей, предназначенных для технологического контроля цифровых схем. Эти генераторы задают последователь- ность входных воздействий на проверяемую и эталонную аппаратуру, где определенные наборы входных воздей

5 0 5 о

Q с

5

0

ствий могут быть запрещенными, так как вызывают неоднозначную реакцию аппаратуры на выходе.

I

Формула изобретения

Устройство для регистрации неисправностей, содержащее формирователь импульсов синхронизации, два регистра, узел сравнения, узел памяти,первый коммутатор, триггер, таймер, элемент ИЛИ, первый элемент И, первый счетчик, причем информационный вход первого регистра является информационным входом устройства, выход первого регистра соединен с информационным входом второго регистра и первым входом узла сравнения, второй вход которого соединен с выходом второго регистра, с информационным входом тайме ра и первым информационным входом узла памяти, первый вход элемента ИЛИ соединен с выходом Равно узла сравнения, второй вход элемента ИЛИ соединен с выходом заема первого счетчика, выход элемента ИЛИ соединен с D-входом триггера, вход сброса которого является входом запуска устройства, вход установки первого триггера является первым входом задания режима работы устройства, первый вход синхронизации которого соединен через формирователь импульса синхронизации с синхровходами первого и второго регистров, таймера, счетным входом первого счетчика, синхровходом первого триггера и первым входом первого элемента И, выход которого соединен с первым информационным входом первого- коммутатора, второй информационный вход которого соединен с вторым синхровходом устройства, отличающееся тем, что, с целью увеличения информативности о регистрируемой информации, устройство содержит с второго по седьмой элементы И, второй коммутатор, второй и третий триггеры, второй и третий счетчики и узел памяти кодов времени, причем выход Равно узла сравнения соединен с информационным входом второго триггера и первым входом второго элемента И, второй вход которого соединен с выходом заема первого счетчика и входом разрешения счета второго счетчика,выход второго элемента И соединен с информационным входом третьего триггера, выход которого соединен с информационным входом узла памяти кодов времени и первым входом третьего элемента И, выход которого соединен с входо разрешения записи второго счетчика, информационные входы которого соединены с разрядными выходами первого счетчика, выход второго счетчика соединен с вторым информационным входом узла памяти, выход заема второго счетчика соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом элемента РШИ, выход четвертого элемента И соединен с первым прямым входом разрешения счета третьего счетчика, инверсный вход разрешения счета которого соединен с первым входом задания режима работы устройства, счетный вход третьего счетчика соединен с выходом второго коммутатора, первый разрядный выход которого соединен с адресными входами узла памяти и узла памяти кодов времени, второй разрядный выход третьего счетчика соединен с управляю- щими вxoдajми первого и второго коммутаторов, вторым прямым входом разрешения счета третьего счетчика и входами записи-чтения узла памяти и

узла памяти кодов времени, выход формирователя импульса синхро низации соединен с синхровходом второго и третьего триггеров, инверсными входами пятого и шестого элементов И, вторым входом третьего элемента И, счетным входом второго счетчика и первым информационным входом второго коммутатора, второй информационный вход которого соединен с вторым синхровходом устройства, выход первого коммутатора соединен с первым входом седьмого элемента И, выход которого соединен с входами разрешения узла памяти и узла памяти кодов времени,вто рой вход седьмого элемента И соединен с выходом таймера, с входом сброса третьего счетчика и первыми входами сброса первого и второго счетчиков, выход первого триггера соединен с прямыми входами пятого элемента И и вторым входом первого элемента И, вторые,входы сброса первого и второго счетчиков соединены с выходами пятого и шестого элементов И соответ-- ственно, выход второго триггера соединен с прямым входом шестого элемента И.

| Устройство для контроля логических схем | 1978 |

|

SU744580A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации состояний контролируемого блока | 1984 |

|

SU1236488A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-05-22—Подача