(Л

ид

Изобретение относится к вычислительной технике и может быть использовано для реализации систем логических функций, описьшающих работу мно- гофункциональных цифровых преобразователей

Целью изобретения является упрощение устройства.

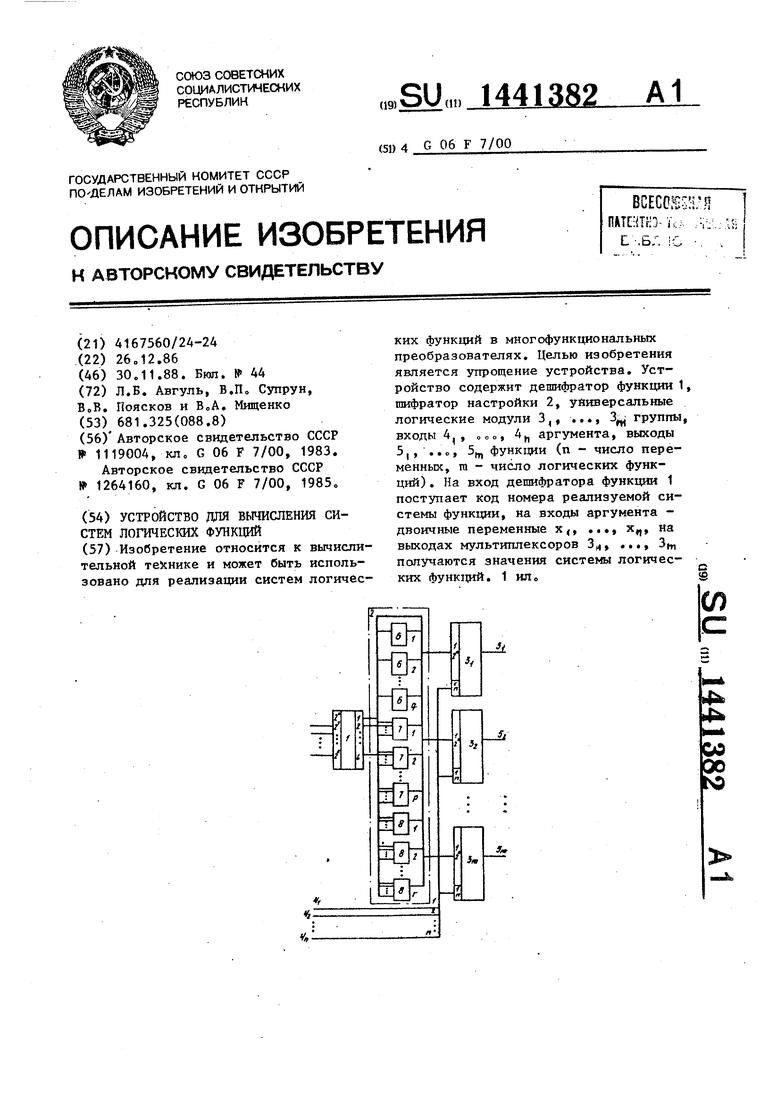

На чертеже представлена функцио- напьная схема устройства.

Устройство содержит дешифра:тор 1 функции, шифратор 2 настройки, универсальные логические модули (УЛМ) 3|, 000, Зо, группы, входы 4, ... А аргумента, выходы 5,, ,.., 5 функции. .

Шифратор настройки содержит q элементов НЕ 64, ..о, 6(,Р элементов ИЛИ 7, , .00,- 7р , г элементов ШТИ-НЕ

80 |,О..О,

Устройство функционирует следующим образом.

На вход дешифратора 1 функции поступает К-разрядный двоичный код но- мера j (j 1, L) реализуемой системы логических функций, на входы 4, 000, 4|, аргумента - двоичные переменные X,, ..„, х„, на входах 5,, ..., 5 реализуются логические функции

t|jV.X,, 0.0, , ... П)

х„), где L - число систем логических

функций; m - число логических функций в системе; п - число переменных функций.

В устройстве используются УЛМ с настройкой класса А (сигналы настройки принадлежат множеству (0,1),

имеющие п информационных и 2 настроечных входов.

При подаче на информационные входы такого модуля переменных х , х „ на его выходе реализуется некоторая логическая функция п переменных, оп- ределяемая вектором настройки U (0.0 г, ..., и,), ,, i 1,2,который подается на настроечные входы модуля. В данном случае в качестве УЛМ использованы мульти- плексоры, для которых вектор настройки tj совпадает с таблицей истинности реализуемой функции. I

УЛМ 3,, .0., 3 образуют так назы ваемую многофункциональную вычислительную среду (МФВС) с обшим числом настроечных входов Кц тп2- . МФВС управляется вектором настройки, компонентами которого являются частные вектора настроек входящих УЛМ, т.е.

(и,, и

г

Urn).

5

0

5

5 0

где и, (U;,, и;а, .-., ) - вектор Настройки i-ro (i 1, m) УЛМ 3.

Каждой j-й (i 1, L) воспроизво- димой системе логических функций f , j (х;, х), j 1, m будет соответствовать определенный вектор Следовательно, для любого S-ro (S 1, Кц) настроечного входа МФВС существует кортеж управления Vg (Vgi, Vgi, ...f VgL), компоненты которого совпадают со значением сигналов настройки на данном входе при последовательной реализации устройством всех L систем логических функщ й.

S

0

Так как

1, Кц9 j

1, L, то число различных кортежей управления не превышает величины К 2 о Кортежи V, S 1, К, формируются с помощью дешифратора 1 функции и элементов НЕ 6,, о.., 6., ИЛИ 7, .0., 7р, ШШ-НЕ 8,, ..., 8. следуншшм образом.

На входы депюфратора 1 функции поступает К-разрядный двоичный код номера j(j 1, L) реализуемой системы логических функций. Поэтому сигнал логической 1 будет только на его J-M выходе (на остальных выходах присутствует сигнал логичес- кого О)о В этой связи кортеж Vg, S 1, Кц может быть сформирован на выходе элемента ИЛИ, входа которого соединяются с выходами дешифратора из условия V,

S1

i; j 1, L.

Если кортеж Vg содержит только .один компоиент, равный логической 1, то кортеж формируется на J-M вькоде дешифратора 1 функции, который непосредственно соединяется с соответствующими настроечнь и входами МФВС.

Кроме того, кортеж V может быть сформирован и на выходе элемента ШШ-НЕ, входы которого соединяются с j-ми выходами Де1вифратора 1. функЩШо

Если Vg содержит только один компонент, равный логическому О, то кортеж формируется на вьосоде элемента НЕ, вход которого соединяется с J-M выходом дешифратора 1, Выход элемента НЕ также соединяемся с соответствующими настроечными входами МФВС.

С целью уменьшения аппаратурньк затрат кортежи управления Vg(S 1,

L г

содержащие не более ly { единичт и);

не более ных компонент 1; j

5J

1, L, целесообразно формировать с помощью элементов ИЛИ и, наоборот, если в кортежах Vg нулевьк компонент-Меньше единичных компонент, кортежи целесооб разно формировать с помощью элементов ИЛИ-НЕ„

Кроме того, возможны также два кортежа управления, все компоненты которых равны логичесмой либо все компоненты равны логическому О, Эти кортежи формируются с помощью соответственно генераторов логической 1 и логического О (не показаны).

Таким образом, из общего числа возможных 2L кортежей управления два кортежа представляют собой константы О и 1, L кортежей формируются непосредственно на выходах деиифрато- ра 1 функ1щи, L кортежей формируются с помощью элементов НЕ, а оставшиеся 2L - 2 кортежей формируются элементами ИЛИ/ИПИ-НЕ, число входов к6

торых не превышает величины

IL

Конкретньй состав шифратора 2 настроек (элементов НЕ, ШШ, ИЛИ-НЕ) зависит от вида реализуемых систем логических функцийо

Формула изобретения

Устройство для вычисления систем логических функций, содержащее дешиф-. ратор функции, вход которого соединен с входом функции устройства, о т- личающееся тем, что, с целью упрощения, устройство содержит пшфратор настройки и группу универсальных логических модулей, причем выходы дешифратора функции соедине- ны с входами шифратора настройки, вы- 1ХОДЫ которого соединены с информационными входами соответствующих универсальных логических моделей группы, управляющие входы которых соединены с входами аргумента устройства, выходы универсальных логических модулей группы соединены с выходами функции устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1559335A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Устройство для вычисления систем логических функций | 1987 |

|

SU1509863A1 |

| Универсальный логический модуль | 1986 |

|

SU1319018A1 |

| Универсальный логический модуль | 1987 |

|

SU1411730A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| Универсальный логический модуль | 1983 |

|

SU1137457A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1441381A1 |

| Универсальный логический модуль | 1988 |

|

SU1520505A1 |

| Устройство для вычисления фундаментальных симметрических булевых функций | 1989 |

|

SU1619246A1 |

Изобретение относится к вычислительной технике и может быть использовано для реализахщи систем логических функций в многофункциональных преобразователях. Целью изобретения является упрощение устройства. Устройство содержит дешифратор функции 1, шифратор настройки 2, уйиверсальные логические модули 3,, ..., 3 группы, входы 4., „00, 4 аргумента, выходы 5,, ..с, 5 функции (п - число переменных, га - число логических функций) . На вход дешифратора функции 1 поступает код номера реализуемой системы функции, на входы аргумента - двоичные переменные х, .., х„, на выходах мультиплексоров 3,4, .. , получаются значения системы логических функций. 1 ило с

| Устройство для вычисления логических выражений @ переменных | 1983 |

|

SU1119004A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-30—Публикация

1986-12-26—Подача