«/ % -

«/И

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем логических функций | 1986 |

|

SU1441382A1 |

| Функциональный преобразователь | 1978 |

|

SU781822A1 |

| Универсальный логический модуль | 1983 |

|

SU1137457A1 |

| Устройство для вычисления систем логических функций | 1987 |

|

SU1432499A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1559335A1 |

| Универсальный логический модуль | 1986 |

|

SU1345187A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для вычисления симметричных булевых функций | 1980 |

|

SU959064A1 |

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации систем логических функций, описывающих работу комбинационных узлов ЭВМ и спецпроцессоров. Цель изобретения - упрощение устройства для вычисления систем логических функций. Устройство содержит дешифратор функций 1, дешифратор 2, шифратор настройки 3, группу элементов ИЛИ 4 и коммутатор 5. На входы функции устройства поступает код номера реализуемой функции, на входы аргумента устройства - двоичные переменные. На выходе устройства реализуется сигнал, совпадающий со значением функции на данном наборе переменных. 2 ил., 2 табл.

7,

VT

5

I

СП

о

со 00

ф со

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации систем логических функций, описывающих рабо- ту комбинационных узлов ЭВМ и спецпроцессоров.

Цель изобретения - упрощение устройства для вычисления систем логических функций.

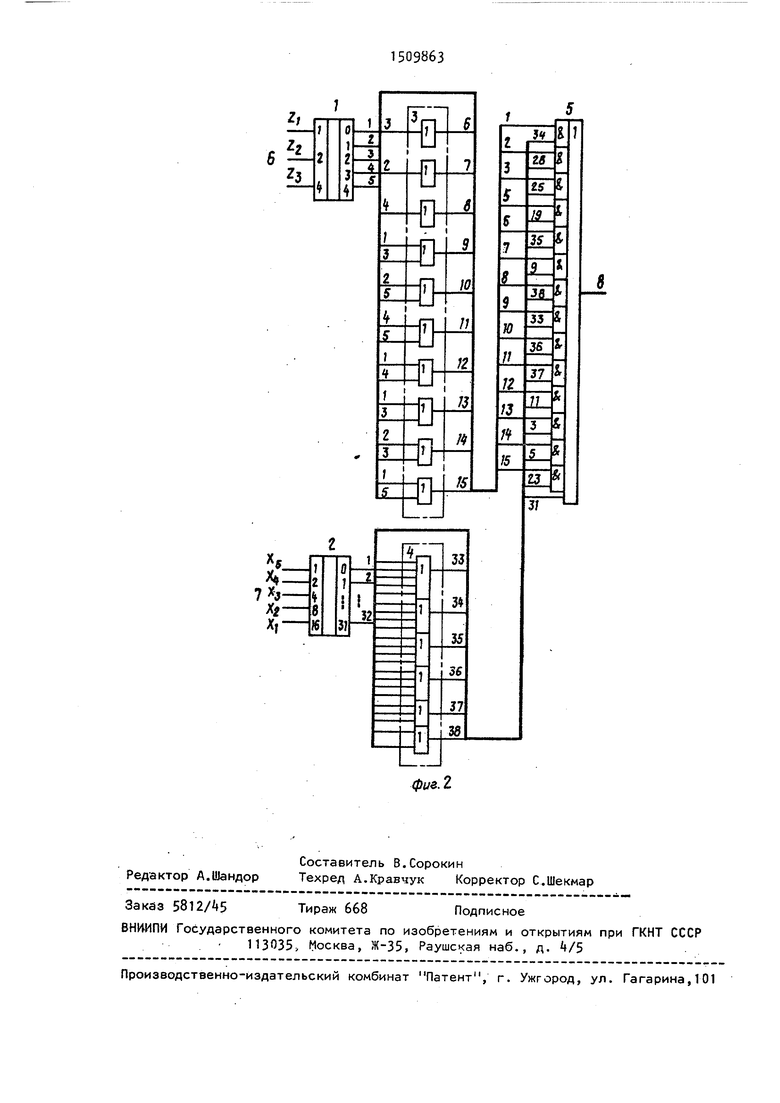

На фиг.1 представлена схема устройства, общий вид; на фиг.2 - функциональная схема устройства для рассматриваемого примера.

Устройство для вычисления систем логических функций содержит дешифратор 1 функций, дешифратор 2, шифратор 3 настройки, группу элементов ИЛИ 4, коммутатор 5, входы 6 функции устройства, входы 7 аргумента устройства, выход 8 устройства. Дешифратор 1 функций имеет m входов и 1 выходов (1 - количество логических функций в реализуемой системе). Дешифратор 2 имеет п входов и 2 вы- ходов (п - количество переменных, от которых зависят функции f;(х , х . ... х) реализуемой системы, где i -1, 2, ... 1).

Шифратор 3 настройки содержит Р 1 элементов НЕ, г элементов ИЛИ, S элементов ИЛИ-НЕ, причем О- г + S

. 2 Г - 21 - 2. Количество входов элементов ИЛИ и ИЛИ-НЕ не превышает

величины

Н(|),

где (а) наибольшее

целое, не пр.евышаюи(ее а. Группа элементов ИЛИ k содержит t элементов ИЛИ, где 0 t 4 2 -Ч

Коммутатор 5 содер «ит Р + г + s i К : inin(2,2) элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с выходом 8 устройства.

Устройство работает следующим образом.

На входы 6,, ..., 6 функции устройства поступает т-разрядный двоичный код Z.

номера

1

ТП

) системы.

реализуемой логическоРь

функции f(x.,, х, ..., на входы 7 1, ..., 7п аргумента устройства - двоичные переменные х,

X соответственно, ((з+1)му выходу дешифратора 2 соответствует j-й набор переменных х

1

Ч

где

3 О, 1, ..., 2-1). На выходе 8 устройства сигнал совпадает со значением функции f-(x,, Xj, .,

.)

на X 2

п Si

наборе с номером j

переменных х, х, ..., х.

Рассмотрим принцип работы устройства.

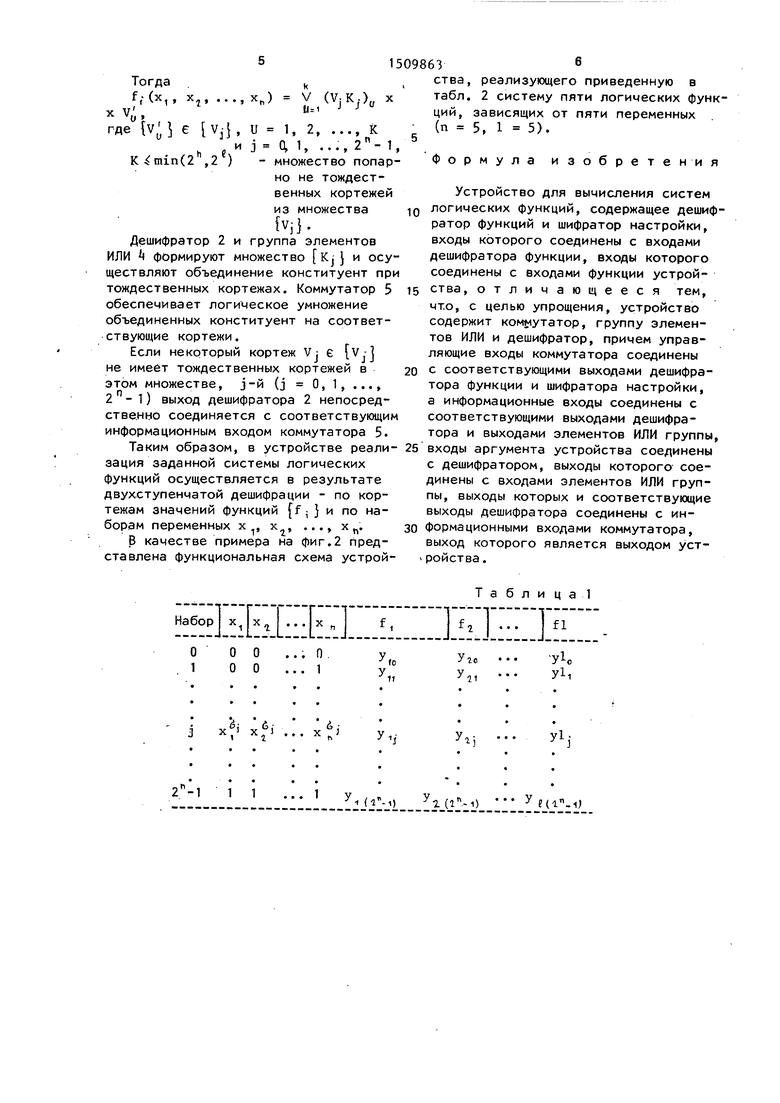

В табл. 1 представлен общий вид реализуемой устройством системы логических функций f.j(x, х, ..., x) i 1, 21. Очевидно, при заданном номере i логической функции

,

j

xj, 1 1,2,

набора j О,

п

переменных х,,

1 о I , f

сформировать сигнал

d.; ..6i

Aj J ,

J

f,ut

устройство на своем выходе должно

у .. f ..

«О.

Обозначим через V Yg.) кортеж значений

j (y,j,, ... воспроизводимых логический функций на j-м наборе переменных X , X ,

Количество

попарно различных кортежей v; ограничено величиной (2,2 ). Для

формирования кортежей Vj используют дешифратор 1 функций и шифратор 3 настройки.

. При подаче двоичного кода Z, ..., Zj, номера функции f.(x,,x2, ...,х„) на выходах дешифратора 1 функций и выходах шифратора 3 .настройки будет сформировано некоторое упорядоченное множество значений этой функции

11 У i} i (-)

среди элементов которого необходимо выбрать значение, соответствующее данному набору двоичных переменных

X

1

X

1

Пусть О, 1,

К . - X

« .

6f

X J

- 1) - конституента

единицы, соответствующая j-му набору.

45

Очевидно, при заданном кoдeZ,...,

0

номера

(-

воспроизводимую на выходе 8 устройства функцию f (х1, х, .. ставить в виде

J

можно предf(i,

X

2

,Х) У К-У;

i-0

м

V KV . « J J

i

55

С целью упрощения целесообразно произвести объединение конституент для тождественных кортежей

(к. V к)

V| при V;

JV

(2 ,2 ) множество попарно не тождественных кортежей из множества

fvji.

Дешифратор 2 и группа элементов ИЛИ i формируют множество KJ и осуществляют объединение конституент при тождественных кортежах. Коммутатор 5 обеспечивает логическое умножение объединенных конституент на соответствующие кортежи.

Если некоторый кортеж V; е iV-j не имеет тождественных кортежей в этом множестве, j-й (j О, 1, ... 2 - 1) выход дешифратора 2 непосредственно соединяется с соответствующим информационным входом коммутатора 5.

Таким образом, в устройстве реали- зация заданной системы логических функций осуществляется в результате двухступенчатой дешифрации - по кортежам значений функций f } и по наборам переменных х , х , ... х .

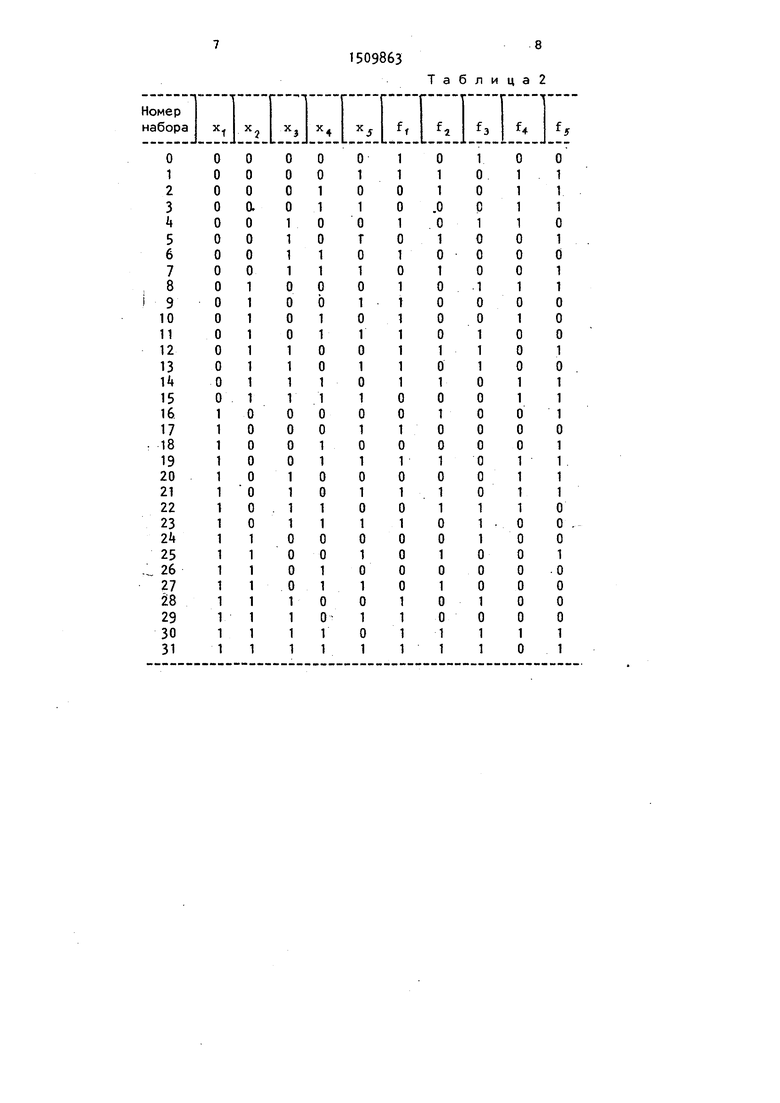

В качестве примера на фиг.2 представлена функциональная схема устрой

6

реализующего приведенную в

2 систему пяти логических функзависящих от пяти переменных

5, 1 5).

Формула изобретения

Устройство для вычисления систем логических функций, содержащее дешифратор функций и шифратор настройки, входы которого соединены с входами дешифратора функции, входы которого соединены с входами функции устройства, отличающееся тем, что, с целью упрощения, устройство содержит коммутатор, группу элементов ИЛИ и дешифратор, причем управляющие входы коммутатора соединены с соответствующими выходами дешифратора функции и шифратора настройки, а информационные входы соединены с соответствующими выходами дешифратора и выходами элементов ИЛИ группы, входы аргумента устройства соединены с дешифратором, выходы которого соединены с входами элементов ИЛИ группы, выходы которых и соответствующие выходы дешифратора соединены с ин- Формационными входами коммутатора, выход которого является выходом уст- ройства.

О 1 2

3 k

5 6 7 8

9 10 11 12 13

1

15

16

17

18

19 20 21 22 23 2k 25

. 26 27 28

29 30 31

О О О О О О О О О О О О О О О О

О О О

а

о

о

о

о

1

1

1

1

1

1

1

1

о

о

о

о

о

о

о

о

о о о о 1 1 1 1 о о о о 1 1 1 1 о о о о 1 1 1 1 о о о о 1 1 1 1

о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о 1 1

Таблица2

1 1 о о 1 о 1 о 1 1 1 1 1 1 1 о о 1 о 1 о 1 о 1 о о о о 1 1 1 1

о 1 1

.0

о 1 о 1 о о о о 1

о 1 о 1 о о 1 о 1 1 о о 1 о 1 о о 1 1

1 о о о 1

о о о .1 о о 1 1 1 о о о о о о о о 1 1 1 о о о 1 о 1 1

о 1 1 1 1 о о о 1 о 1 о о о 1 1 о о о 1 1 1 1 о о о о о о о 1 о

о 1 1 1 о 1 о 1 1 о о о 1 о

1 1 о о о 1 о о о о 1 1

Н I

| Устройство для вычисления логических выражений @ переменных | 1982 |

|

SU1084782A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для вычисления систем логических функций | 1986 |

|

SU1441382A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-09-23—Публикация

1987-07-20—Подача