1

Изобретение относится к вычислительной технике и предназначено для реализации систем логических функций, описывающих работу комбинационных узлов различных цифровых устройств.

Известно устройство для вычисления логических выражений, содержащее универсальный логический модуль, блок памяти и коммутатор 2 каналов, которые подключены к 2 выходам блока памяти, вход записи кторого подключен к вьсходу универсального логического модуля. Это устройство позволяет реализовать любые логические функции п переменных за 2 тактов работы .

Недостаток устройства - низкое быстродействие.

Известно также устройство, содержащее первый дешифратор на п-к входов, второй дешифратор на V входов и кoм fyтaтop 2 каналов, информационные входы которого подключены к выходам дешифраторов, а управляющие входы - к управляющим входам устройства. Данное устройство реализует любые логические функции t переменных. Для реализации систем из гп логических выражений требуется п таких устройств f2j .

Однако данное устройство сложно

Наиболее близким по технической сущности к изобретению является устройство, содержащее адресный формирователь, входные дешифраторы, блок памятиj выходные дешифраторы и усилители считьгаания. Устройство позволяет реализовать систему Логических функций 3 .

Недостаток устройства - аппаратная избыточность.

Цель изобретения - сокращение аппаратурных затрат.

Дпя достижения поставленной цели в устройство для вычисления логических выражений п переменных, со.держащее m блоков памяти (т - количество реализуемых устройством выражений), первый и второй дещифраторы, входы которых соединены соответственно с первой и второй группами входов устройства, введены |Л групп элементов ИЛИ и fn коммутаторов, причем адресные входы i-ro блока памяти ( i 1, ..., m ) соединены с выходами соответствующих элементов ИЛИ i-й группы, входы

9004S

которых соединены с выходами первого дешифратора, значения которых соответствуют одинаковым значениям данного выражения от (h-t) переменных ( 1 - количество входов первой группы устройства), выходы 1-го блока памяти соединены с информационными входами i - го коммутатора, управляющие входы комму10 таторов соединены с выходами второго депшфратора, выходы коммутаторов являются выходами устройства.

Такое построение устройства позволяет реализовать в нем любую систему m логических функций п переменных, при этом обеспечивается уменьшение сложности схемы устройства по сравнению с Q известными аналогичными устройствами .

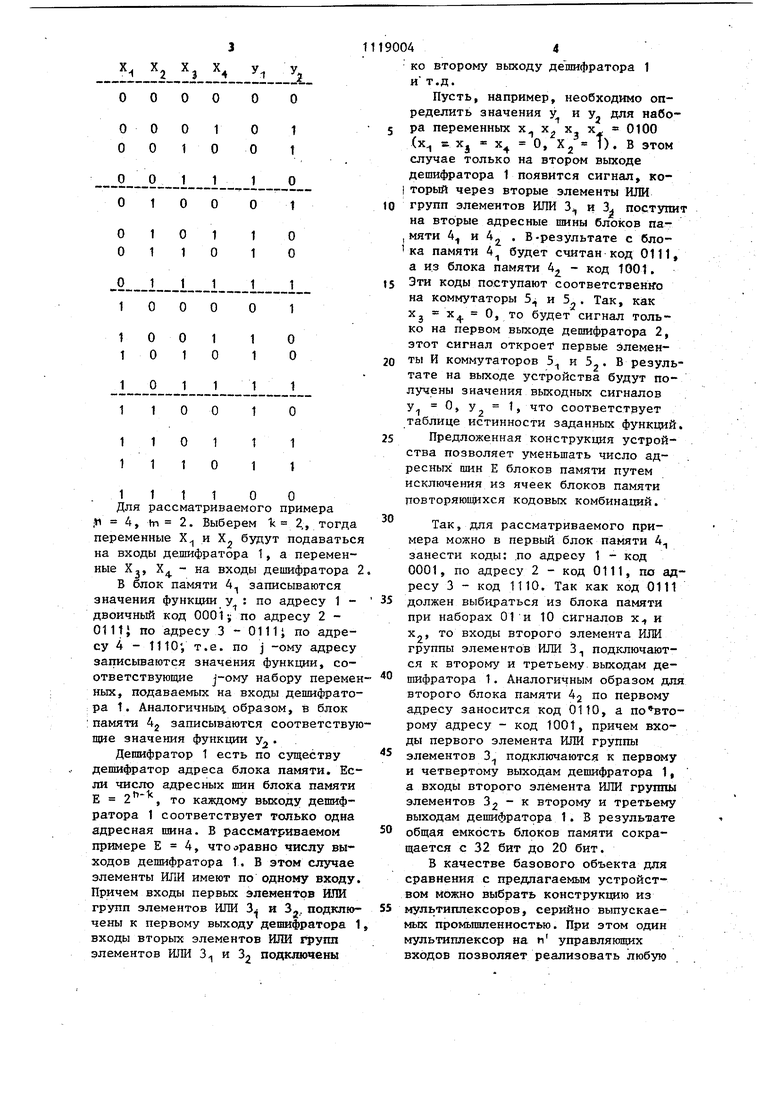

На чертеже изображена структурная схема устройства для вычисления логических выражений ,п перемен5 ных.

Структурная схема устройства содержит первый дешифратор 1, второй дешифратор 2,m групп элементов ИЛИ 3,m блоков памяти 4 - т коммутаторов 5.

В схеме устройства входы дешифратора 1 подключены к информационным входам логических переменных Х 5 Х. устройства, а входы дешифратора 2 - к информационным входам логических переменных Х устройства. 2 выходов дешифратора 1 подключены ко входам элементов

ИЛИ групп элементов ИЛИ 3 - 3, выходы которых подключены к соответствующим адресных шинам блоков памяти 4 - 4, соответственно. 2 информационных выходов каждого бло ка памяти 4 tr, подключены к информационным входам коммутаторов 5 - 5 соответственно. Одноименные управляющие входы коммутаторов 5,, - 5 объединены и подключены к

0 соответствующим 2 выходам дешифратора 2. Выходы коммутаторов 5-, - 5

fji

являются выходами сигналов у - у устройства.

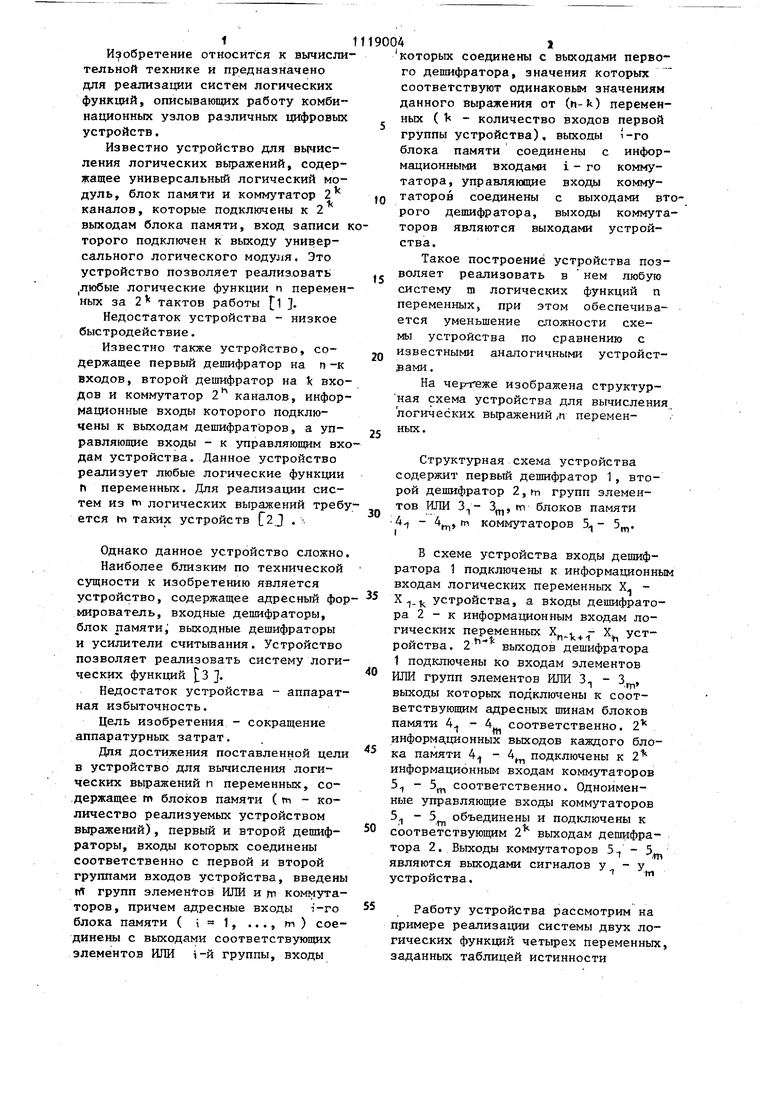

5 Работу устройства рассмотрим на примере реализации системы двух логических функций четырех переменных, заданных таблицей истинности

..

3..

0000 о Для рассматриваемого примера ,1 4, 1п 2. Выберем 1 2,, тогда переменные Х и X, будут подаватьс на входы дешифратора 1, а переменные X,, Х - на входы дешифратора В блок памяти 4 записываются значения функции у : по адресу 1 двоичный код 0001 по адресу 2 Ollli по адресу 3 - Ollli по адресу 4 - 1110, т.е. по j -ому адресу записываются значения функции, соответствующие j-ому набору переме ных, подаваемых на входы дешифрато ра 1. Аналогичный образом, в блок : памяти 4 записываются соответству щие значения функции у Дешифратор 1 есть по существу дешифратор адреса блока памяти. Ес ли число адресных шин блока памяти оМ-1с то каждому выходу дешиф ратора 1 соответствует только одна адресная шина. В рассматриваемом примере Е 4, чтооравно числу выходов дешифратора 1. В этом случае элементы ИЛИ имеют по одному входу Причем входы первых элементов ИЛИ групп элементов ИЛИ 3 И Sjj, подклю чены к первому выходу дешифратора входы вторых элементов ШШ групп элементов ИЛИ 3-, и 32 подключены

1190044

ко второму выходу дешифратора 1 ит.д.

Пусть, например, необходимо определить значения у и у для набо5 Р переменных х х х х 0100 (х Xj х О, Xj Т). В этом случае только на втором выходе дешифратора 1 появится сигнал, ко торый через вторые элементы ШЖ 10 групп элементов ИЛИ 3 и 3 поступит

на вторые адресные шины блоков па,мяти 4 и 4 . В-результате с бло1 ка памяти 4 будет считан код 0111,

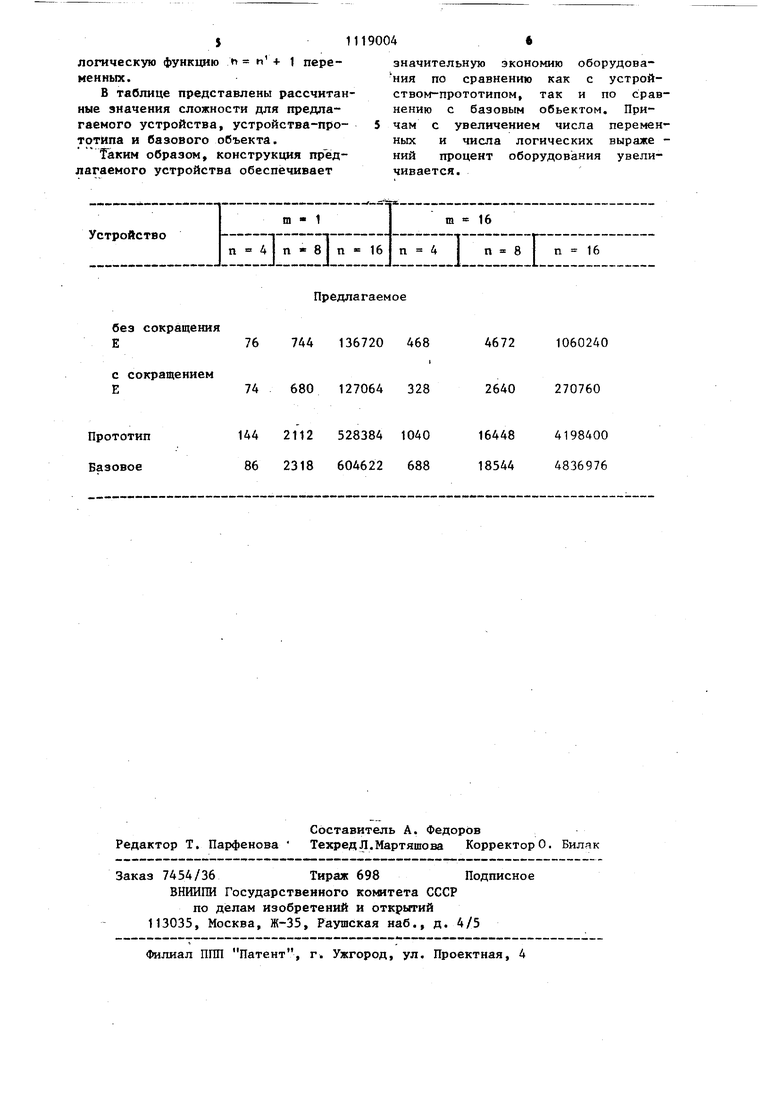

а из блока памяти код 1001. J5 Эти коды поступают соответственно на коммутаторы 5 и 5-. Так, как Xj х О, то будет сигнал только на первом выходе дешифратора 2, этот сигнал откроет первые элемен20 ты И коммутаторов 5 и 5, В результате на выходе устройства будут получены значения выходных сигналов у 1, что соответствует таблице истинности заданных функций. Предложенная конструкция устройства позволяет уменьшать число адресных шин Е блоков памяти путем исключения из ячеек блоков памяти повторяющихся кодовых комбинаций. Так, для рассматриваемого примера можно в первый блок памяти 4 занести коды: .по адресу 1 - код 0001, по адресу 2 - код 0111, по адресу 3 - код 1110. Так как код 0111 должен выбираться из блока памяти при наборах 01 и 10 сигналов х и Xj, то входы второго элемента ШШ группы элементов ИЛИ 3 подключаются к второму и третьему выходам дешифратора 1. Аналогичным образом для второго блока памяти о первому адресу заносится код 0110, а повторому адресу - код 1001, причем входы первого элемента ШШ группы элементов 3 подключаются к первому и четвертому выходам дешифратора 1, а входы второго элемента ИЛИ группы элементов 3 к второму и третьему выходам дешифратора 1. В результате общая емкость блоков памяти сокращается с 32 бит до 20 бит. В качестве базового объекта для сравнения с предлагаемым устройством можно выбрать конструкцию из мультиплексоров, серийно выпускаемых промьшшенкостью. При этом один мультиплексор на м управляюпщх входов позволяет реализовать любую 5111900 логическую функцию и + i переменных. В таблице представлены рассчитанные значения сложности для предлагаемого устройства, устройства-прототипа и базового объекта. Таким образом, конструкция предлагаемого устройства обеспечивает 5 4 значительную эконоьсию оборудования по сравнению как с устройством-прототипом, так и по Сравнению с базовым объектом. Причам с увеличением числа переменных и числа логических выраже НИИ процент оборудования увеличивается.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для вычисления систем логических функций | 1987 |

|

SU1432499A1 |

| Устройство для вычисления систем логических функций | 1985 |

|

SU1264160A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для отображения полутонового изображения на экране телевизионного приемника | 1988 |

|

SU1522273A1 |

УСТРОЙСТВО.ДЛЯ ВЫЧИСЛЕНИЯ ;ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ л ПЕРЕМЕННЫХ, содержащее m блоков памяти ( tn - количество реализуемых устройством выражений), первый и второй дешифраторы, входы которых соединены соответственно с первой и второй группами входов устройства, о т л ичающееся тем, что, с целью сокращения аппаратурных затрат, в него введены m групп элементов ИЛИ и m коммутаторов, причем адресные входы i-ro блока памяти ( t 1, .. ..., m) соединены с выходами соответствующих элементов ИЛИ i-й группы, входы которых соединены с выходами первого дешифратора, значения которых соответствуют одинаковым значениям данного выражения от (ft-к) переменных ( 1 - количество входов первой группы устройства), § выходы . i-ro блока памяти соединены с информационными входами i-ro ком(Л мутатора, управляющие входы коммутаторов соединены с выходами второго дешифратора, выходы коммутаторов являются выходами устройства. §

Предлагаемое

76 7А4 136720 468 74 680 127064 328 144 2112 528384 1040 Прототип 86 2318 604622 688 Базовое

4672 1060240

I 2640 270760 16448 4198400 18544 4836976

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления логических выражений @ переменных | 1981 |

|

SU962918A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| и др | |||

| Микропро.цессорные комплекты повышенного быстродействия, М., Радио и связь, 1981, с | |||

| Соломорезка | 1918 |

|

SU157A1 |

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-03—Подача