Изобретение относится к устройствам преобразовательной техники и может быть использовано в системах программного управления станками и роботами, в системах обработки графической информации, в системах телеуправления и контроля.

Целью изобретения является повышение точности преобразователя за счет уменьшения динамической погрешности преобразователя.

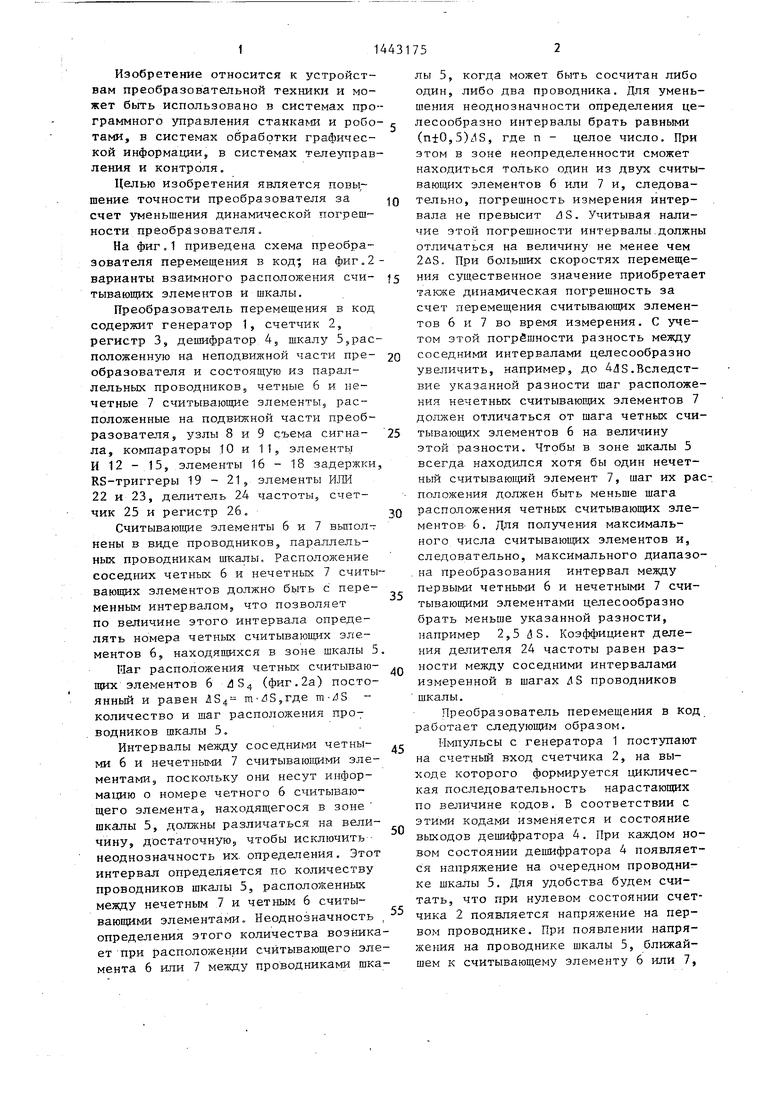

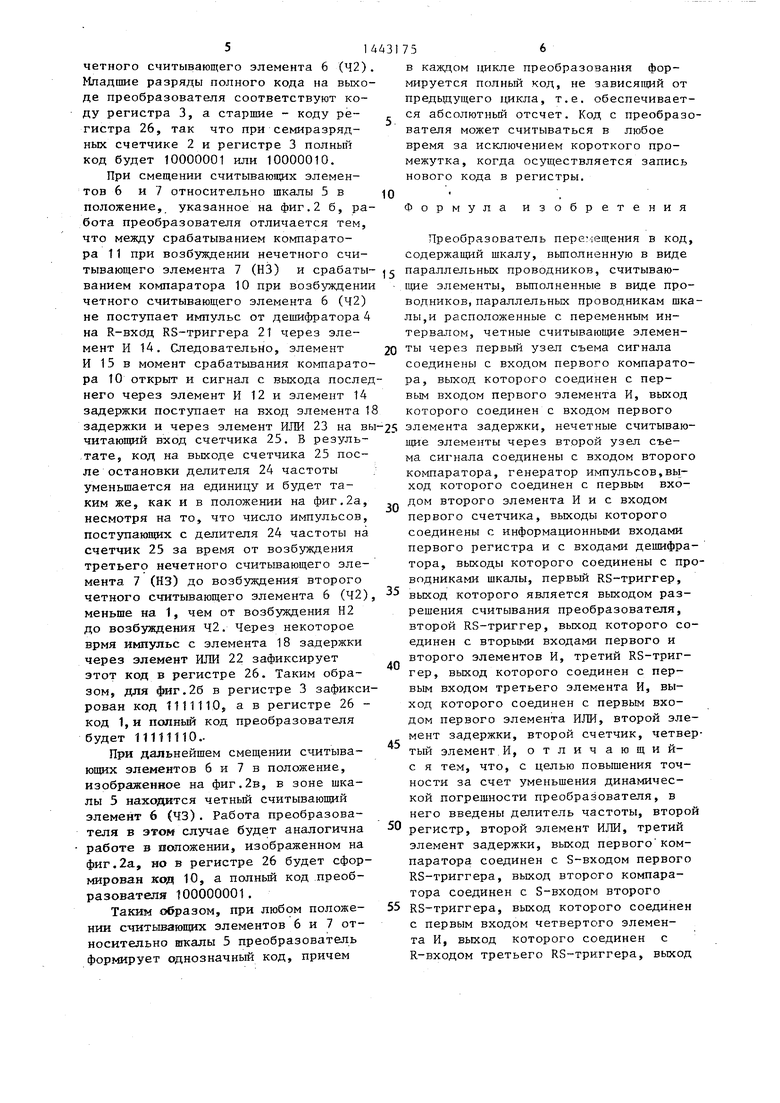

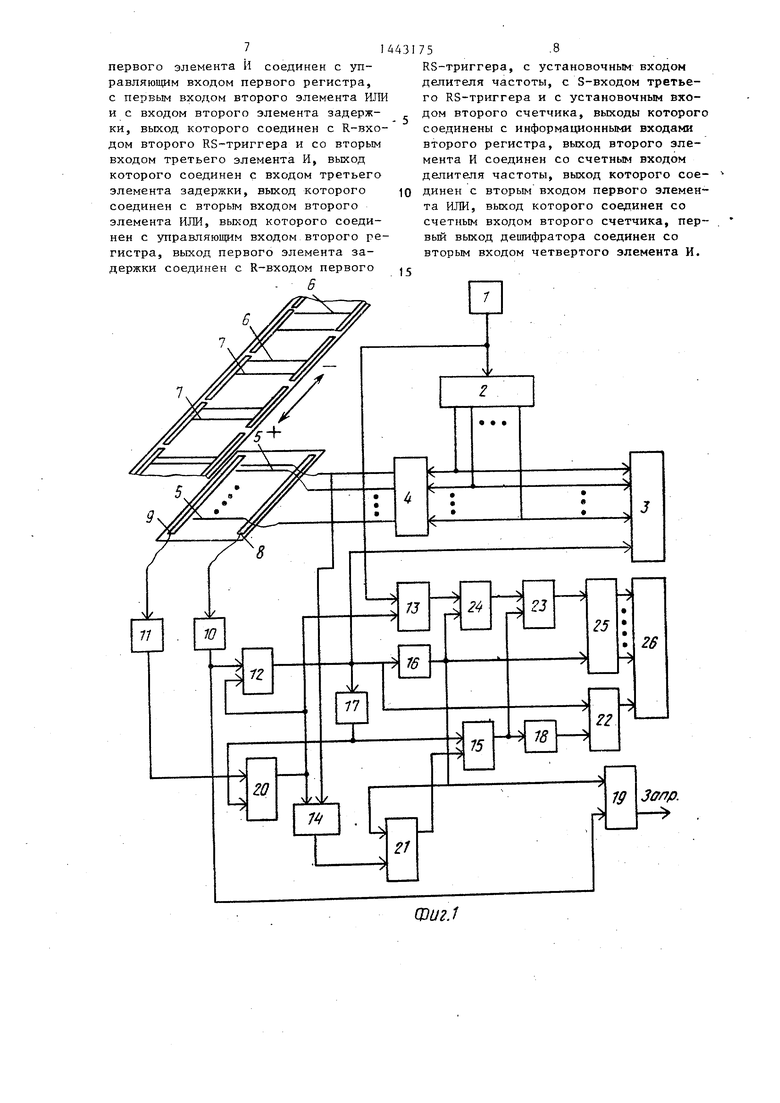

На фиг,1 приведена схема преобразователя перемещения в код; на фиг.2 варианты взаимного расположения счи- тывающих элементов и шкалы.

Преобразователь перемещения в код содержит генератор 1, счетчик 2, регистр 3, дешифратор 4, шкалу 5,расположенную на неподвижной части пре- образователя и состоящую из параллельных проводников, четные 6 и нечетные 7 считываюш 5е элементы, расположенные на подвижной части преобразователя, узлы 8 и 9 съема сигна- ла, компараторы ,10 и 11, элементы И 12 - 15, элементы 16 - 18 задержки RS-триггеры 19 - 21, элементы ИЛИ 22 и 23, делитель 24 частоты, счетчик 25 и регистр 26,

Считываюш 1е элементы 6 и 7 вьшол- нены в виде проводников, параллельных проводникам шкалы. Расположение соседних четных 6 и нечетных 7 считывающих элементов должно быть с переменным интервалом, что позволяет по величине этого интервала определять номера четньк считываюш:их элементов 6, находяш1 хс51 в зоне шкалы 5

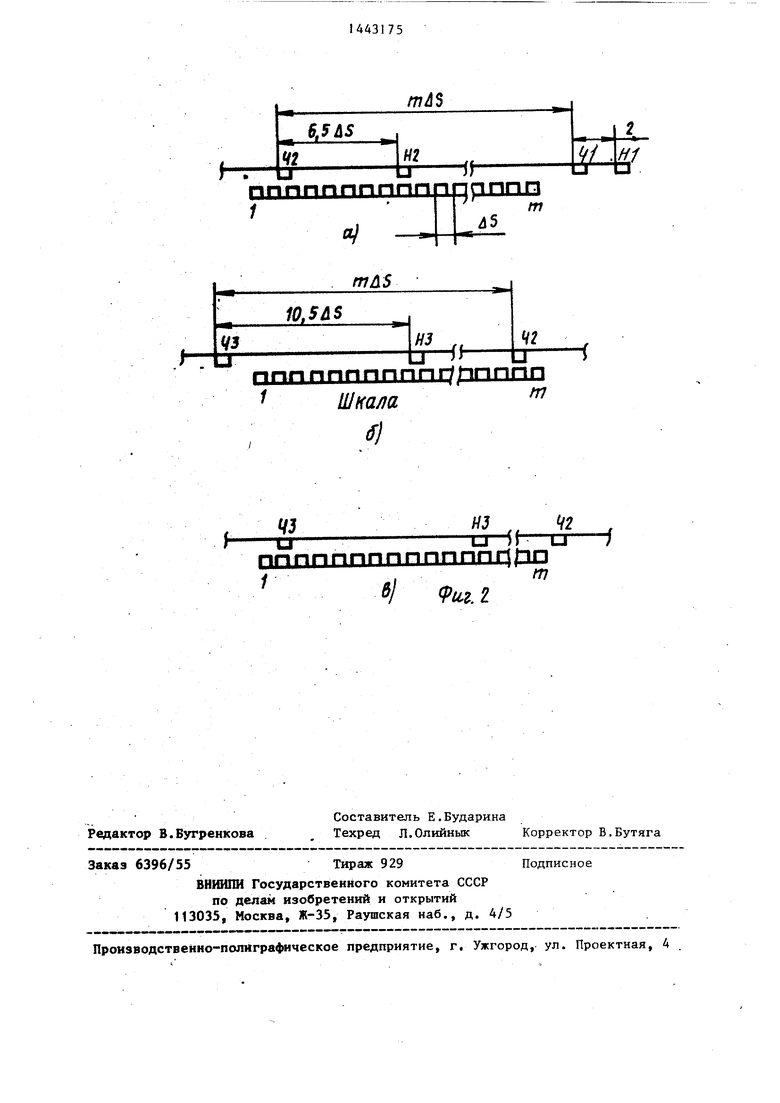

Иаг расположения четных считываю- щих элементов 6 US (фиг.2а) посто- янньй и равен m-/iS количество и шаг расположения проводников шкалы 5

Интервалы между соседними четны- ми 6 и нечетными 7 считывающими элементами, поскольку они несут информацию о номере четного 6 считываю щего элемента, находящегося в зоне шкалы 5, должны различаться на вели- чину, достаточную, чтобы исключить неоднозначность их. определения. Этот интервал определяется по количеству проводников шкалы 5, расположенных между нечетным 7 и четным 6 считывающими элементами. Неоднозначность определения этого количества возникает при расположении считывающего элемента 6 или 7 между проводниками шка

Q

5

0 5 0

Q

5

5

лы 5, когда может быть сосчитан либо один, либо два проводника. Для уменьшения неоднозначности определения целесообразно интервалы брать равными (niO,5)i1S, где п - целое число. При этом в зоне неопределенности сможет находиться только один из двух считывающих элементов 6 или 7 и, следовательно, погрешность измерения интервала не превысит ЛS. Учитывая наличие этой погрешности интервалы,должны отличаться на величину не менее чем 2л5. При больших скоростях перемещения существенное значение приобретает также динамическая погрешность за счет перемещения считываюш 1х элементов 6 и 7 во время измерения. С учетом этой погрешности разность между соседними интервалами целесообразно увеличить, например, до 4ЛS.Вследствие указанной разности шаг расположения нечетных cчитывaюшJ.x элементов 7 должен отличаться от шага четных считывающих элементов 6 на величину этой разности. Чтобы в зоне зпкалы 5 всегда находился хотя бы один нечетный считывающий элемент 7, шаг их расположения должен быть меньше шага расположения четных считывающих элементов- 6. Для получения максимального числа считывающих элементов и, следовательно, максимального диапазо- , на преобразования интервал между первыми четными 6 и нечетными 7 считывающими элементами целесообразно брать меньше указанной разности, например 2,5 &5. Коэффициент деления делителя 24 частоты равен разности между соседними интервалами измеренной в шагах AS проводников шкалы.

Преобразователь перемещения в код работает следующим образом.

Импульсы с генератора 1 поступают на счетньй вход счетчика 2, на выходе которого формируется циклическая последовательность нарастающих по величине кодов. В соответствии с этими кодами изменяется и состояние выходов дешифратора 4. При каждом новом состоянии дешифратора 4 появляется напряжение на очередном проводнике шкалы 5. Для удобства будем считать, что при нулевом состоянии счетчика 2 появляется напряжение на первом проводнике. При появлении напряжения на проводнике шкалы 5, ближайшем к считывающему элементу 6 или 7,

I

на последнем вследствие.наличия емкостной связи наводится наибольшее напряжение, которое поступает через узлы 8 или 9 съема, сигнала на вход соответствующего компаратора 10 или 11. Порог срабатывания компаратора 1 или 11 установлен таким, что при расположении считывающих элементов б и 7 между двумя проводниками шка- лы 5 он обязательно срабатывает при подаче напряжения либо на первый, либо на второй из них. В зоне шкалы 5 могут находиться одновременно два или три соседних считывающих эле мента, поэтому при работе преобразователя происходит периодическое срабатывание компараторов 10 и 11. При срабатывании компаратора 11 RS-триг- гер 20 устанавливается в состояние логической 1 и открывает элементы И 12 - 14. При срабатывании после этого компаратора 10 сигнал через элемент И 12 поступает на входы элементов 16 и 17 задержки. Сигнал с выхода элемента 14 задержки устанавливает в состояние логического О RS-триггер 20, а сигнал с выхода элемента 16 задержки устанавливает в состояние логического О RS-триг- гер 19 и счетчик 25, а в состояние логической 1 RS-триггер 21, а также устанавливает в исходное состояние делитель 24 частоты. Исходное состояние делителя 24 частоты зави

сит от интервала между первым четным 6 (41) и первым нечетным 7 (HI) считывающими элементами (фиг.2) и от разности интервалов и выбирается таким, чтобы возможные сбои (потеря или появление лишнего импульса на входе делителя 24 частоты) не приводили к изменению числа импульсов на выходе делителя 24 частоты. При разности интервалов 4 Л8 -и величине первого интервала 2, (фиг.2) коэффициент деления делителя 24 частоты равен 4, а исходное состояние такое, что первьш импульс на выходе формируется по первому импульсу на входе. Длительность задержки элемента 16 задержки выбирается такой,чтобы указанная установка элементов закончилась до срабатывания компаратора 11. Предположим, что установка бьша осуществлена после возбуждения второго четного считывающего элемента 6 (Ч2, фиг. 2а). После этого при возбуждении второго нечетного элемен

5 о

O

Q

5

754

та (Н2) срабатывает компаратор 11, устанавливает в состояние логической 1 RS-триггер 20, который открывает элементы И 12 - 14. При этом импульсы от генератора 1 (включая импульс, от которого срабатывает компаратор 11) через элемент И 13 начинают поступать на делитель 24 частоты. Сигналы с делителя 24 частоты, частота которых в 4 раза ниже частоты генератора 1, через элемент ИЛИ 23 начинают поступать на вычитающий вход счетчика 25. При прохождении счетчиком 2 н левого состояния сформируется напряжение на первом выходе дешифратора 4, поступающее на первый проводник шкалы 5 и через элемент И 14 на R-вход RS-триггера 21. При этом последний устанавливается в состояние О и закрывает элемент И 15. Затем при подаче напряжения на второй или третий проводник шкалы 5 возбуждается четный считывающий элемент 6, находящийся между этими про- водника№1 42 (фиг.2а), срабатывает компаратор 10, сигнал с которого переводит RS-триггер 19 в состояние Запрет и через элемент И 12 зафиксирует код счетчика 2 в регистре 3, а через элемент ИЛИ 22 - код счетчика 25 в регистре 26. Кроме того,этот же сигнал через элемент 17 задержки устанавливает RS-триггер 20 в состояние логического О, в результате чего закрываются элементы И 12 - 14 и поступление и fflyльcoв на вход .делителя 24 частоты прекращается.Делитель 24 частоты при этом останавливается в одном из средних состояний, причем отклонение его состояния от среднего на один такт, в случае потери или добавления одного импульса, не приводит к изменению числа импульсов на его выходе. Через некоторое время импульс с выхода элемента 16 задержки, запущенного компаратором 10, устанавливает элементы в исходное состояние. При этом снимется сигнал Запрет на выходе преобразователя, запрещающий считывание кода -с преобразователя на время записи информации в регистры 3 и 26. В результате преобразования для положения, изображенного на фиг.2а, в регистре 3 будет зафиксирован код 01 или 10 с нулями в старших разрядах, а в регистре 26 - код 1, соответствующий нахождению в зоне щкалы 5 второго

четного считывающего элемента 6 (Ч2). Младшие разряды полного кода на выходе преобразователя соответствуют коду регистра 3, а старшие - коду регистра 26, так что при семиразрядных счетчике 2 и регистре 3 полньй код будет 10000001 или 10000010.

При смещении считывающих элементов 6 и 7 относительно шкапы 5 в положение, указанное на фиг.2 б, работа преобразователя отличается тем, что между срабатыванием компаратора 11 при возбуждении нечетного считывающего элемента 7 (НЗ) и срабаты- ванием компаратора 10 при возбуждении четного считывающего элемента 6 (42) не поступает импульс от дешифратора 4 на R-вход RS-триггера 21 через элемент И 14. Следовательно, элемент И 15 в момент срабатьшания компаратора 10 открыт и сигнал с выхода последнего через элемент И 12 и элемент 14 задержки поступает на вход элемента 18 задержки и через элемент ИЛИ 23 на вы читающий вход счетчика 25. В результате, код на выходе счетчика 25 после остановки делителя 24 частоты ; уменьшается на единицу и будет таким же, как и в положении на фиг.2а, несмотря на то, что число импульсов, поступающих с делителя 24 частоты на счетчик 25 за время от возбуждения третьего нечетного считывающего элемента 7 (НЗ) до возбуждения второго четного считывающего элемента 6 (Ч2), меньше на 1, чем от возбуждения Н2 до возбуждения Ч2. Через некоторое врмя импульс с элемента 18 задержки через элемент ИЛИ 22 зафиксирует этот код в регистре 26. Таким образом, для фиг.26 в регистре 3 зафиксирован код 1111IIOj а в регистре 26 - код 1, и полный код преобразователя будет 11111110,.

При дальнейшем смещении считывающих элементов 6 и 7 в положение, изображенное на фиг.2в, в зоне шкалы 5 находится четный считывающий элемент 6 (43). Работа преобразователя в этом случае будет аналогична работе в положении, изображенном на фиг.2а, но в регистре 26 будет сформирован код 10, а полный код преобразователя 100000001.

Таким образом, при любом положе- НИИ считывающих элементов 6 и 7 относительно шкалы 3 преобразователь формирует однозначный код, причем

5

0

5

5

756

в каждом цикле преобразования формируется полный код, не завися1ций от предьщущего хщкла, т.е. обеспечивается абсолютный отсчет. Код с преобразователя может считываться в любое время за исключением короткого промежутка, когда осуществляется запись нового кода в регистры.

Формула изобретения

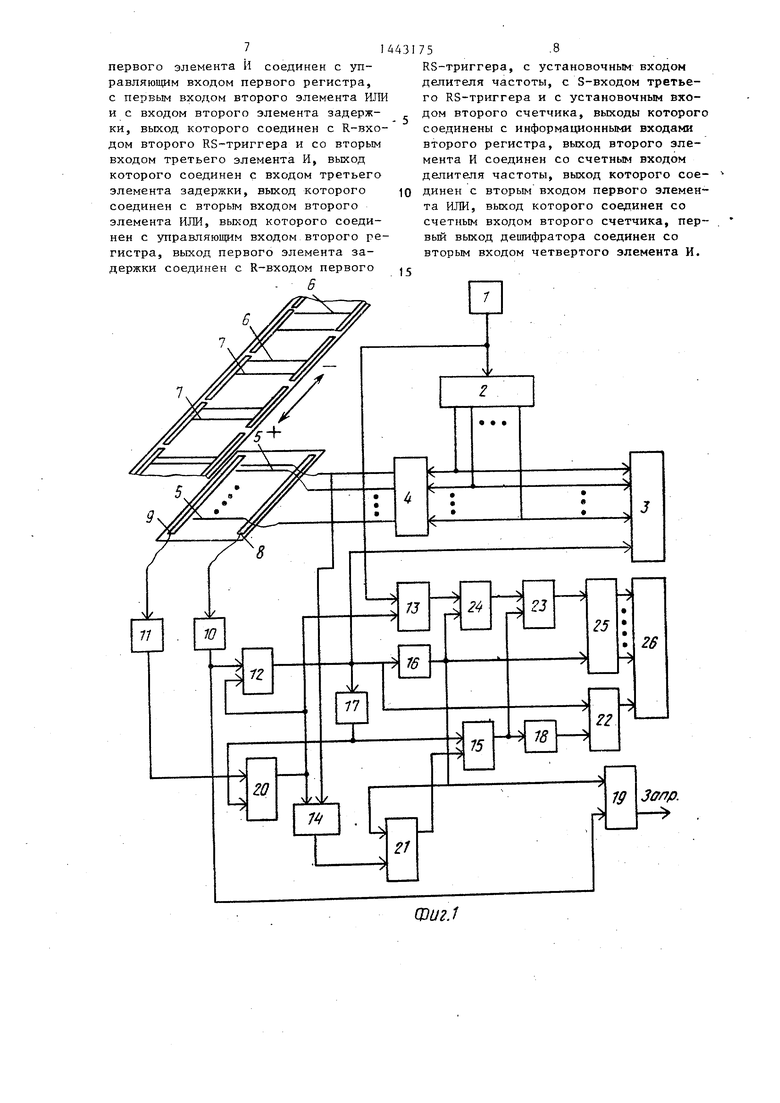

Преобразователь пере:-:ещения в код, содержащий шкалу, выполненную в виде параллельных проводников, считывающие элементы, вьтолненные в виде проводников, параллельных проводникам шкалы, и расположенные с переменным интервалом, четные считывающие элементы через первый узел съема сигнала соединены с входом первого компаратора, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом первого элемента задержки, нечетные считывающие элементы через второй узел съема сигнала соединены с входом второго компаратора, генератор импульсов,выход которого соединен с первым входом второго элемента И и с входом первого счетчика, выходы которого соединены с информационными входами первого регистра и с входами дешифратора, выходы которого соединены с проводниками шкалы, первый RS-триггер, выход которого является выходом разрешения считывания преобразователя, второй RS-триггер, выход которого соединен с вторыми входами первого и второго элементов И, третий RS-триггер, выход которого соединен с первым входом третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй элемент задержки, второй счетчик, четвертый элемент.И, отличающий- с я тем, что, с целью повышения точности за счет уменьшения динамической погрешности преобразователя, в него введены делитель частоты, второй регистр, второй элемент ИЛИ, третий элемент задержки, выход первого компаратора соединен с S-входом первого RS-триггера, выход второго компаратора соединен с З-входом второго RS-триггера, выход которого соединен с первым входом четвертого элемента И, выход которого соединен с R-входом третьего RS-триггера, выход

7I443I

первого элемента И соединен с управляющим входом первого регистра, с первым входом второго элемента ИЛИ и с входом второго элемента задерж- 5

ки, выход которого соединен с R-BXO- дом второго RS-триггера и со вторым входом третьего элемента И, выход которого соединен с входом третьего элемента задержки, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с управляющим входом второго регистра, выход первого элемента задержки соединен с R-входом первого

В

5

10

75.8

RS-триггера, с установочным входом делителя частоты, с S-входом третьего RS-триггера и с установочным входом второго счетчика, выходы которого соединены с информационными входами второго регистра, выход второго элемента И соединен со счетным входом делителя частоты, выход которого соединен с вторьм входом первого элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, первый выход дешифратора соединен со вторым входом четвертого элемента И.

Золр.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь перемещения в код | 1986 |

|

SU1383499A1 |

| Преобразователь перемещения в код | 1985 |

|

SU1269263A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1361711A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1113828A1 |

| Устройство для управления электродвигателем переменного тока | 1984 |

|

SU1457141A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090839C1 |

| Устройство задержки | 1990 |

|

SU1721812A1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090840C1 |

Изобретение относится к устройствам преобразовательной техники и может быть использовано в системах программного управления станками и роботами, обработки графической -информации, телеуправления и контроля. Целью изобретения является повышение точности за счет уменьшения динамической погрешности преобразователя. Поставленная цель достигается тем, что в преобразователь, содержащий шкалу в виде па-. раллельных проводников, укрепленную на неподвижной части преобразователя, считывающие элементы, через узлы съема сигнала соединенные с входами компараторов, три RS-триггёра, генератор, два счетчика, регистр, дешифратор, элемент ИЛИ, четыре элемента И, два элемента задержки,введены второй элемент ИЛИ, второй регистр, третий элемент задержки и делитель частоты. Считываюпще элементы расположены с переменным интервалом, что позволяет определять номер четного считывающего элемента,находящегося в зоне шкалы. Импульсы с генератора изменяют состояние дешифратора, что позволяет поочередно подавать напряжение на проводники шкалы. В регистрах одновременно фиксируется положение четных и нечетных считывающих элементов, что позволяет однозначно определять положение считывающих элементов относительно шкалы, а одновременное получение отсчетов уменьшает динамическую погрешность. 2 ил. в (Л с N 4 СО сл

Фиг.1

Г Шкала

VJ

ri

нз cг-5

nnnnnnnnnnnnnrtMn

нз cг-5

nrtMn

/ . 2

w

| Преобразователь угла поворота вала в код | 1983 |

|

SU1113828A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь перемещения в код | 1985 |

|

SU1269263A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-07—Публикация

1986-10-22—Подача