Изобретение относится к радиотехнике и может быть использовано для задержки электрических сигналов в радиолокационных станциях (РЛС).

Известно устройство задержки, содержащее последователоно соединенные первый преобразователь уровня, вход которого является первым входом устройства задержки, аналоговый сдвиговый регистр и фильтр нижних частот, выход которого является выходом устройства задержки, и после- довательно соединенные второй преобразователь уровня, вход которого является вторым входом устройства задержки, и генератор тактовых импульсов, выход

которого соединен с вторым входом аналогового сдвигового регистра.

Недостатком известного устройства является низкая точность сохранения амплитуды задержанных сигналов, обусловленная взаимным влиянием сигналов соседних элементов памяти в аналоговом сдвиговом регистре.

Наиболее близким к предлагаемому по технической сущности является устройство задержки, содержащее последовательно соединенные первый преобразователь уровня, аналоговый сдвиговый регистр и фильтр нижних частот, выход которого является выходом устройства задержки, а также второй преобразователь уровня, генератор

vj Ю

00 Ю

тактовых импульсов, первый выход которого соединен с вторым входом аналогового сдвигового регистра, и блок управления временем задержки, первый вход которого соединен с вторым выходом генератора так- товых импульсов, второй вход соединен с выходом второго преобразователя уровня, третий и четвертый входы являются третьим и четвертым входами устройства задержки, а выход блока управления соединен с вхо- дом генератора тактовых импульсов, входы первого и второго преобразователей уровня являются соответственно первым и вторым входами устройства задержки,блок управления временем задержки содержит элемент И, два триггера, дешифратор, задающий генератор, два элемента ИЛИ и два счетчика, при этом первый вход элемента И является входом второго блока управления временем задержки, второй вход соединен с выходом первого триггера, первый вход которого соединен с шиной управляющих импульсов с переменным периодом и являющегося входом третьего блока управления временем задержки, вход дешифратора соединен с шиной кода изменения периода входных импульсов и является входом четвертого блока управления временем задержки. Выход дешифратора соединен с первым вхо- дом задающего генератора, выход которого соединен с вторым входом первого элемента ИЛИ, первый вход которого соединен с выходом элемента И, а выход является выходом блока управления временем задерж- ки и соединен с входом генератора тактовых импульсов, второй выход которого соединен через первый вход блока управления временем задержки с первыми входами первого и второго счетчиков. Второй вход первого счетчика соединен с первым выходом второго триггера, а выход - с вторым входом первого триггера и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго счетчика,вы- ход - с входом второго триггера, второй выход которого соединен с вторым входом задающего генератора и вторым входом второго счетчика.

Недостатком известного устройства яв- ляется низкая точность сохранения амплитуды задержанных импульсов, обусловленная взаимным влиянием сигналов соседних элементов памяти в аналоговом сдвиговом регистре.

Известно, что разложение Z преобразования устройства задержки описывается выражением

H(z) 2 (i±rrLV

n 0П

(1-е)1

,N

-(N-n)

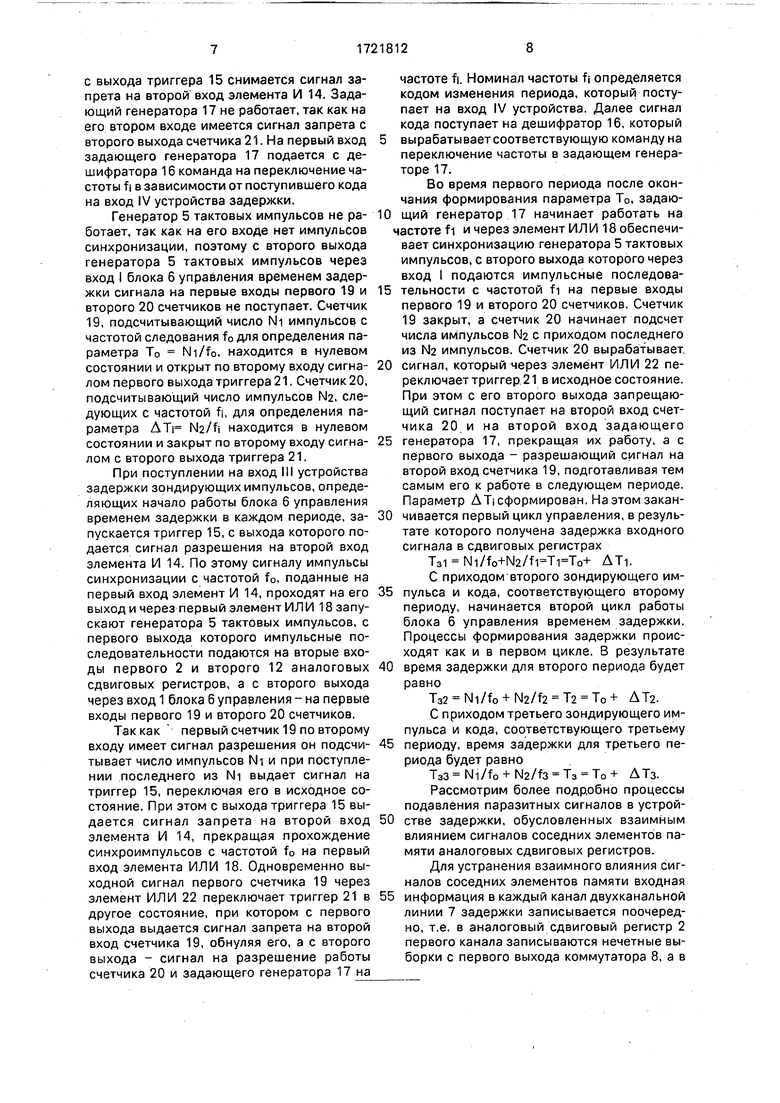

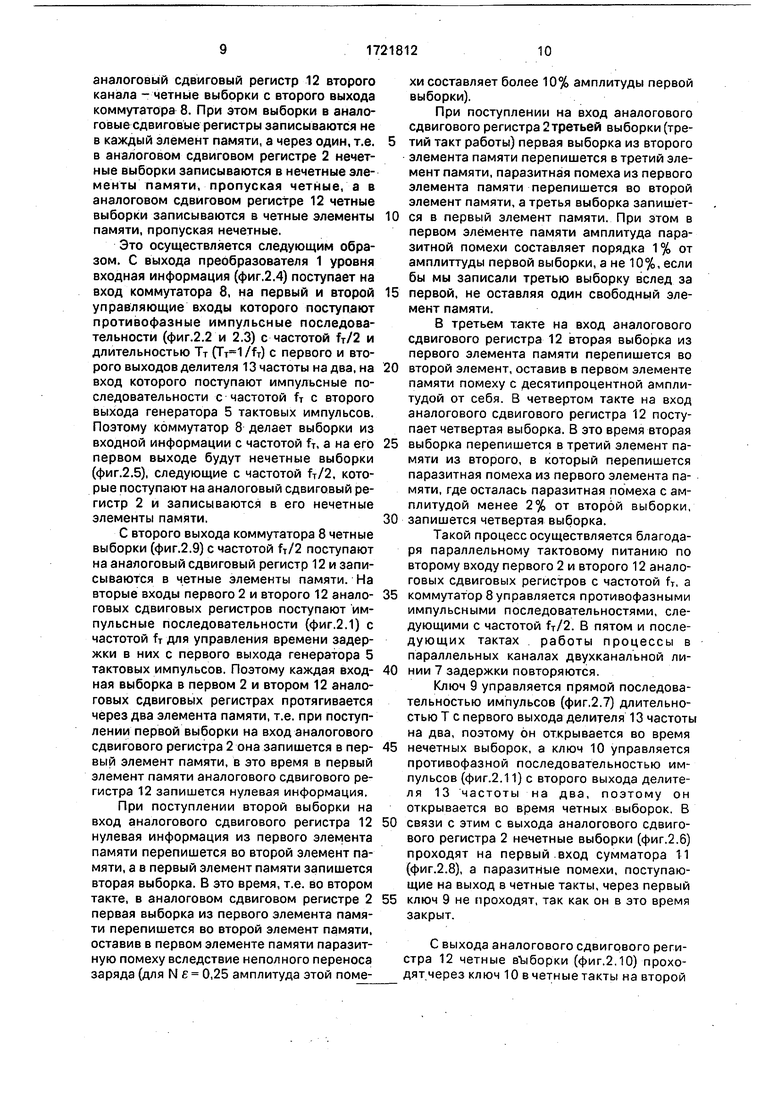

Импульсная характеристика N каскадной линии задержки на ПЗС с потерями переноса на один каскад памяти Ј для разных N-E приведена на фиг.З. Вследствие неполного переноса заряда выходной задержанный сигнал расплывается, его амплитуда в 1М-м периоде уменьшается и появляется цепочка паразитных сигналов в последующих (N+n) тактах, а также искажается частотная характеристика (фиг.4). Из фиг.З видно, например, для МЈ 0,1 амплитуда паразитного сигнала в N+1 такте составляет порядка 10% от основного, амплитуда которого уменьшилась до 90%, а для NЈ-0,25 амплитуда паразитного сигнала составляет более 20%. Эти паразитные сигналы накладываются на полезный сигнал при перемещении информации по аналоговому сдвиговому регистру и искажают его амплитуду, т.е. происходит взаимное влияние сигналов соседних элементов памяти.

Снизить взаимное влияние.можно, если оставить часть элементов памяти свободными, т.е. записывать информацию не в каждый элемент памяти, а, например, через один элемент, тогда искажение амплитуды задержанного сигнала от влияния сигналов соседних элементов памяти резко снижается. Например, для аналогового сдвигового регистра с ,1 второй сигнал записывать не в N-1 элемент памяти, где амплиту- . да паразитного сигнала составляет более 10% от основного (первого), а в N-2, где амплитуда паразитного сигнала составляет менее одного процента от основного (первого), тогда влияние сигналов соседних элементов памяти снижается более чем в 10 раз.

Но этот способ снижения влияния для аналоговых сдвиговых регистров с однока- нальной структурой применить нельзя, потому что необходимо будет увеличить число элементов памяти до 2N, что увеличит потери с NЈ до 2Ne , а тактовую частоту fr необходимо повысить при этом в два раза, что в итоге приведет к увеличению потерь более чем в 4 раза.

Цель изобретения - повышение точности сохранения амплитуды задержанных сигналов за счет уменьшения амплитуды помех от взаимного влияния сигналов соседних элементов памяти аналогового регистра сдвига.

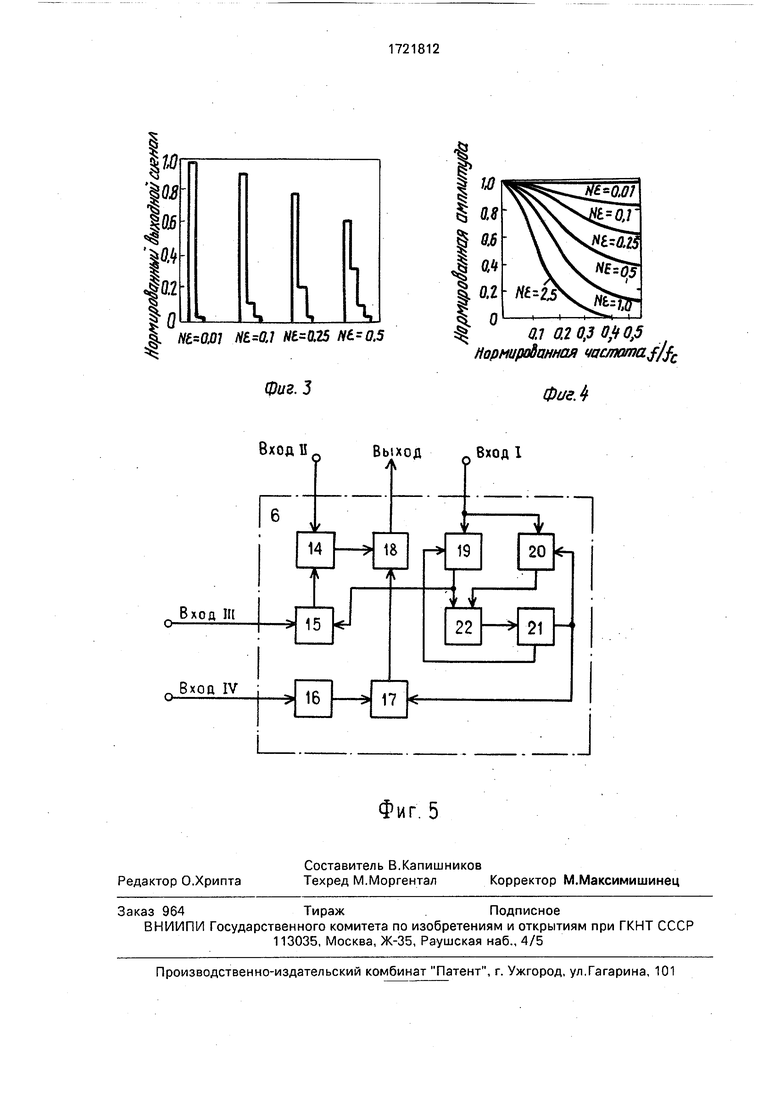

На фиг. 1 .представлена блок-схема устройства задержки; на фиг.2 - эпюры, пояс- няющие работу двухканальной линии задержки; на фиг.З - импульсная характеристика N-каскадного аналогового сдвигового

регистра на приборах с зарядовой связью, обладающей неэффективностью переноса е на фиг.4 - частотная характеристика аналогового сдвигового регистра для разных по- терь NE ; на фиг.5 - функциональная схема блока управления временем задержки.

Устройство задержки содержит преобразователь 1 уровня, первый аналоговый сдвиговый регистр 2, фильтр 3 нижних час- тот, второй преобразователь 4 уровня, генератор 5 тактовых импульсов, блок 6 управления временем задержки, двухка- нальную линию 7 задержки, коммутатор 8, первый 9 и второй 10 ключи, сумматор 11, второй аналоговый сдвиговый регистр 12, делитель 13 частоты на два. Блок 6 управления временем задержки содержит элемент И 14, первый триггер 15, дешифратор 16, задающий генератор 17, первый элемент ИЛИ 18, первый 19 и второй 20 счетчики, второй триггер 21 и второй элемент ИЛИ 22.

Устройство задержки работает следующим образом.

Входной импульсный сигнал через пер- вый преобразователь 1 уровня и коммутатор 8 поступает на двухканальную линию 7 задержки, каналы которой объединены с помощью сумматора 11. На вторые входы первого 2 и второго 12 аналоговых сдвиговых регистров подаются импульсные последовательности, следующие с частотой fT от генератора 5 тактовых импульсов, определяющие время задержкиТ3 входного сигнала в первом 2 и втором 12 аналоговых сдвиговых регистрах. Задержанные сигналы с выходом первого 2 и второго 12 аналоговых сдвиговых регистров через сумматор 11 подаются на вход фильтра 3 нижних частот, с помощью которого выделяется полез- ный сигнал и подавляются помехи от импульсов тактового питания, следующих с частотой fr и их гармоник, потому что полоса среза фильтра 3 нижних частот равна fr/2. С выхода фильтра 3 нижних частот задер- жанных полезный сигнал поступает на выход устройства задержки.

На вход генератора 5 тактовых импульсов подаются синхроимпульсы с выхода блока 6 управления временем задержки, который вырабатывает определенные импульсные последовательности, обеспечивающие формирование требуемой задержки входного сигнала в первом 2 и втором 12 аналоговых сдвиговых регистрах.

Принцип формирования необходимой задержки Т3 вытекает из закона изменения периода входных сигналов.

Для сигналов с постоянным периодом следования Тс время задержки определяется выражением

Тз М/тт(1)

где N - число элементов памяти в каждом регистре;

fr - частота следования тактовых импульсов.

Для этого на второй вход блока 6 управления временем задержки через вход II устройства задержки и второй преобразователь 4 уровня подаются импульсы запуска, следующие с частотой , а на третий вход через вход III устройства задержки поступают импульсные последовательности с частотой fr, обеспечивающие жесткую синхронизацию генератора 5 тактовых импульсов по каждому элементу памяти аналоговых сдвиговых регистров.

Для формирования времени задержки T3i сигналов, следующих с изменяющимся периодом TI по закону

Ti-V+ATi,(2)

где То - постоянная часть периода П, Т0 N,/fT,

кроме подачи импульсов запуска и синхронизации соответственно на вход III устройства задержки, на его вход IV подается код, соответствующий периоду П. на основании которого с помощью блока 6 управления формируется соответствующее время задержки

AT3i N2/fi,(3)

где N2 N-Ni

fi - изменяющая частота в соответствии с изменением поступающего кода.

Таким образом, общее время задержки T3i будет равно

T3i Ni/fT+N2/frT0+ (4)

Выражение (4) подтверждает возможность межпериодной обработки сигналов с изменяющемся периодом от импульса к импульсу. При реализации выражения (4) технически обеспечивается получение любой задержки в любой очередности в соответствии с приходящим кодом. Реализация выражения (4) осуществляется с помощью блока 6 управления временем задержки, функциональная схема которого приведена на фиг.5.

На вход II устройства задержки подаются импульсные последовательности с частотой f0, которые через преобразователь 4 уровня и вход II блока 6 управления временем задержки поступают на первый вход элемента И 14, но не проходят на выход, ожидая сигнал разрешения по второму его входу. На второй вход триггера 15 подается сигнал разрешения е выхода счетчика 19, а

с выхода триггера 15 снимается сигнал запрета на второй вход элемента И 14. Задающий генератора 17 не работает, так как на его втором входе имеется сигнал запрета с второго выхода счетчика 21. На первый вход задающего генератора 17 подается с дешифратора 16 команда на переключение частоты f j в зависимости от поступившего кода на вход IV устройства задержки.

Генератор 5 тактовых импульсов не работает, так как на его входе нет импульсов синхронизации, поэтому с второго выхода генератора 5 тактовых импульсов через вход I блока 6 управления временем задержки сигнала на первые входы первого 19 и второго 20 счетчиков не поступает. Счетчик 19, подсчитывающий число NI импульсов с частотой следования f0 для определения параметра То Ni/fo, находится в нулевом состоянии и открыт по второму входу сигналом первого выхода триггера 21. Счетчик 20, подсчитывающий число импульсов N2, следующих с частотой fi, для определения параметра ATi N2/fj находится в нулевом состоянии и закрыт по второму входу сигналом с второго выхода триггера 21,

При поступлении на вход III устройства задержки зондирующих импульсов, определяющих начало работы блока 6 управления временем задержки в каждом периоде, запускается триггер 15, с выхода которого подается сигнал разрешения на второй вход элемента И 14. По этому сигналу импульсы синхронизации с частотой f0, поданные на первый вход элемент И 14, проходят на его выход и через первый элемент ИЛИ 18 запускают генератора 5 тактовых импульсов, с первого выхода которого импульсные последовательности подаются на вторые входы первого 2 и второго 12 аналоговых сдвиговых регистров, а с второго выхода через вход 1 блока 6 управления - на первые входы первого 19 и второго 20 счетчиков.

Так как первый счетчик 19 по второму входу имеет сигнал разрешения он подсчитывает число импульсов NI и при поступлении последнего из NI выдает сигнал на триггер 15, переключая его в исходное состояние. При этом с выхода триггера 15 выдается сигнал запрета на второй вход элемента И 14, прекращая прохождение синхроимпульсов с частотой f0 на первый вход элемента ИЛИ 18. Одновременно выходной сигнал первого счетчика 19 через элемент ИЛИ 22 переключает триггер 21 в другое состояние, при котором с первого выхода выдается сигнал запрета на второй вход счетчика 19, обнуляя его, а с второго выхода - сигнал на разрешение работы счетчика 20 и задающего генератора 17 на

частоте fi. Номинал частоты fi определяется кодом изменения периода, который поступает на вход IV устройства, Далее сигнал кода поступает на дешифратор 16, который

вырабатывает соответствующую команду на переключение частоты в задающем генераторе 17.

Во время первого периода после окончания формирования параметра Т0, задающий генератор .1.7 начинает работать на частоте fi и через элемент ИЛИ 18 обеспечивает синхронизацию генератора 5 тактовых импульсов, с второго выхода которого через вход I подаются импульсные последовательности с частотой fi на первые входы первого 19 и второго 20 счетчиков. Счетчик 19 закрыт, а счетчик 20 начинает подсчет числа импульсов N2 с приходом последнего из N2 импульсов. Счетчик 20 вырабатывает.

сигнал, который через элемент ИЛИ 22 переключает триггер. 21 в исходное состояние. При этом с его второго выхода запрещающий сигнал поступает на второй вход счетчика 20 и на второй вход задающего

генератора 17, прекращая их работу, а с первого выхода - разрешающий сигнал на второй вход счетчика 19, подготавливая тем самым его к работе в следующем периоде. Параметр ДТ|сформирован. Наэтомзаканчивается первый цикл управления, в результате которого получена задержка входного сигнала в сдвиговых регистрах T3i Ni/fo+N2/fi Ti To+ ATi. С приходом второго зондирующего импульса и кода, соответствующего второму периоду, начинается второй цикл работы блока 6 управления временем задержки. Процессы формирования задержки происходят как и в первом цикле. В результате

время задержки для второго периода будет равно

T32 Ni/f0 + N2/f2 T2 T0+ AT2. С приходом третьего зондирующего импульса и кода, соответствующего третьему

периоду, время задержки для третьего периода будет равно

T33 Ni/fo + N2/f3 T3 To + ДТ3. Рассмотрим более подробно процессы подавления паразитных сигналов в устройстве задержки, обусловленных взаимным влиянием сигналов соседних элементов памяти аналоговых сдвиговых регистров.

Для устранения взаимного влияния сигналов соседних элементов памяти входная

информация в каждый канал двухканальной линии 7 задержки записывается поочередно, т.е. в аналоговый сдвиговый регистр 2 первого канала записываются нечетные выборки с первого выхода коммутатора 8, а в

аналоговый сдвиговый регистр 12 второго канала -четные выборки с второго выхода коммутатора 8. При этом выборки в аналоговые сдвиговые регистры записываются не в каждый элемент памяти, а через один, т.е. в аналоговом сдвиговом регистре 2 нечетные выборки записываются в нечетные элементы памяти, пропуская четные, а в аналоговом сдвиговом регистре 12 четные выборки записываются в четные элементы памяти, пропуская нечетные.

Это осуществляется следующим образом. С выхода преобразователя 1 уровня входная информация (фиг.2.4) поступает на вход коммутатора 8, на первый и второй управляющие входы которого поступают противофазные импульсные последовательности (фиг.2.2 и 2.3) с частотой fT/2 и длительностью Тт () с первого и второго вы ходов делителя 13 частоты на два, на вход которого поступают импульсные последовательности с частотой fT с второго выхода генератора 5 тактовых импульсов. Поэтому коммутатор 8 делает выборки из входной информации с частотой fT, а на его первом выходе будут нечетные выборки (фиг.2.5), следующие с частотой fT/2, которые поступают на аналоговый сдвиговый регистр 2 и записываются в его нечетные элементы памяти.

С второго выхода коммутатора 8 четные выборки (фиг.2.9) с частотой fT/2 поступают на аналоговый сдвиговый регистр 12 и запи- сываются в четные элементы памяти. На вторые входы первого 2 и второго 12 аналоговых сдвиговых регистров поступают импульсные последовательности (фиг.2.1) с частотой fT для управления времени задержки в них с первого выхода генератора 5 тактовых импульсов. Поэтому каждая входная выборка в первом 2 и втором 12 аналоговых сдвиговых регистрах протягивается через два элемента памяти, т.е. при поступлении первой выборки на вход аналогового сдвигового регистра 2 она запишется в первый элемент памяти, в это время в первый элемент памяти аналогового сдвигового регистра 12 запишется нулевая информация.

При поступлении второй выборки на вход аналогового сдвигового регистра 12 нулевая информация из первого элемента памяти перепишется во второй элемент памяти, а в первый элемент памяти запишется вторая выборка. В это время, т.е. во втором такте, в аналоговом сдвиговом регистре 2 первая выборка из первого элемента памяти перепишется во второй элемент памяти, оставив в первом элементе памяти паразитную помеху вследствие неполного переноса заряда (для N Ј 0,25 амплитуда этой помехи составляет более 10% амплитуды первой выборки).

При поступлении на вход аналогового сдвигового регистра 2третьей выборки (третий такт работы) первая выборка из второго элемента памяти перепишется в третий элемент памяти, паразитная помеха из первого элемента памяти перепишется во второй элемент памяти, а третья выборка запишётся в первый элемент памяти. При этом в первом элементе памяти амплитуда паразитной помехи составляет порядка 1 % от амплиттуды первой выборки, а не 10%, если бы мы записали третью выборку вслед за

первой, не оставляя один свободный элемент памяти.

В третьем такте на вход аналогового сдвигового регистра 12 вторая выборка из первого элемента памяти перепишется во

второй элемент, оставив в первом элементе памяти помеху с десятипроцентной амплитудой от себя. В четвертом такте на вход аналогового сдвигового регистра 12 поступает четвертая выборка. В это время вторая

выборка перепишется в третий элемент памяти из второго, в который перепишется паразитная помеха из первого элемента памяти, где осталась паразитная помеха с амплитудой менее 2% от второй выборки,

запишется четвертая выборка.

Такой процесс осуществляется благодаря параллельному тактовому питанию по второму входу первого 2 и второго 12 аналоговых сдвиговых регистров с частотой fT, a

коммутатор 8 управляется противофазными импульсными последовательностями, следующими с частотой fr/2. В пятом и последующих тактах . работы процессы в параллельных каналах двухканальной линии 7 задержки повторяются.

Ключ 9 управляется прямой последовательностью импульсов (фиг.2.7) длительностью Т с первого выхода делителя 13 частоты на два, поэтому он открывается во время

нечетных выборок, а ключ 10 управляется противофазной последовательностью импульсов (фиг.2.11) с второго выхода делителя 13 частоты на два, поэтому он открывается во время четных выборок. В

связи с этим с выхода аналогового сдвигового регистра 2 нечетные выборки (фиг.2.6) проходят на первый вход сумматора 11 (фиг.2.8), а паразитные помехи, поступающие на выход в четные такты, через первый

ключ 9 не проходят, так как он в это время закрыт.

С выхода аналогового сдвигового регистра 12 четные выборки (фиг.2.10) проходят через ключ 10 в четные такты на второй

вход сумматора 11 (фиг.2.12), а паразитные помехи, поступающие на выход в нечетные такты, через второй ключ 10 не проходят, так как он в это время закрыт.

На выход сумматора 11 нечетные и чет- ные выборки задержанной входной информации объединяются (фиг.2.13) и следуют с частотой fT на вход фильтра 3 нижних частот, который выделяет огибающую дискретных выборок входной информации (фиг.2.14) и выдает ее в качестве задержанного сигнала с периодом Тс на выход устройства задержки.

Таким образом, образование двух каналов в линии 7 задержки, обеспечение парал- лельной работы первого 2 и второго 12 аналоговых сдвиговых регистров на тактовой частоте 1т, поочередное их питание входной информацией с помощью коммутатора 8, запись ее в первый 2 и второй 12 аналоговые сдвиговые регистры через один элемент памяти и поочередное считывание с их выходов задержанной информации на входы сумматора 11с помощью первого 9 и второго 10 ключей позволило сохранить чис- ло N элементов памяти в каждом регистре, а также снизить амплитуду паразитных помех, обусловленных взаимным влиянием сигналов соседних элементов памяти, в 10 раз и более, при этом частотные характери- стики первого 2 и второго 12 аналоговых сдвиговых регистров становятся более прямолинейными.

Использование предлагаемого устройства в импульсных РЛС позволяет обеспе- чить обработку сигналов как с постоянным, так и с изменяющимся периодом следования, устраняя при этом наличие слепых скоростей, а также повысить качество обработки сигналов в целом.

Формула изобретения

Устройство задержки, содержащее первый и второй преобразователи уровня, входы которых являются соответственно первым и вторым входами устройства за- держки, первый аналоговый сдвиговый регистр, генератор тактовых импульсов, первый выход которого соединен с вторым входом первого аналогового сдвигового регистра, блок управления временем задержки, первый и второй входы которого соединены соответственно с вторым выходом генератора тактовых импульсов и выходом второго преобразователя уровня, третий и четвертый входы блока управления временем задержки являются соответственно третьим и четвертым входами устройства задержки, а выход соединен с входом генератора тактовых импульсов, и фильтр нижних частот, выход которого является выходом устройства задержки, отличающееся тем, что, с целью повышения точности сохранения амплитуды задержанных сигналов за счет уменьшения амплитуды помех от взаимного влияния сигналов соседних элементов памяти аналогового сдвигового регистра, линия задержки выполнена двухканальной, состоящей из делителя частоты на два, коммутатора, первого и второго ключей, сумматора и второго аналогового сдвигового регистра, причем вход делителя частоты на два соединен с вторым выходом генератора тактовых импульсов, а первый и второй выходы соединены соответственно с первым и вторым управляющими входами коммутатора, информационный вход которого соединен с выходом первого преобразователя уровня, первый выход коммутатора через последовательно соединенные первый аналоговый сдвиговый регистр и первый ключ соединен с первым входом сумматора, а второй выход коммутатора через последовательно соединенные второй аналоговый сдвиговый, регистр и второй ключ - с вторым входом сумматора, выход которого соединен с входом фильтра нижних частот, управляющие входы первого и второго ключей соединены соответственно с первым и вторым выходами делителя частоты на два, второй вход второго аналогового сдвигового регистра соединен с выходом генератора тактовых импульсов.

.1 .2S NC.0.5

Фиг. 3

I о

ОЛ 0.2 0,3 0/f 0,5

Нормироданная частота f/fc

Фае. Ь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1991 |

|

SU1800601A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Цифровой фазовращатель | 1984 |

|

SU1239630A1 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

| ЧАСТОТНО-МОДУЛИРОВАННЫЙ ВЫСОТОМЕР | 1996 |

|

RU2106655C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

Изобретение относится к радиотехнике и может быть использовано для задержки электрических сигналов. Цель изобретения - повышение точности сохранения амплитуды задержанных сигналов за счет уменьшения амплитуды помех от взаимного влияния сигналов соседних элементов памяти аналогового сдвигового регистра. Устройство задержки содержит первый и второй преобразователи уровня,фильтр нижних частот, генератор тактовых импульсов, блок управления времени задержки и двухка- нальную линию задержки, имеющую коммутатор, первый и второй ключи, .сумматор, первый и второй аналоговые сдвиговые регистры и делитель частоты на два. Использование данного устройства в импульсных РЛ С позволяет обеспечить обработку сигналов как с постоянным, так и с изменяющимся периодом следования, устраняя при этом наличие слепых скоростей, а также повысить качество обработки сигналов в целом. 5 ил. Ё

ВходиВыход лВход I

| Зинкл | |||

| К/МОП - делитель частоты, как синхронизатор ГШЗ-линии задержки | |||

| - Электроника, 1975, № 16 | |||

| Авторское свидетельство СССР № 1385985.Ю1.Н 03 К 5/153, 1987 | |||

| Приборы с зарядовой связью | |||

| Под ред | |||

| М.Хоувза, Д.Моргана | |||

| - М.: Энергоиздат, 1981, с.135-139, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1992-03-23—Публикация

1990-04-06—Подача