ToKinotue uf- tg/меи

ПереЗатцвл vacfnt

Вихав

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ цикловой синхронизации | 1975 |

|

SU664304A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Способ цикловой синхронизации и система для его осуществления | 1987 |

|

SU1711342A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ | 2020 |

|

RU2752003C1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| СПОСОБ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ В УСТРОЙСТВАХ ПРИЕМА СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2020 |

|

RU2747777C1 |

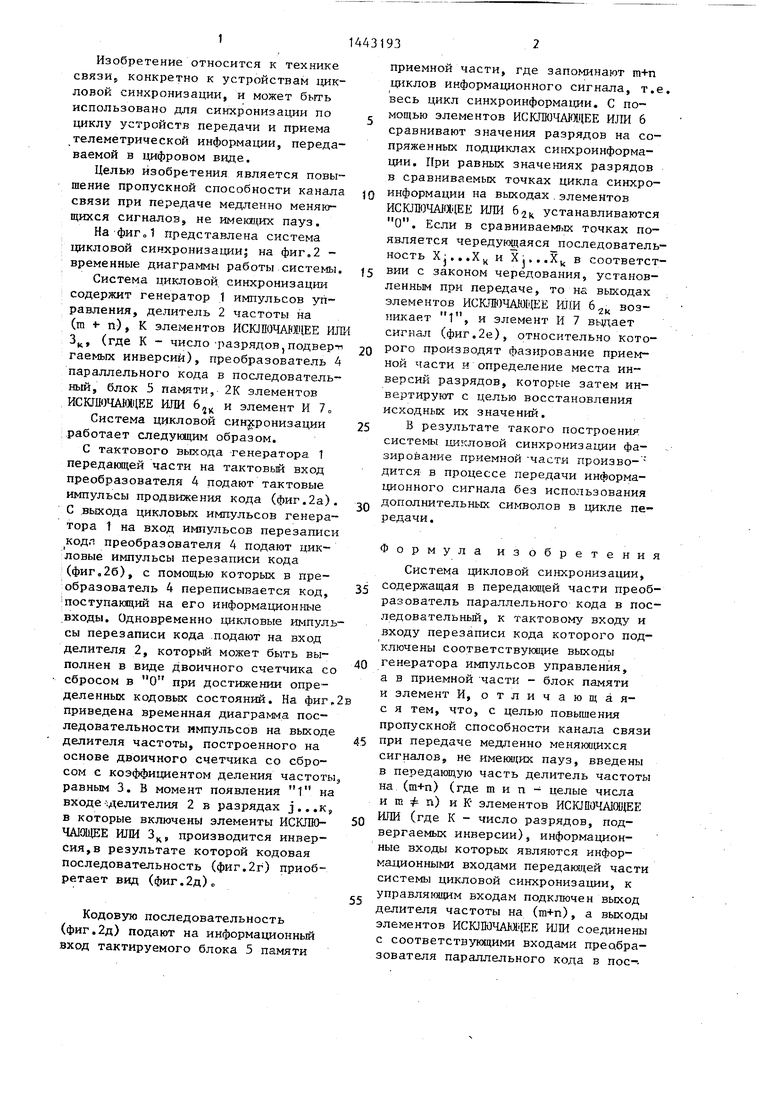

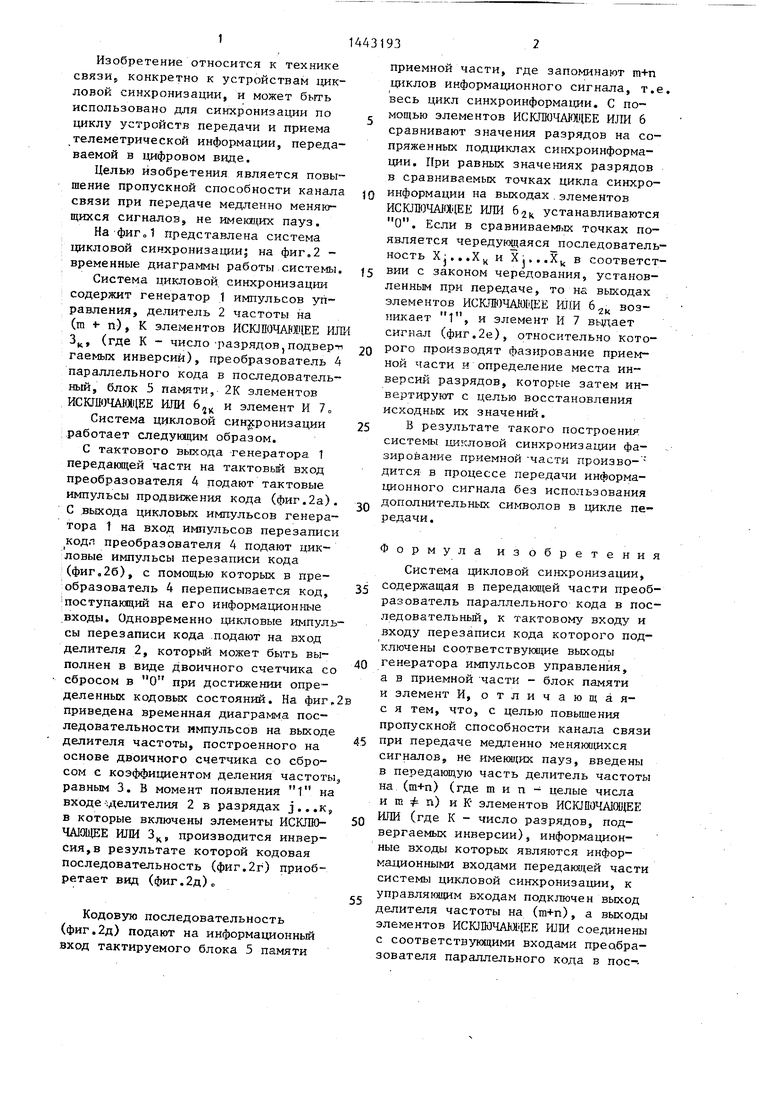

Изобретение относится к технике связи. Цель изобретения - повышение пропускной способности канала связи при передаче медленно меняющихся сигналов, не иъзеющих пауз. Система цикловой синхронизации содержит в передающей части г-р 1 импульсов управления, делитель 2 частоты, эл-ты ИСКШ)ЧАЮ1ЦЕЕ ИЛИ 3 и преобразователь 4 параллельного кода в последовательньй, а в приемной части блок памяти 5, зл-ты ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и эл-т И 7. В данной системе цикловой синхронизации фазирование приемной части производится в процессе передачи информационного сигнала без использования дополнительных символов в цикле передачи. Цель достигается введением делителя 2 и эл-тов ИСКЛЮЧАКИЦЕЕ ИЛИ 3 и 6. 2 Ш1.

HMHIMUH KoStt

Sxoi

ntfieaen.

WW:

-й канал j-potpf н fasiad

Пцигнюя часа

&9

Ни гули дюзирв аю№

Фие.1

Изобретение относится к технике связи,, конкретно к устройствам цикловой синхронизации, и может быть использовано для синхронизации по циклу устройств передачи и приема телеметрической информации, передаваемой в цифровом виде.

Целью изобретения является повышение пропускной способности канала связи при передаче медленно меняющихся сигналов, не имекщих пауз.

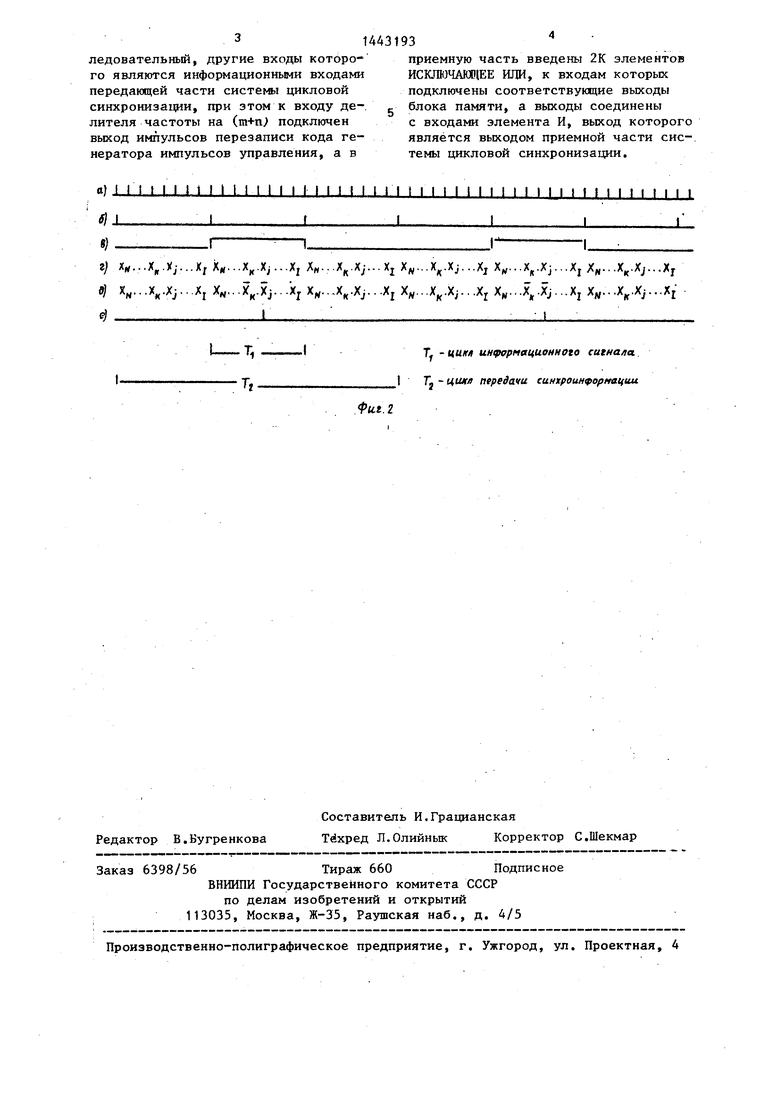

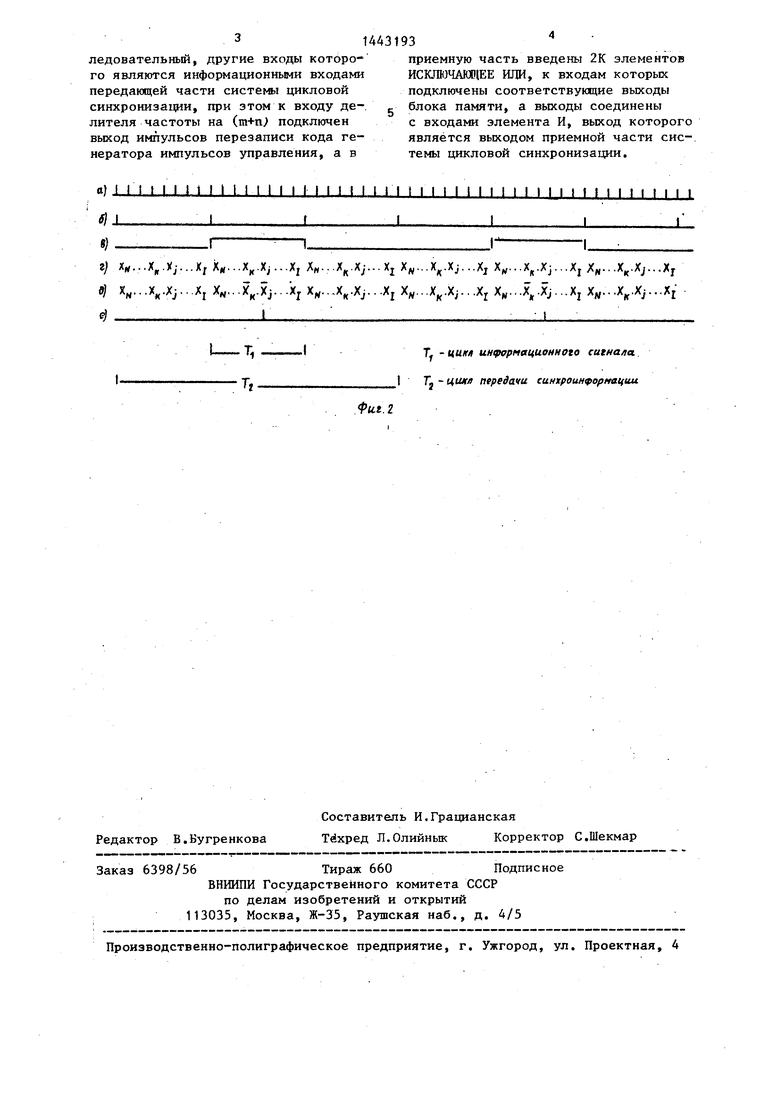

На фиго1 Представлена система цикловой синхронизации; на фиг,2 - временные диаграммы работы системы,

Система цикловой синхронизации содержит генератор 1 импульсов управления, делитель 2 частоты на (га +- п), К элементов ИСЮПОЧАИЦЕЕ ШШ 3, (где К - число разрядов,подверт гаемых инверсий), преобразователь 4 параллельного кода в последовательный, блок 5 памяти, 2К элементов ИСКГЮЧАИХЦЕЕ ИЖ 6 и элемент И 7„

Система цикловой син|сронизации работает следуицим образом.

С тактового выхода генератора 1 переданщей части на тактовьй вход преобразователя 4 подают тактовые импульсы продвижения кода (фиг.2а). С выхода цикловых импульсов генератора 1 на вход импульсов перезаписи кодл преобразователя 4 подают цикловые импульсы перезаписи кода (фиг,26), с помощью которых в преобразователь 4 переписывается код, поступающий на его информационные ОБХОДЫ. Одновременно 1дакловые импульсы перезаписи кода подают на вход делителя 2, который может быть выполнен в виде двоичного счетчика со сбросом в О при достижении определенных кодовых состояний. На фиг, приведена временная диаграмма последовательности импульсов на выходе делителя частоты, построенного на основе двоичного счетчика со сбросом с коэффициентом деления частоты равным 3, В момент появления 1 на входечделителия 2 в разрядах J,..K, в которые включены элементы ИСКЛЮ- ЧАЮЩЕЕ ИЛИ 3, производится инверсия, в результате которой кодовая последовательность (фиг.2г) приобретает вид (фиг.2д)„

Кодовую последовательность (фиг,2д) подают на информационный вход тактируемого блока 5 памяти

0

5

0

5

приемной части, где запоминают m+n циклов информационного сигнала, т.е. весь цикл синхроинформации. С помощью элементов ИСКЛЮЧАИЦЕЕ ИЛИ 6 сравнивают значения разрядов на сопряжен ньсх под циклах синхроинформации. При равных значениях разрядов в сравниваемых точках цикла синхроинформации на выходах.элементов ИСЮдаЧАКадЕЕ или 6 устанавливаются О, Если в сравниваем11К точках появляется чередуяздаяся последовательность Xj.,.X) и Xj,,,X в соответствии с законом чередования, установленным при передаче, то на выходах элементов ИСКШЗЧАЮЩЕЕ ЮШ 6 возникает 1, и элемент И 7 вьщает сигнал (фиг,2е), относительно которого производят фазирование приемной части и определение места инверсий разрядов, которые затем инвертируют с целью восстановления исходных их значений,

В результате такого построения системы цикловой синхронизации фазирование приемной -части произво- дится в процессе передачи информационного сигнала без использования дополнительных символов в цикле передачи.

Формула изобретения

Система цикловой синхронизации, содержащая в передающей части преобразователь параллельного кода в послед овательньй, к тактовому входу и входу перезаписи кода которого подключены соответствугацие выходы генератора импульсов управления, а в приемной -части - блок памяти и элемент И, отличающая- с я тем, что, с целью повышения пропускной способности канала связи при передаче медленно меняюищхся сигналов, не имекацих пауз, введены в передающую часть делитель частоты на (m+n) (где тип- целые числа и m чЬ п) и К- элементов ИСЮПОЧАМЧЕЕ ИЛИ (где К - число разрядов, подвергаемых инверсии), информационные входы которых являются информационными входами передаю цей части системы цикловой синхронизации, к управлякнцим входам подключен выход делителя частоты на (т+п), а выходы элементов ИСЮ1ЮЧАИ.1|ЕЕ ИЛИ соединены с соответствующими входами преобразователя параллельного кода в пос-31443193

ледовательный, другие входы которо- приемную часть введены 2К элементов го являются информационными входами ИСКЛЮЧАга11ЕЕ ИДИ, к входам которых

подключены соответствующие выходы g блока памяти, а выходы соединены с входами элемента И, выход которого является выходом приемной части системы цикловой синхронизации.

передающей части система цикловой синхронизации, при этом к входу делителя частоты на (m+n; подключен выход импульсов перезаписи кода генератора импульсов управления, а в

о) I it I I I 1 1 I I 1 I 1 I I I I I I 1 1 I t I I I I I I I I I I I 1 I I II 1 1 М М I I I I

rfl J tI l

|.

в)I1 I

Z) X|...X|j.Xj. ..K; АИ. ..X.Xj ...Xj }(H- : X...X.Xj. ..Xj X...X|j.Xj...Xj XN- .X.Xj...Xj- X.. .X.Xj. Xj X,. . -Xj X...X.Xj.. -Xj X...Xj.X;.. .Xj X...X.Xj. ..Xj Хд,.. ,X.Xj...Xj

tTf 1T, -uuir/i индюрмациомного futHoaa.

|.

Tj цшт передачи синхсоин орнлчии

| Способ цикловой синхронизации | 1975 |

|

SU664304A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-12-07—Публикация

1985-12-29—Подача