Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых узлов, блоков и устройств.

Целью изобретения является расширение области применения устройства для контроля цифровых узлов путем обеспечения возможности контроля проводного монтажа приборов, секций,

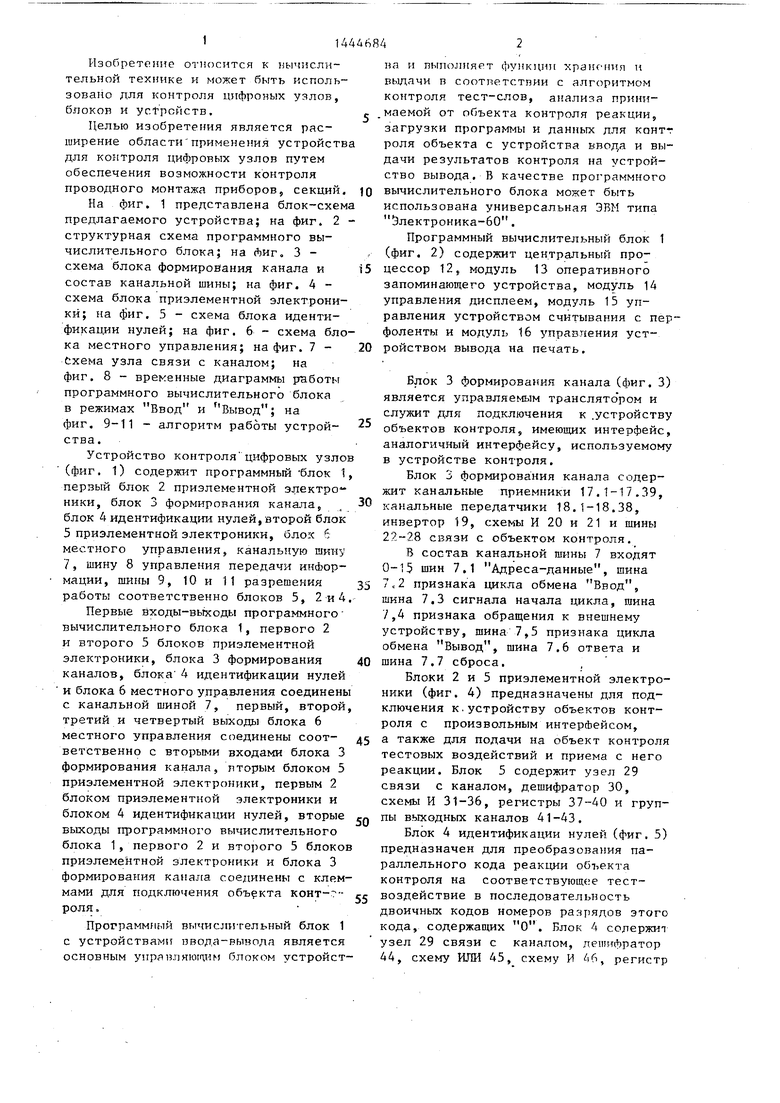

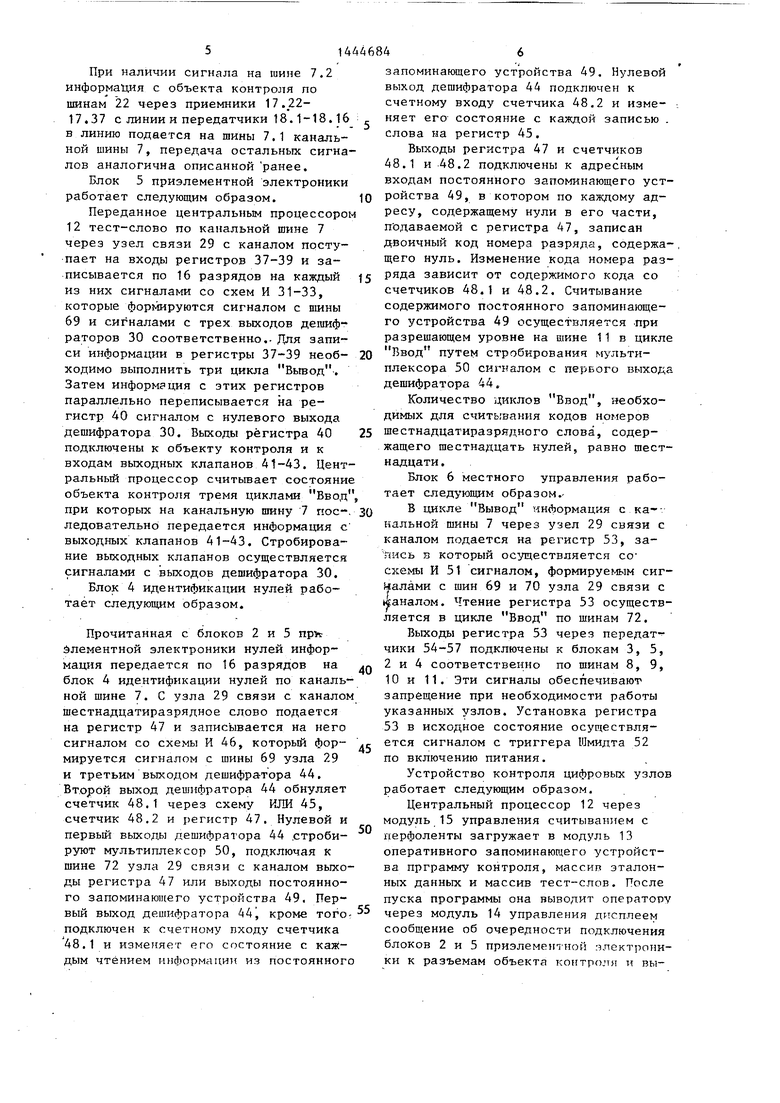

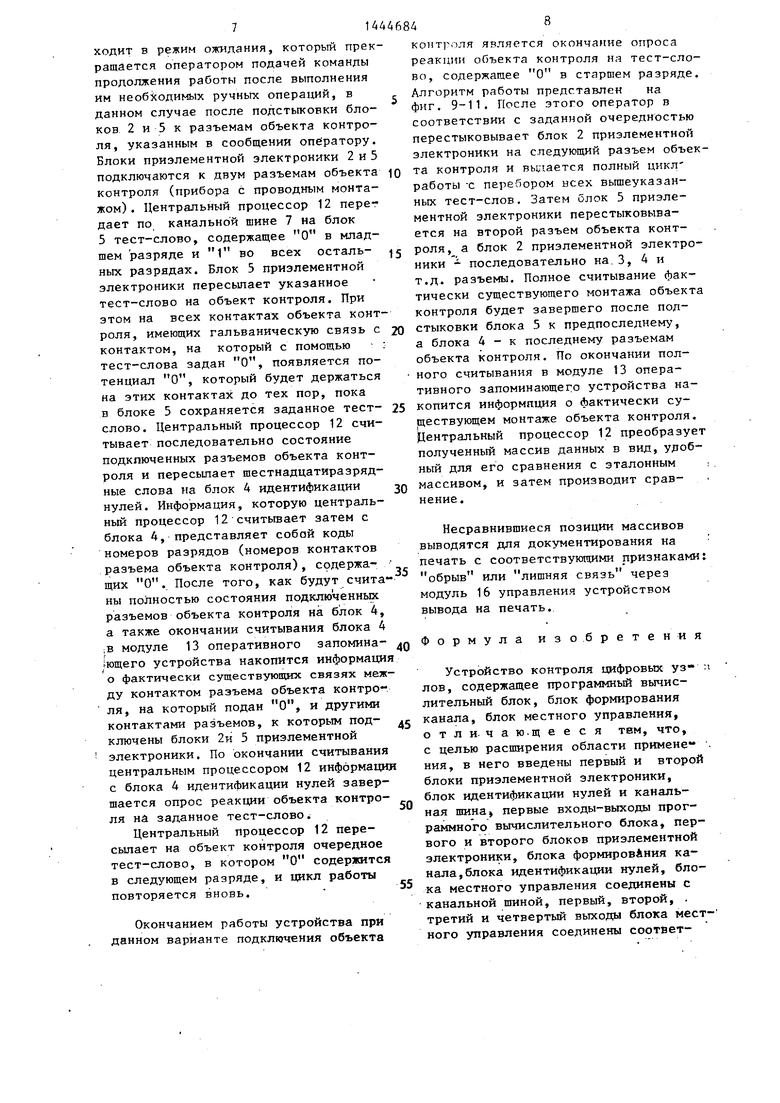

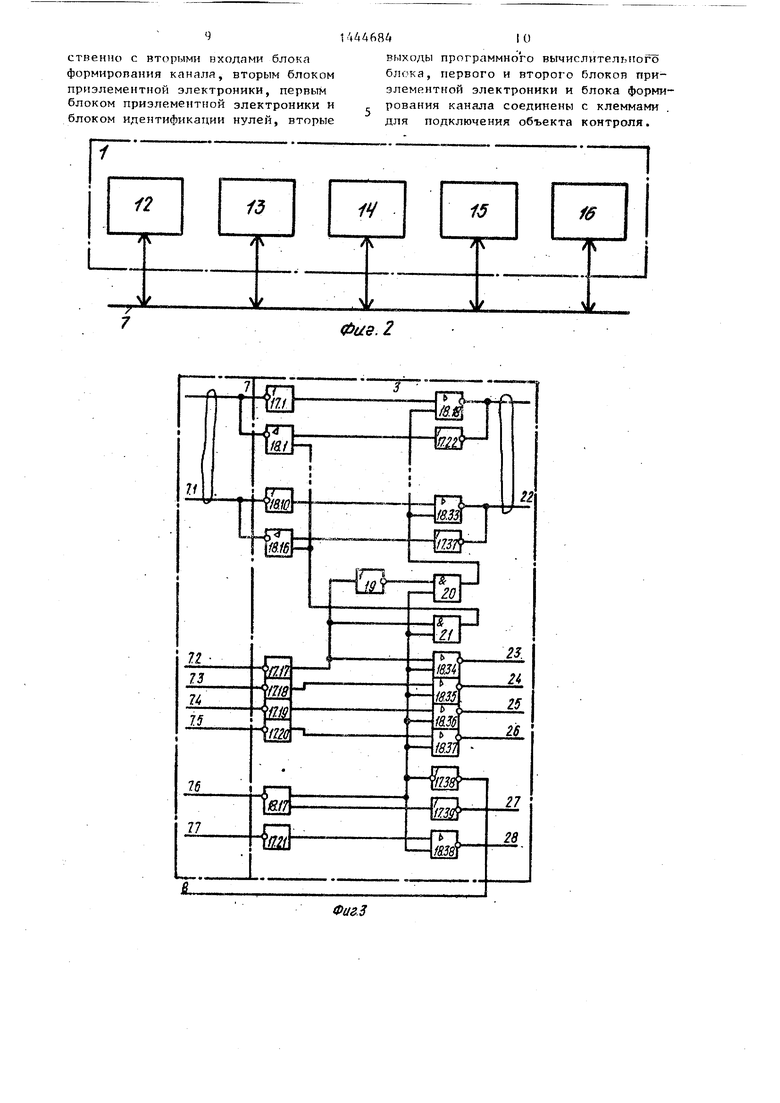

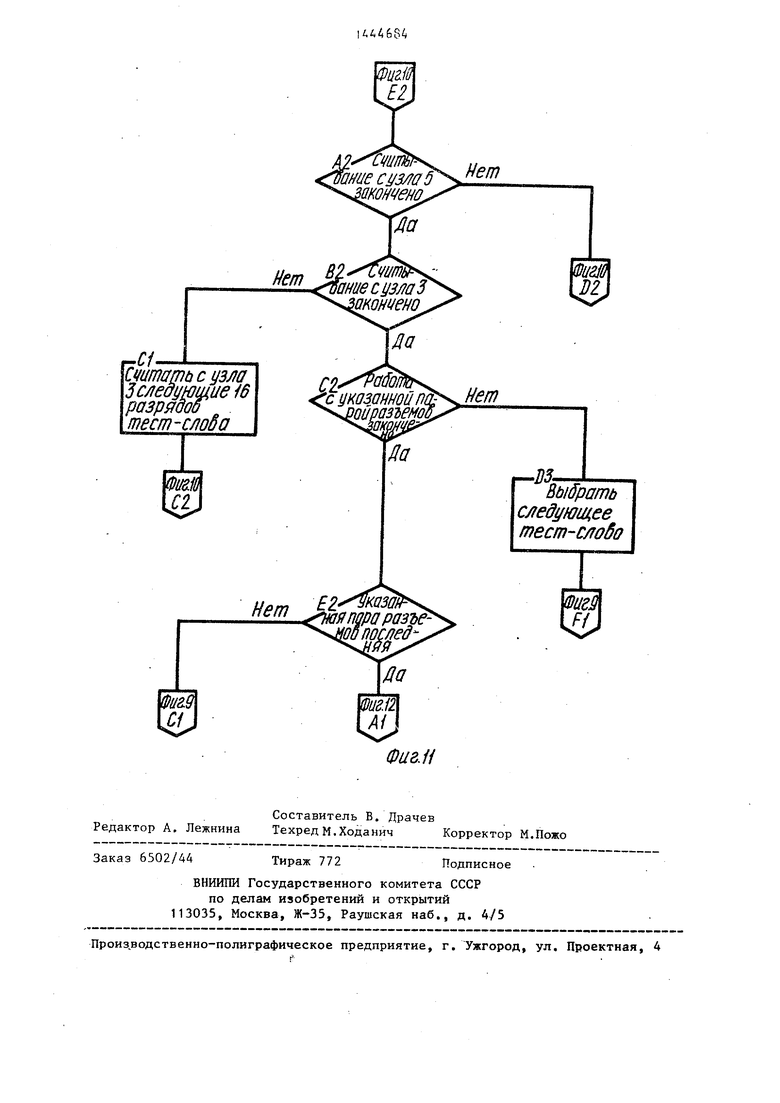

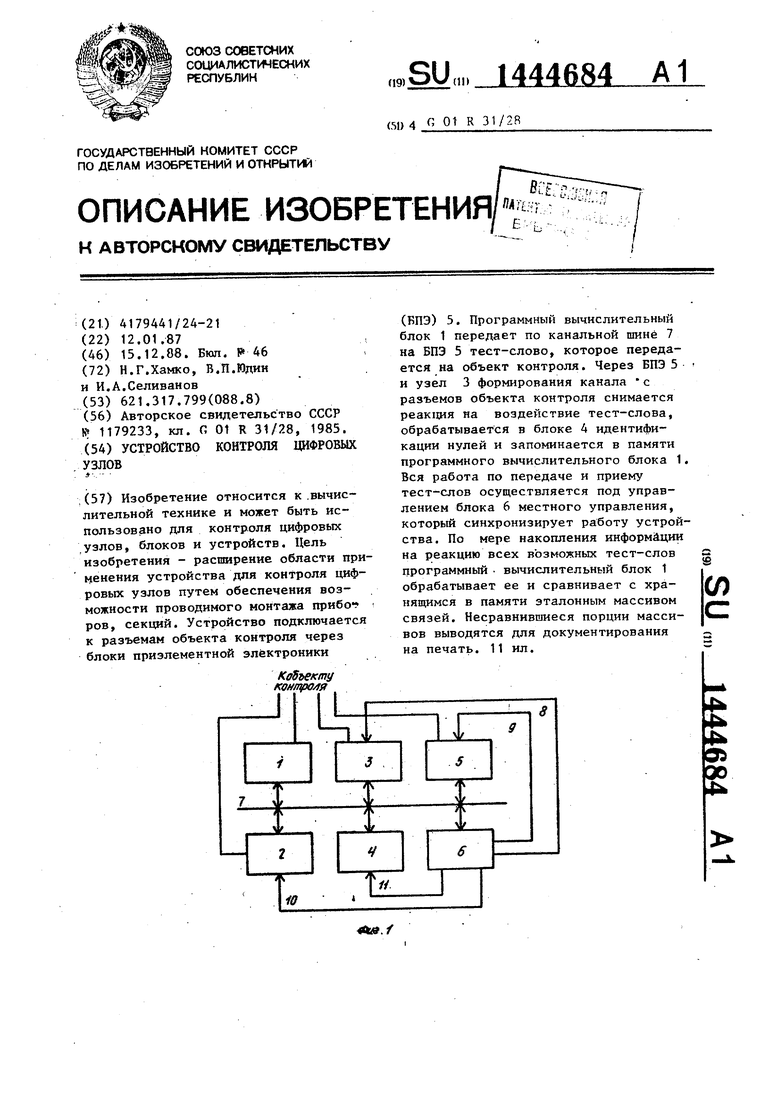

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - структурная схема программного вычислительного блока; на Лиг, 3 - схема блока формирования канала и состав канальной шины; на фиг. 4 - схема блока приэлементной электроники; на фиг. 5 - схема блока идентификации нулей; на фиг. 6 - схема блока местного управления; на фиг. 7 - Схема узла связи с каналом; на фиг. 8 - временные диаграммы работы программного вычислительного блока в режимах Ввод и Вывод ; на фиг. 9-11 - алгоритм работы устрой- ства.

Устройство контроля цифровых узлов (фиг, 1) содержит программный блок 1, первый блок 2 приэлементной электро НИКИ, блок 3 формирования канз-па , блок 4 идентификации нулей, второй блок 5 приэлементной электроники, блох 6 местного управления, канальную шкну 7, шину 8 управления передачи информации, шины 9, 10 и 11 разрешения работы соответственно блоков 5, 2 и 4.

Первые вхсды-вь1ходы программного вычислительного блока 1, первого 2 и второго 5 блоков приэлементной электроники, блока 3 формирования каналов, блока 4 идентификации нулей и блока 6 местного управления соединены с канальной шиной 7, первый, второй, третий и четвертый выходы блока 6 местного управления соединены соот- ветственно с вторыми входами блока 3 формирования канала, вторым блоком 5 приэлементной электроники, первым 2 блоком приэлементной электроники и блоком 4 идентификации нулей, вторые выходы программного вычислительного блока 1, первого 2 и второго 5 блоков приэлементной электроники и блока 3 формирования канала соединены с клеммами для подключения объекта конт- - роля.

Программный вг.1числительный блок 1 с устройствами нвода-вывода является основным yпpalзляIOIaи блоком устройст

0 5

0 з

0 5 с

ва t выполняет функции храигршл и выдачи в соотяетстпии с алгоритмом контроля тест-слов, анализа принимаемой от объекта контроля реакции, загрузки программы и данных для кантг роля объекта с устройства ввода и выдачи результатов контроля на устройство вывода. В качестве программного вычислительного блока может быть использована универсальная ЭВМ типа Электроника-60.

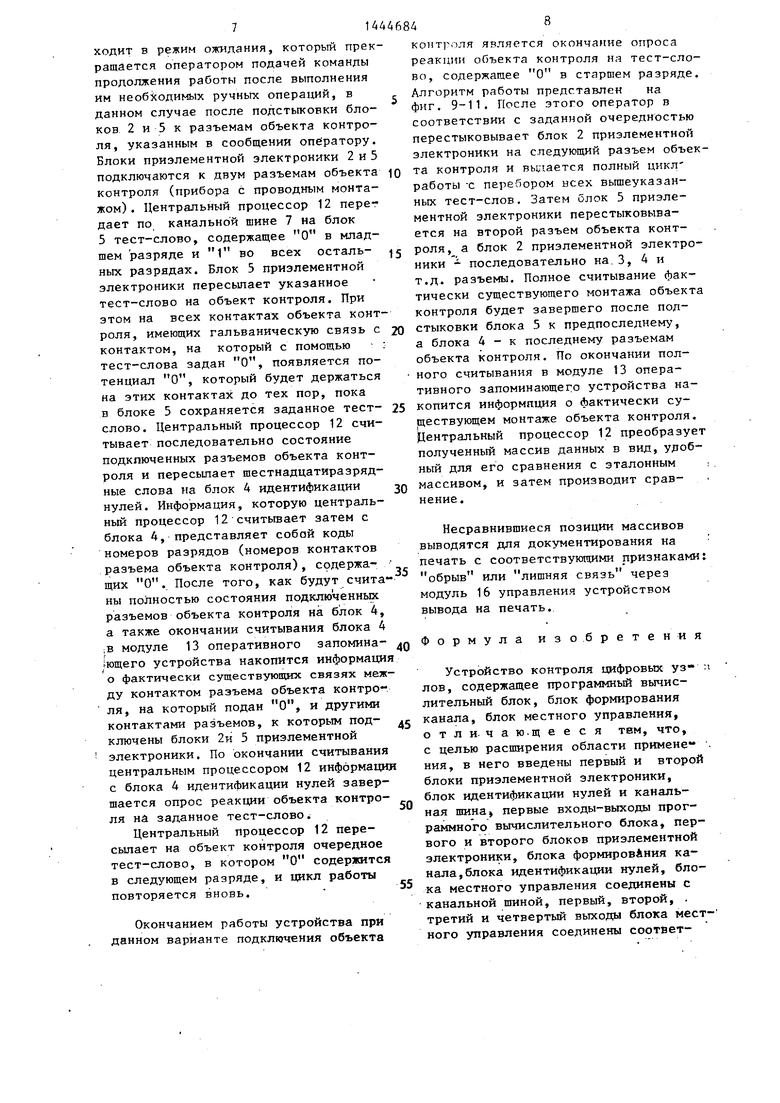

Программный вычислительный блок 1 (фиг. 2) содержит центральный процессор 12J модуль 13 оперативного запоминающего устройства, модуль 14 управления дисплеем, модуль 15 управления устройством считывания с перфоленты и модуль 16 управления устройством вывода на печать.

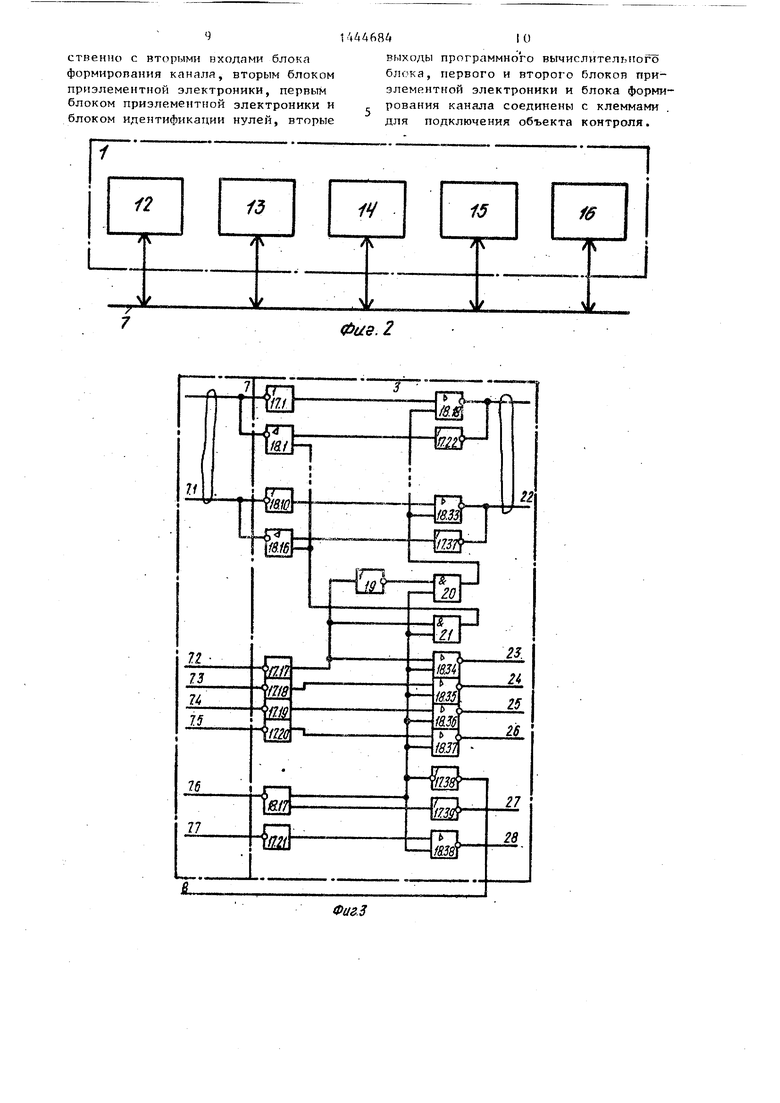

Блок 3 формирования канала (фиг. 3) является управляемым транслято ром и слуяшт для подключения к .устройству объектов контроля, имеющих интерфейс, аналогичный интерфейсу, используемому в устройстве контроля.

Блок 3 формирования канала содержит канальные приемники 17.1-17.39, канальные передатчики 18.1-18.38, инвертор 19, схемы И 20 и 21 и шины 22-28 связи с объектом контроля.

В состав канальной шины 7 входят 0-15 шин 7,1 Адреса-данные, шина 7,2 признака цикла обмена Ввод, шина 7.3 сигнала начала цикла, шина 7,4 признака обращения к внешнему устройству, шина 7,5 признака цикла обмена Вывод, шина 7.6 ответа и шина 7.7 сброса.

Блоки 2 и 5 приэлементной электроники (фиг. 4) предназначены для подключения к.устройству объектов контроля с произвольным интерфейсом, а также для подачи на объект контроля тестовых воздействий и приема с него реакции. Блок 5 содержит узел 29 связи с каналом, дешифратор 30, схемы И 31-36, регистры 37-40 и группы выходных каналов 41-43.

Блок 4 идентификации нулей (фиг, 5) предназначен для преобразования параллельного кода реакции объекта контроля на соответствующее тест- воздействие в последовательность двоичных кодов номеров разрядов этого кода, содержащих О. Блок 4 содержи узел 29 связи с каналом, дешифратор 44, схему ИЛИ 45, схему И 46, регистр

47, счетчики 48.1 и 48,2, постоянное запоминающее устройство 49 и мультиплексор 50.

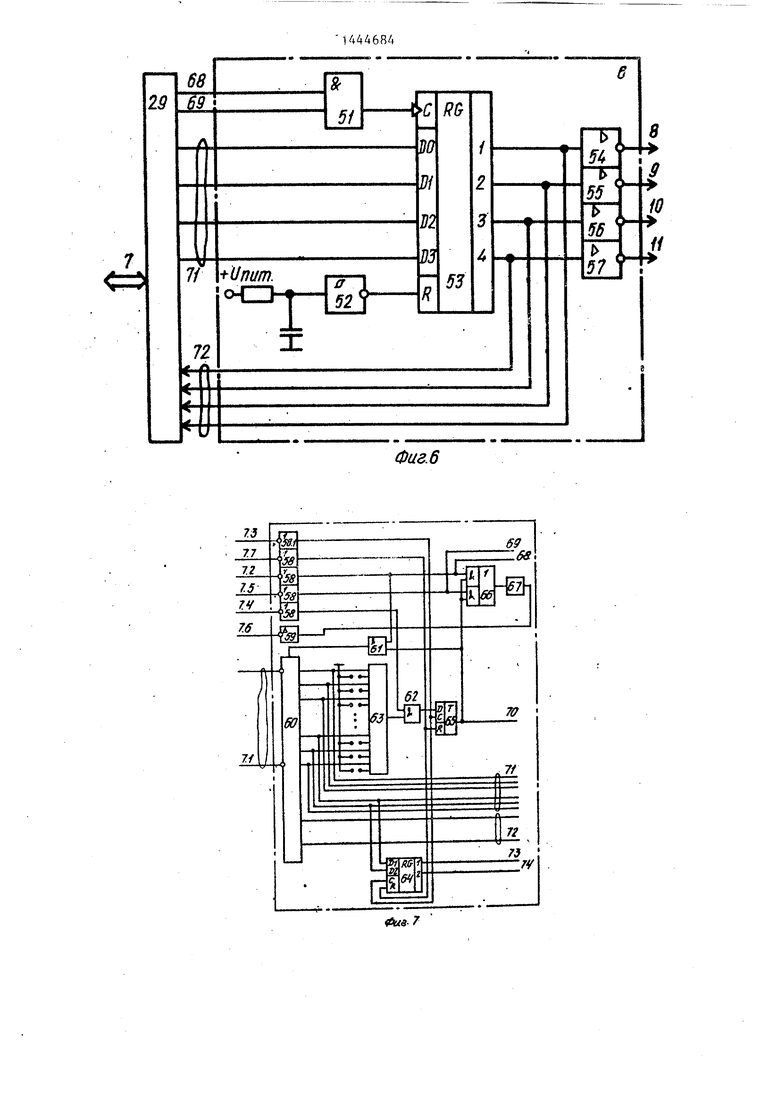

Блок 6 местного управления (фиг. 6 управляет работой блоков 2, 3, 4 и 5 Блок 6 содержит узел 29 связи с каналом, схему, И 51, триггер Шмидта 52, регистр 33 и инверторы 54-57.

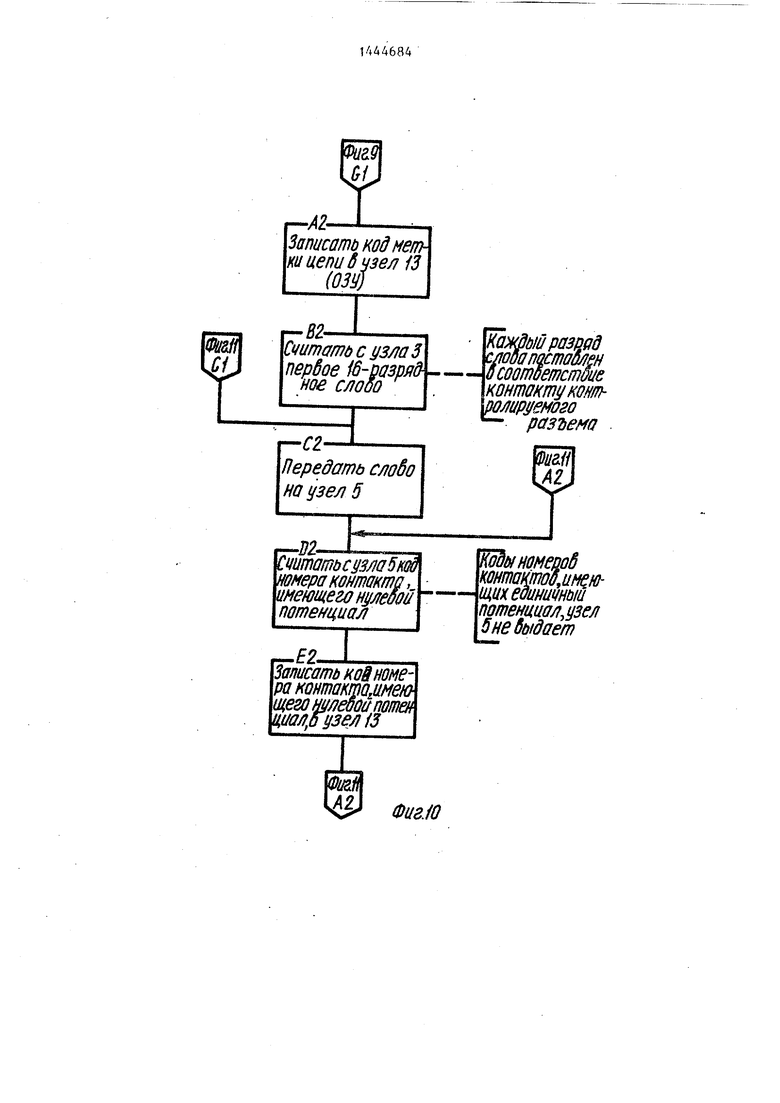

Узел 29 связи с каналом (фиг. 7) предназначен для обеспечения пересылок информации между блоками устройства контроля.

Узел 29 содержит приемники 58.1- 58.5 с линии, передатчик 59 в линию, приемо-передатчики 60, схемы И 61 и 62, схему 63 сравнения, регистр 64, триггер 65, схему 2И-Ш1И 66, схему 67 задержки, шину 68 разрешения чтения информации, шину 69 разрешения записи информации, шину 70 выбора узла, шины 71 записи информации, шины 72 чтения информации, нулевую шину 73 адреса выбора регистра и, первую шину 74. адреса выбора регистра.

Устройство контроля цифровых узло построено по схеме с общей шиной. Обмен информацией в нем осуществляется по инициативе центрального процессора 12 через узлы связи с узлом 29 в соответствии с временными диаграммами, представленными на фиг. 8. Выдача информации с центрального процессора 12 на один из блоков 2, 4, 5 и модулей 13, 14, 15, 16 устройства производится следующим образом. Центральный про- цесрор 12 выставляет требуемый адрес обращения на шину 7.1 канальной шины 7, признак обращения к внешнему устройству на шину 7.4 и сигнал начала цикла на шину 7.3.Через время,необходимое для надежной передачи адреса, процессор 12 выставляет на шину 7.1 соответствующие данные и сигнал на шину 7.5 признака цикла обмена Вы

вод

Установленный на шине 7.1 адрес поступает на узлы связи с каналом всех блоков устройства, где пройдя через приемо-передаГчики 60 поступает на схему 63 сравнения. Схема 63

Блок 3 формирования канала не имеет узла 29 связи с каналом, так как является транслятором канальных сигналов. Он работает следующим образом. Канальные сигналы, поступающ на блок 3 по шине 7, проходят через

50

приемники 17.1-17.21, поступают на передатчики соответственно 18.1- 18.38 и при отсутствии запрещающего сигнала на шине 8 и сигнала на шине

сравнения узла 29, на котором собст- 55 подаются на объект контроля по

венный адрес (заданный на кроссиро- шинам 22-26 и 28, сигнал с объекта

вочном поле) совпал с поступившим

с канальной шины 7, формирует на

выходе сигнал, опрашивающий схему

контроля с шины 27 через приемник. 17.39 и передатчик 18.17 подается на шину 7.6 канальной шины 7.

0

5

0

И 62. При наличии сигнала на шине

7.4признака обращения к внешнему устройству схема И 62 формирует сигнал на вход триггера 65, запись в которой производится по шине 7.3 через приемник 58.1 с линии. Выход триггера 65 стробирует схему 66, которая вместе со схемой задержки

67 формирует через передатчик 59 в линию при наличии сигнала на шине

7.5импульс ответа на шину 7.6 канальной шины 7. Первый и второй разряды адреса с приемо-передатчиков 60 поступают на входы регистра 64, запись в который осуществляется сигналом на шине 7.3 через приемник 58.1 с линии . Сброс регистра 64

и триггера 65 осуществляется сигналом на шине 7.7 через приемник 58,2 с линии.

Установленные к этому времени на шине 7.1 данные через канальные приемо-передатчики 60 по шине 71 постуS пают на заданный блок и сопроБож,па- ются сигналами разрешения записи информации по шине 69, выбора блока 70 и двумя разрядами адреса по шинам 73 и 74.

0 Работа при чтении центральным процессором 12 информации отличается тем, что вместо сигнала на шину 7.5 процессор выставляет сигнал на шину 7.2 признака цикла обмена Ввод.

5 В этом случае на- требуемый блок пересылается сигнал по шине 68, по шине 72 данные от узла подаются на приемо-передатчики 60, которые стро- бируются для передачи информации на канальную шину 7 сиг налом со схемы И 61. Сигнал на выход схемы И 61 формируется сигналом с выхода триггера 65 при наличии сигнала на шине 7.2.

Блок 3 формирования канала не имеет узла 29 связи с каналом, так как является транслятором канальных сигналов. Он работает следующим образом. Канальные сигналы, поступающие на блок 3 по шине 7, проходят через

0

5

0

приемники 17.1-17.21, поступают на передатчики соответственно 18.1- 18.38 и при отсутствии запрещающего сигнала на шине 8 и сигнала на шине

контроля с шины 27 через приемник. 17.39 и передатчик 18.17 подается на шину 7.6 канальной шины 7.

-

При наличии сигнала на шине 7.2 информадая с объекта контроля по шинам 22 через приемники 17,22- 17.37 с линии и передатчики 18.1-18.16 в линию подается на шины 7.1 канальной шины 7, передача остальных сигналов аналогична описанной ранее.

Блок 5 приэлементной электроники работает следующим образом.

Переданное центральным процессором 12 тест-слово по канальной шине 7 через узел связи 29 с каналом поступает на входы регистров 37-39 и записывается по 16 разрядов на каждый из них сигналами со схем И 31-33, которые формируются сигналом с шины 69 и сигналами с трех ВЬЕХОДОВ дешифраторов 30 соответственно.. Для записи информации в регистры 37-39 необходимо выполнить три цикла Вьгеод. Затем информация с этих регистров параллельно переписывается на регистр 40 сигналом с нулевого выхода дешифратора 30. Выходы регистра 40 подключены к объекту контроля и к входам выходных клапанов 41-43. Центральный процессор считьтает состояни объекта контроля тремя циклами Ввод при которых на канальную шину 7 последовательно передается информация с выходных клапанов 41-43. Стробирова- ние выходных клапанов осуществляется сигналами с выходов дешифратора 30.

Блок 4 идентификации нулей работает следующим образом.

Прочитанная с блоков 2 и 5 пртк элементной электроники нулей информация передается по 16 разрядов на блок 4 идентификации нулей по канальной шине 7. С узла 29 связи с каналом шестнадцатиразрядное слово подается на регистр 47 и записывается на него сигналом со схемы И 46, который формируется сигналом с шины 69 узла 29 и третьим выходом дешифратора 44. Второй выход дешифратора 44 обнуляет счетчик 48.1 через схему ИЛИ 45, счетчик 48.2 и регистр 47. Нулевой и первый выходы дешифратора 44 .строби- руют мультиплексор 50, подключая к шине 72 узла 29 связи с каналом выходы регистра 47 или выходы постоянного запоминающего устройства 49, Первый выход дешифратора 44, кроме того подключен к счетному входу счетчика 48.1 и изменяет его состояние с каждым чтением информации из постоянног

5

5

0

5

0

0

Q

5

0

запоминающего устройства 49. Нулевой выход дешифратора 44 подключен к счетному входу счетчика 48.2 и изме- . няет его состояние с каждой записью . слова на регистр 45.

Выходы регистра 47 и счетчиков 48.1 и 48.2 подключены к адресным входам постоянного запоминающего устройства 49, в котором по каждому адресу, содержащему нули в его части, подаваемой с регистра 47, записан двоичный код номера разряда, содержа-, щего нуль. Изменение кода номера разряда зависит от содержимого кода со счетчиков 48.1 и 48.2. Считывание содержимого постоянного запоминающего устройства 49 осуществляется .при разрешающем уровне на шине 11 в цикле Ввод путем стробированич мультиплексора 50 сигналом с первого выхода дешифр а т ора 44.

Количество циклов Ввод, необходимых для считывания кодов номеров шестнадцатиразрядного слова, содержащего шестнадцать нулей, равно шестнадцати.

Блок 6 местного управления работает следующим образом.В цикле Вывод информация с ка-- кальной шины 7 через узел 29 связи с каналом подается на регистр 53, за- TsHCb в который осуществляется со- схемы И 51 сигналом, формируемым сигналами с шин 69 и 70 узла 29 связи с каналом. Чтение регистра 53 осуществляется в цикле Ввод по шинам 72.

Выходы регистра 53 через передат- чики 54-57 подключены к блокам 3, 5, 2 и 4 соответственно по шинам 8, 9, 10 и 11. Эти сигналы обеспечивают запрещение при необходимости работы указанных узлов. Установка регистра 53 в исходное состояние осуществляется сигналом с триггера Шмидта 52 по включению питания.

Устройство контроля цифровых узлов работает следующим образом.

Центральный процессор 12 через модуль 15 управления считыванием с перфоленты загружает в модуль 13 оперативного запоминающего устройства прграмму контроля, массип эталонных данных и массив тест-слов. После пуска программы она выводит оператору через модуль 14 управления дисплеем сообщение об очередности подключения блоков 2 и 5 приэлементной ялектрони- ки к разъемам объекта контроля и вы10

15

25

ходит в режим ожидания, который прекращается оператором подачей команды продолжения работы после выполнения им необходимых ручных операций, в данном случае после подстыковки блоков 2 и 5 к разъемам объекта контроля, указанным в сообщения опе ратору. Блоки приэлементной электроники 2 и 5 подключаются к двум разъемам объекта контроля (прибора с проводным монтажом) . Центральный процессор 12 передает по канальной шине 7 на блок 5 тест-слово, содержащее О в младшем разряде и 1 во всех остальных разрядах. Блок 5 приэлементной электроники пересыпает указанное тест-слово на объект контроля. При этом на всех контактах объекта контроля, имеющих гальваническую связь с 20 контактом, на который с помощью - : тест-слова задан О, появляется потенциал О, который будет держаться на этих контактах до тех пор, пока в блоке 5 сохраняется заданное тест- слово. Центральный процессор 12 считывает последовательно состояние подключенных разъемов объекта контроля и пересьтает шестнадцатиразрядные слова на блок 4 идентификации нулей. Информация, которую центральный процессор 12считывает затем с блока 4, представляет собой коды номеров разрядов (номеров контактов разъема объекта контроля), содержа- щих О. Цосле того, как будут считаны полностью состояния подключенньгх разъемов объекта контроля на блок 4, а также окончании считывания блока 4 ;В модуле 13 оперативного запомина- дд ющего устройства накопится информация о фактически существующих связях между контактом разъема объекта контре- ля, на который подан О, и другими контактами разъемов, к которым подключены блоки 2и 5 приэлементной электроники. По окончании считывания центральным процессором 12 информации с блока 4 идентификации нулей завер- щается опрос реакции объекта контроля на заданное тест-слово

Центральный процессор 12 пересылает на объект контроля очередное тест-слово, в котором О содержится в следующем разряде, и цикл работы повторяется вновь.

30

45

50

55

Окончанием работы устройства при данном варианте подключения объекта

10

5

5

20 д

0

5

0

5

контроля является окончание опроса реакции объекта контроля на тест-слово, содержащее О в старшем разряде. Алгоритм работы представлен на фиг. 9-11. После этого оператор в соответствии с заданной очередностью перестыковывает блок 2 приэлементной электроники на следующий разъем объекта контроля и вьщается полный цикл работы х перебором всех вышеуказанных тест-слов. Затем блок 5 приэлементной электроники перестыковывается на второй разъем объекта контроля, а блок 2 приэлементной электроники - последовательно на. 3, 4 и т.д. разъемы. Полное считывание фактически существующего монтажа объекта контроля будет завершего после подстыковки блока 5 к предпоследнему, а блока 4 - к последнему разъемам объекта контроля. По окончании полного считывания в модуле 13 оперативного запоминающего устройства накопится информация о фактически существующем монтаже объекта контроля. Центральный процессор 12 преобразует полученный массив данных в вид, удобный для его сравнения с эталонным ; . массивом, и затем производит сравнение.

Несравнивщиеся позиции массивов выводятся для документирования на печать с соответствующими признаками: обрыв или лишняя связь через модуль 16 управления устройством вывода на печать.

Формула изо.бретения

Устройство контроля цифровых уз- ;- лов, содержащее программный вычислительный блок, блок формирования канала, блок местного управления, отличаю.щееся твм, что, с целью расширения области примене . ния, в него введены первый и второй блоки приэлементной электроники, блок идентификации нулей и канальная щина, первые входы-выходы программного вычислительного блока, первого и второго блоков приэлементной электроники, блока формировАния канала, блока идентификации нулей, блока местного управления соединены с канальной щиной, первый, второй, . третий и четвертый выходы блока мест- ного управления соединены соответственно с вторыми гзходпми блока формнропания канала, вторым блоком прнэлементной электроники, первым блоком приэлемеитной электроники и блоком идентификации нулей, вторые

выходы программного вычислительного блока, первого и второго блокоп при- элементной электроники и блока формирования канала соединены с клеммами . для подключения объекта контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля цифровых узлов | 1989 |

|

SU1661690A2 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

Изобретение относится к .вычислительной технике и может быть использовано для контроля цифровых узлов, блоков и устройств. Цель изобретения - расширение области применения устройства для контроля цифровых узлов путем обеспечения возможности проводимого монтажа прибо- ров, секций. Устройство подключается к разъемам объекта контроля через блоки приэлементной электроники КоЪъекту (БПЭ) 5. Программный вычислительный блок 1 передает по канальной шине 7 на БПЭ 5 тест-слово, которое передается на объект контроля. Через БПЭ 5 и узел 3 формирования канала с разъемов объекта контроля снимается реак1щя на воздействие тест-слова, обрабатывается в блоке 4 идентификации нулей и запоминается в памяти программного вычислительного блока 1. Вся работа по передаче и приему тест-слов осуществляется под управлением блока 6 местного управления, который синхронизирует работу устройства. По мере накопления информации на реакцию всех возможных тест-слов программный вычислительный блок 1 обрабатывает ее и сравнивает с хранящимся в памяти эталонным массивом связей. Несравнившиеся порции массивов выводятся для документирования на печать. 11 ил. В (Л

0U8 2

/

5

77

Фиг. 6

A2

Звтсат код мегп- миепибчзел i3 (ОЗУ)

г-вгСчитать с узла 3 пердое id-дйзряд- ное ело 00

г-сг- Передать слобо но узел 5

П.

Шташьсцзлабкод номера контактд,, веющего Н1/яеоои потенциа/

.Е2.

Записать коВтме- ра нонтактимею- ш,егош/леойи потек и.иал,дузел13

4Р Фиг.10

Фиаз

Каждйшрщрд ста nqcmao/isH бсоотоежтт конткту KQHifh лируемого - разъема

Фиг.Ц AL

Wt HOMeuuS тткюоо.имею- шдк единичный потенииал.дзел 5недыдает

HP т - чип/от

с узла 2 шон(ено

С цттьсузлй 5слеоуюш ие i6 разрядоо тст-слооа

Ф1/г.Ё

сг

Нет

Фаа9

а

Редактор А, Лежнина

Составитель В. Драчев

Техред М.Ходанич Корректор М.Пожо

Заказ 6502/44

Тираж 772

ВНИИПИ Государстненного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Нет

D2

Нет

след1/юи ее тест-слобо

тз

Ff

Фа&.И

Подписное

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

| Г, 01 R 31/28, 1985. | |||

Авторы

Даты

1988-12-15—Публикация

1987-01-12—Подача