Изобретение относится к вычислительной технике и может быть исполь- зовано при построении систем измерения, управления и обработки данных в реальном масштабе времени на базе мини(микро) ЭВМ.э

Цель изобретения - повышение пропускной способности устройства и расширение класса решаемых задач.

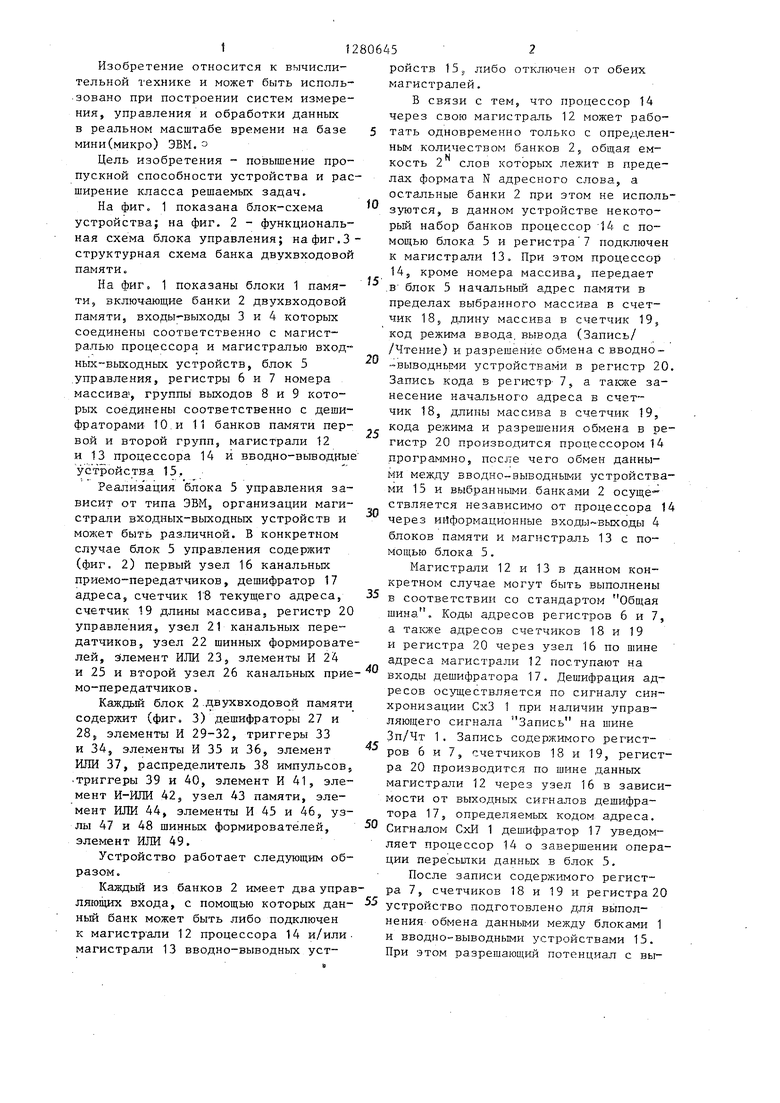

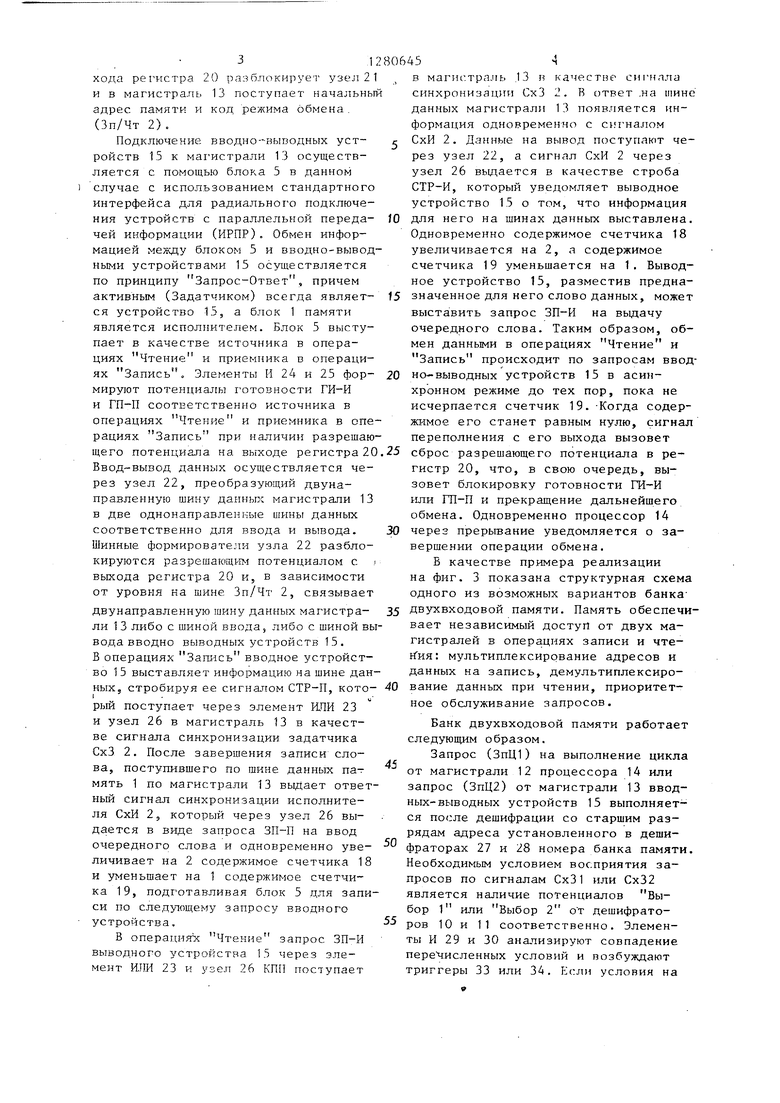

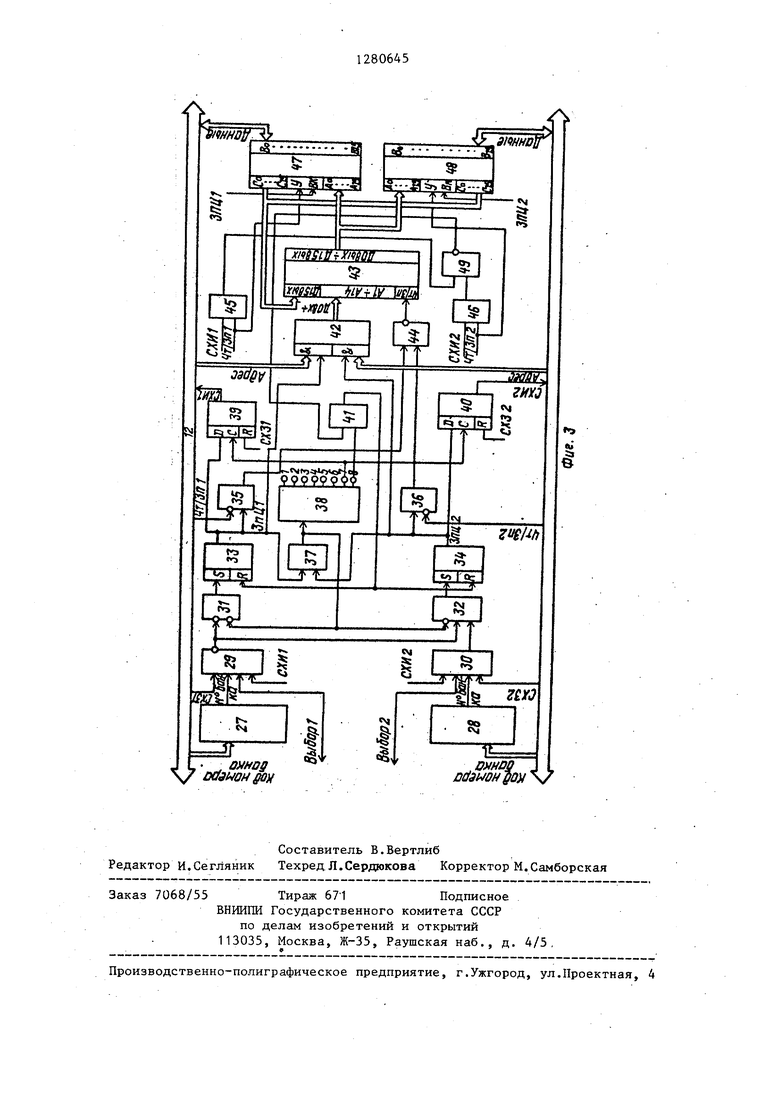

На фиг. 1 показана блок-схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг.3- структурная схема банка двухвкодовой памяти.

На фиг. 1 показаны блоки 1 памяти, включ-ающие банки 2 двухвходовой памяти, входы-выходы 3 и 4 которых соединены соответственно с магистралью процессора и магистралью входных-выходных устройств, блок 5 .управления, регистры 6 и 7 номера массива , группы выходов 8 и 9 которых соединены соответственно с дешифраторами 10.и 11 банков памяти первой и второй групп, магистрали 12 и 13 процессора 14 и вводно-выводрые устройства 15..

Реализ ация блока 5 управления зависит от типа ЭВМ, организации магистрали входных-выходных устройств и может быть различной. В конкретном случае блок 5 управления содержит (фиг. 2) первый узел 16 канальных приемо-передатчиков, дешифратор 17 адреса, счетчик 18 текущего адреса, счетчик 19 длины массива, регистр 20 управления, узел 21 канальных передатчиков, узел 22 шинных формирователей, з лемент ИЛИ 23э элементы И 24

10

15

ройств 15, либо отключен от обеих магистралей.

В связи с тем, что процессор 14 через свою магистраль 12 может работать одновременно только с определенным количеством банков 2. общая емN

КОСТЬ 2 слов которых лежит в пределах формата N адресного слова, а остальные банки 2 при этом не исполь зуются, в данном устройстве некото- рьй набор банков процессор 14с помощью блока 5 и регистра 7 подключен к магистрали 13, При этом процессор 14, кроме номера массива, передает

20

25

В блок 5 начальный адрес памяти в пределах выбранного массива в счетчик 18, длину массива в счетчик 19, код режима ввода, вывода (Запись/ /Чтение) и разрешение обмена с вводно- -выводными устройствами в регистр 20 Запись кода в регистр 7, а Taicuce занесение нач-ального адреса в счетчик 18, длины массива в счетчик 19, кода режима и разрешения обмена в ре гистр 20 производится процессором 14 программно, после чего обмен данными между вводно-выводньшн устройства ми 15 и выбранными банками 2 осуще ствляется независимо от процессора 1 через информационные вход1з1 выхо,цы 4 блоков памяти и магистраль 13 с помощью блока 5.

Магистрали 12 и 13 в данном конкретном случае могут быть выполнены в соответствии со стан.дартом Общая шина. Коды адресов регистров 6 и 7, а также адресов счетчиков 18 и 19 и регистра 20 через узел 16 по шине адреса магистрали 12 поступают на

30

4П

и 25 и второй узел 26 канальных прие- входы дешифратора 17. Дешифрация адресов осуществляется по сигналу синхронизации СхЗ 1 при наличии управ45

МО-передатчиков.

Каждьй блок 2 .двухвходовой памяти содержит (фиг. 3) дешифраторы 27 и 28, элементы И 29-32, триггеры 33 и 34, элементы И 35 и 36, элемент ИЛИ 37, распределитель 38 импульсов, триггеры 39 и 40, элемент И 41, элемент И-ИЛИ 42, узел 43 памяти, элемент ИЛИ 44, элементы И 45 и 46, узлы 47 и 48 шинных формирователей, элемент ИЛИ 49.

Устройство работает следующим образом.

Казкдый из банков 2 имеет два управляющих входа, с помощью которых дан- 55 ный банк может быть либо подключен к магистр-али 12 процессора 14 и/или. магистрали 13 вводно-выводных уст50

1

ляющего сигнала Запись на шине Зп/Чт 1. Запись содержимого регистров 6 и 7, счетчиков 18 и 19, регистра 20 производится по шине данных магистрали 12 через узел 16 в зависимости от выходнь х сигналов дешифратора 17, определяемых кодом адреса. Сигналом СхИ 1 дешифратор 17 уведомляет процессор 14 о завершении операции пересылки данных в блок 5,

После записи содержимого регистра 7 , счетчиков 18 и 19 и регистра 20 устройство подготовлено для выполнения обмена данньми между блоками 1 и вводно-выводными устройствами 15. Лри этом разрешающий потенциал с вы

5

ройств 15, либо отключен от обеих магистралей.

В связи с тем, что процессор 14 через свою магистраль 12 может работать одновременно только с определенным количеством банков 2. общая емN

КОСТЬ 2 слов которых лежит в пределах формата N адресного слова, а остальные банки 2 при этом не используются, в данном устройстве некото- рьй набор банков процессор 14с помощью блока 5 и регистра 7 подключен к магистрали 13, При этом процессор 14, кроме номера массива, передает

0

5

В блок 5 начальный адрес памяти в пределах выбранного массива в счетчик 18, длину массива в счетчик 19, код режима ввода, вывода (Запись/ /Чтение) и разрешение обмена с вводно- -выводными устройствами в регистр 20. Запись кода в регистр 7, а Taicuce занесение нач-ального адреса в счетчик 18, длины массива в счетчик 19, кода режима и разрешения обмена в регистр 20 производится процессором 14 программно, после чего обмен данными между вводно-выводньшн устройствами 15 и выбранными банками 2 осуще ствляется независимо от процессора 14 через информационные вход1з1 выхо,цы 4 блоков памяти и магистраль 13 с помощью блока 5.

Магистрали 12 и 13 в данном конкретном случае могут быть выполнены в соответствии со стан.дартом Общая шина. Коды адресов регистров 6 и 7, а также адресов счетчиков 18 и 19 и регистра 20 через узел 16 по шине адреса магистрали 12 поступают на

0

П

входы дешифратора 17. Дешифрация адресов осуществляется по сигналу синхронизации СхЗ 1 при наличии управ45

55

50

1

ляющего сигнала Запись на шине Зп/Чт 1. Запись содержимого регистров 6 и 7, счетчиков 18 и 19, регистра 20 производится по шине данных магистрали 12 через узел 16 в зависимости от выходнь х сигналов дешифратора 17, определяемых кодом адреса. Сигналом СхИ 1 дешифратор 17 уведомляет процессор 14 о завершении операции пересылки данных в блок 5,

После записи содержимого регистра 7 , счетчиков 18 и 19 и регистра 20 устройство подготовлено для выполнения обмена данньми между блоками 1 и вводно-выводными устройствами 15. Лри этом разрешающий потенциал с вы312

хода регистра 20 разблокирует узел 2 1 и в магистраль 13 поступает начальный адрес памяти и код режима обмена. (Зп/Чт 2),

Подключение вводно- выводных устройств 15 к магистрали 13 осуществляется с помощью блока 5 в данном случае с использованием стандартного интерфейса для радиального подключения устройств с параллельной передачей информации (ИРПР). Обмен информацией между блоком 5 и вводно-вывод- ными устройствами 15 осуществляется по принципу Запрос-Ответ, причем активнь м (Задатчиком) всегда является устройство 15, а блок 1 памяти является исполнителем. Блок 5 выступает в качестве источника в операциях Чтение и приемника в операциях Запись. Элементы И 24 и 25 формируют потенциалы готовности ГИ-И и ГП-П соответственно источника в операциях Чтение и приемника в операциях Запись при наличии разрешающего потенциала на выходе регистра 20 Ввод-вывод данных осуществляется через узел 22, преобразующий двунаправленную шину данных магистрали 13 в две однонаправленные шины данных соответственно для ввода и вывода. Шинные формирователи узла 22 разблокируются разрешающ гм потенциалом с ) выхода регистра 20 и, в зависимости от уровня на шине Зп/Чт 2, связывает двунаправленную шину данных магистрали 13 либо с шиной ввода, либо с шиной вывода вводно выводных устройств 15. В операциях Запись вводное устройство 15 выставляет информацию на шине данных, стробируя ее сигналом СТР-П, который поступает через элемент ИЛИ 23 и узел 26 в магистраль 13 в качестве сигнала синхронизации задатчика СхЗ 2. После завершения записи слова, поступившего по шине данных память 1 по магистрали 13 выдает ответный сигнал синхронизации исполнителя СхИ 2, который через узел 26 выдается в виде запроса ЗП-П на ввод очередного слова и одновременно увеличивает на 2 содержимое счетчика 18 и уменьшает на 1 содержимое счетчика 19, подготавливая блок 5 для записи по следующему запросу вводного устройства,

В операция Чтение запрос ЗП-И выводного устройства 15 через элемент ШШ 23 и узел 26 КПП поступает

06454

в магистраль .13 н качестве сигнала синхронизации СхЗ 2. В .на тине данных магистрали 13 появляется информация одновременно с сигналом г СхИ 2. Данные на вывод поступают через узел 22, а сигнал СхИ 2 через узел 26 выдается в качестве строба СТР-И, который уведомляет выводное устройство 15 о том, что информация

для него на шинах данных выставлена. Одновременно содержимое счетчика 18 увеличивается на 2, а содержимое счетчика 19 уменьшается на 1. Выводное устройство 15, разместив предна5 значенное для него слово данных, может выставить запрос ЗП-И на выдачу очередного слова. Таким образом, обмен данными в операциях Чтение и Запись происходит по запросам ввод0 но-выводных устройств 15 в асинхронном режиме до тех пор, пока не исчерпается счетчик 19. -Когда содержимое его станет равным нулю, сигнал переполнения с его выхода вызовет

5 сброс разрешающего потенциала в регистр 20, что, в свою очередь, вызовет блокировку готовности ГИ-И или ГП-П и прекращение дальнейшего обмена. Одновременно процессор 14

0 через прерывание уведомляется о завершении операции обмена.

В качестве примера реализации на фиг. 3 показана структурная схема одного из возможных вариантов банка

5 двухвходовой памяти. Память обеспечивает независимый доступ от двух магистралей в операциях записи и чте- нГия: мультиплексирование адресов и данных на запись, демультиплексиро0 вание данных при чтении, приоритетное обслуживание запросов.

Банк двухвходовой памяти работает следующим образом.

Запрос (ЗпЦ1) на выполнение цикла от магистрали 12 процессора 14 или запрос (ЗпЦ2) от магистрали 13 вводных-выводных устройств 15 выполняется после дешифрации со старшим разрядам адреса установленного в дешифраторах 27 и 28 номера банка памяти. Необходимым условием восприятия запросов по сигналам СхЗ1 или Сх32 является наличие потенциалов Выбор 1 или Выбор 2 от дешифрато- ров 10 и 11 соответственно. Элементы И 29 и 30 анализируют совпадение пере численных условий и возбуждают триггеры 33 или 34. Если условия на

5

0

иыпо.чненяе запросов возникают от двух магистралей одновременно, элементы И 31 и 32 обеспечивают более высокий приоритет в данном случае запросу от магистрали 12 процессора 14. Возбужденный запрос ЗпЦ1 или ЗпЦ2 поступает на элемент И-ШМ «42 и подключает к адресному входу узла 43 шину адреса магистрали 12 или 13 и одновременно через элемент ИЛИ 37 запускает распределитель 38, обеспечивающий требуемую тактировку работы узла 43, Распределитель формирует на выходах 1-8 перепад потенциалов, существующих на каждом выходе до снятия запроса ЗпЦ1 или ЗпЦ2 на выходе, причем величина интервала между возбуждением запроса и формированием перепада потенциалов на каждом выходе различная. В зависимости от типа применяемого узл 43 памяти используются со- отБетст ующие выходы распределителя 38. Общим для всех типов памяти является выдача в конце цикла синхроподключение (Замещение) .комбинаций банков памяти поочередно к процессору и вводным-выводным устройством; достигается строгая регулярность обмена данными с объектом измерения (управления), определяемая только объектом, формирующим запросы на обмен, независимо от процессора.

Ш

5

20

Формула изобретения

Устройство для сопряжения многоблочной памяти с процессором и ввод- но-выводными устройствами, содержащее первый узел канальных приемо-передат- чиков, первый вход-выход которого соединен с магистралью процессора, группа выходов соединена с группой входов дешифратора адреса, а вход и выход - соединены соответственно, с первым выходом дешифратора адреса и информационным входом первого регистра номера массива, управляющий вход которого подключен ко второму выходу дешифратора адреса, а группа

визирующих импульсов СхИ1, СхИ2 в со- 25 доходов - к входам дешифраторов бан- ответствующую магистраль с выходом ков данных первой группы, выходы ко- триггеров 39 и 40 и снятие текущего торых соединены с первыми входами вы- запроса ЗпЦ1 или ЗпЦ2. Снятие запро- борки банка многоблочной памяти.

сов в операциях Запись происходит в конце цикла, а в операциях Чтение - после снятия соответствующего СхИ (СхИ1 или СхИ2). Этот алгоритм реализует элементы И 41, 45, 46. Шинные формирователи узлов 47 и 48 осуществляют подключение двунаправленной шины данных магистралей 12 и 13 к выходной шине данных узла 43 в операциях Чтение и выходной шине данных.узла 43 в операциях Запись. Управление шинньми формирователями узлов 47 и 48 производится сигналами ЗпЦ1, ЗпЦ2, Чт/3п1, Чт/3п2.

Таким образом, устройство обеспечивает прямой доступ к многоблочной памяти со стороны вводно/выводных устройств с автономным от процессора выполнением операций передачи дан- к.ых. Это позволяет более гибко использовать многоблочную память объема, превышающего адресный формат процессора; повысить по сравнению с известным устройством скорость обмена информацией между памятью, процессором и вводно-выводными устройствами.за счет одновременного выполнения операций передачи данных по обеим магистралям; осуи естплять по мере готовности массивов быстрое .

30

отличающееся тем, что, с целью повышения пропусной способности устройства, в него введены второй регистр номера массива, вторая группа дешифраторов банков данных, второй узел канальных приемо-передат35 чиков, узел канальных передатчиков, счетчик длины массива, регистр управления, счетчик адреса, два элемента И, элемент ИЛИ и узел шинных формирователей, причем информационные

входы регистра управления, счетчика адреса и счетчика длины массива соединены с выходом первого узла канальных приемо-передатчиков и информационным входом-второго регистра номера массива, группа выходов которого соединена с входами дешифраторов банков данных второй группы, выходы которых соединены с вторыми входами выборки банка многоблочной памяти, управляю50 щий вход второго регистра номера массива соединен с третьим выходом дешифратора адреса, четвертый, пятый и шестой выходы которого подключены соответственно, к управляющим входам

55 счетчика адреса, счетчика длины мае- сива и регистра управления, первый разрядный выход которого соединен с разрешающими входами узла каналь45

06456

подключение (Замещение) .комбинаций банков памяти поочередно к процессору и вводным-выводным устройством; достигается строгая регулярность обмена данными с объектом измерения (управления), определяемая только объектом, формирующим запросы на обмен, независимо от процессора.

Формула изобретения

Устройство для сопряжения многоблочной памяти с процессором и ввод- но-выводными устройствами, содержащее первый узел канальных приемо-передат- чиков, первый вход-выход которого соединен с магистралью процессора, группа выходов соединена с группой входов дешифратора адреса, а вход и выход - соединены соответственно, с первым выходом дешифратора адреса и информационным входом первого регистра номера массива, управляющий вход которого подключен ко второму выходу дешифратора адреса, а группа

доходов - к входам дешифраторов бан- ков данных первой группы, выходы ко- торых соединены с первыми входами вы- борки банка многоблочной памяти.

отличающееся тем, что, с целью повышения пропусной способости устройства, в него введены второй регистр номера массива, вторая группа дешифраторов банков данных, второй узел канальных приемо-передатчиков, узел канальных передатчиков, счетчик длины массива, регистр управения, счетчик адреса, два элемента И, элемент ИЛИ и узел шинных формирователей, причем информационные

входы регистра управления, счетчика адреса и счетчика длины массива соединены с выходом первого узла канальных приемо-передатчиков и информационным входом-второго регистра номера массива, группа выходов которого соединена с входами дешифраторов банков данных второй группы, выходы которых соединены с вторыми входами выборки банка многоблочной памяти, управляющий вход второго регистра номера массива соединен с третьим выходом дешифратора адреса, четвертый, пятый и шестой выходы которого подключены соответственно, к управляющим входам

счетчика адреса, счетчика длины мае- сива и регистра управления, первый разрядный выход которого соединен с разрешающими входами узла каналь

ных передатчиков, узла шинных формирователей, первым входом первого и прямым входом второго элементов И и является входом сигнала прерывания процессора, второй выход .регистра управления соединен с первым информационным входом узла канальных передатчиков, вторым входом первого элемента И, инверсным входом второго элемента И и входом задания направления обмена узла шинных формирователей, вход сброса регистра управления соединен с выходом переполнения счетчика длины массива, вычитающий вход которого соединен с первым выходом второго узла канальных приемопередатчиков, входами синхронизации ввода и вывода вводно-выводных устройств и суммирующим входом счетчика адреса, выход которого соединен с вторым информационным входом узла канальных передатчиков, первый и второй выходы которого, входгвыход узла шинных формирователей и второй выход и первый вход второго узла канальных

приемо-передатчиков соединены через магистраль вводно-выводных устройств с соответствующими входами-выходами многоблочной памяти, второй вхйд второго узла канальных -приемо-передатчиков соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами синхронизации ввода и вьгаода вводно-выводных устройств, выходы первого и

второго элементов И и выход и информационный вход узла шинных формирователей соединены соответственно с входами сигналов готовности вывода и ввода, информационными входами и

информационными выходами вводно-выводных устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Устройство сопряжения процессора с многоблочной памятью | 1989 |

|

SU1702383A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении систем измерения, управления и обработки данных в реальном масштабе времени на базе мини(микро) ЭВМ. Целью изобретения является повышение пропускной способности устройства 1 и расширение класса решаемых задач. Устройство содержит блоки 1 памяти, включающие :банки 2. двухвходовой памяти, входы- выходы 3,4 которых соединены соответ- CTBetJHo с магистралью процессора и магистралью входных-выходных устройств, блок 5 управления, регистры 6, 7 номера массива, группы выходов 8,9 которых соединены соответственно с дешифраторами 10, 11 банков памяти первой и второй групп, магистрали 12, 13 процессора 14 и вводно- выводные устройства 15. Устройство обеспечивает прямой доступ к многоблочной памяти со стороны вводно-выт водных устройств с автономным от процессора выполнением операций передачи данных. Это позволяет более гибко использовать многоблочную память объема, превьш1ающего адресный .формат процессора. 3 ил. I (Л

. прерывания программ процессора

«б

ftq

l

В регистр 6 В регистр 7

Фик.2

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1984-12-03—Подача