4j

со

Изобретение относится к области втоматики и вычислительной техники и может быть использовано при технической диагностике дискретных объ- актов. .

Целью изобретения является повышение- быстродействия устройства.

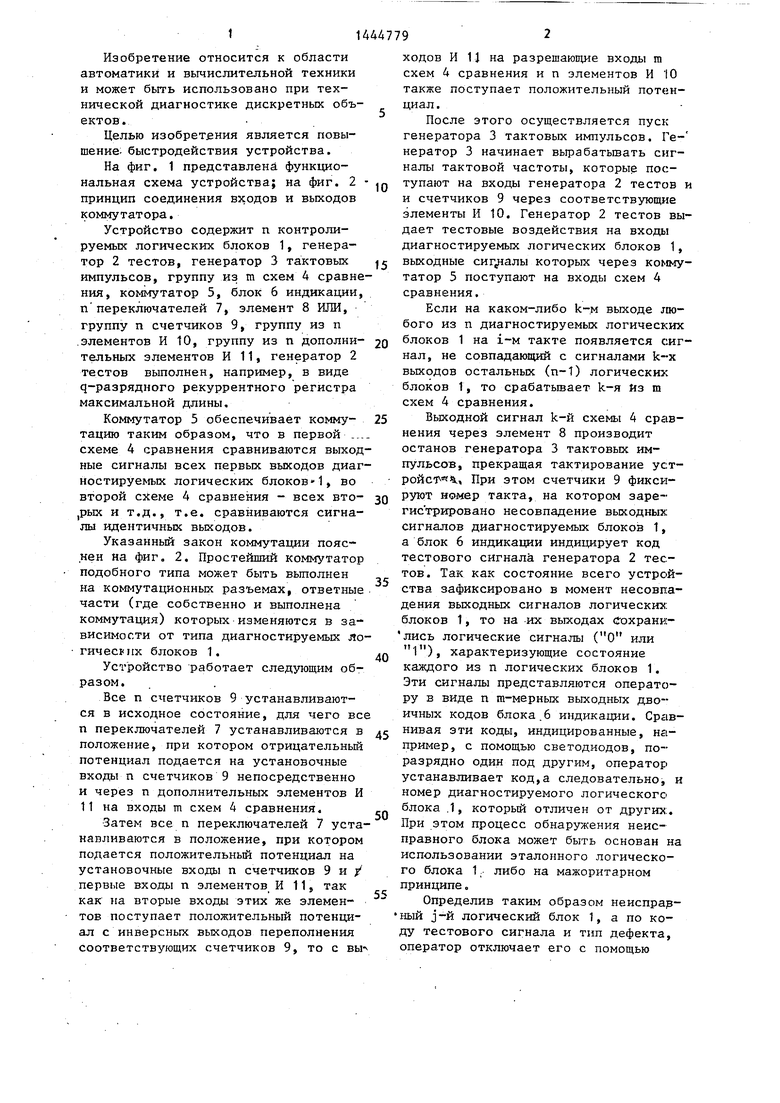

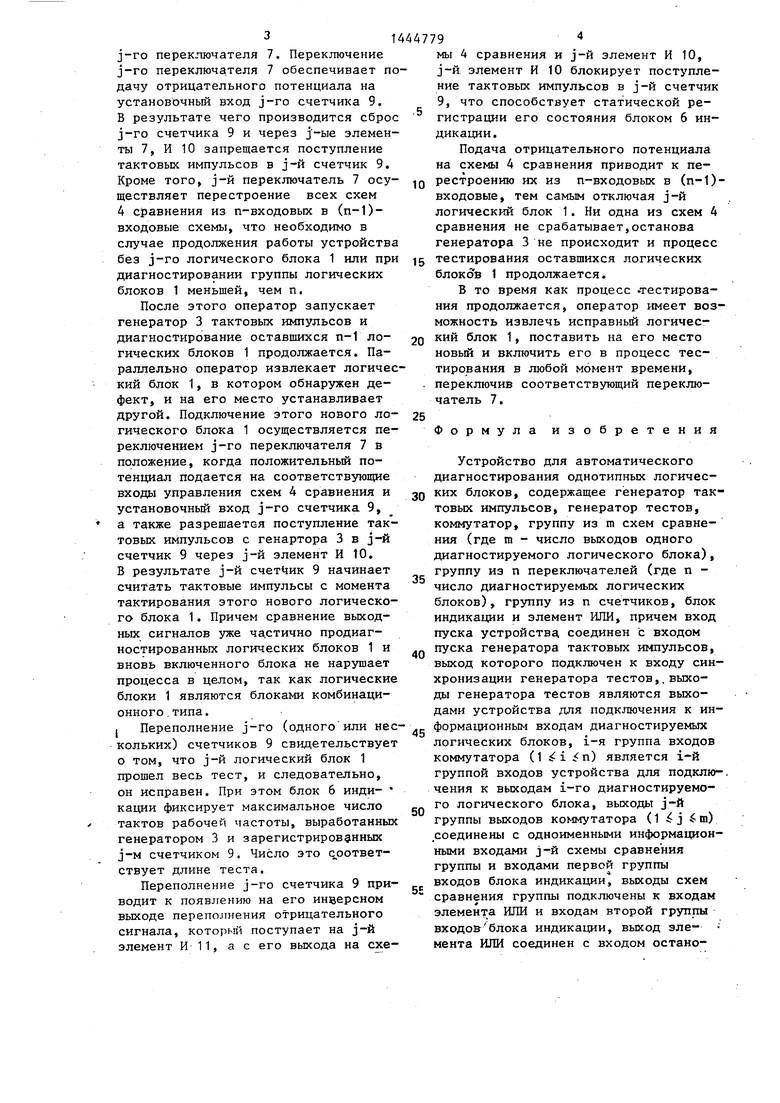

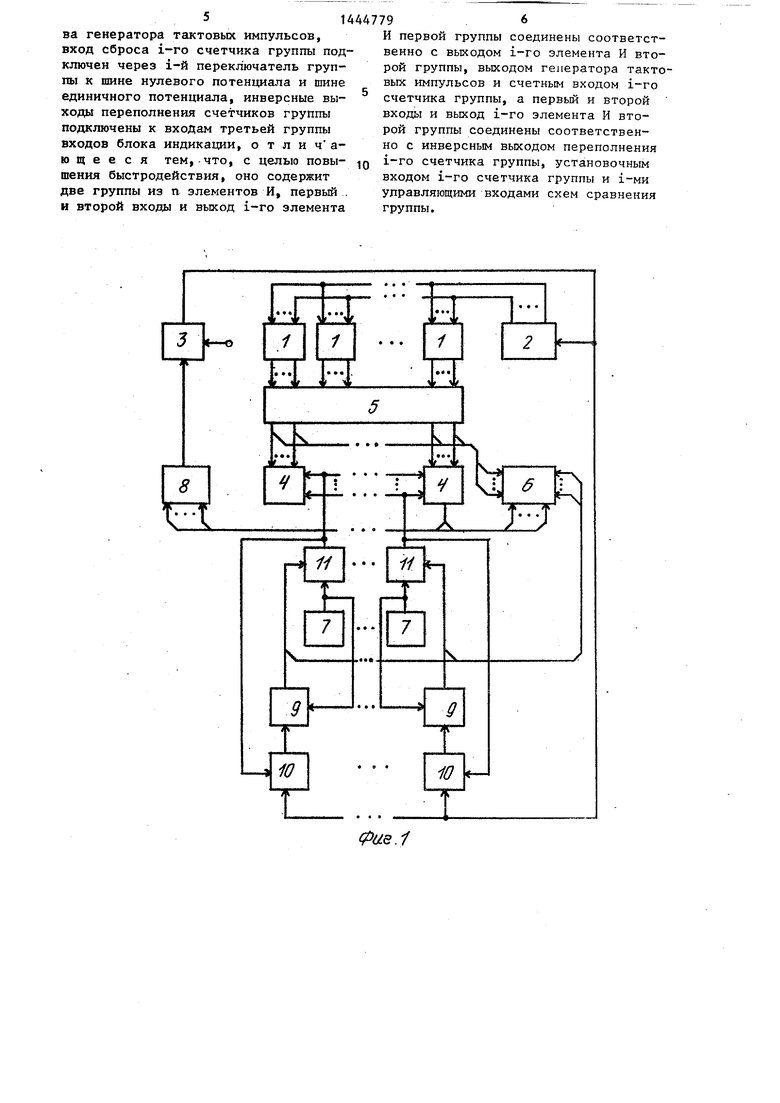

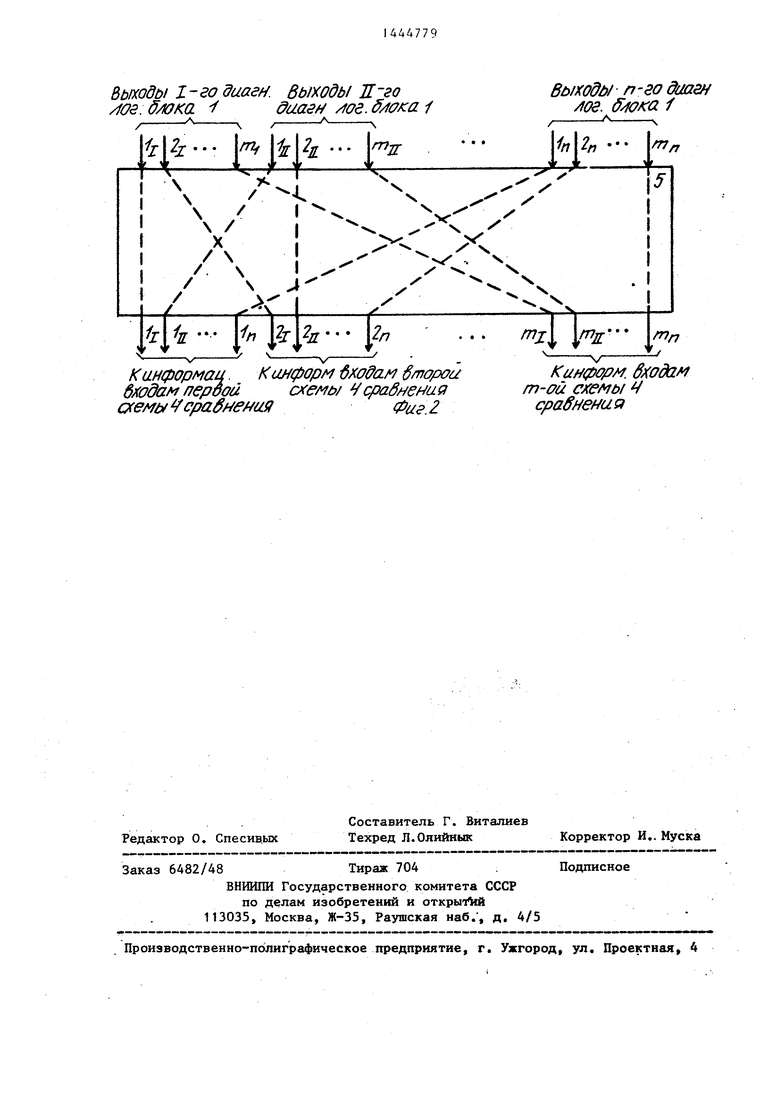

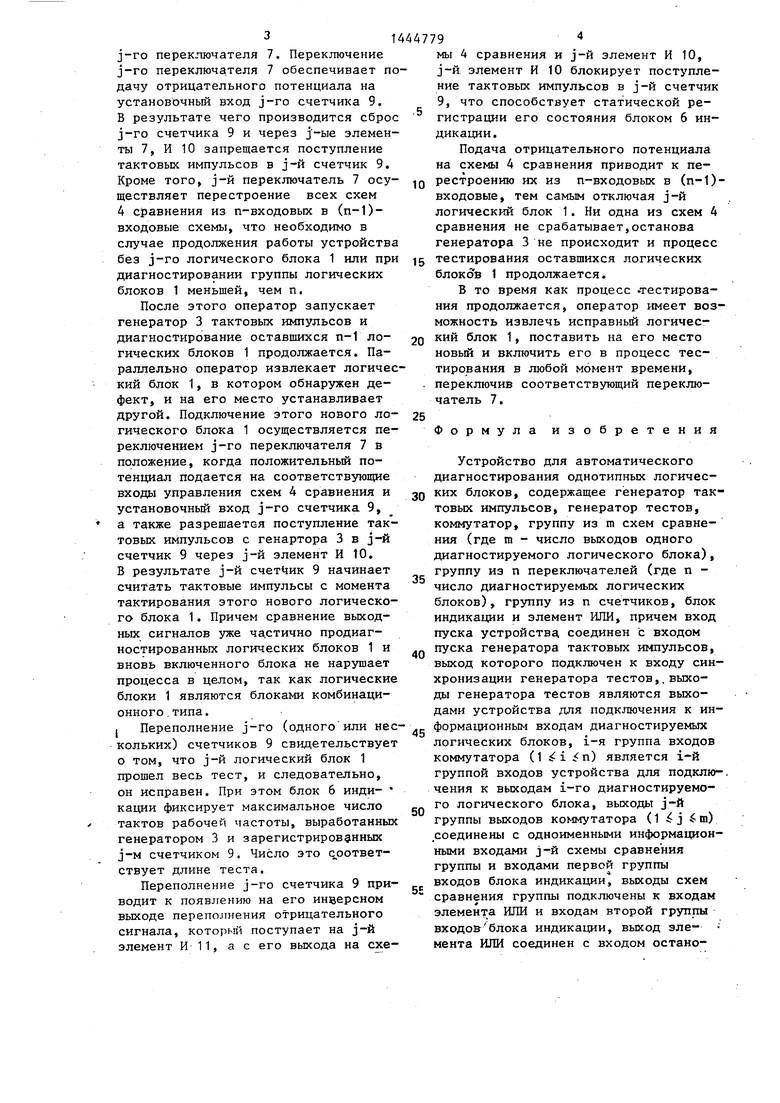

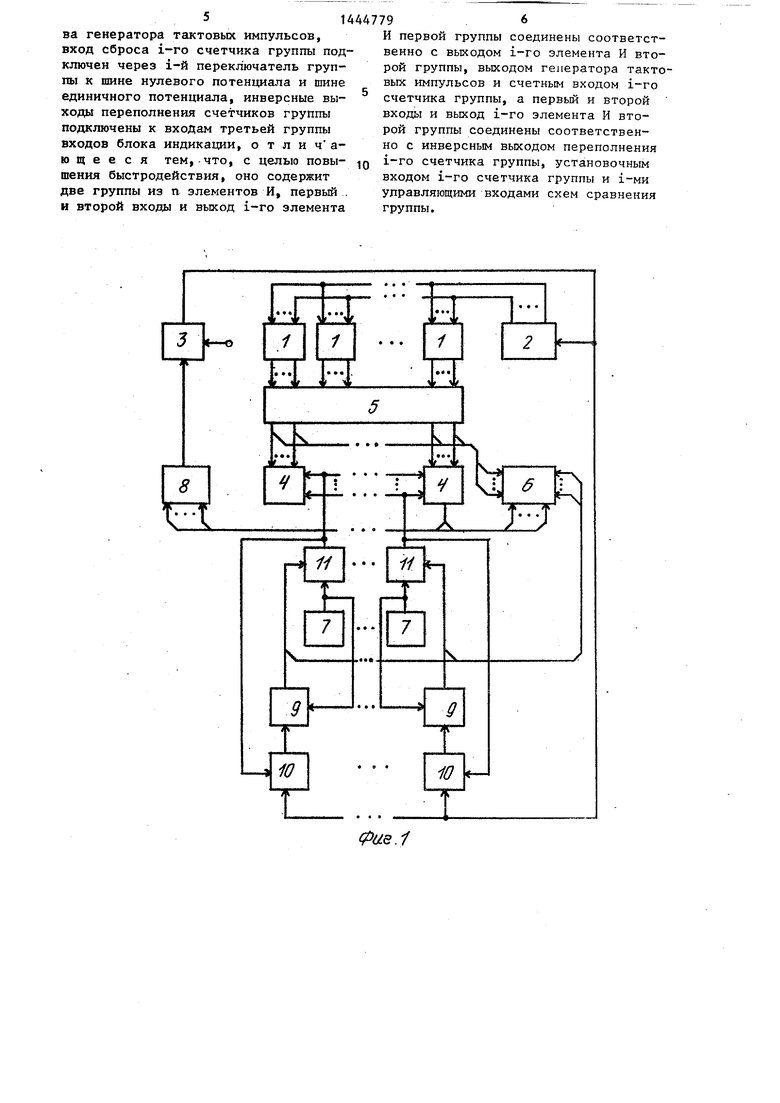

На фиг. 1 представлен функциональная схема устройства; на фиг. 2 - Q принцип соединения входов и выходов коммутатора.

Устройство содержит п контролируемых логических блоков 1, генератор 2 тестов, генератор 3 тактовых импульсов, группу из m схем 4 сравнения, коммутатор 5, блок 6 индикации, п переключателей 7, элемент 8 ИЛИ, группу п счетчиков 9, группу из п элементов И 10, группу из п дополни- 20 тельных элементов И 11, генератор 2 тестов выполнен, например, в виде q-разрядного рекуррентного регистра максимальной длины.

Коммутатор 5 обеспечивает комму- 25

тацию таким образом, что в первой

схеме 4 сравнения сравниваются выходные сигналы всех первых выходов диагностируемых логических блоков 1, во второй схеме 4 сравнения - всех вто- зО рых и т.д., т.е. сравниваются сигналы идентичных выходов.

Указанный закон коммутации пояснен на фиг. 2. Простейший коммутатор подобного типа может быть выполнен на коммутационных разъемах, ответные части (где собственно и выполнена коммутация) которых изменяются в за- висимости от типа диагностируемых Ло- гичесгих блоков 1.4Q

Устройство работает следующим образом.

Все п счетчиков 9 устанавливаются в исходное состояние, для чего все п переключателей 7 устанавливаются в 45 положение, при котором отрицательный потенциал подается на установочные входы п счетчиков 9 непосредственно и через п дополнительных элементов И 11 на входы m схем 4 сравнения. -п

Затем все п переключателей 7 устанавливаются в положение, при котором подается положительный потенциал на установочные входы п счетчиков 9 и У первые входы п элементов И 11, так как на вторые входы этих же элементов поступает положительный потенциал с инверсных выходов переполнения соответствующих счетчиков 9, то с вы

35

55

0

5

О

Q

5 п

5

5

ходов и 1J на разрешающие входы m схем 4 сравнения и п элементов И 10 также поступает положительный потенциал .

После этого осуществляется пуск генератора 3 тактовых импульсов. Ге- нератор 3 начинает вьфабатьтать сигналы тактовой частоты, которые поступают на входы генератора 2 тестов и и счетчиков 9 через соответствующие элементы И 10. Генератор 2 тестов выдает тестовые воздействия на входы диагностируемых логических блоков 1, выходные которых через коммутатор 5 поступают на входы схем 4 сравнения.

Если на каком-либо k-м выходе JDO- бого из п диагностируемых логических блоков 1 на i-M такте появляется сигнал, не совпадающий с сигналами k-x выходов остальных (п-Т) логических блоков 1, то срабатьшает k-я из m схем 4 сравнения.

Выходной сигнал k-й схемы 4 сравнения через элемент 8 производит останов генератора 3 тактовых импульсов, прекращая тактирование уст- ройсТ ч, При этом счетчики 9 фиксируют номер такта, на котором заре- гис трировано несовпадение вькодных сигналов диагностируемых блоков 1, а блок 6 индикации индицирует код тестового сигнала генератора 2 тестов. Так как состояние всего устройства зафиксировано в момент несовпадения выходных сигналов логических: блоков 1, то на их выходах Сохранк- лись логические сигналы (О или 1), характеризующие состояние каждого из п логических блоков 1. Эти сигналы представляются оператору в виде п га-мерных выходных двоичных кодов блока.6 индикации. Сравнивая эти коды, индицированные, например, с помощью светодиодов, поразрядно один под другим, оператор устанавливает код,а следовательно, и номер диагностируемого логического блока .1, который отличен от других;. При этом процесс обнаружения неисправного блока может быть основан на использовании эталонного логического блока 1, либо на мажоритарном принципе.

Определив таким образом неиспрар- ный j-й логический блок 1, а по коду тестового сигнала и тип дефекта, оператор отключает его с помощью

j-го переключателя 7, Переключение j-ro переключателя 7 обеспечивает пдачу отрицательного потенциала на установочный вход j-ro счетчика 9. В результате чего производится сбро j-ro счетчика 9 и через j -ые элементы 7, И 10 запрещается поступление тактовых импульсов в j-й счетчик 9. Кроме того, j-й переключатель 7 осуществляет перестроение всех схем 4 сравнения из п-входовых в (п-1)- входовые схемы, что необходимо в случае продолжения работы устройства без j-ro логического блока 1 или при диагностировании группы логических блоков 1 меньшей, чем п.

После этого оператор запускает генератор 3 тактовых импульсов и диагностирование оставшихся п-Г логических блоков 1 продолжается. Параллельно оператор извлекает логический блок 1, в котором обнаружен дефект, и на его место устанавливает другой. Подключение этого нового логического блока 1 осуществляется переключением j-ro переключателя 7 в положение, когда положительный потенциал подается на соответствующие входы управления схем 4 сравнения и установочный вход j-ro счетчика 9, а также разрешается поступление тактовых импульсов с генартора 3 в j-й счетчик 9 через j-й элемент И tO, В результате j-й 9 начинает считать тактовые импульсы с момента тактирования этого нового логического блока 1. Причем сравнение выходных сигналов уже частично продиаг- ностированных логических блоков 1 и вновь включенного блока не нарушает процесса в целом, так как логические блоки 1 являются блоками комбинационного, типа.

J Переполнение j-ro (одного или нес кольких) счетчиков 9 свидетельствует о том, что j-й логический блок 1 прошел весь тест, и следовательно, он исправен. При этом блок 6 инди- кации фиксирует максимальное число тактов рабочей частоты, выработанных генератором 3 и зарегистрированных J-M счетчиком 9. Число это с оответ- ствует длине теста.

Переполнение j-ro счетчика 9 приводит к появлению на его инверсном выходе переполнения отрицательного сигнала, которьм поступает на j-й элемент И 11, а с его выхода на схе

0

5

0

5

мы 4 сравнения и j-й элемент И 10, j-й элемент И 10 блокирует поступление тактовых импульсов в j-й счетчик 9, что способствует статической регистрации его состояния блоком 6 индикации.

Подача отрицательного потенциала на схемы 4 сравнения приводит к перестроению их из п-входовых в (п-1)- входовые, тем самым отключая j-й логический блок 1. Ни одна из схем 4 сравнения не срабатывает,останова генератора 3 не происходит и процесс тестирования оставшихся логических блоко в 1 продолжается.

В то время как процесс «тестирования продолжается, оператор имеет возможность извлечь исправный логический блок 1, поставить на его место новый и включить его в процесс тестирования в любой момент времени, переключив соответствующий переключатель 7.

Формула изобретения

5

0

0

Устройство для автоматического диагностирования однотипных логичес- 0 ких блоков, содержащее генератор тактовых импульсов, генератор тестов, коммутатор, группу из m схем сравнения (где m - число выходов одного диагностируемого логического блока), группу из п переключателей (где п - число диагностируемых логических блоков), группу из п счетчиков, блок индикации и элемент ИЛИ, причем вход пуска устройства соединен с входом пуска генератора тактовых импульсов, выход которого подключен к входу синхронизации генератора тестов,, выходы генератора тестов являются выходами устройства для подключения к информационным входам диагностируемых логических блоков, i-я группа входов коммутатора (1 i п) является i-й группой входов устройства для подклю-. чения к выходам i-ro диагностируемого логического блока, выходы j-й группы выходов коммутатора (1 j ю) .соединены с одноименными информационными входами j-й схемы сравнения группы и входами первой группы входов блока индикации, выходы схем сравнения группы подключены к входам элемента ИЛИ и входам второй группы входов блока индикации, выход эле- - мента ИЛИ соединен с входом остано

ва генератора тактовых импульсов, вход сброса i-ro счетчика группы подключен через i-й переключатель группы к шине нулевого потенциала и шине единичного потенциала, инверсные выходы переполнения счетчиков группы подключены к входам третьей группы входов блока индикации, о т л и ч а- ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит две группы из п элементов И, первый . и второй входы и выход i-ro элемента

14447796

И первой группы соединены соответственно с выходом i-ro элемента И второй группы, выходом генератора тактовых импульсов и счетным входом i-ro счетчика группы, а первый и второй входы и выход i-ro элемента И второй группы соединены соответственно с инверсным выходом переполнения i-ro счетчика группы, установочным входом i-ro счетчика группы и i-ми управляющими входами схем сравнения группы.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического диагностирования группы однотипных логических блоков | 1987 |

|

SU1444778A1 |

| Устройство для непрерывного диагностирования однотипных логических блоков | 1984 |

|

SU1234840A1 |

| Устройство для поиска кратных дефектов в группе объектов | 1983 |

|

SU1233157A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для поиска кратных неисправностей в однотипных логических блоках | 1978 |

|

SU781816A1 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для обнаружения кратных дефектов в группе типовых элементов замены | 1983 |

|

SU1126966A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1674132A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при технической диагностике дискретных объектов. Целью изобретения является повышение быстродействия устройства. С этой целью в устройство, содержащее генератор тактовых импульсов, генератор тестов, коммутатор, группу схем сравнения, группу переключателей, группу счетчиков, блок индикации и элемент ИЛИ, введены две группы элементов ИЛИ. 2 ил. с S

Фаз.1

BbiKOdbi I-годиагн. Bbiwdbi Ж-го /fO3: д/юка -/daadf /foe. /

pz--

Канформаи. Кинформ м&ам второй бходам/7epoGd о(емь/ аемь/ сраб е/ ияФиг 2

Bi ixodi / п-го даагн /loe. . /

№ - h

xт fКинформ. входа f т-ой схемы срабнеиаа

| Устройство для поиска кратных неисправностей в однотипных логических блоках | 1978 |

|

SU781816A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля типовыхэлЕМЕНТОВ зАМЕНы | 1979 |

|

SU832557A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для непрерывного диагностирования однотипных логических блоков | 1984 |

|

SU1234840A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-02-04—Подача