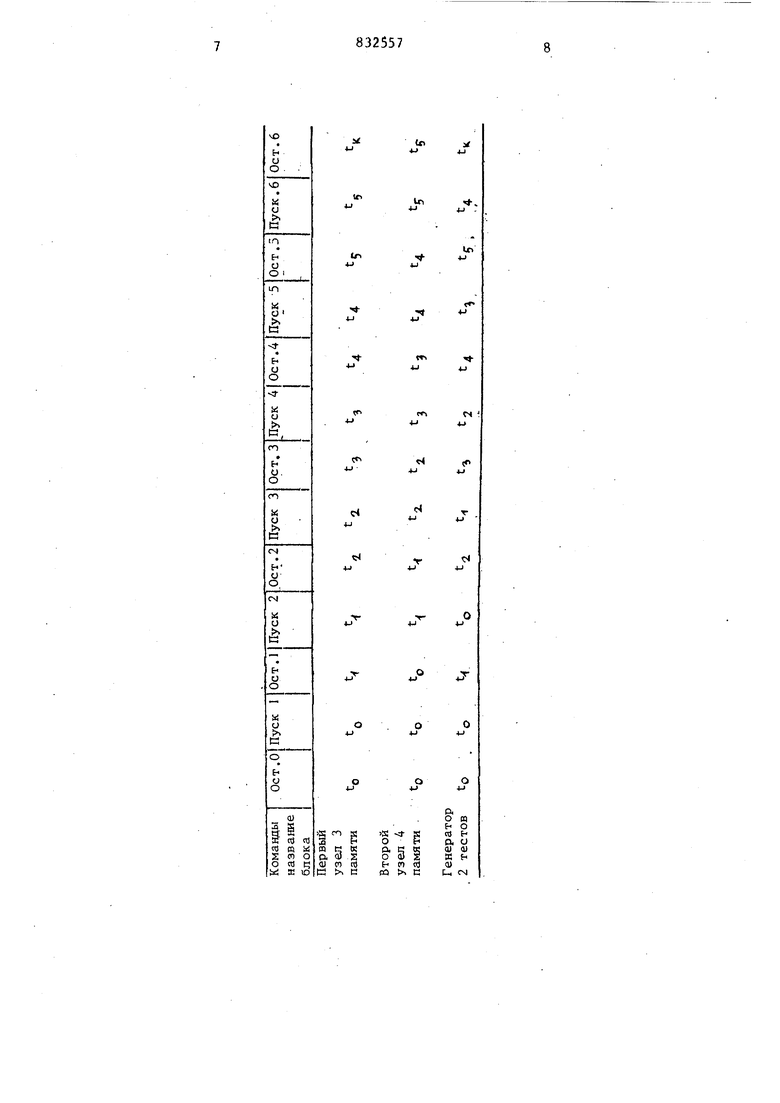

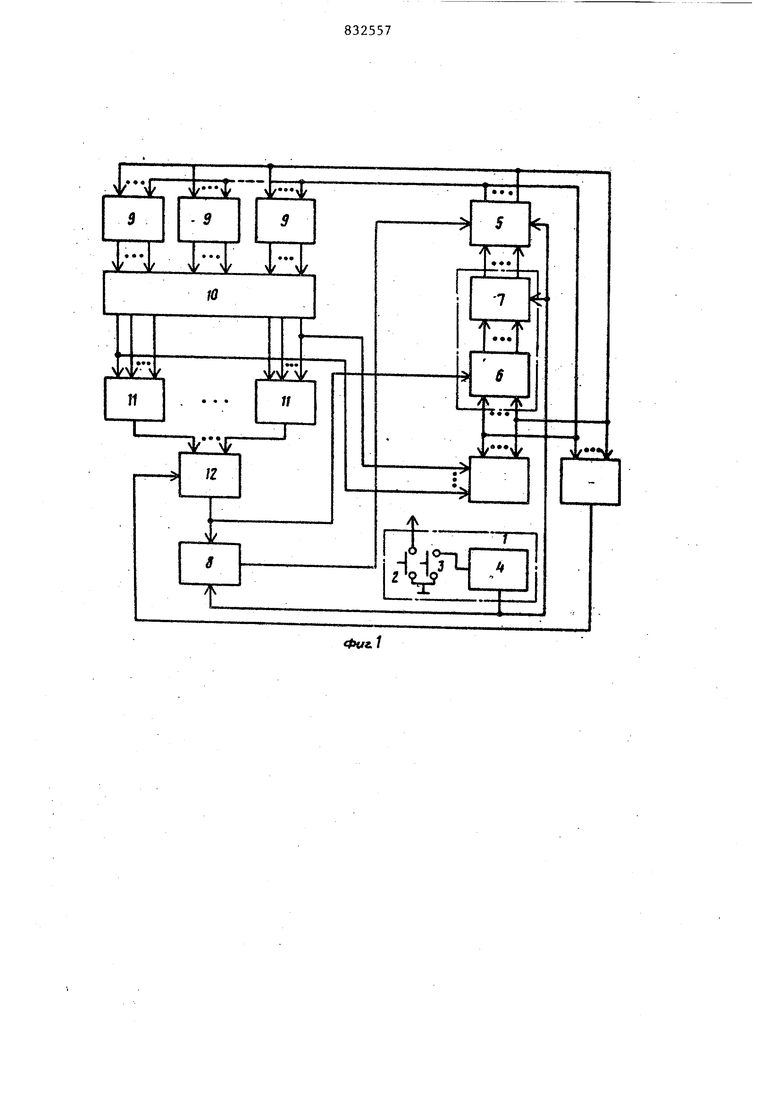

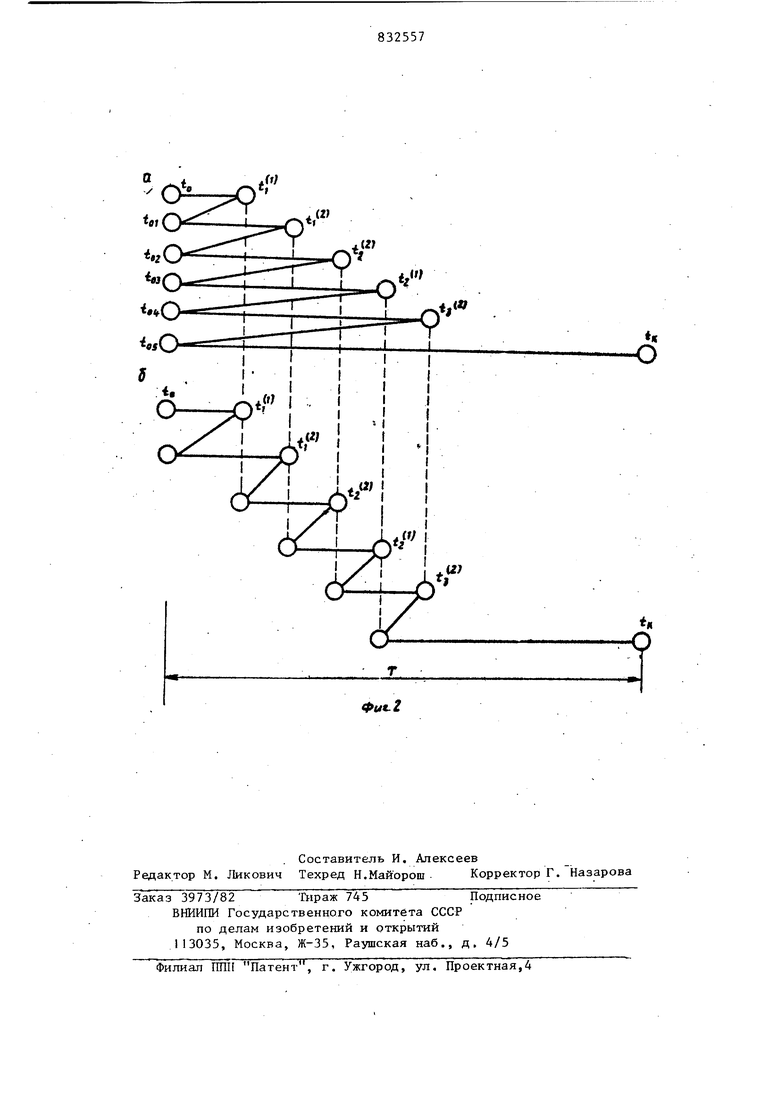

Изобретение относится к контролю устройств вычислительной техники и . может быть использовано для нахоадения дефектов в типовых элементах замены ЦВМ. Известно устройство поиска дефектов в логических блоках, которое позволяет контролировать типовые эле менты замены 1 . Однако при использовании этого -устройства на поиск всех дефектов затрачивается значительное время. Наиболее близким техническим реше нием к предлагаемому является устрой ство для нахождения кратных неисправ ностей в схемах ЦВМ. Это устройство позволяет отыскивать дефекты одновременно в нескольких объектах. Устройство содержит генератор импульсов, элементы ИЗЖ, стробирующие, бло кирующие и управляющие ключ, деимфратор,-линию задержки, счетчик импульсов, триггер остановки, трипер последнехо C4eT4ttKa, кнопки Сброс и Пуск, накапливающий сумматор, индикатор совпадения, схему сборки, иидикатС5|Г исправности 2. Недостаток устройства - значительные затраты времени на поиск дефектов. Цель изобретения - повышение быстр од ейств я устройства. Поставленная цель достигается тем, что в устройство введен 6jioK оперативной памяти, первый управляющий вход которого соединен с выходом блока управления и управляющим входом генератора тестов, второй управляющий вход - с выходом элемента 1ШИ, группа информационных входов - со второй группой входов блока индикации и группой входов дешифратора, группа информационных выходов - с группой информационных входов -генератора тестов. блок оперативной памятиг содержит последовательно соединенные первый и второй узлы пепмяти, iin(l)op8мационные входы первого узла памяти являются ии ормационными входаьш бло ка, управляющий вход - вторым управляющим входом блока, информационные выходы второго узла памяти являются информационными выходами блока, уп-. равляющий вход - первым управляющим входом блока. Это позволяет после обнаружения очередного дефекта тест (генератор тестов возвращать не в исходное состояние, а в состояние, соответствующее . моменту обнаружения предыду щего дефекта, В результате участок теста, на котором не обнаруживались дефекты, не повторяется несколько ра На фиг, 1 представлена структурна схема устройства)на фиг. 2 - временная диаграмма работы устройства. Устройство содержит блок 1 управления, генератор 2 тестов, блок 5 оперативной памяти, состоящий из последовательно соединенных первого уз ла 3 памяти и второго узла 4 памяти, генератор 6 импульсов, N контролируемых типовых элементов 7 замены, коммутатор 8, элементов 9 неравнозначности, элементы 0 ИЛИ, блок 11 индикации, дешифратор 12, Устройство работает следующим образом, По команде блока 1 управления (связь для упрощения на чертеже не по казана) устаналиваются в исходные состояния генератор 2 тестов, первый узел 3 памяти и второй 4 узел памяти блока 5 оперативной памяти. Затем по команде Пуск блока 1 управления последовательно осуществляются следующие операции: генератор 2 тестов устанавливается в состояние , соответствующее содержимому второго узла 4 памяти, а содержимое первого узла 3 памяти блока 5 оперативной памяти переписьшается во второй узел 4 памяти блока 5 оперативной памяти. По этой же команде генератор 6 импульсов начинает вырабатывать импульсы рабочей частоты, поступление которы в генератор 2 тестов вызывает генерацию тестовых сигналов. Эти сигнал подаются на контролируемые типовые элементы 7 замены таким образом, чт на идентичных входах всех контролируемых элементов 7 действуют одинаковые сигналы. Выходные сигналы кон ролируемых элементов 7, пройдя чере коммутатор 8, попадают на И N-BX 4 овых элементов 9 неравнозначности, где N - количество контролируемых типовых элементов 7 замены,а Ичисло выходов одного типового элемента 7 замены. Причем коммутатор 8 обеспечивает подключение идентичных выходов контролируемых типовых элементов 7 замены к одному и тому же элементу 9 неравнозначности. Если на каком-то К-ом выходе любого из контролируемых типовых элементов 7 замены на i -ом тестовом сигнале появляется сигнал неадекватный сигналам на К-ых выходах остальных контролируемых типовых элементах 7 замены, то срабатывает К-ый элемент 9 неравнозначности . Выходной сигнал (команда Останов) К-ого элемента 9 неравнозначности через, элемент 10 ИЛИ прекращает генерацию импульсов рабочей частоты генератора 6 импульсов и тем самым прекращает работу генератора 2 тестов. Эта же команда разрешает запись состояния генератора 2 тестов в первый узел 3 памяти блока 5 оперативной памяти. Кроме того, логические состояния (О или 1) выходов всех контролируемых типовых элементов 7 замены и генератора 2 тестов индицируются с помощью блока 1I индикации, по показаниям которого определяется неисправный типовой.элемент 7 замены и су цествующий в. нем дефект. После обнаружения и фиксации дефекта блока 1 управления вновь вырабатывает команду Пуск. По этой команде генератор 2 тестовустанавливается в состояние, соответствующее содержимому второго узла 4 памяти блока 5 оперативной памяти, а состояние -t-f первого узла 3 памяти блока 3 оперативной памяти заносится во .второй узел 4 памяти ёлока 5 оперативной памяти. В таблице показана последовательность переходов -состояний генератора 2 тестов, первого и второго узлов 3,4 памяти блока 5 оперативной памяти по командам Останов, соответствующим моментам обнаружения, дефектов, и Пуск. Рассмотрим временную диаграмму, которую можно интерпретировать, как граф переходов состояний генератора 2 тестов, поиска дефектов в двух контролируемых типовых элементах 7 замены, реализуемую в известном устройстве на примере двух дефектов в первом и трех - во втором типовых элементах 7 замены (фиг. 2 а). Вершины i р и-Ь, обозначают начало и конец теста, время генерирования которого Т.

ч Вершины - соответствуют номентам (состояниям)обнаружения -го дефекта в j -ом типовом элементе 7 замены, а вершины tnT повторным запускам теста. Реализуемый в известном устройстве принцип основан на повторных запусках теста с начального

состояния после обнаружения кавдого дефекта. Последний прогон теста свидетельствует об исправности обоих типовых элементов 7 замены.Временная диаграмма, поиска Дефектов в тех же типовых элементах 7 замены, реализуемая в предпагаемом устройстве, показан на фиг. 2 б. Между обозначениями на фиг, 2 и таблицей существует следуищее соответствие

Ч ,2 г 5 2 ч Как видно из фиг. 2 б, при повторных запусках тест начинается не сначала, а с состояния, соответств щегр моменту обг1яруже}тя предьщуще дефекта, В результате этого суммар время поиска всех дефектов сокраща ся. Если на всей длине теста э кон ролируемых типовых элементах 7 замены не обнаружено ни одного дефек та, то не срабатывает ни один элемент 9 неравнозначности. Прекращени проверки производится при появлении на выходах генератора 2 тестов последнего тестового сигнала, который вьщеляется дешифратором 12 и через элемент ИЛИ 10 останавливает генератор 6 импульсов. При этом исправность всех контролируемых типовых элементов 7 замены индицируется бло ком 11 индикации. Выигрыш во времен от применения предлагаемого устройс по сравнению с известным можно опре делить следующим образом: T-..t,),-r, ,где Т/( -/суммарное время поиска всех дефектов в известном устройстве; .,,,.ti,.,u,,, где |сумг-арное время поиска всех дефектов в предлагаемом устройстве. т т ТиГТт Oчeвиднoj что отношетше T-t/Ti 7 1, т. е. предлагаемое устройство обеспечивает, сокращение времени поиска всех дефектов, следовательно, повышает быстродействие. Формула изобретения 1. Устройство для контроля типовы элементов замены,содержащее генера7тор тестов, группа информационных выходов которого подключена ко входам контролируемых элементов и к группе входов дешифратора, выход которого подсоединен к первому входу элемента ИЛИ, выходом подключенного к первому управляющему входу генератора импульсов, второй управляющий вход которого соединен с выходом блока управления, а выход - с входом синхронизации генератора тестов, выходы контролируемых элементов подключены ко входам коммутатора, группы выходов которого подключены к группам входов соответствующих элементов неравнозначности и первой группе входов блока индикации, выходы элементов неравнозначности соединены с соответствующими входами элемента ИЛИ, о тли чающеес я тем, что с целью повышения быстродействия устройства, оно содержит блок оперативной памяти, первый управляющий вход которого соединен с выходом блока управления и управляющим входом генератора тестов, второй управляющий вход - с выходом элемента ИЛИ, группа информационных входов - со второй группой входов бло- . ка индикации и группой входов дешифратора, группа информационных выходов - с группой информационных входов генератора тестов, 2, Устройство по п, 1, отличающееся тем, что блок оперативной памяти содержит последовательно соединенные первый и второй узлы памяти, информационные входы первого узла памяти являются информационными входами блока, управляющий вход - вторым управляющим входом блока, информационные выходы второ о узла памяти являются информационными выходами блока, управляющий вход - первым управляющим входом блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 378852, кл. S 06 F 11/00, 1968, 2,Авторское свидетельство СССР 533894, кл, G 06 Р 31/28, 1976 (прототип),

Фил. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска кратных дефектов в группе объектов | 1983 |

|

SU1233157A1 |

| Устройство для обнаружения кратных дефектов в группе типовых элементов замены | 1983 |

|

SU1126966A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для поиска кратных неисправностей в однотипных логических блоках | 1978 |

|

SU781816A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

Авторы

Даты

1981-05-23—Публикация

1979-07-16—Подача