4; 4

4

00

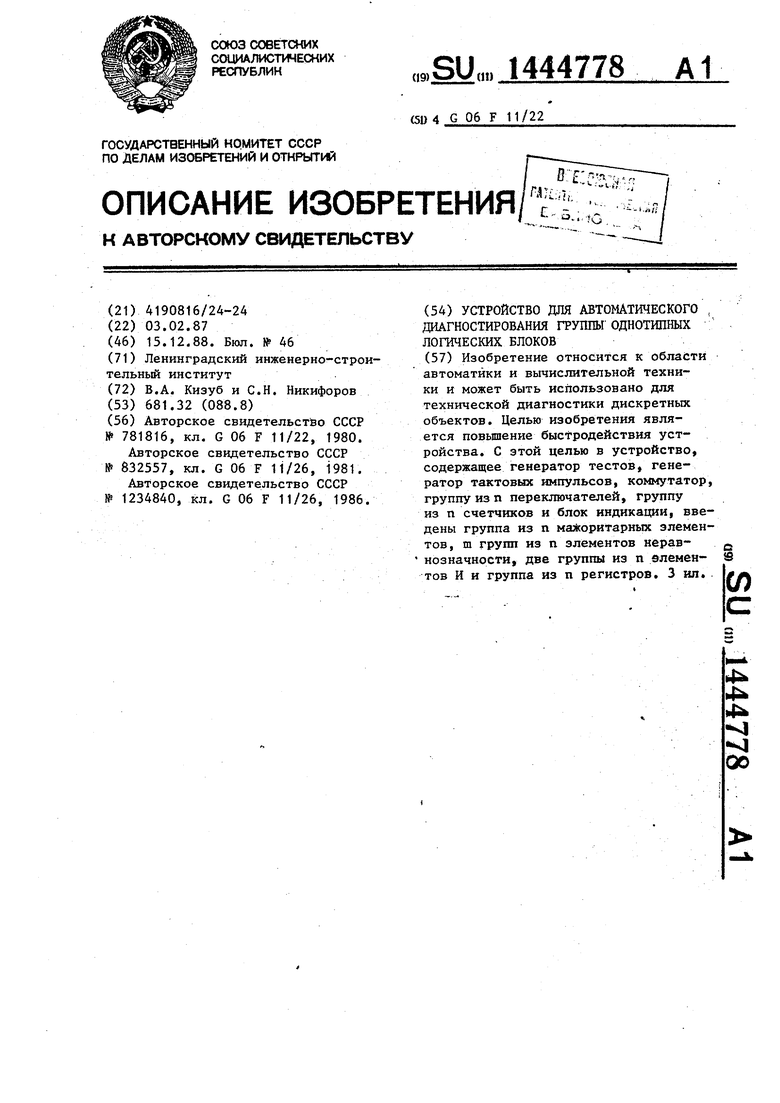

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для технической диагностики дискретных объектов, .

Целью изобретения является повышение быстродействия устройства.

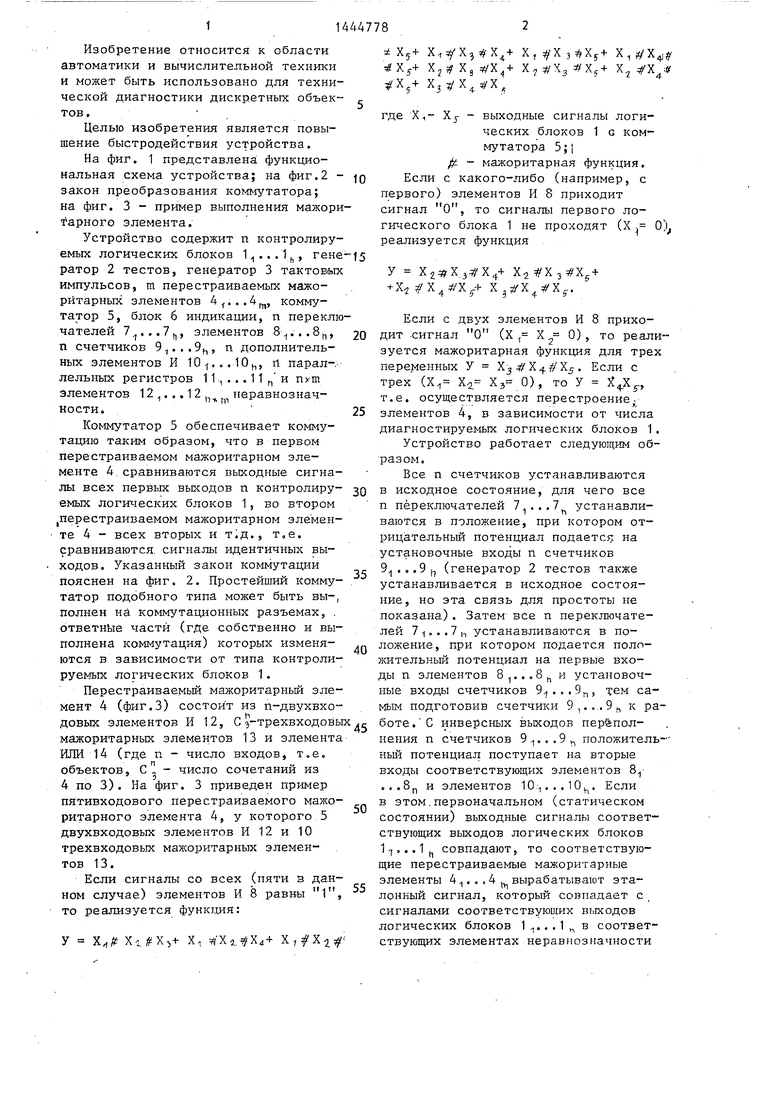

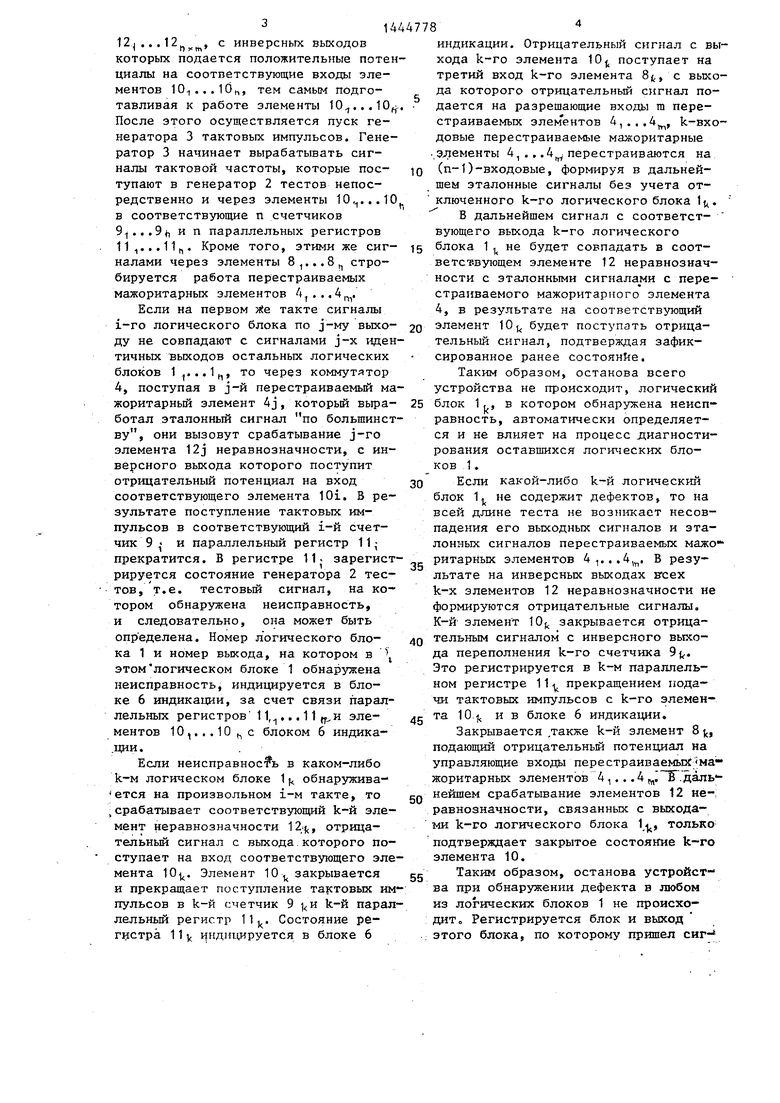

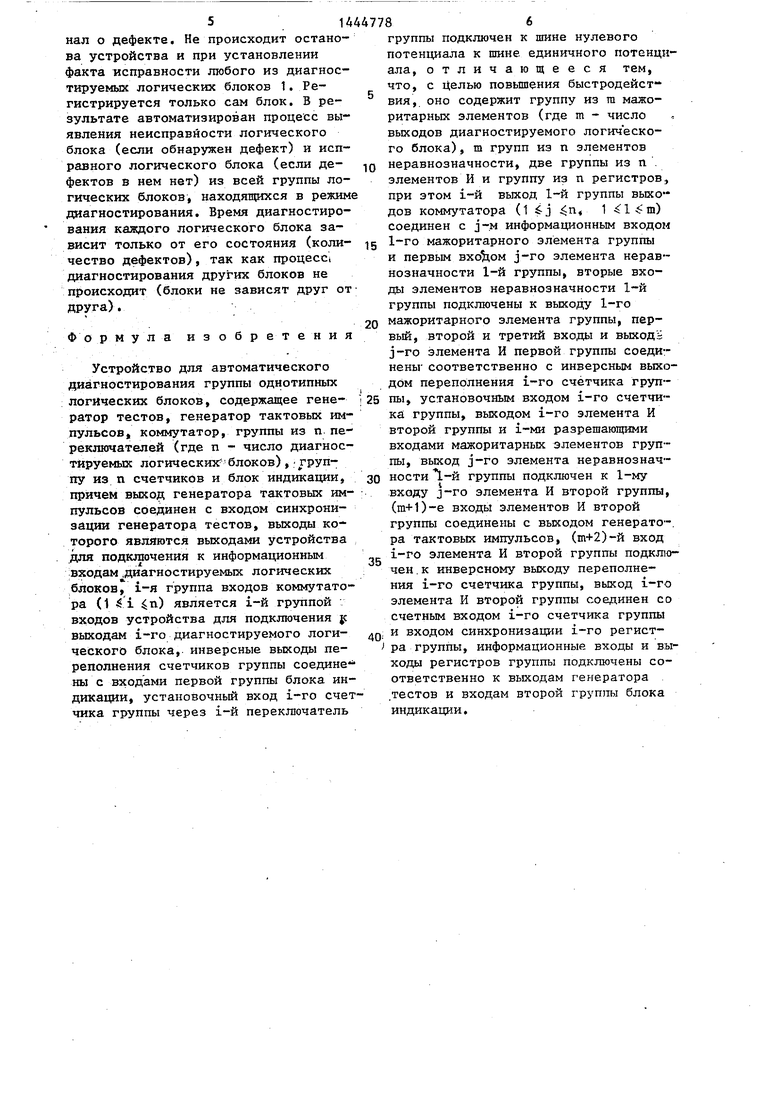

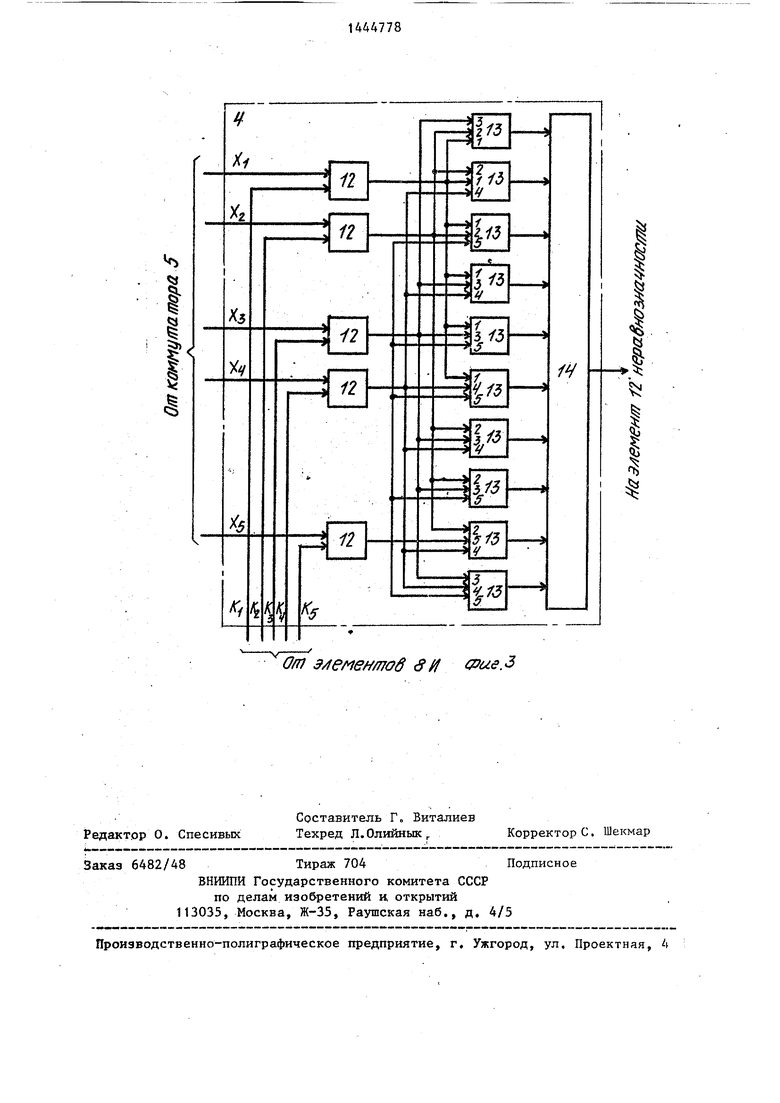

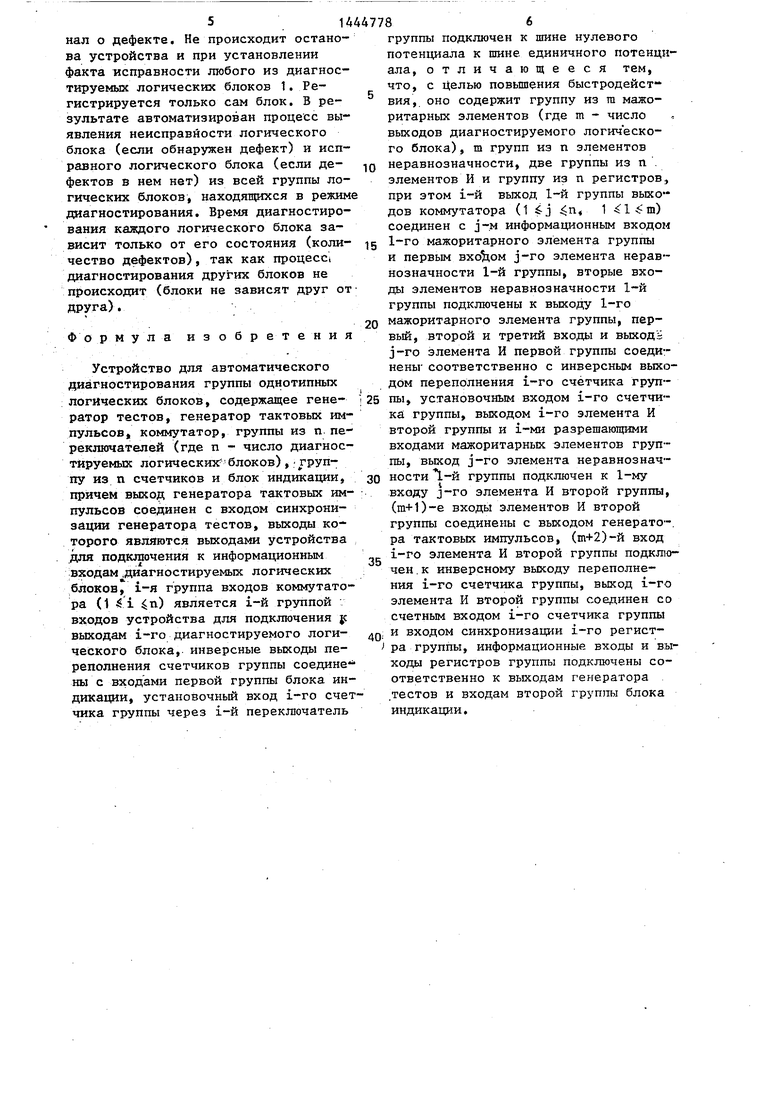

На фиг, 1 представлена; функциональная схема устройства; на фиг,2 - закон преобразования коммутатора; на фиг, 3 - пример выполнения мажоритарного элемента.

Устройство содержит п контролируемых логических блоков 1 ,. , 1 , гене ратор 2 тестов, генератор 3 тактовых импульсов, m перестраиваемых мажоритарных элементов 4,,.4, коммутатор 5, блок 6 индикации, п переключателей 7,,, 7, элементов 8ч,,,. 8 f,, п счетчиков 9,,,,9f,5 п дополнительных элементов И 10 ...10,, п парал-. лельных регистров 11 , , , , 11 и пхт элементов 12 ,, ,, 12 , неравнозначности.

Коммутатор 5 обеспечивает коммутацию таким образом, что в первом перестраиваемом мажоритарном элементе 4 сравниваются выходные сигналы всех первых выходов п контролируемых логических блоков 1, во втором перестраиваемом мажоритарном элементе 4 - всех вторых и т,д,, т,е, сравниваются, сигналы идентичных выходов. Указанный закон коммутации пояснен на фиг, 2, Простейший коммутатор подобного типа может быть выполнев на коммутационных разъемах, . ответные части (где собственно и выполнена коммутация) которых изменяются в зависимости от типа контроли- pyet-aix логических блоков 1,

Перестраиваемьй мажоритарный элемент 4 (фиГоЗ) состоит из п-двухвхо1

х, Х,

Xj9i Xj +

.

Xf +

(Х,

0).

где Х,- Xj- - выходные сигналы логических блоков 1 G коммутатора 5;|

- мажоритарная функция. Если с какого-либо (например, с первого) элементов И 8 приходит сигнал О, то сигналы первого логического блока 1 не проходят реализуется функция

У . Х2 Хэ#Х5 + t-X .

Если с двух элементов И 8 приходит .сигнал О (X ,, X 0), то реализуется мажоритарная функция для трех переменных У X;j:#X4#Xj, Если с трек (Х Х2. Хэ 0), то У ), т.е, осуществляется перестроение, элементов 4, в зависимости от числа диагностируемых логических блоков 1.

Устройство работает следующим образом.

Все п счетчиков устанавливаются в исходное состояние, для чего все п переключателей 7.,,7 устанавливаются в положение, при котором отрицательный потенциал подается на установочные входы п счетчиков 9,.,9| (генератор 2 тестов также устанавливается в исходное состояние, но эта связь для простоты пе показана), Затем все п переключателей 71,,.7 п устанавливаются в положение, при котором подается положительный потенциал на первые входы п элементов 8 ,,.8, и установочные входы счетчиков 9..,9f, тем самым подготовив счетчики 9,,,,.9., к ра

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического диагностирования однотипных логических блоков | 1987 |

|

SU1444779A1 |

| Устройство для поиска кратных дефектов в группе объектов | 1983 |

|

SU1233157A1 |

| Устройство для диагностирования @ групп однотипных логических блоков | 1984 |

|

SU1196878A1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для непрерывного диагностирования однотипных логических блоков | 1984 |

|

SU1234840A1 |

| Распределенная система для программного управления с мажоритированием | 1990 |

|

SU1727112A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для технической диагностики дискретных объектов. Целью изобретения является повышение быстродействия устройства. С зтой целью в устройство, содержащее генератор тестов, генератор тактовых импульсов, коммутатор, группу из п переключателей, группу из п счетчиков и блок индикации, введены группа из п мажоритарных элементов, m групп из п элементов нерав- нозначности, две группы из п элементов И и группа из п регистров. 3 ил. о « (Л

довых элементов И 12, Сз-трехвходовькд боте, С инверсных выходов перёполмажоритарных элементов 13 и элемента ИЛИ 14 (где п - число входов, т.е. объектов, с - число сочетаний из 4 по 3), На фиг, 3 приведен пример пятивходового перестраиваемого мажоритарного элемента 4, у которого 5 двухвходовых элементов И 12 и 10 трехвходовых мажоритарных элементов 13,

Если сигналы со всех (пяти в данном случае) элементов И 8 равны 1, то реализуется функция:

нения п счетчиков 9 .,,. , 9 у, положительный потенциал поступает на вторые входы соответствующих элементов ..,8 и элементов 10.-i,..10. , Если

50

в этом,первоначальном (статическом состоянии) выходные сигналы соответствующих выходов логических блоков 1-1.,, 1 совпадают, то соответствующие перестраиваемые мажоритарные элементы 4,,, . , 4 ( вырабатывают эталонный сигнал, который совпадает с, сигналами соответствующих выходов логических блоков 1 ,, . 1 ( в соответ- У Xi#X,+ X,, ствующих элементах неравнозначности

55

боте, С инверсных выходов перёполнения п счетчиков 9 .,,. , 9 у, положитель- ный потенциал поступает на вторые входы соответствующих элементов ..,8 и элементов 10.-i,..10. , Если

12i...12., , с инверсных выходов

1 Г) X m

которых подается положительные потенциалы на соответствующие входы элементов 10i...l6rt, тем самым подготавливая к работе элементы 10... 10, После этого осуществляется пуск генератора 3 тактовых импульсов. Генератор 3 начинает вырабатывать сигналы тактовой частоты, которые пос- тупают в генератор 2 тестов непосредственно и через элементы 10,... ТО в соответствующие п счетчиков 9...9f| и п параллельных регистров 11...11. Кроме того, этими же сиг- налами через элементы 8 .,, 8 , стро- бируется работа перестраиваемых мажоритарных элементов 4,....

Если на первом я{е такте сигналы i-ro логического блока по j-му выходу не совпадают с сигналами j-x идентичных выходов остальных логических блоков 1 ...1, то через коммутятор 4, поступая в j-й перестраиваемьй мажоритарный элемент 4j, который выработал эталонный сигнал по большинству, они вызовут срабатывание j-ro элемента 12j неравнозначности, с инверсного выхода которого поступит отрицательный потенциал на вход соответствующего элемента 101. В результате поступление тактовых импульсов в соответствующий i-й счетчик 9 и параллельный регистр 11; прекратится. В регистре 11- зарегист рируется состояние генератора 2 тестов, т.е. тестовый сигнал, на котором обнаружена неисправность, и следовательно, она может быть определена. Номер л огического бло- ка 1 и номер выхода, на котором в этом логическом блоке 1 обнаружена неисправность, индицируется в блоке 6 индикации, за счет связи параллельных регистров 11,... 11 эле- ментов 10 ,... 10 с блоком 6 индика- .ции.

Если неисправность в каком-либо k-M логическом блоке 1 f обнаружива- ется на произвольном i-м такте, то срабатывает соответствующий k-й элемент неравнозначности 12;, отрицательный сигнал с выхода.которого поступает на вход соответствующего элемента 10. Элемент 10. закрывается и прекращает поступление тактовых им пульсов в k-й счетчик 9 и k-й параллельный регистр 11. Состояние регистра 11 индицируется в блоке 6

1444778

0

5

Q 5

о 0 5

о g

индикации. Отрицательный сигнал с выхода k-ro элемента 10 поступает на третий вход k-ro элемента 8(., с выхода которого отрицательный сигнал подается на разрешающие входы га пере- страиваемьк элем ентов 4,.,.4, k-вхо- довые перестраиваемые мажоритарные элементы 4, .. .4 перестраиваются на (п-1)-входовые, формируя в дальней- щем эталонные сигналы без учета отключенного k-ro логического блока Ц. В дальнейшем сигнал с соответст- вующего выхода k-ro логического блока 1 не будет совпадать в соот- ветст.вующем элементе 12 неравнозначности с эталонными сигналами с перестраиваемого мажоритарного элемента 4, в результате на соответствующий элемент Ю будет поступать отрицательный сигнал, подтверждая зафиксированное ранее состояние.

Таким образом, останова всего устройства не происходит, логический блок 1,, в котором обнаружена неисправность, автоматически определяется и не влияет на процесс диагностирования оставшихся логи 1еских блоков 1.

Если какой-либо k-й логический блок Ц не содержит дефектов, то на всей длине теста не возникает несовпадения его выходных сигналов и эталонных сигналов перестраиваемых мажо ритарных элементов 4 ,...4,. В результате на инверсных выходах вх;ех k-x элементов 12 неравнозначности не формируются отрицательные сигналы. К-й элемент 10j закрывается отрицательным сигналом с инверсного выхода переполнения k-ro счетчика 9,. Это регистрируется в k-м параллельном регистре 11. прекращением подачи тактовых импульсов с k-ro элемента 10. и в блоке 6 индикации.

Закрывается .также k-й элемент 8 , подающий отрицательный потенциал на управляющие входы перестраиваемых мажоритарных элементов 4,... 4 . В .дапь нейшем срабатывание элементов 12 не-; равнозначности, связанных с выходами k-ro логического блока 1д, только подтверждает закрытое состояние k-го элемента 10.

Таким образом, останова ycTpoftCT- ва при обнар;ужении дефекта в любом из логических блоков 1 не происходит Регистрируется блок и выход этого блока, по которому пришел сиг-

нал о дефекте. Не происходит останова устройства и при установлении факта исправности любого из диагностируемых логических блоков 1, Регистрируется только сам блок. В результате автоматизирован процесс выявления неисправности логического блока (если обнаружен дефект) и исправного логического блока (если дефектов в нем нет) из всей группы логических блоков, находящихся в режим диагностирования. Время диагностирования каждого логического блока зависит только от его состояния (количество дефектов), так как процесс диагностирования других блоков не происходит (блоки не зависят друг от друга).

Формула изобретения

Устройство для автоматического диагностирования группы однотипных логических блоков, содержащее гене- ратор тестов, генератор тактовых импульсов, коммутатор, группы из п переключателей (где п - число диагностируемых логических блоков), Группу из п счетчиков и блок индикации, причем выход генератора тактовых импульсов соединен с входом синхронизации генератора тестов, вьссоды которого являются выходами устройства для подключения к информационным входам .диагностируемых логических блоков, i-я группа входов коммутатора (1 i. 4п) является i-й группой взсодов устройства для подключения {с выходам i-ro диагностируемого логического блока, инверсные выходы переполнения счетчиков группы соедине ны с входами первой группы блока индикации, установочный вход i-ro счетчика группы через i-й переключатель

5

0

группы подключен к шине нулевого потенциала к шине единичного потенциала, отличающееся тем, что, с целью повышения быстродейст ВИЯ,, оно содержит группу из m мажоритарных элементов (где m - число выходов диагностируемого логического блока), m групп из п элементов неравнозначности, две группы из п . элементов И и группу из п регистров, при этом i-й выход 1-й группы выхо ДОН коммутатора (1 j 4п, 1 ) соединен с j-M информационным входом 1-го мажоритарного элемента группы и первым j-ro элемента неравнозначности 1-й группы, вторые входы элементов неравнозначности 1-й группы подключены к выходу 1-го мажоритарного элемента группы, первый, второй и третий входы и выходь j-ro элемента И первой группы соединены соответственно с инверсным выходом переполнения i-ro счётчика груп5 пы, установочным входом i-ro счетчика; группы, выходом i-ro элемента И второй группы и i-ми разрешающими входами мажоритарных элементов группы, выход j-ro элемента неравнозначности 1-й группы подключен к 1-му входу J-ro элемента И второй группы, (т+1)-е входы элементов И второй группы соединены с выходом генерато-. ра тактовых импульсов, (т+2)-й вход i-ro элемента И второй группы подключен .к инверсному выходу переполнения i-ro счетчика группы, выход i-ro элемента И второй группы соединен со счетным входом i-ro счетчика группы

Q. и входом синхронизации i-ro регнст- ра группы, информационные входы и выходы регистров группы подключены соответственно к выходам генератора .тестов и входам второй группы блока индикации.

0

5

Фие.-f

. 8ь/)(одй/ 1-гобь/хадш Ж-гоBbixodbi п-га

. аиаенос. /los. /y/fff/caf /ое. /fofca i &иаенос ог. /fujca /

... К Ы

,il

v

Канфор. в}(ода/ кинформ. nep6oii схемы У б/77орой схемь/ cpadneHuffсравнениеФиа. 2

ff7

II

У7

Кинфо/. х(ам т-ойсхемш cpa eHLisf

O/n э/1е ен/по6 S И Фие.З

| Устройство для поиска кратных неисправностей в однотипных логических блоках | 1978 |

|

SU781816A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля типовыхэлЕМЕНТОВ зАМЕНы | 1979 |

|

SU832557A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для непрерывного диагностирования однотипных логических блоков | 1984 |

|

SU1234840A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-02-03—Подача