Изобретение относится к автоматическому контролю средств вычислительной техники и может применяться в автоматизированных системах управления и контроля.

Цель изобретения - повышение достоверности контроля за счет осуществления выбора эталона на том же самом испытательном стенде, на котором впоследствии производится разбраковка очередных объектов контроля, а также подтверждение в каждом такте разбраковки исправности эталона.

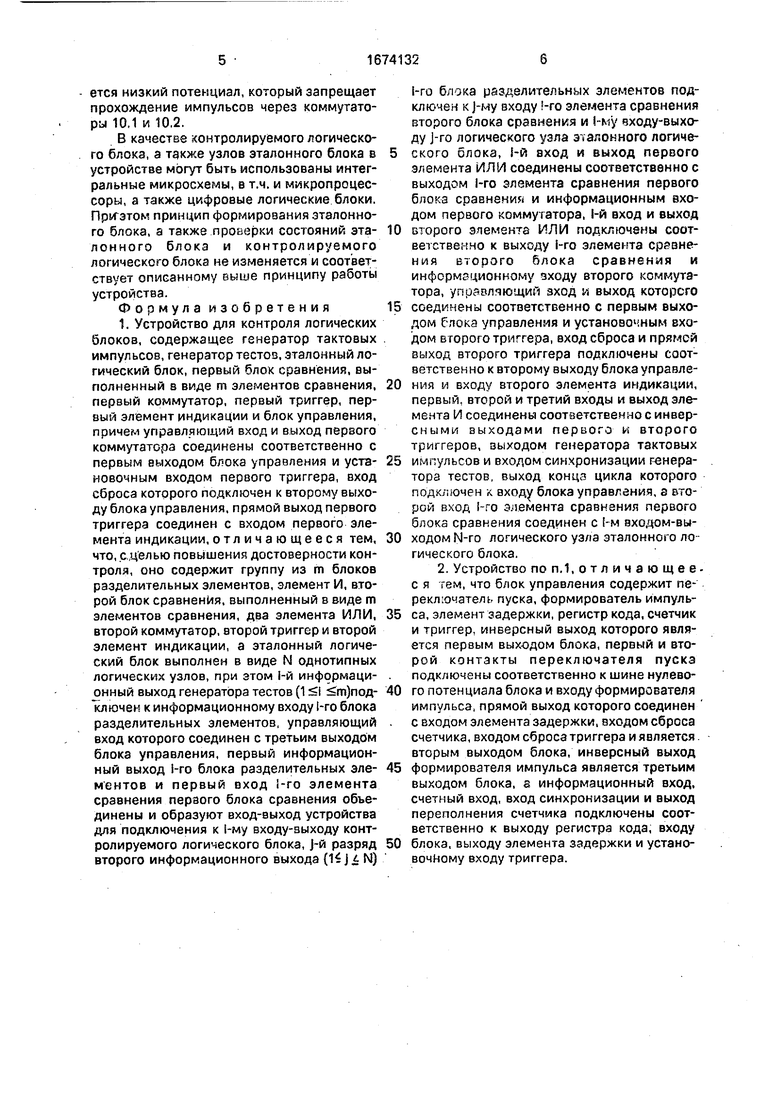

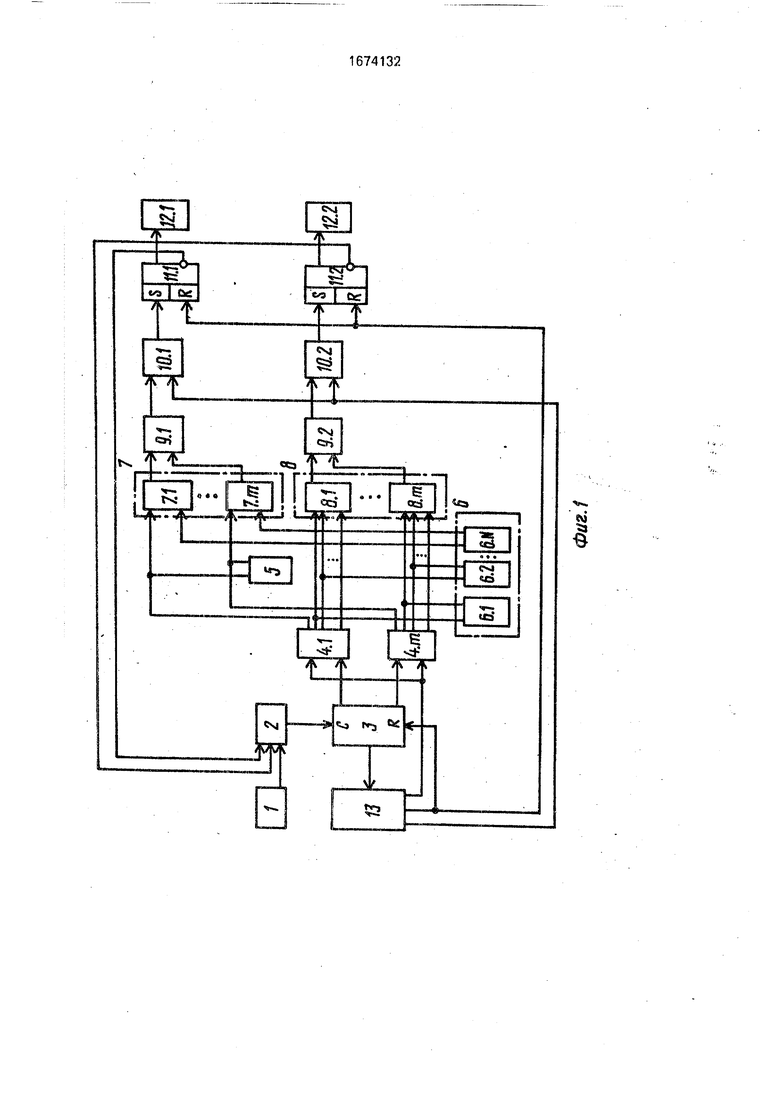

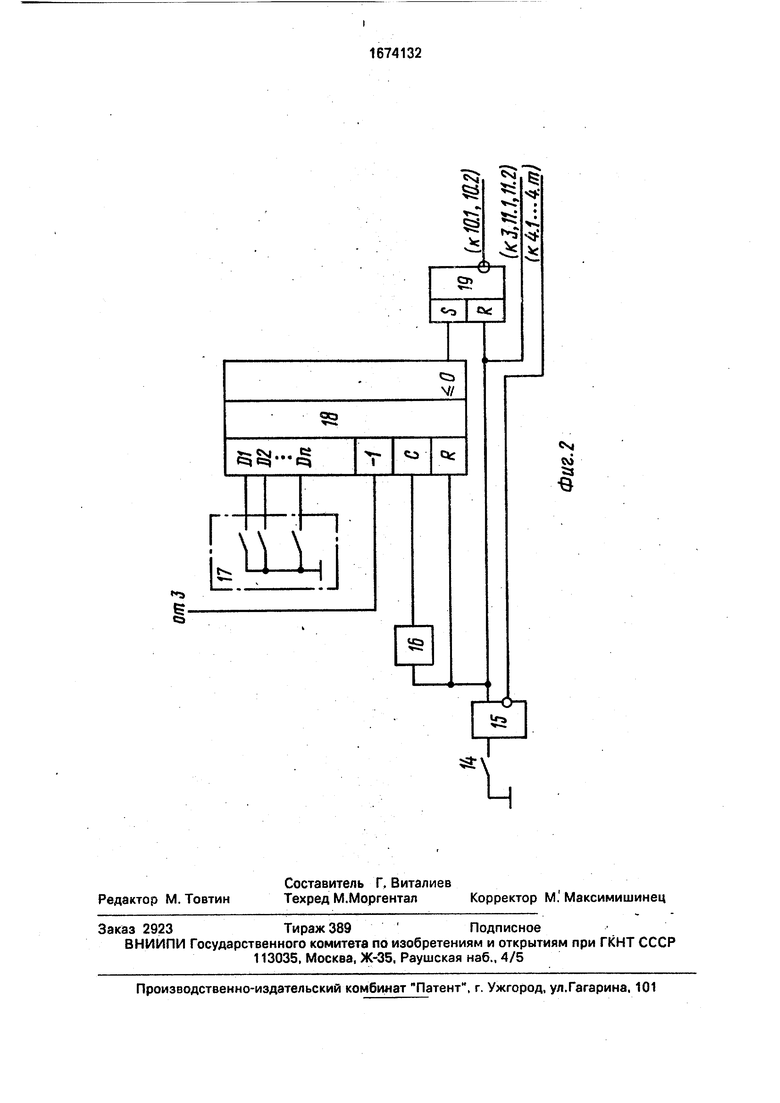

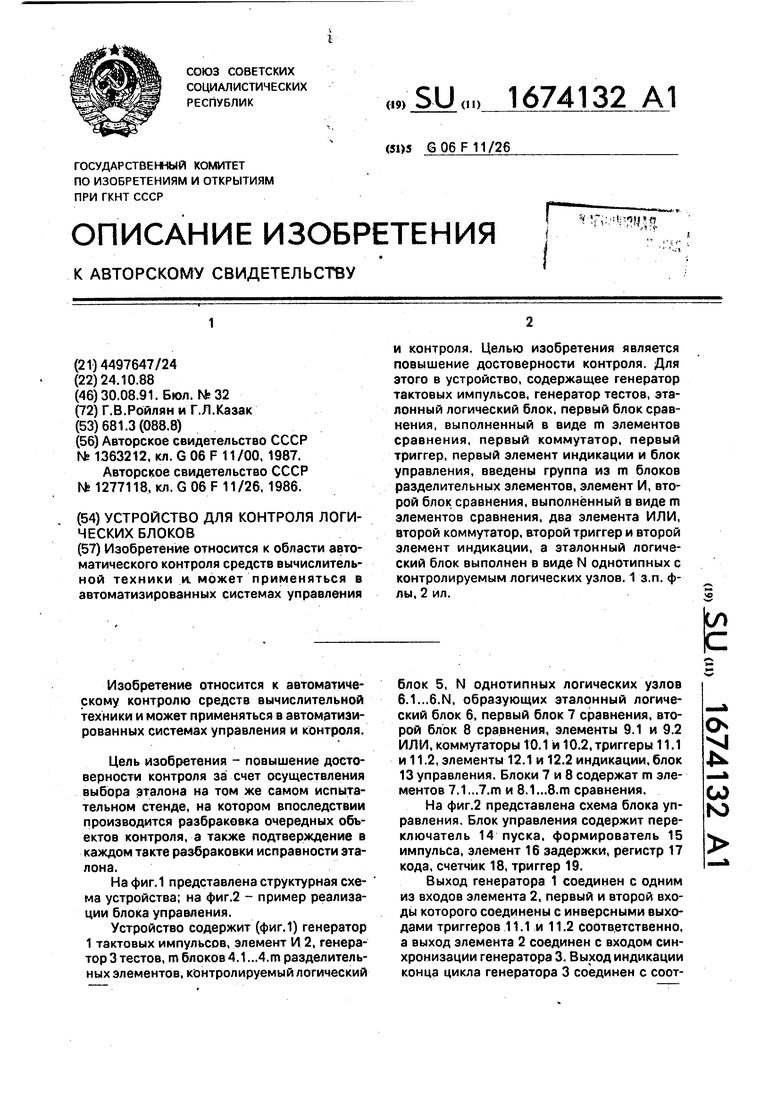

На фиг.1 представлена структурная схема устройства; на фиг.2 - пример реализации блока управления.

Устройство содержит (фиг.1) генератор 1 тактовых импульсов, элемент И 2, генератор 3 тестов, m блоков 4.1 ...4.т разделительных элементов, контролируемый логический

блок 5, N однотипных логических узлов 6.1...6.N. образующих эталонный логический блок 6, первый блок 7 сравнения, второй блок 8 сравнения, элементы 9.1 и 9.2 И Л И, коммутаторы 10.1 и 10.2, триггеры 11.1 и 11.2.элементы 12.1 и 12.2 индикации,блок 13 управления. Блоки 7 и 8 содержат m элементов 7.1,..7.т и 8.1...8.т сравнения.

На фиг.2 представлена схема блока управления. Блок управления содержит переключатель 14 пуска, формирователь 15 импульса, элемент 16 задержки, регистр 17 кода, счетчик 18, триггер 19.

Выход генератора 1 соединен с одним из входов элемента 2, первый и второй входы которого соединены с инверсными выходами триггеров 11.1 и 11.2 соответственно, а выход элемента 2 соединен с входом синхронизации генератора 3. Выход индикации конца цикла генератора 3 соединен с соотО

g

со ю

ветствующим входом блока 13 управления, а информационные выходы генератора 3 соединены с соответствующими входами m блоков 4.1..А.т, управляющие входы которых соединены с третьим выходом блока 13 управления, а вход сброса генератора 3 соединен с вторым выходом блока 13 управления и входами сброса триггеров 11.1 и 11.2. Первые выходы блоков 4.1. . 4.т соединены с соответствующими входами-выходами контролируемого логического блока 5, а остальные m выходов блоков 4.1..Am соединены с соответствующими входами элементов 8 1 ...8.т блока 8 сравнения и с соответствующими входами-выходами узлов 6.1...6.N, образующих эталонный блок 6. При этом входы-выходы узла 6.N соединены также со вторыми входами соответствуюиих элементов 7.1...7.ГТ1 блока 7 сравнения, выходы которых соединены с соответствующими входами элемента 9.1, а выходы m элементов 8.1 ...8.m блока 8 сравнения соединены с соответствующими входами элемента 9.2. Выход элемента 9.1 соединен с информационным входом коммутатора 10.1, а выход элемента 9.2 соединен с информационным йходом коммутатора 10.2, причем управляющие входы коммутаторов сседиьспы с первым выходом блока 13. Выходы коммутаторов 10.1 и 10.2 соединены с вующими информационными входами триггеров 11.1 и 11.2, прямые выходы которых соединены с входами соответствующих элементов 12.1 и 12.2 иидикаии,

В блоке 13 управления пхсд формирователя 15 импульса соединен с одним из контактов переключателя 14 пуско, второй контакт которого подключена тине нулесо го потенциапо, ч прямой выход формирователя 15 импульсов соединен с входом элемента 16 задержки и входами сброса счетчика 18 и триггера 19 блока и яьляется вторым выходом блока. Инверсный выход формирователя 15 импульса является т реть- им выходом блока. Выход элемента 16 задержки соединен с входом синхронизации счетчика 18, информационный сход которого соединен с соответствующим et ;ходом регистра 17 кода, а вход вычитания ютчика 18 является входом блока. Выход переполнения счетчика 18 соединен с установочным входом триггера 19 блока, инверсный выход копрою является первым выходом блока.

Устройство работает следующим образом.

При нажатии переключателя 14 пуска формирователь 15 вырабатывает импульс сброса, устанавливающий счетчик 18, триггер 19 блока управления, 1енератог Зтестоз и триггеры 11 в исходное состояние, rooiветствующее отсутствию свечения элементов 12 индикации. На инверсных выходах триггеров 11 и соответственно на первом и втором входах элемента 2 устанавливается

высокий потенциал, что разрешает прохождение тактовых импульсов с выхода генератора 1 на оходсинхронизации генератора 3, на информационных выходах которого появляются m-разрядные наборы стимулиру0 ющих воздействий, которые поступают на информационные входы m блоков 4.1,..4.m.

После окончания импульса сброса на инверсном выходе формирователя 15 появ5 ляется низкий потенциал, поступающий на входы разрешения блоков 4.1. .4,т, которые начинают передавать выходные наборы, формируемые генератором 3 на входы кон- т ролируемого блок 5 и на входы N однотип0 ных 6 1.. 6.N узлов, образующих эталонный олок. Элементы 7,1...7.т блока 7 сравнения сравнивают сиги шы на выходах блока 5 и узла 6.N и в случае несовпадения реакций рыдают сигнал через элемент 9.1 и коммута5 гор 10.1 на триггер 11.1, на прямом выходе которого устанавливается высокий потенциал, сое , влствующий свечению индикатора Р. 1, т ня инверсном выходе триггера 11.1 устанавливается низкий потенциал, ко0 торий подается на первый вход эпемента 2, запрещая поступление импульсов с выхода генератора 1 на вход генератора 3.

Элементы 8.1,..8.т блока 8 сравнения сравнивают сигналы на выходах узлов

5 6.1...8.N, образующих эталонный блок, и в случае несовпадения реакций выдают сигнал через элемент 9 2 и коммутатор 10.2 на триггер 11 2, на прямом выходе которого устанавливаете; высокий потенциал, соот0 оетстоующий свечсчнию индикатора 12.2, а на инверсном выходе триггера 11.2 устанавливается низкий потенциал, который подается на второй вход элемента 2, запрещая поступление импульсов с выхода генератое ря 1 на оход генератора 3.

Блок 13 управления работает следующим образом, Импульс сброса с прямого выход:, формирователя 15 импульса, через элемент 16 задержки, поступает на вход

0 синхоснизации счетчика 18, обеспечивая запис в счетчик кода числа циклов, заданно регистром 17 кода. На вычитающий вход счетчика 18 поступают с генератора 3 импульг.ы индикации конца цикла. При сов5 падении числа вычитающих импульсов с к.0- дом числа циклов, на выходе переполнения счетчика 18 появляется импульс, который устанавливает на прямом выходе триггера 19 блока высокий потенциал. При Этом на инверсном выходе ;риггору 19устанапливается низкий потенциал, который запрещает прохождение импульсов через коммутатору 10,1 и 10.2.

В качестве контролируемого логического блока, а также узлов эталонного блока Е устройстве могут быть использованы интегральные микросхемы, в т.ч. и микропроцессоры, а также цифровые логические блоки, принцип формирования эталонного блока, а также проверки состояний лонного блока и контролируемого логического блока не изменяется и соответствует описанному пыше принципу работы устройства.

Формула зобретения

1. Устройство для контроля логических блоков, содержащее генератор тактовых импульсов, генератор тестоо, эталонный логический блок, первый блок сравнения, выполненный в виде m элементов сравнения, первый коммутатор, первый триггер, первый элемент индикации и блок управления, причем управляющий вход и выход первого коммутатора соединены соответственно с первым выходом блока управления и уста- Новотным входом первого триггера, вход сброса которого подключен к второму выходу блока управления, прямой выход первого триггера соединен с входом первого элемента индикации, отличающееся тем, что, с целью повышения достоверности контроля, оно содержит группу из m блоков разделительных элементов, элемент И, второй блок сравнения, выполненный в виде m элементов сравнения, два элемента ИЛИ, второй коммутатор, второй триггер и второй элемент индикации, а эталонный логический блок выполнен в виде N однотипных логических узлов, при этом 1-й информационный выход генератора тестов (1 гп)под- ключей к информационному входу 1-го блока разделительных элементоэ управляющий вход которого соединен с третьим выходом блока управления, первый информационный выход 1-го блока раздетительных эле- ментов и первый вход 1-го элемента сравнения перзого блока сравнения объединены и образуют вход-выход устройства для подключения к 1-му входу-выходу контролируемого логического блока, J-й разряд второго информационного выхода (1Ј j t. N)

1-го блока разделительнмх элементов подключен к J-му входу -го элемента сравнения гяорого блока сравнения и 1-му яходу-выхо- ду j-ro логического узла а.алойного логического блока, 1-й вход и выход первого элемента ИЛИ соединены соответственно с выходом 1-го элемента сравнения первого блока сравнение и информационным входом первого коммутатора, 1-й вход и выход скорого элемента ИЛИ подключены соот- веютвенно к выходу 1-го элемента сравнения второго Ъпока сравнения и информационному зходу второго коммутатора, управляющий зход и выход которого соединены соответственно с первым выходом С-л ока управления и установочным входом второго триггера, вход сброса и прямей выход второго триггера подключены соответственно к второму выходу блока управления и входу второго элемента индикации, первый, второй и третий входы и выход элемента И соединены соответственно с инвер- сными выходами перього ь второго триггеров, выходом генератора тактовых импульсов и входом синхронизации генератора тестов, выход конця цикла которого подключен к входу блока управления, а агорой вход 1-го элемента сравнения первого блока сравнения соединен с 1-м входом-выходом N-го логического узла эталонно о ло гического блока.

2. Устройство по п. 1,отличающее, с я гем, что блок управления содержит переключатель пуска, формирователь импульса, элемент задержки, регистр кода, счетчик и триггер, инверсный выход которого является первым выходом блока, первый и второй контакты переключателя пускэ подключены соответственно к шине нулевого потенциала блока и входу формирователя импульса, прямой выход которого соединен с входом элемента задержки, входом сброса счетчика, входом сброса триггера и является вторым выходом блока, инверсный выход формирователя импульса является третьим выходом блока, г информационный вход, счетный вход, вход синхронизации и выход переполнения счетчика подключены соответственно к выходу регистра кода, входу блока, выходу элемента задержки и установочному входу триггера.

Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель температуры | 1982 |

|

SU1111038A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1223234A1 |

| Устройство для контроля электрических соединений | 1988 |

|

SU1619310A2 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

Изобретение относится к области автоматического контроля средств вычислительной техники и может применяться в автоматизированных системах управления и контроля. Целью изобретения является повышение достоверности контроля. С этой целью в устройство, содержащее генератор тактовых импульсов, генератор тестов, эталонный логический блок, первый блок сравнения, выполненный в виде M элементов сравнения, первый коммутатор, первый триггер, первый элемент индикации и блок управления, введены группа из M блоков разделительных элементов, элемент И, второй блок сравнения, выполненный в виде M элементов сравнения, два элемента ИЛИ, второй коммутатор, второй триггер и второй элемент индикации, а эталонный логический блок выполнен в виде N однотипных с контролируемым логических узлов. 1 з.п. ф-лы, 2 ил.

I

s

Г

ILM.J

с Г SS

ч

S3

fc:

cxj Csj

I

ra

tn

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1277118A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-10-24—Подача