Изобретение относится к вычислиельной технике и может быть использовано в автоматизированных системах управления для сопряжения процессо- ров.

Целью изобретения является повьппе- ние надежности устройства за счет соращения аппаратурных затрат при форировании адреса ячейки общей памяти, д

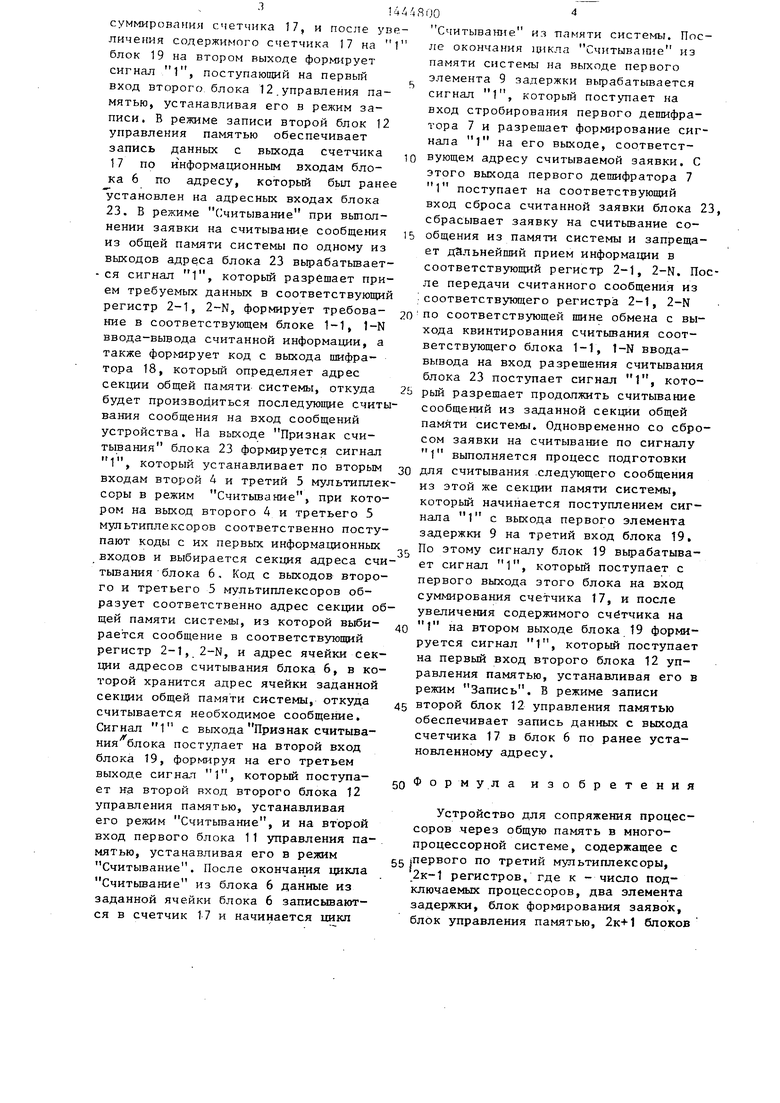

На чертеже представлена функциональная схема устройства для сопряжения процессоров.

Устройство содержит N блоков ввода вывода 1-1-1-N, N входных регистров 15 2-1-2-N, первый-третий мультиплексоы 3-5J блок 6 оперативной памяти, первый и второй дешифраторы 7,8| первый и второй элементы 9, 10 задержки, ервый и второй блоки 11, 12 управ- 20 ления памятью, каждый из которых соержит элемент ИЛИ 13, триггер 14, элемент 15 задержки, одновибратор 16, счетчик 17, шифратор 13, блок 19 синхронизации, состоящий из элементов 25 ЛИ 20, 21 и элемента 22 задержки, блок 23 формирования заявок.

Устройство работает в .режимах Запись и Считывание. В режиме За- пись данные, которые необходимы за- 30 писать в общую память системь, поступают в блоки ввода-вывода 1-1-1-N под управлением соответствующего процессора системы, что сопровождается выработкой сигнала 1 по выходу кви- тирования записи соответствующего блока ввода-вьшода.

С информационных выходов блоков ввода-вывода данные поступают на информационные входы первого мульти- 40 плексора 3, При выполнении заявки на запись сообщения в общую память системы по выходу адреса записываемой заявки блока 23 формирования заявок вырабатывается сигнал 1, j который разрешает прохождение требуемых данных на выходы первого мультиплексора 3 и втооые информационные входы второго 4 и третьегоi5 мультиплексоров. На выходе признака запи- . си блока 23 формируется сигнал 1, который устанавливает второй 4 и третий 5 мультиплексоры в состояние Запись, при котором на выходы этих мультиплексоров поступает информация -. с их вторых информационньк входов. Код с выхода второго мультиплексора 4 образует адрес заданной секции блока 6, в которую производится запись данных, поступающих с пыходов первого мультиплексора. 3 на выход сообщений устройства. Код с выхода третьего мультиплексора 5 содержит адрес ячейки памяти в заданной секции блока 6, по которому производится считывание из блока 6 в счетчик 17, а потом запись данных в блок 6, поступающих с выходов счетчика 17 на выход устройства, адрес ячейки секции общей памяти системы. Данные, считываемые с информационных выходов блока 6 за- письтаются по информационным входам в счетчик 17 и представляют собой по содержанию адрес ячейки в заданной секции памяти системы, куда записываются сообщения с выхода сообщений устройст)за.

После окончания цикла считывания из блока 6, который формируется вторым блоком 12 управления памятью (из блока 6 :в счетчик 17 записывается содержимое ячейки памяти секции адресов записи блока 6), начинается цикл з аииси в общую память системы, которьм формируется первым блоком 11 управления памятью. Величина задержки цикла записи в общую память системы определяется элементом задержки в первом блоке управления памятыо После око.нчания дакла записи в общую память системы с выхода второго элемента 10 задержки вырабатьшается сигнал 1, которьй поступает на вход стробирования второго дешифратора и разрешает формирование сигнала 1 на одном из его выходов, соответствующего адресу секции, общей памяти системы, куда записывается сообщение. С выхода дешифратора 8 Iсигнал 1 поступает на соответствующий вход сброса записываемой заявки блока 23 для сброса признака заявки на з апись сообщения в общую память системы и на соответствующий вход разрешения записи соответствующего, блока ввода-вывода 1-1-1-N. После окончания цикла записи в общую память системы параллельно со сбросом записанной заявки осуществляется процесс подготовки записи следующего сообщения в эту же секцию общей памяти системы,, который начинается поступлением сигнала 1 с выхода второго элемента 10 задержки на четвертый вход блока 19 синхронизации. По этому сигналу блок 19 на первом выходе формирует сигнал 1, поступающий на вход

суммирования счетчика 17, и после ув личения содержимого счетчика 17 на блок 19 на втором выходе формирует сигнал 1, поступающий на первьш вход второго блока 12.управления памятью, устанавливая его в режим записи. В режиме записи второй блок 12 управления памятью обеспечивает запись данных с выхода счетчика 17 по и нформационным входам блока 6 по адресу, который был ране установлен на адресных входах блока 23. В режиме ( читывание при выполнении заявки на считывание сообщения из общей памяти системы по одному из выходов адреса блока 23 вырабатьшает- ся сигнал 1, который разрешает прием требуемых данных в соответствующий регистр 2-1, 2-N, формирует требование в соответствующем блоке 1-1, 1-N ввода-вывода считанной информации, а также формирует код с выхода шифратора 18, который определяет адрес секции общей памяти системы, откуда будет производиться последующие считывания сообщения на вход сообщений устройства. На выходе Признак считывания блока 23 формируется сигнал 1, который устанавливает по вторым входам второй 4 и третий 5 мультиплексоры в режим Считьшание, при котором на выход второго 4 и третьего 5 мультиплексоров соответственно поступают коды с их первых информационных входов и выбирается секция адреса считывания блока 6. Код с выходов второго и третьего 5 мультиплексоров образует соответственно адрес секции общей памяти системы, из которой выбирается сообщение в соответствующий регистр 2-1, 2-N, и адрес ячейки секции адресов считывания блока 6, в которой хранится адрес ячейки заданной секции общей памяти системы, откуда считывается необходимое сообщение. Сигнал 1 с вькода Признак считыва- ния блока поступает на второй вход блока 19, формируя на его третьем выходе сигнап 1, который поступает wa второй вход второго блока 12 управления памятью, устанавливая его режим Считывание, и на второй вход первого блока 11 управления памятью, устанавливая его в режим Считывание. После окончания цикла Считывание из блока 6 данные из заданной ячейки блока 6 записываются в счетчик 17 и начинается цикл

ОО

Считывание из памяти системы. Пос- ле окончания )ц1кла Считыва1ше из памяти системы на выходе первого элемента 9 задержки вырабатывается сигнал 1, который поступает на вход стробирования первого дешифратора 7 и разрешает формирование сигнала 1 на его выходе, соответствующем адресу считываемой заявки. С этого выхода первого дешифратора 7 1 поступает на соответствующий вход сброса считанной заявки блока 23, сбрасывает заявку на считьтание сообщения из памяти системы и запрещает дальнейший прием информации в соответствующими регистр 2-1, 2-N. После передачи считанного сообщения из соответствунлцего регистра 2-1, 2-N

по соответствующей шине обмена с выхода квинтирования считывания соответствующего блока 1-1, 1-N ввода- вывода на вход разрешения считывания блока 23 поступает сигнал 1, который разрешает продолжить считывание сообщений из заданной секции общей памяти системы. Одновременно со сбросом заявки на считывание по сигналу 1 выполняется процесс подготовки

для считывания .следующего сообщения из этой же секции памяти системы, который начинается поступлением сигнала 1 с выхода первого элемента задержки 9 на третий вход блока 19,

По этому сигналу блок 19 вырабатывает сигнал 1, который поступает с первого выхода этого блока на вход суммирования счетчика 17, и после увеличения содержимого счётчика на

1 на втором выходе блока 19 формируется сигнал 1, который поступает на первый вход второго блока 12 управления памятью, устанавливая его в режим Запись. В режиме записи

второй блок 12 управления памятью обеспечивает запись данных с выхода счетчика 17 в блок 6 по ранее установленному адресу.

Фор мул а изобретения

Устройство для сопряжения процессоров через общую память в многопроцессорной системе, содержащее с первого по третий мультиплексоры, 2к-1 регистров, где к - число подлючаемых процессоров, два элемента адержки, блок формирования заявок, блок управления памятью, 2к+ блоков

5U4A8006

ввода-вьшода, первый и второй дешиф- мяти устройства и подключен к инфор- раторы, входы-выходы сообщений блоков ввода-вывода являются входами-выходами шин обмена устройства, выходы сомационным входам блока оперативной памяти, информационные выходы которо го подключены к информационны входа счетчика, счетный вход которого подключен к первому выходу блока синхронизации, второй и третий выходы которого подключены соответственно к

общений блоков ввода-вьтода подключв ны к информационным входам первого мультиплексора, вькод которого является выходом сообщений устройства, выходы регистров подключены к входам сообщений соответствующих блоков ввода-вьшода, выходы квитирования записи и считывания которых подключены соответственно к входам заявок на запись и входам разрещения считывания блока формирования заявок, выходы второго дешифратора подключены к входам сброса записанной заявки блока формирования заявок и к входам раз мяти устройства и подключен к инфор-

мационным входам блока оперативной памяти, информационные выходы которого подключены к информационны входам счетчика, счетный вход которого подключен к первому выходу блока синхронизации, второй и третий выходы которого подключены соответственно к

.первому и второму входам второго блока управления памятью, выходы которого подключены к входам режима и строба блока оперативной памяти, адресные входы которого подключены к выхоходам третьего мультиплексора и

выходам признака записи блока формирования заявок, выходы адреса считывания заявки которого.подключены к соответствующим входам разрешения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1988 |

|

SU1557570A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1986 |

|

SU1388881A2 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| СИСТЕМА УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ДОКУМЕНТООБОРОТОМ ИНФОРМАЦИОННО-МАРКЕТИНГОВОГО ЦЕНТРА | 2004 |

|

RU2260843C1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для ввода информации | 1986 |

|

SU1372317A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1986 |

|

SU1403070A1 |

| Устройство для обмена информацией | 1989 |

|

SU1644149A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

Изобретение позволяет реализовать многопроцессорные системы с высоким быстродействием за счет организации асинхронного обращения процессоров через общую память. Целью изобретения является повышение надежности устройства Это достигается тем, что в устройстве вместо 2к+1 счетчиков адреса, где к определяется количеством подключаемых к устройству процессоров, введены блок оперативной памяти емкостью 2к+1, счетчик, второй блок управления памятью, блок синхронизации и шифратор. 1 ил. а S (Л

решения записи соответствующих блоков 20 передачи блоков ввода-вывода, к вхо- ввода-вьшода, выходы первого дешифра дам стробирования соответствующих тора подключены к входам сброса считанной заявки блока формирования заявок, выходы признака записи и признарегистров и к информационным входам шифратора, выходы которого подключены к первым информационным входам

ка считывания блока формирования зая- 2Ь второго и третьего мультиплексоров.

вок подключены соответственно к.первому и второму входам блока управления памятью и соответственно через первый и второй элементы задержки - к входам стробирования первого и второго дешифраторов соответственно, первый и второй выходы блока управлени памятью являются выходами режима и стробирования общей памяти устройства соответственно, выходы разрядов адреса, выходы первого мультиплексора подключены к информационным входам второй группы второго мультиплексора, выходы которого подключены к входам первого и второго дешифраторов и являются, выходами группы разрядов адреса секции общей памяти устройств, о тличающееся тем что, с целью повышения надежности за счет сокращения аппаратурных затрат при формировании адреса ячейки общей памяти, в него введены сметчик, блок оперативной памяти, второй блок управления памятью, блок синхронизации и шифратор, выход счетчика является выходом адреса ячейки общей папередачи блоков ввода-вывода, к вхо- дам стробирования соответствующих

регистров и к информационным входам шифратора, выходы которого подключены к первым информационным входам

вторые информационные входы второго и третьего мультиплексоров подключены к вых;оду соббщений устройства, первый, второй, третий и четвертый входы блока синхронизации соответственно подключены к выходам признака . записи и признака считывания блока формирования заявок и к выходам первого и второго элементов задержки, g вход сообщений устройства подключен к информационным входам регистров, причем блок синхронизации содержит два элемента ИЛИ и элемент задержки, . первый и второй входы первого элемен- ) та ИЛИ являются первым и вторым входами блока синхронизации, первый и второй входы второго элемента ИЛИ являются третьим и четвертым входами блока синхронизации, выход второго элемента ШШ подключен к входу элемента задержки и является первым выходом блока синхронизации, выход элемента задержки является вторым выходом блока синхронизации, выход первого элемента ИЛИ является третьим вы- зодом (элока синхрониза Ц{И,

5

0

| Патент США | |||

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 1972 |

|

SU425314A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1012232A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-03-18—Подача