ходов блока, выход входного коммутатора команды соединен с первым входом регистра команды, второй вход и с первого.по шестой выходы являются „соответственно пятым входом, пятым, шестым, четвертым, первым , BTO-I рым и третьим выходами блока, а седьмой выход регистра команды соединен с первым входом выходного коммутатора команды, выход входного коммутатора слова соединен с входом регистра слова, выход которого является восьмым выходом блока, выход входного коммутатора управления coe-динеНС входом усилителя, выход которого является седьмым выходом блока, первый, вход выходного коммутатора слова, первый и четвертый входы выходного коммутатора управления являются соответственно шестым, четвертым и третьим входёьми блока, вторые и третьи входы выходных коммутаторов команды, слова и управления объединены и являются .соответственно вторым и первым выходами блока.

3. Устройство по п. 1, отличающееся тем, что блок управления содержит три усилителя, пять элементов И, шесть элементов ИЛИ, семь элементов задержки, регистр кода операции,. причем первые входы первого, второго элементов И и входы первого и второго усилителей, вторые входш первого и второго элеентов И, а также вход третьего усиителя являются соответственно третьим, четвертым и пятым входами лока выход первого элемента И оединен с входом первого элемента задержки и первым входом первого элемента ИЛИ, выход которого соеинен с входом регистра кода операий, выход первого элемента задержи соединен с первым входом второго элемента ИЛИ и входом третьего элемента задержки, выход которого соединен с первым входом третьего элемента ИЛИ, выход второго элемента И

.соединен с вторым входом первого элемента ИЛИ и входом второго элемента задержки, выход которого соединен с вторым входом второго элемента ИЛИ и входом четвертого элемента .задержки, выходом соединенного с вторим входом третьего элемента ИЛИ, выходы первого элемента задержки, второго и третьего элементов .ИЛИ, а также регистра кода операций явля- ются вторым, первым,, четвертым и третьим выходами блока, выход первого усилителя соединен с первым входом пятого элемента И, выход второго усилителя соединен с первыми входами третьего и четвертого элементов И, второй вход третьего элемента И и второй вход пятого элемента И, а также второй вход четвертого элемента И являются соответственно первым и вторым входами блока, выход третьего элемента И соединен с первыми входами четвертого и пятого.элементов ИЛИ, выход четвертого элемента И соединен с входом пятого элемента задержки, выходом соедин,енного с первым входом шестого элемента ИЛИ,выход пятого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход третьего усилителя соединен с входом шестого элемента задержки, выход которого подключен к второму входу шестого элемента ИЛИ и входу седьмого элемента задержки, выходом соединенного с третьим входом четвертого и вторим входом пятого элементов ИЛИ, выходы четвертого элемента И, четвертого и шестого элементов ИЛИ являются соответственно пятым, шестым и седьмым выходс1ми блока, выходы пятого элемента задержки, пятого элемента ИЛИ и пятого элемента И являются соответственно десятым, девятым и восьмым выходами блока, выход шестого элемента задержки является одиннадцатым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1015367A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1013937A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1976 |

|

SU983714A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

1. МНОГОУРОВНЕВОЕ УСТРОЙСТВО ДЛЯ КОММУТАЦИИ ПРОЦЕССОРОВ В МНОГОПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержащее на каждом уровне группы модулей коммутации, в каждой из которых модули коммутации соединены шинами связи по принципу каждый с каждым, каждый модуль коммутации нижнего уровня соединен шинами связи с процессорами, п групп модулей коммутации объединены в блоки, отличающееся тем, что, с целью повышения живучести системы и увеличения коэффициента использования оборудования, каждый модуль коммутации каждой группы соответствующего блока каждого уровня соединен, шинами связи с соответствующими модулями коммутации соответствующих групп соответствующего блока более высокого уровня, модули коммутации казедой группы которого соединены шинами связи с соответствующими модулями коммутации всех групп соответствующего блока более ниэкого уровня/ причем ксмкдый модуль коммутации содержит блок связи,, память адресов свободных модулей к коммутации и процессоров, блок управления память занятости модулей коммутации и процессоров, буферную память, причем группа входов и выходов блока связи соединена шинами связи с процессорами либо дополнительными модулями более низкого,более высокого или этого же уровня, первые четыре выхода блока связи соединены соответственно с первымвходом памяти адресов свободных модулей коммутации и процессоров и с первого по третий входами памяти занятости модулей коммутации и процессоров , с четвертого по седьмой входы и первый, второй выходы которой соединены соответственно с первого по четвертый выходами и первым, вторым входами блока управления, с пятого по седьмой выходы которого соединены с вторым, третьим и четвертым входами памяти адресов свободных (Л модулей-коммутации и процессоров, пятый вход и первый, второй выходы которого соединены соответственно с третьим выходом памяти занятости модулей коммутации и первым, вторым входами блока связи, третий, четвертый и пятый входы которого соединены соответственно с восьмым, девятым и десятым выходами блока управления, с третьего по пятый входы и го to одиннадцатый выхрд которого соединены соответственно с пятого по седьмой выходами блока связи и с ы to первым входом буферной памяти, второй вход и выход которой соединены соответственно с восьмым выходом и шестым входом блока связи. 2. Устройство по п. 1, отличающееся тем, что блок связи содержит входной коммутатор команды, входной коммутатор слова, входной коммутатор управления, регистр команды, регистр слова, усилитель, выходной коммутатор команды, выходной коммутатор слова, выходной коммутатор управления, причем входы входных и выходы выходных коммутаторов команды, слова и .управления образуют группу входов и группу вы

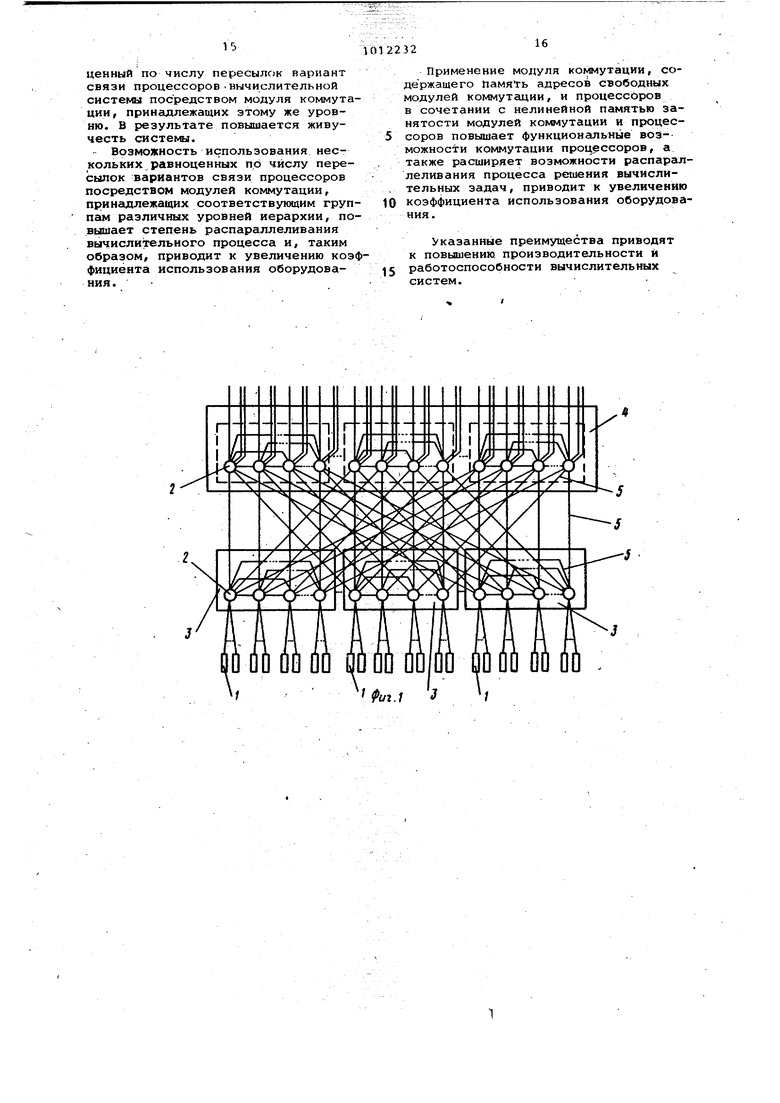

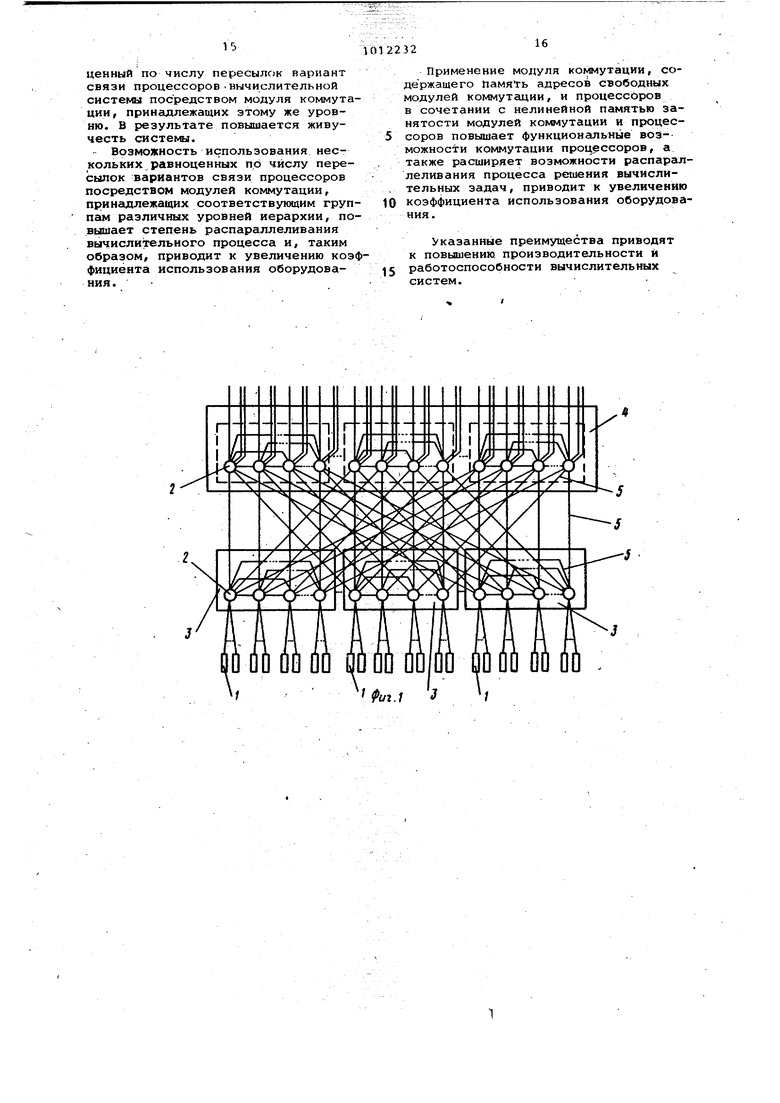

Изобретение относится к вычисли- тельной технике и может быть использовано при построении высокопроизводительных многопроцессорных вычислительных .систем.

Известно многоуровневое устройство для коммутации процессоров в многопроцессорной системе, содержа-, щее на каждом уровне группы модулей коммутации, соединенные через шины связи с соответствующим модулем коммутации более высокого уровня, а модули коммутации каждой группы соединены между собой шинами связи по кольцу tl

Недостатками известного устройства являются низкий коэффициент использования оборудования, определяемый ограничением связей модулей, принадлежащих одной группе, только связями по кольцу и ограниченными связями модулей коммутации, принадлежащих различным уровням, а также низкая живучесть вследствие того, что неисправность любого модуля коммутации приводкт к отключению соответствующей группы модулей коммута ции. В результате уменьшается производительность системы. Наиболее близким к предлагаемому является многоуровневое устройство для коммутации процессоров в многопроцессорной вьачислительной системе содержащее на каждом уровне группы модулей коммутации, в каждой из которых модули коммутации соединены между собой шинами связи по принципу каждый с каждым, каждый модуль коммутации нижнего уровня соединен шинами .связи с процессорами, а п групп модулей коммутации объединены в блоки 2 3. Недостатками такого устройстгва для коммутации процессора являются низкий коэффициент использования оборудования вследствие ограничений на связи между модулями, принадлежащим разным уровням, и низкая живучесть, определяемая, тем, что выход из строя некоторого модуля коммутации не позволяет использовать в составе вычислительной системы соответствукяцую группу модулей коммутации (процессоров). Это приводит к снижению производительности системы. Цель изобрете ния - повышение живучести многопроцессорной вычислительной системы. . Поставленная цель достигается тем, что в- многоуровневом устройстве для коммутации процессоров в мно гопроцессорной вычислительной системе, содержащем на каждом уровне группы модулей коммутации, в каждой из которых модули коммутации соединены по принципу каждый с каждым, каждый модуль коммутации нижнего уровня соединен,шинами связи. с процессорами, п групп модулей коммутации объединены в блок, кажды модуль коммутации каждой группы соответствующего блока каждого уровня соединен шинами связи с соответству ющими модулями коммутации соответствующих групп соответствунндего блока более высокого уровня, модули коммутации каждой группы которого соединены шинами связи с соотве ствующими модулями коммутации всех групп соответствующего блока более низкого уровня, причем каждай модуль коммутации содержит блрк связи память адресов свободных модулей ко мутации и процессоров, блок управле лия, память занятости модулей коммутации и процессоров, буферную па мять , причем группа входов и выход блока связи соединена с шинами свя зи с процессорами либо дополнитель ными модулями коммутации более низ кого, более высокого или этого же уровня, первые четыре выхода блока связи соединены соответственно с первым входом памяти адресов свободных модулей коммутации и процессоров и с первого по третий входами памяти занятости модулей коммутации и процессоров, с четвертого по седьмой входы и первый, второй выходы которой соединены соответственно с первого по четвертый выходами и первым, вторым входами блока управленияс пятого по седьмой выходил которого соединены с вторым, третьим и четвертым входами памяти адресов свободных модулей коммутации и процессоров, пятый вход и первый, второй выходы которого соединены соответственно с третьим выходом памяти занятости модулей коммутации и первым, вторым входами блока связи, третий, четвертый и пятый входы которого соединены соответственно с восьмым, девятым и десятым выходами блока управления, с третьего по пятый входы и, одиннадцатый выход которого соединены соответственно с пятого по седьмой выходами блока связи и с первым входом буферной памяти,- второй вход и выход которого соединен соответственно с восьмым выходом и шестым входом блока связи. Кроме того, блок связи содержит входной коммутатор команды, входной коммутатор слова, входной коммутатор управления, регистр команды, регистр слова, усилитель, выходной коммутатор команды, выходной коммутатор слова, выходной коммутатор управления, причем входы, входных и выходы выходных коммутаторов команды слова и управления образуют группу входов и группу выходов блока, выход входного ко1«пиутатора команды соединен с первым входом регистра команды, второй вход и с первого, по шестой выходы которого являются соответственно пятьам входом, пятым, шестым, четвертым, первым, вторым и третьим выходами блока, а седьмой выход регистра команды соединен с первым входом выходного коммутатора команды, выход входного коммутатора слова соединен с входом регистра слова, выход которого является восьмым выходом блока, выход входного коммутатора управления соединен с входом усилителя, выход которого является седьмым выходом блока, первый вход выходного коммутатора слова, первый и четвертый входы выходного коммутатора управления являются соответственно шестым, четвертым и третьим входами блока, вторяле и третьи входы выходных коммутаторов команды, слова и управления объединены и являются соответственно вторым и первым входами блока. Блок управления содержит три усилителя, пять элементов И, шесть элементов ИЛИ, семь элементов задержки регистр кода операции, причем первые входы первого, второго злементов иИ входы первого и второго уси лителей, вторые входы первого и вто рого элементов И, а также вход третьего усилителя являются соответственно третьим, четвертым и пятым вх дами блока, выход первого элемента И соединен с входом первого элемент задержки и первым входом первого элемента ИЛИ, ,выход которого, соединен с входом регистра кода операций выход первого элемента задержки сое динен с первым .входом второго элемента ИЛИ и входом третьего элемента задержки, выход которого соединен с первым входом третьего элемен та ИЛИ, выход второго элемента И со дкнен с вторым входом первого элемента ИЛИ и- входом второго элемента задержки, выход которого соединен с вторым входом второго элемен та ИЛИ и входом четвертого элемента задержки, выходом соединенного с вторым входом третьего элемента ИЛИ выходы первого элемента задержки, второго и третьего элементов ИЛИ, а также регистра кода операций явля ются вторым, первым, четвертым и третьим выходами блока, выход первого усилителя соединен с первым входом пятого элемента И, выход вто рого усилителя соединен с первыми входами третьего и четвертого элеме тов И, второй вход третьего элемента И ивторой вход пятого элемента И, а также второй вход четвертого элемента И являются соответствен но первым.и вторым входами блока, выход третьего элемента И соединен с первыми входами четвертого и пято го элементов ИЛИ, выход четвертого элемента И соединен с входом пятого элемента задержки, выходом соединенного с первым входом шестого элемента ИЛИ, выход пятого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход третьего усилителя соединен с входом шестого элемента задержки, выход которого подключен к второму входу шестого элемента ИЛИ и входу седьмого элемента задержки, выходом соединенного с третьим входЪм четвертого и вторым входом пятого элементов ИЛИ, выходы четвертого элемента И, четвертого и шестого элементов ИЛИ являются соответственно пятым, шестым и седьмым выходами блока, выходы пятого элемента задержки, пятого элемента ИЛИ и пятого элемента И являются соответственно десятым, девятым и восьмым выходами блока, выход шестого элемента задержки являетсй одиннадцатым выходо блока. На фиг. 1 приведена структурная схема предлагаемого многоуровневого устройства для коммутации процессоров в многопроцессорной вычислительной системе; на фиг. 2 - структурная схема модуля коммутации; на фиг. 3 и 4 - структурная схема блока связи и функциональная схема устройства управления, такого модуля. MHoj oypoBHeBoe устройство для коммутации процессоров (фиг. 1) содержит процессор 1, модули 2 коммутации , группы 3 модулей коммутации, блок 4 модулей коммутации, шины 5 связи, соединяющие между собой мо;1уль коммутации и процессор, либо два модуля ком1 1утации, принадлежащих одной группе или соседним уровням. Модуль коммутации (фиг. 2) содержит блок б связи, память 7 занятости модулей коммутации и процессоров, память 8 адресов свободных модулей коммутации и процессоров, буферную память 9, блок 10 управления, шину 11, соединяющую первый выход памяти адресов свободных модулей коммутации и процессоров с первым входом блока связи, шину 12, соединяющую первый выход блока связи с первым входом памяти адресов свободных модулей коммутации и процессоров, шины 13, 14 и 15, соединяющие второй третий и четвертый выходы блока связи с первым, вторым, третьим входами памяти занятости модулей коммутации и процессоров соответственно, шины 16 - 19, соединяющие выходы блока управления с первого по четвертый с входами памяти занятости модулей коммутации и процессоров с четвертого по седьмой соответственно, шины 20 и 21, соединяющие первый и второй выходы памяти занятости модулей коммутации и процессоров соответственно с первым и вторым входами блока управления, шину 22,- соединяющую третий выход памяти занятости модулей коммутации и процессоров с пятым входом памяти адресов свободных модулей коммутации и процессоров, шины 22 - 25, соединя-. ющие выходы блока управления с пятого по седьмой с входами памяти адресов свободных модулей коммутации и процессоррв с второго по четвертый соответственно/ шину 26, соединяющую одиннадцатый выход блока управления с первым входом буферной памяти, шину 27, соединяющую восьмой выход блока связи с вторым входом буферной памяти, шину 28, соединяющую выход буферной памяти с шестым входом блока памяти, шину 29, соединяющую второй выход памяти адресов свободных модулей коммутации и процессоров с вторым входом блока связи, шину 30, соединяющую восьмой выход блока управления с третьим входом блока связи,-шины 31 - 35, соединяющие седьмой, шестой, пятый выходы и четвертый, пятый входы блока свяэй с пятым, четвертым, третьим входами и девятым, десятым выходами блока управления соответственно.

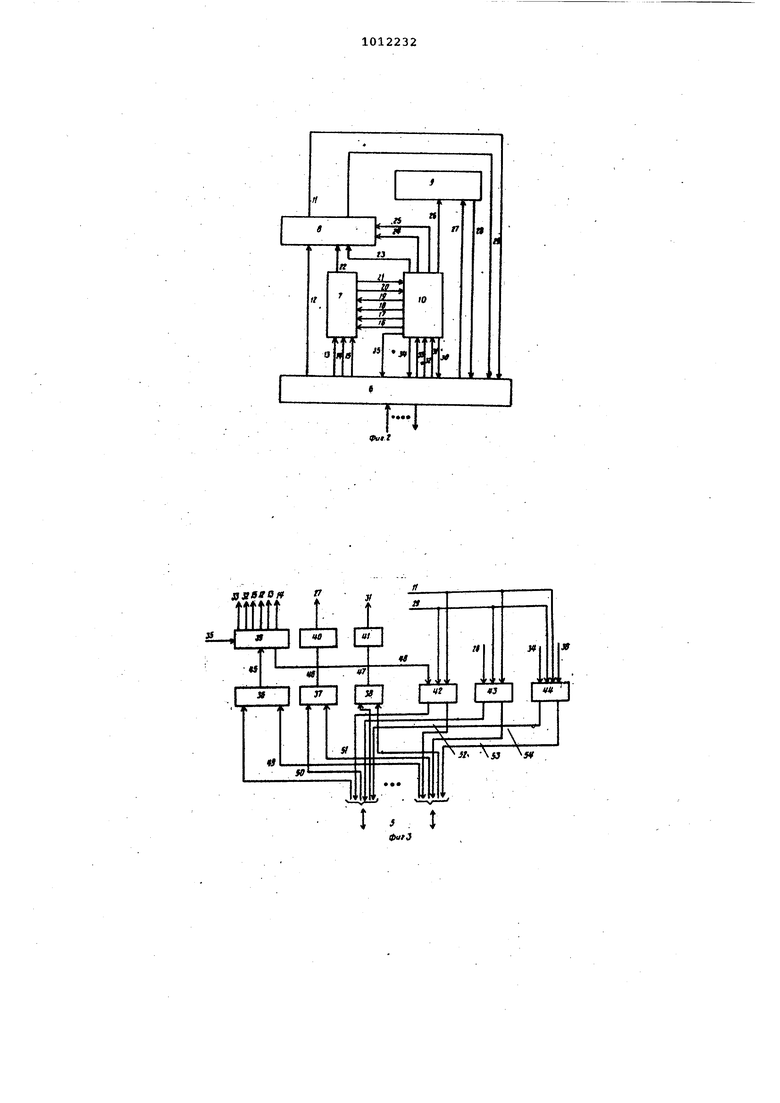

Блок связи (фиг. 3/ содержит вхоные коммутаторы команды 36, слова 37, управления 38, регистры команды 39 и слова 40, усилитель 41, выходные коммутаторы команды 42, слова 43, управления 44, шину 45, соединяющую выход входного коммутатора команды с первым входом регистра команды, шину 46, соединяющую выход входного коммутатора слова с входом регистра слова, шину 47, соединяющу выход входного коммутатора управления с входом усилителя, шину 48, , соединяющую выход регистра команды с первым входом выходного коммутатора.команды, ши«ы 49, 50 и 51 , соединяющие выходы процессоров (, модулей коммутации ), подключенных к входу данного модуля коммутации, соответственно с входами входных коммутаторов слова, команды, управления, шины 52, 53 и 54, соединяющие входы процессоров ( модулей коммутации ), подключенных к данному мо дулю коммутации, соответственно с выходами выходных коммутаторов команды,- слова, управления.

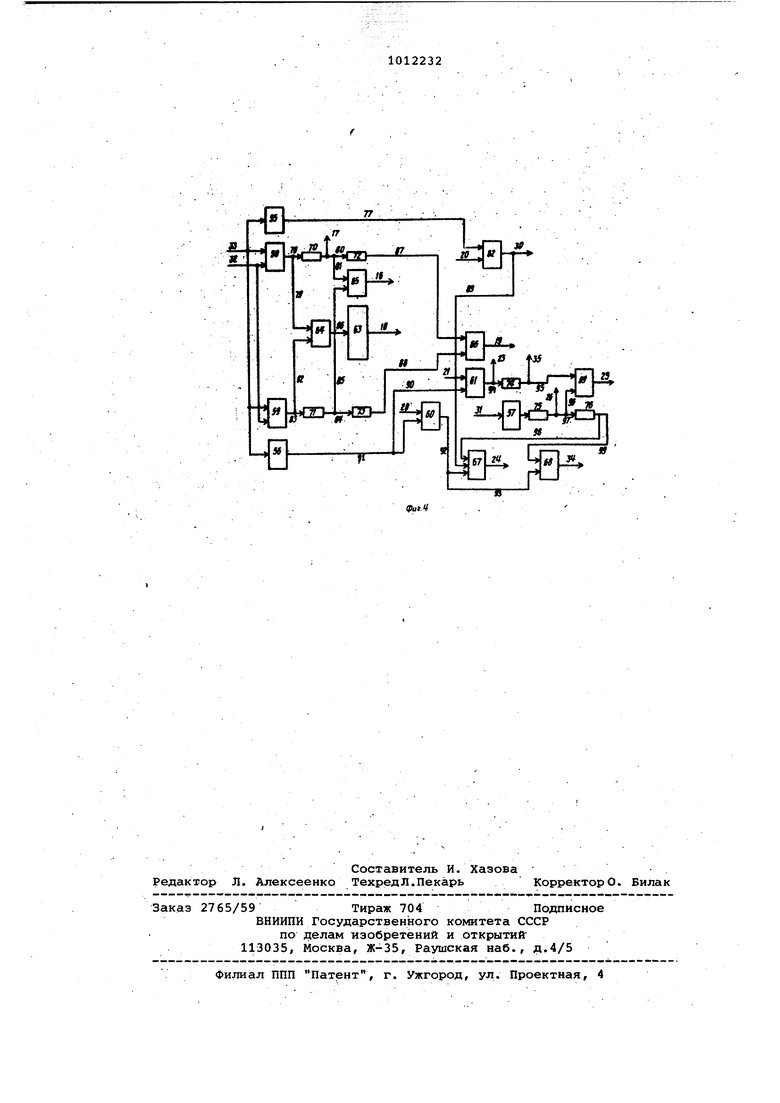

Блок управления (,фиг. 4) содержит однотипные усилители 55 - 57, .элементы И 58 - 62, регистр 63 кода операции, элементы ИЛИ 64 - 69, линии 70 -. 76 задержки, шину 77, соединяющую выход усилителя 55 с первым входом элемента И 62, шины 78 и 79, соединяющие -выход элемента И 58 с входом элемента 70 задержки и первым входом элемента 64 соответственно, шины 80 и 81, соединяющие выход элемента 70 задержки соответственно с входом элемента 72 задержки и первым входом элемента ИЛИ 65, шины 83 и 8-2, соединяющие выход элемента И 59 с входом элемета 71 задержки и вторым входом элемента ИЛИ 64, шины 84 и 85, соединякяцие выход элемента 71 задержки с входом элемента 73 задержки и вторым входом элемента ИЛИ 65, шину 86, соединяющую выход элемента ИЛИ 64 с входом регистра 63 кода операции, шину 87, соединякяцую выход элемента 72 задержки с первым входом, элемента ИЛИ 66, шину 88, соединяющую выходы элемента 73 эадержки 73 с вторым входом элемента ИЛИ 66, шину 89, соединяющую вы.ход элемента И 62 с вторым входом элемента ИЛИ 67i шины 90 и 91, соединяющие выход усилителя 56 с вторыми входами элементов 61 и 60 соответственно, шины 92 и 93, соединяющие выход элемента И 60 соответственно с третьим входом элемента ИЛИ 67 и вторым входом элемента ИЛИ 68, шину 94, соединяющую выход элемента, И 61 с входом элемета 74 задержки, шину 95, соединяющцю выходэлемента 74 задержки с первым входом элемента ИЛИ 69, шины 96 и 97, соединяющие выход линии 75 задержки соответственно с вторым входом элемента ИЛИ 69 и входом элемента задержки 76, шины 98 и 99, . соединяющие выход линии 76 задержки с первыми входами элементов ИЛИ 67 и 68 соответственно.

Работа предлагаемого многоуров0невого устройства для коммутации процессоров в многопроцессорной вычислительной системе состоит в обеспечении взаимодействия процессоров при решении одной задачи ( допускаю5щей распараллеливание процесса вычислений ) либо некоторого множества задач. Взаимодействие реализуется под действием .специальной операционной системы. В результате ее ра0боты процессоры, входящие в состав системы, объединяются в группы, структуры которых отвечают структуре данных и операторов класса решаемых задач. Системные средства ор5ганизации динамических связей процессоров системы содержатся в модулях коммутации и процессорах.

Работа модуля коммутации состоит в следующем. На модуль коммутации от связанных с ним процессоров пос0тупают команды. Эти команды могут быть двух типов, содержащие информацию о их свободе либо о запросе на связь.

Команды состоят из четырех полей

5 А, В, С, Д, где А - поле кода команды, В - поле признака свободы процессора данного типа, С - поле адреса процессора, Д - поле управляющей информации.

0

При поступлении команды, содержащей информацию о свободе, содержимое полей команды Л и Д с выхода блока 6 связи по шинам 33 и 32 связи поступает на блок 10 управления и ини5циирует его работу. Одновременно с этим содержимое полей В и С по шинам 13 и 15 связи поступает на память 7 занятости модулей коммутации и процессоров и, кроме того, содержимое поля С передается еще по каналу 12

0 в память 8 адресов свободных моду- лей коммутации и процессоров. Под действием управляющих сигналов, поступающих на. память 7 -из блока 10 управления по шинам 16 - 19 связи,

5 в памяти 7 запоминается содержимое полей В и С команды. После окончания записи в памяти 7 содержимого полей В и С выполняемой команды из памяти 7 в блок 10 управления по

0 шине связи 20 поступает соответствующий сигнал. В ответ на этот сигнал из блока 10 управления по шине 24 связи на память 8 поступает управляющий сигнал, под действием которого адрес процессора, предпстя5

вившего информацию о свободе, по шине 11 связи поступает в блок 6 связи. Одновременно с этим блок 10 управления выдает по шине 30 сигнал о окончании выполнения принятой команды. Этот сигнал через блок связи передается по адресу, хранящемуся в памяти 8, на процессор, предоставивший информацию о свободе. На этом выполнение данной команды заканчивается.

При поступлении команды, содержащей информацию о запросе на связь, так же, как и при поступлении команды, содержащей информацию о свободе , содержимое полей А и Д команды с выхода блока 6 связи по шинам 33 м 32 связи поступает на блок 10 управления и инициирует его работу, а содержимое поля С - адрес процессора по шине 12 связи из блока б поступает в память 8. Однако, в отличие от реализации команды о свободе, при реализации команды о запросе на связь.на память 7 передается только содержимое поля В - при,знак свободы процессора. Это содержимое передается по шине 14 связи. В соответствии с содержимым поля В в памяти 7 осуществляется ассоциатиный поиск адресов свободных процессоров требуемого типа. Поиск адресов выполняется под действием уп- равляющих сигналов, поступающих из блока 10 по шинам 16, 17 и 18 связи.

Если в памяти 7 занятости модулей коммутации и процессоров адрес свободного процессора найден, то этот адрес из памяти 7 по шине 22 передается в память 8 адресов свободных модулей коммутации и процессоров. Из этой же памяти 7 по шине 20 связи в блок 10 управления передается сигнал об окончании ассоциативного поиска. Под действием этого сигнала в блоке 10 управления вырабатываются сигналы, управляющие обменом информацией между процессором, пославшим запрос на связь и свободным процессором, адрес которого передан в память 8.

Обмен выполняется так. Из блока 10 управления по шине 24 связи на память 8. поступает управляющийсигнал, под действием которого адрес процессора, выставившего запрос на связь, поступает в блок связи по шине 11 связи. Из этого же блока 10 по шине 34 связи через блок 6 связи на процессор, выставивший запрос на связь, поступает сигнал, управляющий считыванием информации из этого процессора. Считанная информация, через блок 6 по шине 27 связи передается в буферную память 9. Одновременно с поступлением информации в буферную память 9 через блок 6 по шине 31| связи на блрк 10.

.улравления поступает управляющий сигнал. Под действием этого сигнала с задержкой на время, необходимое для принятия информации в буферную память 9, в блоке 10 управления формируется управляющий сигнал, поступающий по шине 25 связи на память 8 и обеспечивающий передачу адреса свободного процессора по шине 29 связи. По окончании передачи адреса свободного процессора в блок 6 в блоке 10 .формируется управляющий сигнал, обеспечивающий передачу . первого слова и информации, записанной в буферной памяти 9, через блок б в свободный функциональный процессор. Этот управляющий сигнал из блока 10 поступает на буферную память 9 по шине 26 связи, а информация в блок 6 и далее в свободный процессор передается из буферной памяти 9 по шине 28 связи. Через временной интервал, необходимый для принятия в свободный процессор первого слова, блок 10 управления выдает управляющие сигналы, инициирующие считывание последующих слов информации из процессора, выставившего запрос на связь, в выбранный свободный процессор.

Признаком окончания обмена, а следовательно, и команды в целом в случае удовлетворения запроса является отсутствие управляющего сиг{нал в шине 31 связи. В случае, когда обмен не закончен, сигнал в шине 31 присутствует всегда - именно этот сигнал и инициирует дальнейшую работу блока 10 для выполнения требуемых циклов обмена.

Если же запрос не удовлетворен, т.е. в памяти 7 не найден адрес свободного процессора, соответствукнций сигнал поступает из памяти 7 в блок 10 по шине 21 связи. В ответ на этот сигнал блок 10 выдает управляющий сигнал который по шине 23 связи поступает в память 8 и формирует в этой памяти адрес модуля коммутации более высокого уровня иерархии. Далее через временной интервал, необходимый для установления кода адреса в памяти 8, в блоке 10 управ|ления формируется управляющий сигнал обеспечивающий передачу адреса модуля коммутации более высокого уровня иерархии, хранящегося в памяти 8, в блок б. Этот управляклций сигнал передается по шине 25 связи, а информация об адресе передается из памяти 8 в блок 6 по шине 29 связи.

Под действием управляющего сигнала , поступающего из блока 10 на блок 6 по шине 35 связи, команда о запросе на связь передается в модуль коммутации более высокого уровня иерархии .

Процесс выполнения команды запроса на связь с модулем коммутации брлее высокого уровня иерархии аналогичен уже рассмотренному процессу выполнения команды запроса на связь с модулем коммутации данного уровня иерархии. В случае окончательного отрицательного ответа модуль коммутации последнего уровня иерархии .вырабатывает отрицательный ответ, кото1ялй передается запрашиваемому модулю.

Блок 10 связи работает следующим образом.

Команды от процессоров по шине 49 связи через коммутатор 36 и далее по шине 45 связи поступают в регистр 39 команды и хранятся в этом регистре в течение всего времени выполнения команды. Поля А и Д команды по каналам 33 и 32 соответственно поступают в блок 10 управления. Поле В команды по каналу 14 поступает на память 7. Поля В и С по шинам 13 и 15 связи соответственно поступают на память 7, а поле С по шине 12 связи поступает еще на память 8. Инициируется работа блока управления по выполнению команды..

При выполнении команды, содержащей информацию о свободе процессора определенного типа после окончания работы памяти 7, коммутатор 44 управляющей информации производит коммутацию управляющего сигнала, поступающего из блока 10 управления по шине 30 связи в процессор, предоставивший информацию о свободе. Адрес этого функционального процессора поступает на коммутатор 44 из памяти 8 по шийе 11 связи.

При выполнении командц: запрос на связь Ё случае, если в памяти 7 модуля коммутации найден адрес свободного процессора требуемого типа, происходит обмен информационными словами между процессором, поспавшим запрос насвязь, и свободным процессором. При обмене информацией управляющий сигнал,- под действием которого происходит считывание информации из процессора, выставившего запрос на связь, поступает из блока 10 управления модуля коммутации по шине 34 связи на коммутатор 44. Адрес этого процессора поступает на коммутатор 44 из памяти 8 по ,шине11 связи. Сигнал, поступающий на коммутатор 44 по шине 34 связи, проходит через этот коммутатор и по шине 54 связи поступает в требуемый процессор.

- Считываемое информационное слово из процессоре- по каналу 50 поступает на коммутатор 37 и далее по каналу 46 в регистр 40 слова. Из регистра 40 это слово, по шине 27 связи передается в буферную память 9 модуля коммутации. Одновременно с поступлением информационного слова в регистр 40 из процессора на 1 рммутатор 38 по шине 51 связи поступает управляющий сигнал, который из коммутатора 38 по шине 47 связи поступает на усилитель 41 и далее по

шине 31 связи в блок 10 управления.

Под действием управляющего сигнала, поступающего из блока 10 в буферную память 33 по шине 26 связи, информационное слово, .хранящееся в

o буферной памяти 9, по шине 28 связи передается на коммутатор 43, с :; оммутатора 43 по шине связи 53 - в свободный процессор. Адрес этого процессора передается на коммутатор 43

из памяти 8 по шине 29 связи.

В случае, если при выполнении команды запрос на связь адрес свободного процессора в памяти 7 данного модуля коммутации не найден, в памяти 8 этого модуля коммутации формируется адрес модуля коммутации

более высокого уровня иерархии..Этот адрес из памяти 8 поступает на коммутатор 42 по шине 29 связи. Под действием управляющего сигнала, поступающего из блока 10 управления по шине 35 связи, команда запрос на связь, хранящаяся в регистре 39, по шире 48 связипоступает на коммутатор 42, ас выхода этого ком0 мутаторй по шине связи 52 - в модуль коммутации более высокого уровня иерархий. I

Блок управления (фиг. 4) рабо-,

с тает следующим образом.

По шине 33 связи с блока 6 связи на элементы И 59 и 58, усилители 56 и 55 поступает содержимое поля А команды. По шине 32 связи на элементы И 59 и 58 поступает информация поля Д команды. При выполнении команды информация о свободе в соответствии с кодом выполняемой команды на выходе усилителя устанавливается разрешающий потенциал этой команды,

5 а управляющий сигнал проходит через элемент И 58. С выхода этого элемента по шине 79 связи через элемент ИЛИ 64 управляющий сигнал поступает в регистр 63 и устанавливает в этом

Q регистре код команды чтение по

признаку. С выхода регистра 63 код команды по шине 18 связи поступает в память 7 занятости модулей комму- . тации и процессоров. -Через время Т

е элемента 70 задержки после поступления управляющего сигнала в регистр 63 управляющий сигнал поступает в память 7 по шине 17 связи, а также по шине 16 связи через элемент ИЛИ 65. Временной интервал У равен

0 времени, необходимому для формирования кода в регистре 63. Через время Со через элемент ИЛИ 66 в память 7 поступает сигнал по шине 19 связи начала выполнения операции в

5 этом блоке. После окончании работы

памяти 7 в блок 10 управления (фиг. 3) поступает сигнал на элемен И 62. Так как на второй вход этого элемента поступает разрешающий потенциал с усилителя 55, управляющий сигнал поступает в блок б модуля коммутации по каналу 30, а в память 8 этого модуля - через элемент ИЛИ 67 по шине 24 связи. Под действием этих сигналов в процессор, предоставивший информацию о свободе, поступает сигнал об окончании выполнения даЕшой команды.

При выполнении команды запрос на связь управляющий потенциал формируется на выходе усилителя 56, а управляющий сигнал проходит -через элемент И 59. С выхода элемента И 5 по шине 82 связи через элемент ИЛИ

64управляющий сигнал поступает в регистр 63 и устанавливает в этом регистре код команды чтение по принаку. Через время Тд элемента 71 задержки управляющий сигнал поступает по шине 85 связи на элемент ИЛ

65и, пройдя через этот элемент, в память 7 по шине 16 связи. Временной интервал Т элемента 71 задержки равен временному интервалу

С элемента. 70 задержки. Через время элемента 73 задержки через , . элемент ИЛИ 66 в память 7 по каналу 19 поступает сигнал сначала выполнения операции в этом блоке. Временной интервал равен временному интервалу 2 .

Если в 11амяти 2 найдено слово с данным ассоциативным признаком, в этом блоке формируется сигнал окончания его работы, который поступает по шине 20. связи на элемент И 60 и проходит через него, так как на первом входе этого элемента имеется разрешающий потенциал, формируемый на выходе усилителя 56. Под действием сигнала, сформированного на выходе эл.емента И 60, происходит обмен информацией между процессором выставившим команду запрос на связь, и свободным процессором. Управление обменом реализуется так. Под действием управляющего сигнала, сформированного на выходе элемента И 60, в память 8 модуля коммутации поступает управляющий сигнал по шине 24 связи с выхода элемента ИЛИ 67, а также в блок 6 модуля коммутации по шине 45 связи с выхода элемента ИЛИ 68. Под действием этих управляющих сигналов происходит считывание информационных процессора, выставившего команду запг рос на связь.

Одновременно со считыванием информации из процессора, выставившего команду запрос на связь, управляющий сигнал поступает по шине 31 связи на усилитель 57. Через время Ту, необходимое для формирования кода считанного информационного слова в буферной памяти 9 (фиг. 2 ), на этот блок по шине 26 связи поступает управляющий сигнал. Управляющий сигнал поступает также память 6 модуля коммутации с выхода элемента ИЛИ 69 по шине 25 связи. Под действием управляющих сигналов, поступающих по шинам 25 и 26 связи, происходит передача информации из буферной Пс1мяти 9 модуля коммутации в свободный процессор, удовлетворяющий запрос.

Через временной интервал f g, необходимый для передачи информационного слова из буферной памяти 9 в свободный процессор, управляющие сигналы с выходов элементов ИЛИ 67 и 68 по шинам 24 и 34 связи соответственно снова поступают на память 8 и блок 6 связи модуля коммутации для организации нового цикла обмена информацией между процессором, выставившим запрос на связь, и свободным процессором, удовлетворяющим этот запрос.

Признаком окончания цикла обмена информации является отсутствие управляющего сигнала, приходящего из процессора по шине 31 связи.

Если же в памяти 7 не найдено слово, удовлетворяклцее требуемому признаку опроса, в этом блоке вырабатывается управляющий сигнал, поступающий на элемент И 61. Так как на первом входе этой схемы имеется разрешающий потенциал (этот потенциал поступает с выхода усилителя 56 по шине 91 связи ), на выходе элемента И 61 формируется управляющий сигнал. Этот управляющий сигнал поступает по шине 23 связи в память 8 и устанавливает в этой памяти код адреса модуля коммутации более высокого уровня иерархии. Через время Т элемента 74 задержки управляющий сигнал поступает в блок 6 модуля коммутации по шине 3-5 связи, а по каналу 25 в память 8 этого процессора.- Временной интервал (Необходим для формирования в памяти 8 кода адреса модуля коммутации более высокого уровня иерархии. I

Под действием управляющих сигна.лов, поступающих по шине 25 связи в память 8 и по шине 35 связи - в блок 6, данный модуль коммутации посылает команду запрос на связь в модуль коммутации более высокого уровня иерархии.

Изобретение позволяет получать следующие преимущества.

Применение предложенных межуровневых связей между модулями коммутации при выходе из строя модуля коммутации некоторого уровня иерархии позволяет использовать равноценный по числу пересылок вариант связи процессоров.вычислительной системы посредством модуля коммутации, принадлежащих этому же уровню. В результате повышается живучесть системы.

Возможность использования нескольких равноценных по числу пересылок вариантов связи процессоров посредством модулей коммутации, принадлежащих соответствующим группам различных уровней иерархии, повышает степень распараллеливания вычислительного процесса и, таким образом, приводит к увеличению коэффициента использования оборудования.

Применение модуля коммутации, содержащего Память адресов свободных модулей коммутации, и процессоров в сочетании с нелинейной памятью занятости модулей коммутации и процессоров повьииает функциональные воз-можности коммутации процессоров, а. также расширяет возможности распараллеливания процесса решения вычислительных задач, приводит к увеличению коэффициента использования оборудования.

Указанные преимущества приводят к повышению, производительности и работоспособности вычислительных

систем.

ГТТИй-.

VL

яявва a

ti

10

FT

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ОПТИЧЕСКИ ИЗМЕНЯЕМЫЙ ЭЛЕМЕНТ | 2003 |

|

RU2314210C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения металлического покрытия хрома на углеродном волокне для композиционных материалов триботехнического назначения | 2024 |

|

RU2830506C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1979-11-13—Подача