поступающие на выходы сообщений и ад- s«. выходы адреса секции общей памяти устреса секции общей памяти устройства, а также на адресные входы первого 3 и второго 4 блоков оперативной памяти. Блок синхронизации вырабатывает

ройства и адресные входы блоков 3 и 4. Блок 10 синхронизации вырабатывает , сигнал, который поступает на вход считывания блока 6, запуская первый

выходы адреса секции общей памяти устройства и адресные входы блоков 3 и 4. Блок 10 синхронизации вырабатывает , сигнал, который поступает на вход считывания блока 6, запуская первый

3 и второй 4 блоки на циклы считывания согласно установленным адресам как описано выше в режиме Запись.

В результате выполнения цикла считывания из общей памяти по заданному адресу по входу сообщений устройства осуществляется запись данных в соответствующий регистр 2 под управлением блока 5. По заднему фронту сигнала с выхода строба блока 5, который одновременно поступает на входы строба блоков 10 и 11 аналогично описанному выше в режиме Запись, блок 10 вырабатывает сигнал вычитания для счетчи- ка 8 и сигнал суммирования для счетчика 7. После увеличения содержимого первого 7 и уменьшения второго 8 счетчиков с выхода записи блока 10 на вход записи блока 6 поступает сигнал 1, который запускает циклы записи блоков 3 и 4 по ранее установленным адресам.

Формула изобретения

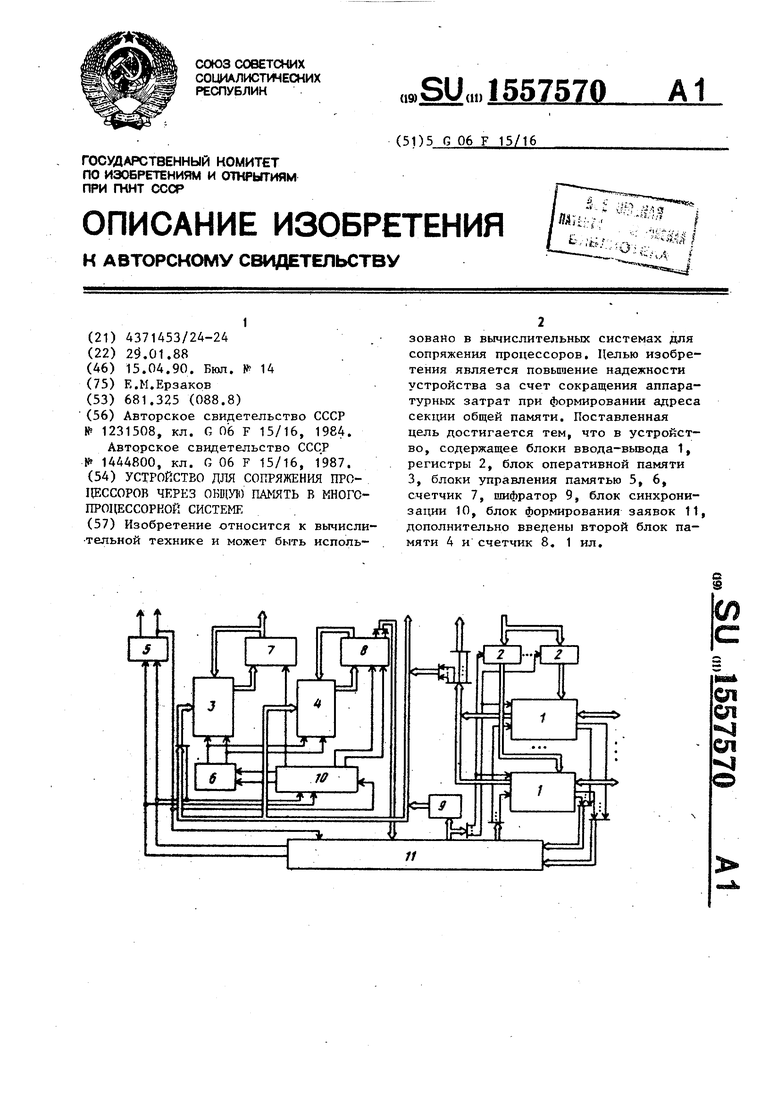

Устройство для сопряжения процессоров через общую память в многопроцессорной системе, содержащее N блоков ввода-вывода, N регистров, блок памяти, -первый и второй блоки управления памятью, первый и второй счетчики, шифратор, блок синхронизации и блок формирования заявок, информаг ционные входы-выходы блоков ввода- вдвода являются входами-выходами обмена устройства, выходы квитирования записи всех блоков ввода-вывода подключены соответственно к входам разрешения считывания с 1 по N-й блока формирования заявок, выходы адреса записи заявок с первого по N-й которого подключены к входам разрешения приема блоков ввода-вывода с первого по N-й соответственно, выходы квитирования утения которых подключены к входам заявки на запись блока формирования заявок, выходы адреса считывания заявок с первого по N-й которого подключены к входам разрешения передачи информации блоков ввода-вывода с первого по N-й,входам строби- рования регистров с первого по N-й и входам шифратора,информационные выходы которых подключены к одноименным входам блоков ввода-вывода с первого по N-и соответственно, информа-

0

5

0

5

ционные входы регистров являются вхо- дом сообщений устройства, выход приз- нака записи блока формирования заявок соединен с входом записи первого блока управления памятью и одноименным входом блока синхронизации, выход записи которого подключен к одноименному вхрду второго блока управления памятью, выходы режима и строба которого соединены с одноименными входами блока памяти, информационные выходы которого соединены с информационными входами счетчика, информационные выходы которого соединены с информационными входами блока памяти и являются выходом адреса ячейки секций общей памяти устройства, выход признака считывания блока формирования заявок соединен с входом считывания первого блока управления памятью, адресным входом первого блока памяти и одноименным входом считывания блока синхронизации, выходы считывания и суммирования которого подключены к одноименным входам второго блока управления памятью и счетчика соответственно, выходы режима и строба первого блока управления памятью являются од оименными выходами устройства, отличающееся тем, что, с целью повышения надежности за счет сокращения аппаратурных затрат при формировании адреса секции общей памяти, в него введены второй блок па мяти и второй счетчик, информационный выход которого соединен с одноименным входом второго блока памяти, информационный выход которого соединен с одноименным входом второго счетчика, управляющие выходы которого соединены с входом заявки на считывание блока формирования заявок, вход строба которого соединен с одноименными выходом первого блока управления памятью и входом блока синхронизации, выходы режима вычитания и режима суммирования которого соединены с входами вычитания и суммирования второго счетчика соответственно, выходы адреса блоков ввода-вывода через общую шину соединены с входами адреса блоков памяти, выходом шифратора и выходом ад0

5

0

реса секции общей памяти устройства, информационные выходы блока ввода- выхода через общую шину соединены с выходом сообщений устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1987 |

|

SU1444800A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения процессоров. Целью изобретения является повышение надежности устройства за счет сокращения аппаратурных затрат при формировании адреса секции общей памяти. Поставленная цель достигается тем, что в устройство, содержащее блоки ввода-вывода 1, регистры 2, блок оперативной памяти 3, блоки управления памятью 5, 6, счетчик 7, шифратор 9, блок синхронизации 10, блок формирования заявок 11, дополнительно введены второй блок памяти 4 и счетчик 8. 1 ил.

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1987 |

|

SU1444800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-04-15—Публикация

1988-01-29—Подача