Изобретение относится к импульсной технике и может использоваться в резервированных устройствах деления частоты, счета времени и счета им- пульсов.

Цель изобретения - повышение надежности за счет того, что при сбое одного из резервных каналов ( счетчиков импульсов ) производится полная коррекция информации сбившегося счетчика импульсов, а при отказе элементов одного резервного канала и сбое счетчика импульсов в другом производится фазирование счетчиков импуль- сов работоспособных резервных каналов, при этом максимальное время коррекции информации сбившегося счетчика импульсов, а также максимальное время фазирования счетчиков импульсов работоспособных резервных каналов . равно периоду следования импульсов синхронизации.

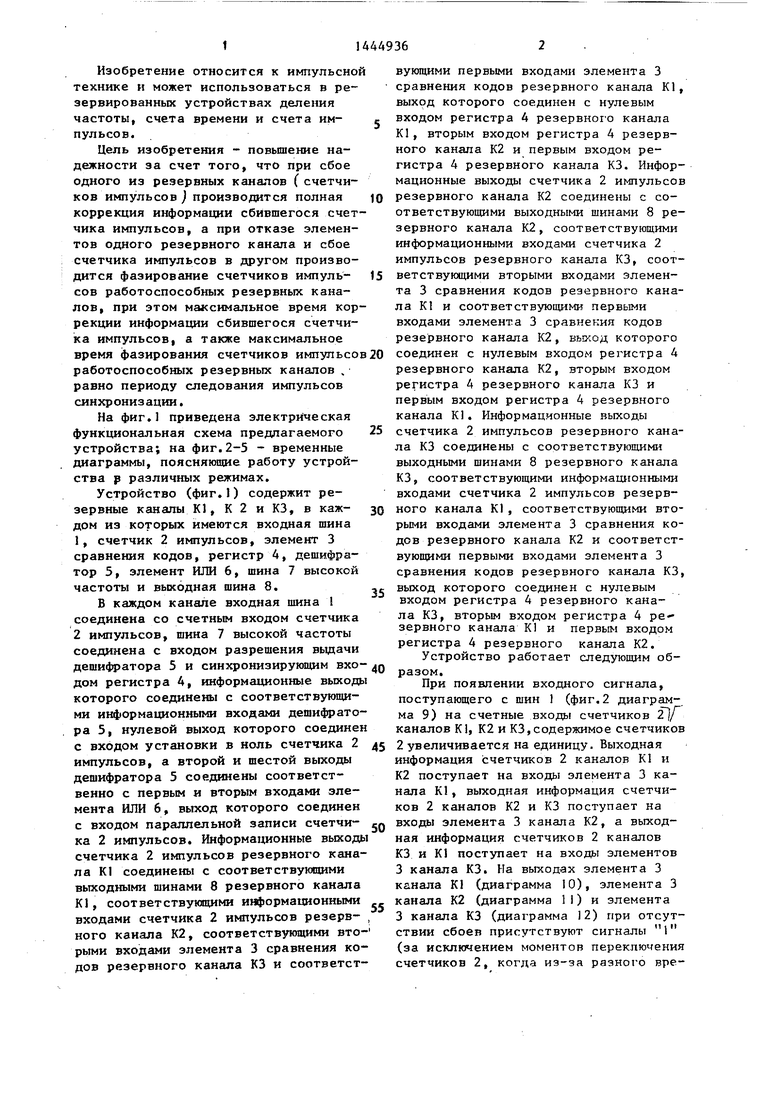

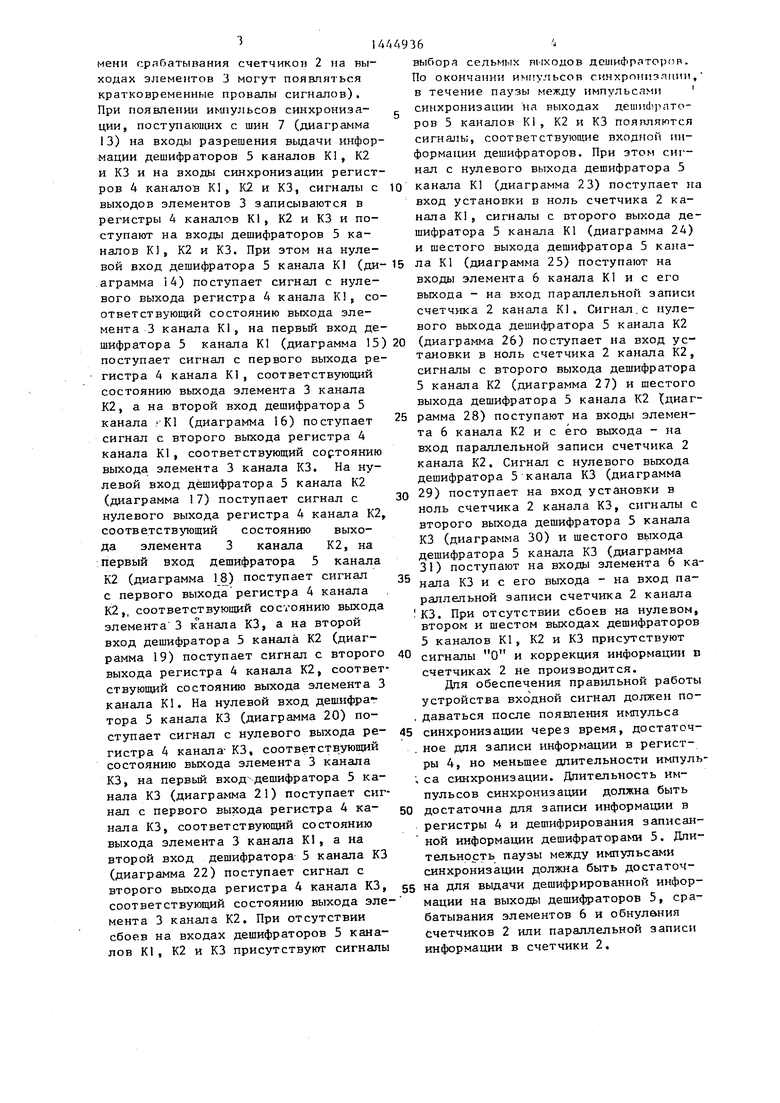

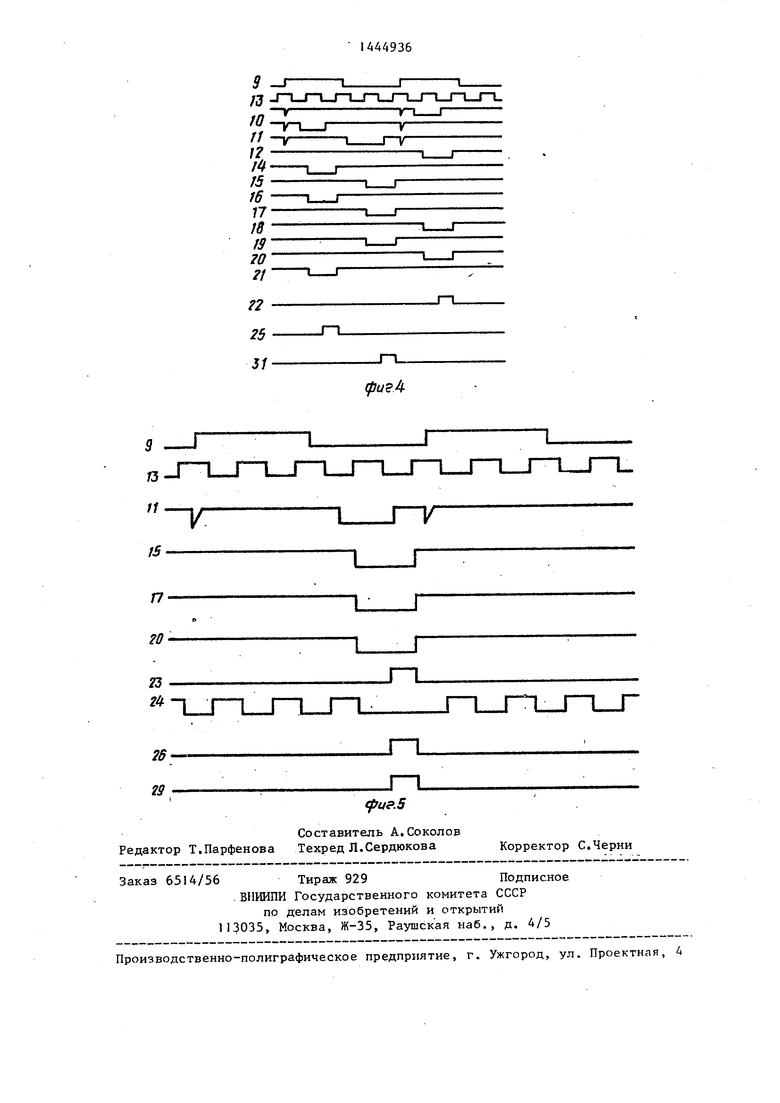

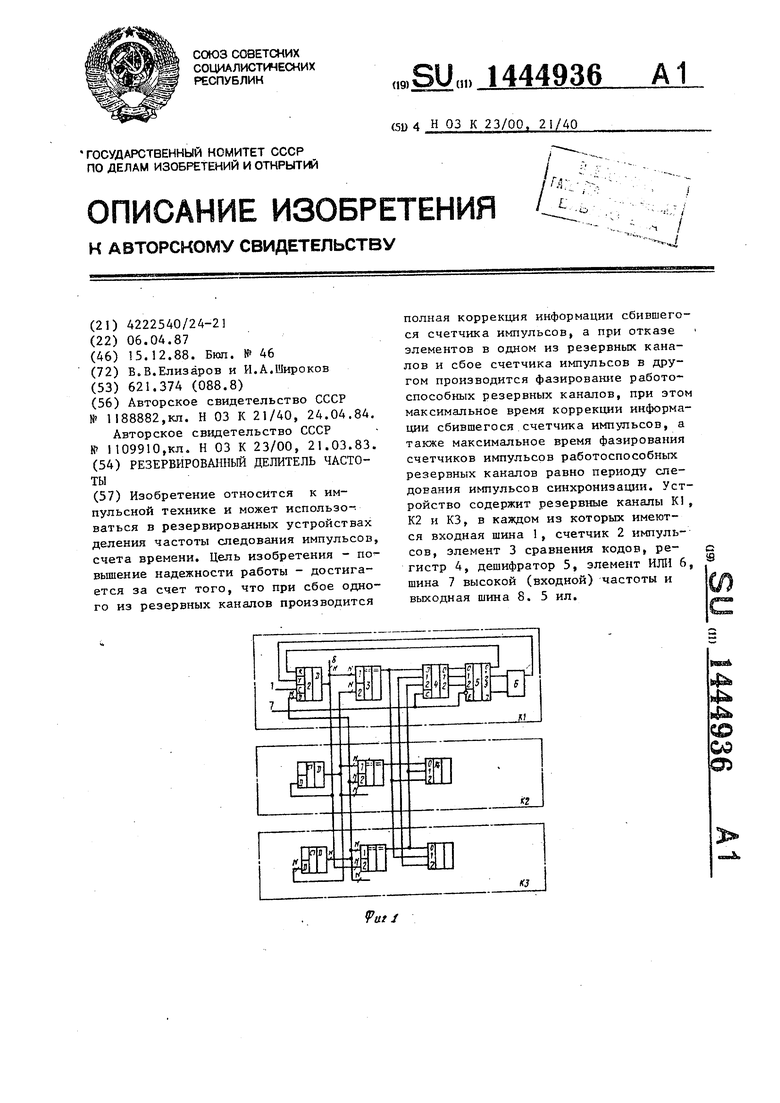

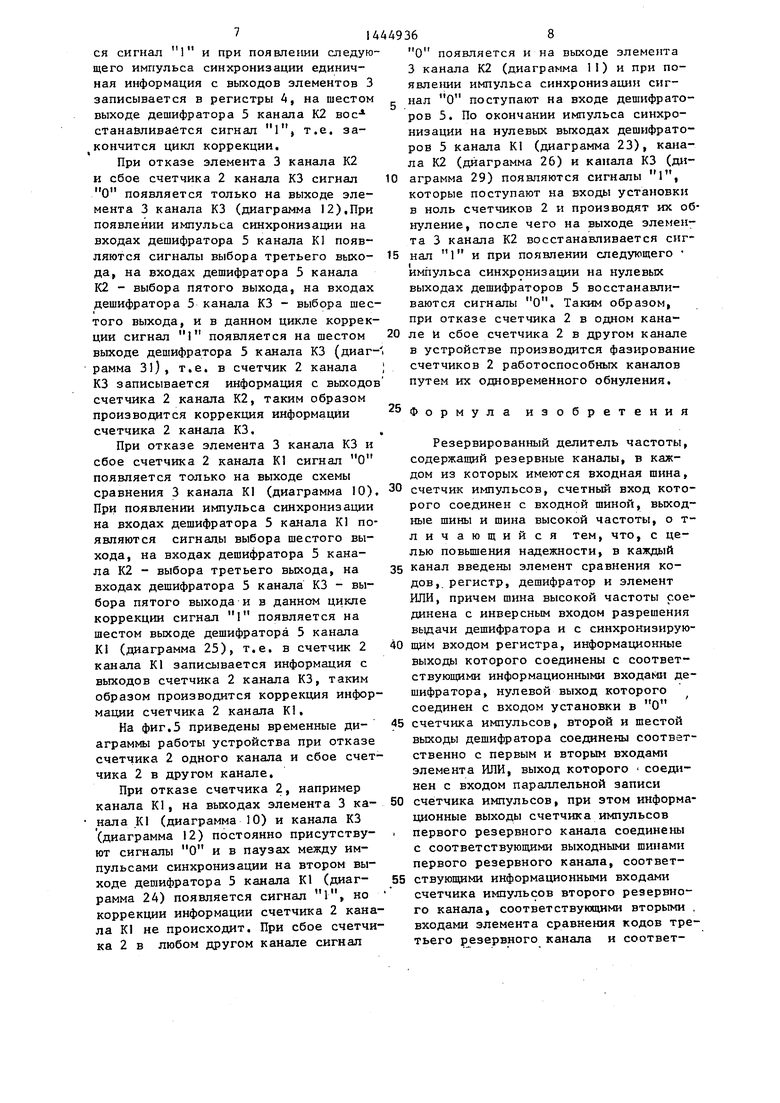

На фиг.1 приведена электрическая функциональная схема предлагаемого устройства; на фиг.2-5 - временные диаграммы, поясняющие работу устройства р различных режимах.

Устройство (фиг.1) содержит резервные каналы К1, К 2 и КЗ, в каж- дом из которых имеются входная шина 1, счетчик 2 импульсов, элемент 3 сравнения кодов, регистр 4, дешифратор 5, элемент ИЛИ 6, шина 7 высокой частоты и выходная шина 8.

В каждом канале входная шина соединена со счетным входом счетчика 2 импульсов, шина 7 высокой частоты соединена с входом разрешения выдачи дешифратора 5 и синхронизирующим вхо- дом регистра А, информационные выходы которого соединены с соответствующими информационными входами дешифратора 5, нулевой выход которого соединен с входом установки в ноль счетчика 2 импульсов, а второй и шестой выходы дешифратора 5 соединены соответственно с первым и вторым входами элемента ИЛИ 6, выход которого соединен с входом параллельной записи счетчи- ка 2 импульсов. Информационные выходы счетчика 2 импульсов резервного канала К1 соединены с соответствующими выходными шинами 8 резервного канала К1, соответствующими информационными входами счетчика 2 импульсов резерв- ного канала К2, соответствующими вторыми входами элемента 3 сравнения кодов резервного канала КЗ и соответст

5

О

Q з Q

5

вующнми первьми входами элемента 3 сравнения кодов резервного канала К1, выход которого соедннен с нулевым входом регистра 4 резервного канала К1, вторым входом регистра 4 резервного канала К2 и первым входом регистра 4 резервного канала КЗ. Информационные выходы счетчика 2 импульсов резервного канала К2 соединены с соответствующими выходными шинами 8 резервного канала К2, соответствующими информационными входами счетчика 2 импульсов резервного канала КЗ, соответствующими вторыми входами элемента 3 сравнения кодов резервного канала К1 и соответствующими первыми входами элемента 3 сравнения кодов резервного канала К2, вьжод которого соединен с нулевым входом регистра 4 резервного канала К2, вторым входом регистра 4 резервного канала КЗ и первым входом регистра 4 резервного канала К1. Информационные выходы счетчика 2 импульсов резервного канала КЗ соединены с соответствующими выходными шинами 8 резервного канала КЗ, соответствующими информационными входами счетчика 2 импульсов резервного канала К1, соответствующими вторыми входами элемента 3 сравнения кодов резервного канала К2 и соответст- вуюшими первыми входами элемента 3 сравнения кодов резервного канала КЗ, выход которого соединен с нулевым входом регистра 4 резервного канала КЗ, вторым входом регистра 4 резервного канала К1 и первым входом регистра 4 резервного канала К2.

Устройство работает следующим образом.

При появлении входного сигнала,

поступающего с шин 1 (фиг.2 диаграмма 9) на счетные входы счетчиков каналов К1, К2 и КЗ,содержимое счетчиков

2увеличивается на единицу. Выходная информация счетчиков 2 каналов KI и К2 поступает на входы элемента 3 канала К1, выходная информация счетчиков 2 каналов К2 и КЗ поступает на входы элемента 3 канала К2, а выходная информация счетчиков 2 каналов КЗ и К1 поступает на входы элементов

3канала КЗ. На выходах элемента 3 канала К1 (диаграмма 10), элемента 3 канала К2 (диаграмма 11) и элемента

3 канала КЗ (диаграмма 12) при отсутствии сбоев присутствуют сигналы 1 (за исключением моментов переключения счетчиков 2, когда из-за разного вре 1/

менн срабатывания счетчикои 2 на выходах элементов 3 могут появляться кратковременные провалы сигналов). При появлении икшульсов синхронизации, поступающих с шин 7 (диаграмма 13) на входы разрешения выдачи информации дешифраторов 5 каналов К1, К2 и КЗ и на входы синхронизации регистров 4 каналов К1, К2 и КЗ, сигналы с выходов элементов 3 записываются в регистры 4 каналов К1, К2 и КЗ и поступают на входы дешифраторов 5 каналов К, К2 и КЗ. При этом на нулевой вход дешифратора 5 канала К1 (диаграмма i4) поступает сигнал с нулевого выхода регистра 4 канала К, соответствующий состоянию выхода элемента 3 канала К1, на первый вход дешифратора 5 канала К1 (диаграмма 15) поступает сигнал с первого выхода регистра 4 канала К1, соответствующий состоянию выхода элемента 3 канала К2, а на второй вход дешифратора 5 канала уК (диаграмма 16) поступает сигнал с второго выхода регистра 4 канала К1, соответствующий состоянию выхода элемента 3 канала КЗ. На нулевой вход дешифратора 5 канала К2 (диаграмма 17) поступает сигнал с нулевого выхода регистра 4 канала К2, соответствующий состоянию выхода элемента 3 канала К2, на первый вход дешифратора 5 канала К2 (диаграмма ) поступает сигнал с первого выхода регистра 4 канала К2,, соответствующий состоянию выхода элемента 3 к анала КЗ, а на второй вход дешифратора 5 канала К2 (диаграмма 19) поступает сигнал с второго выхода регистра 4 канала К2, соответствующий состоянию выхода элемента 3 канала К1. На нулевой вход дешифратора 5 канала КЗ (диаграмма 20) поступает сигнал с нулевого выхода регистра 4 канала- КЗ, соответствующий состоянию выхода элемента 3 канала КЗ, на первьй вход дешифратора 5 канала КЗ (диаграмма 21) поступает сигнал с первого выхода регистра 4 канала КЗ, соответствующий состоянию выхода элемента 3 канала KI, а на второй вход дешифратора 5 канала КЗ (диаграмма 22) поступает сигнал с второго выхода регистра 4 канала КЗ, соответствующий состоянию выхода элемента 3 канала К2. При отсутствии сбоев на входах дешифраторов 5 каналов К1, К2 и КЗ присутствуют сигналы

4936

выбора седьмых пмходов дешифраторов. По окончании импульсов синхротшзяпии, в течение паузы между импульсами синхронизации на выходах дeшиd paтo- ров 5 каналов К1, К2 и КЗ пояпляются сигналы, соответствующие входной ми- формации дешифраторов. При этом сигнал с нулевого выхода дешифратора 5

0 канала К1 (диаграмма 23) поступает на вход установки в ноль счетчика 2 канала К1, сигналы с второго выхода дешифратора 5 канала К1 (диаграмма 24) и шестого выхода дешифратора 5 кана5 ла К1 (диаграмма 25) поступают на входы элемента 6 канала KI и с его выхода - на вход параллельной записи счетчика 2 канала К1. Сигнал.с нулевого выхода дешифратора 5 канала К2

0 (диаграмма 26) поступает на вход установки в ноль счетчика 2 канала К2, сигналы с второго выхода дешифратора 5 канала К2 (диаграмма 27) и шестого выхода дешифратора 5 канала К2 (диаг5 рамма 28) поступают на входы элемента 6 канала К2 и с его выхода - на вход параллельной записи счетчика 2 канала К2. Сигнал с нулевого выхода дешифратора 5 канала КЗ (диаграмма

0 29) поступает на вход установки в ноль счетчика 2 канала КЗ, сигналы с второго выхода дешифратора 5 канала КЗ (диаграмма 30) и шестого выхода дешифратора 5 канала КЗ (диаграмма 31) поступают на входа элемента 6 ка нала КЗ и с его выхода - на вход параллельной записи счетчика 2 канала КЗ. При отсутствии сбоев на нулевом, втором и шестом выходах дешифраторов 5 каналов К1, К2 и КЗ присутствуют

0 сигналы О и коррекция информащш п счетчиках 2 не производится.

Дпя обеспечения правильной работы устройства вхо дной сигнал должен по- , даваться после появления импульса

5 синхронизации через время, достаточное для записи информации в регистры 4, но меньшее длительности импуль- ; са синхронизации. Длительность импульсов синхронизации должна быть

0 достаточна для записи информации в регистры 4 и дешифрирования записанной информации дешифраторами 5. Дпи- тельность паузы между импульсами синхронизации должна быть достаточ5 на для вьщачи дешифр фованной информации на выходы дешифраторов 5, срабатывания элементов 6 и обнуления счетчиков 2 или параллельной записи информации в счетчики 2,

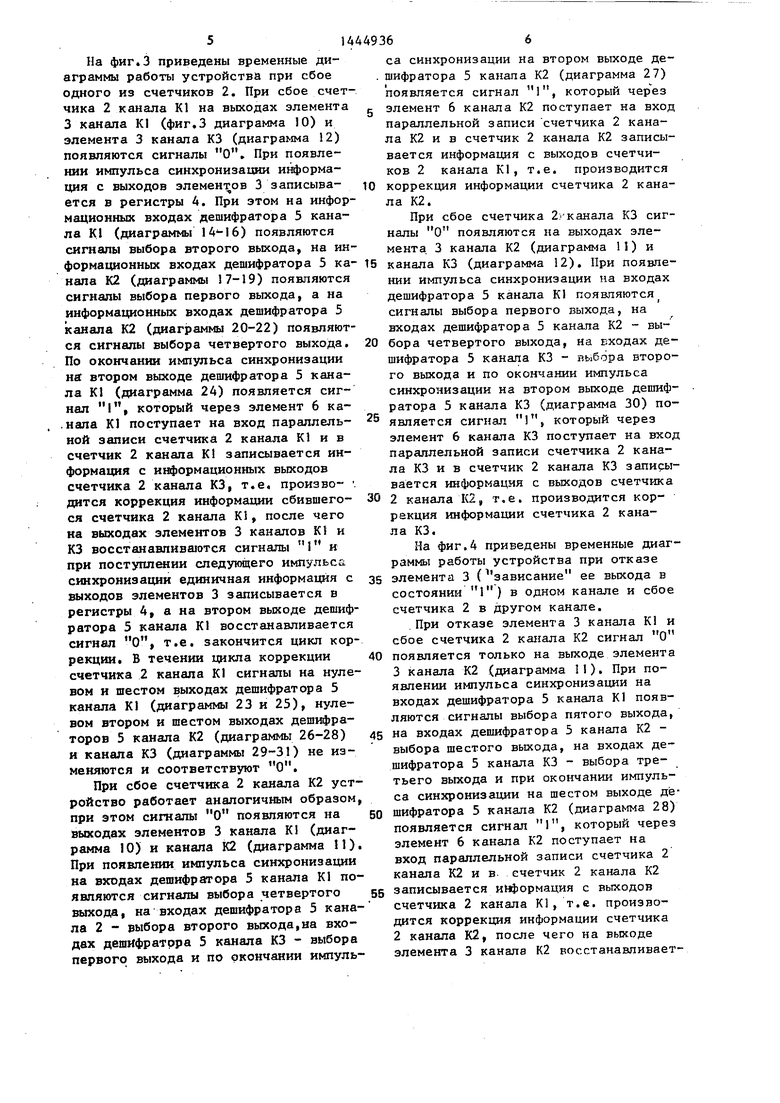

На фиг.З приведены временные диаграммы работы устройства при сбое одного из счетчиков 2. При сбое счетчика 2 канала К1 на выходах элемента 3 канала К1 (фиг.З диаграмма 10) и элемента 3 канала КЗ (диаграмма 12) появляются сигналы О, При появлении импульса синхронизации информация с выходов элементов 3 записывается в регистры 4. При этом на информационных входах дешифратора 5 канала К1 (диаграммы ) появляются сигналы выбора второго выхода, на информационных входах дешифратора 5 канала К2 (диаграммы 17-19) появляются сигналы выбора первого выхода, а на информационных входах дешифратора 5 канала К2 (диаграммы 20-22) появляются сигналы выбора четвертого выхода. По окончании импульса синхронизации нас втором выходе дешифратора 5 канала К1 (диаграмма 24) появляется сигнал 1, который через элемент 6 ка- .нала К1 поступает на вход параллельной записи счетчика 2 канала К1 и в счетчик 2 канала К записывается информация с информационных выходов счетчика 2 канала КЗ, т.е. произво . дится коррекция информации сбившегося счетчика 2 канала К1, после чего на выходах элементов 3 каналов Ki и КЗ восстанавпившотся сигналы 1 и при поступлении следующего импульса синхронизации единичная информация с выходов элементов 3 записывается в регистры 4, а на втором выходе дешифратора 5 канала К1 восстанавливается сигнал О, т.е. закончится цикл коррекции. В течении цикла коррекции счетчика 2 канала К1 сигналы на нулевом и шестом выходах дешифратора 5 канала К1 (диаграммы 23 и 25), нулевом втором и шестом выходах дешифраторов 5 канала К2 (диаграммы 26-28) и канала КЗ (диаграммы 29-31) не изменяются и соответствуют О.

При сбое счетчика 2 канала К2 устройство работает аналогичным образом, при этом сигналы О появляются на выходах элементов 3 канала К1 (диаграмма 10) и канала К2 (диаграмма 11). При появлении импульса синхронизации на входах дешифратора 5 канала К1 появляются сигналы выбора четвертого выхода, на входах дешифратора 5 канала 2 - выбора второго выхода,на входах дешифратора 5 каиала КЗ - выбора первого выхода и по окончании импульса синхронизации на втором выходе де- шифратора 5 канапа К2 (диаграмма 27) появляется сигнал 1, который чер ез элемент 6 канала К2 поступает на вход параллельной записи счетчика 2 канала К2 и в счетчик 2 канала К2 записывается информация с выходов счетчиков 2 канала К1, т.е. производится

коррекция информации счетчика 2 канала К2.

При сбое счетчика 2: к знала КЗ сигналы О появляются на выходах элемента. 3 канала К2 (диаграмма 11) и

канала КЗ (диаграмма 12). При появлении импульса синхронизации на входах дешифратора 5 канала К1 появляются сигналы выбора первого выхода, на входах дешифратора 5 канала К2 - вы

бора четвертого выхода, на входах дешифратора 5 канала КЗ - выбора второго выхода и по окончании импульса синхронизации на втором выходе дешифратора 5 канала КЗ (диаграмма 30) появляется сигнал , который через элемент 6 канала КЗ поступает на вход параллельной записи счетчика 2 канала КЗ и в счетчик 2 канала КЗ записывается информация с выходов счетчика

2 канала К2, т.е. производится коррекция информации счетчика 2 канала КЗ.

На фиг.4 приведены временные диаграммы работы устройства при отказе

элемента 3 ( зависание ее выхода в состоянии 1) в одном канале и сбое счетчика 2 в другом канале.

.При отказе элемента 3 канала К1 и сбое счетчика 2 каиала К2 сигнал О

появляется только на выходе элемента 3 канала К2 (диаграмма II). При появлении импульса синхронизации на входах дешифратора 5 канала К1 появляются сигналы выбора пятого выхода,

на входах дешифратора 5 канала К2 - выбора шестого выхода, на входах дешифратора 5 канала КЗ - выбора третьего выхода и при окончании импульса синхронизации на шестом выходе дёшифратора 5 канала К2 (диаграмма 28) появляется сигнал 1, который через элемент 6 канала К2 поступает на вход параллельной записи счетчика 2 канала К2 и в счетчик 2 канала К2

записывается ий})0рмация с выходов счетчика 2 канала К1, т.е. производится коррекция информации счетчика 2 канала К2, после чего на выходе элемента 3 канала К2 восстанавливает

ся сигнал 1 и при появлении следующего импульса синхронизации единичная информация с выходов элементов 3 записывается в регистры 4, на шестом выходе дешифратора 5 канала К2 нос- станавливается сигнал I т.е. за- кончится цикл коррекции.

При отказе элемента 3 канала К2 и сбое счетчика 2 канала КЗ сигнал О появляется только на выходе элемента 3 канала КЗ (диаграмма 12),При появлении импульса синхронизации на входах дешифратора 5 канала К1 появляются сигналы выбора третьего выхода, на входах дешифратора 5 канала К2 - выбора пятого выхода, на входах дешифратора 5 канала КЗ - выбора шестого выхода, и в данном цикле коррекции сигнал 1 появляется на шестом выходе дешифратора 5 канала КЗ (диаграмма 31), т.е. в счетчик 2 канала КЗ записывается информация с выходов счетчика 2 канала К2, таким образом производится коррекция информации счетчика 2 канала КЗ.

При отказе элемента 3 канала КЗ и сбое счетчика 2 канала К1 сигнал О появляется только на выходе схемы сравнения 3 канала К1 (диаграмма 10) При появлении импульса синхронизации на входах дешифратора 5 канала К1 появляются сигналы выбора шестого выхода, на входах дешифратора 5 канала К2 - выбора третьего выхода, на входах дешифратора 5 канала КЗ - выбора пятого выхода и в данном цикле коррекции сигнал 1 появляется на шестом выходе дешифратора 5 канала К1 (диаграмма 25), т.е. в счетчик 2 канала К1 записывается информация с выходов счетчика 2 канала КЗ, таким образом производится коррекция информации счетчика 2 канала К1.

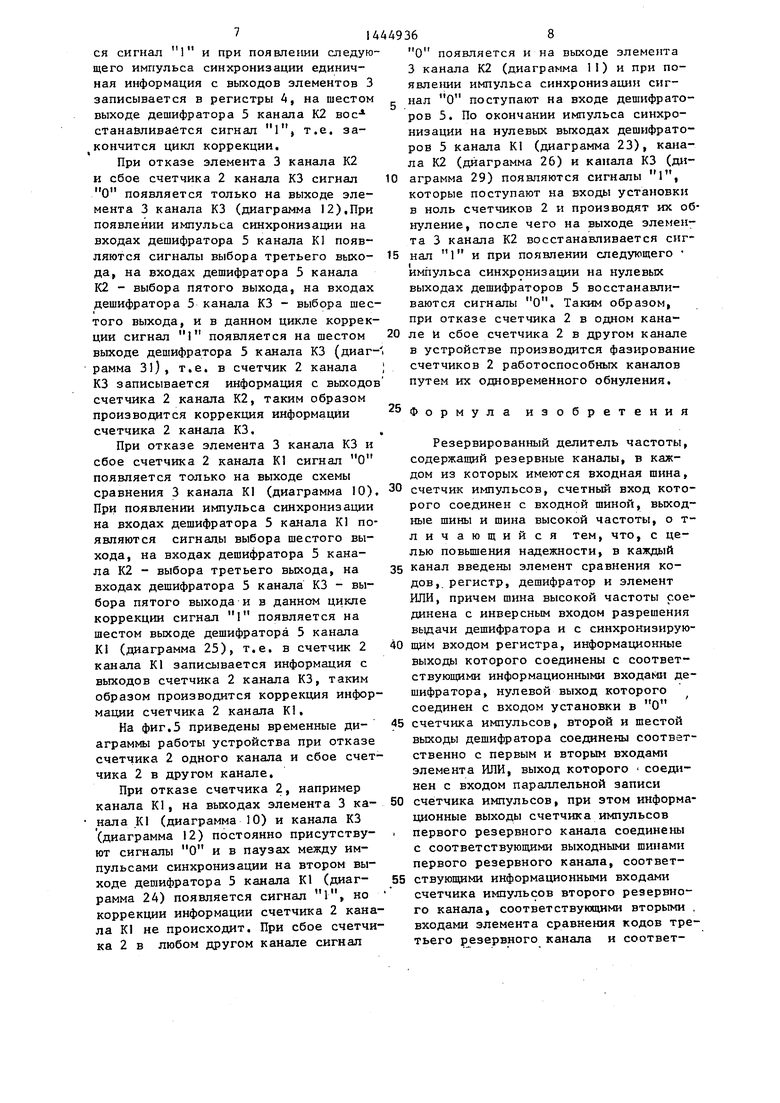

На фиг.5 приведены временные диаграммы работы устройства при отказе счетчика 2 одного канала и сбое счетчика 2 в другом канале.

При отказе счетчика 2, например канала К1, на выходах элемента 3 канала К1 (диаграмма 10) и канала КЗ (диаграмма 12) постоянно присутствуют сигналы О и в паузах между импульсами синхронизации на втором выходе дешифратора 5 канала К1 (диаграмма 24) появляется сигнал 1, но коррекции информации счетчика 2 канала К1 не происходит. При сбое счетчика 2 в любом другом канапе сигнал

О появляется и на выходе элемента 3 канала К2 (диаграмма II) и при появлении импульса синхронизации сих- нал О поступают на входе дешифраторов 5. По окончании импульса синхронизации на нулевых выходах дешифраторов 5 канала К1 (диаграмма 23), канала К2 (диаграмма 26) и канала КЗ (диаграмма 29) появляются сигнапы 1, которые поступают на входы установки в ноль счетчиков 2 и производят их обнуление, после чего на выходе элемента 3 канала К2 восстанавливается сиг- нал 1 и при появлении следующего импульса синхронизации на нулевых выходах дешифраторов 5 восстанавливаются сигналы О, Таким образом, при отказе счетчика 2 в одном канале и сбое счетчика 2 в другом канале в устройстве производится фазирование счетчиков 2 работоспособных каналов путем их одновременного обнуления.

20

25 ф

ормула изобретения

0

5

Резервированный делитель частоты, содержащий резервные каналы, в каждом из которых имеются входная шина, счетчик импульсов, счетный вход которого соединен с входной шиной, выходные шины и шина высокой частоты, о т- личающийся тем, что, с целью повышения надежности, в каждый канал введены элемент сравнения кодов,, регистр, дешифратор и элемент ИЛИ, причем шина высокой частоты соединена с инверсным входом разрешения выдачи дешифратора и с синхронизирую0 щим входом регистра, информационньш выходы которого соединены с соответствующими информационными входами дешифратора, нулевой выход которого соединен с входом установки в О счетчика импульсов, второй и шестой выходы дешифратора соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с входом параллельной записи счетчика импульсов, при этом информационные выходы счетчика импульсов первого резервного канала соединены с соответствующими выходными шинами первого резервного канала, соответ5 ствующими информационными входами счетчика импульсов второго резервного канала, соответствующими вторьми . входами элемента сравнения кодов третьего резервного канала и соответ5

0

914

ствующими первыми входами элемента сравнения кодов первого резервного канала, выход которого соединен с нулевым входом ч регистра первого резер- вного канала, вторым входом регистра второго резервного) канала и с первым входом регистра третьего резервного канала, причем информационные выходы счетчика импульсов второго резервно- го канала соединены с соответствующими выходными шинами второго резервного канала, соответствующими информационными входами счетчика импульсов

третьего резервного канала, соответствующими вторыми входами элемента сравнения кодов первого резервного канала и соответствующими первыми входами элемента сравнения кодов второго резервного канала, выход которого соединен с нулевым входом регистО

ра второго резервного канала, с первым входом регистра первого резервного канала и вторым входом регистра третьего резервного канала, информационные выходы счетчика импульсов третьего резервного канала соединены с соответствующими выходными шинами третьего резервного канала, соответствующими информационными входами счетчика импульсов первого резервного канала, соответствующими вторыми входами элемента сравнения кодов второго резервного канала и соответствующими первыми входами элемента сравнения кодов третьего резервного канала, выход которого соединен с нулевым входом регистра третьего резервного канала, вторым входом регистра первого резервного канала и первым входом регистра второго резервного канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для сопряжения двух ЭВМ с общим внешним устройством | 1986 |

|

SU1365089A1 |

| Устройство для решения задачи синхронизации работы объектов в сети связи | 1989 |

|

SU1777150A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1290537A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

Изобретение относится к импульсной технике и может использо-: ваться в резервированных устройствах деления частоты следования импульсов, счета времени. Цель изобретения - по- вьшение надежности работы - достигается за счет того, что при сбое одного из резервных каналов производится полная коррекция информации сбившегося счетчика импульсов, а при отказе элементов в одном из резервных каналов и сбое счетчика импульсов в другом производится фазирование работоспособных резервных каналов, при этом максимальное время коррекции информации сбившегося счетчика импульсов, а также максимальное время фазирования счетчиков импульсов работоспособньпс резервных каналов равно периоду следования импульсов синхронизации. Устройство содержит резервные каналы К1, К2 и КЗ, в каждом из которых имеются входная шина 1, счетчик 2 импульсов, элемент 3 сравнения кодов, регистр 4, дешифратор 5, элемент ИЛ11 6, шина 7 высокой (входной) частоты и выходная шина 8. 5 ил. с 9

rs to

f

v

Y

ПГ

30

«гЗ

у

(риг.2

/J

fO

n

2 l 15 16 77 IB f9 20 t

2

25 31

9 Г5

11

-у

23

гц.

26- 29

гт

| Резервированный делитель частоты | 1984 |

|

SU1188882A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для сортировки гирь одного наименования | 1926 |

|

SU9910A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-06—Подача