1 12

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и мо-, жет быть использовано для преобразования последовательных кодов, посту- пагощих по линии связи, в параплельны код.

Цель изобретения - повышение достоверности преобразования путем обеспечения покадрового контроля принимаемой информации.

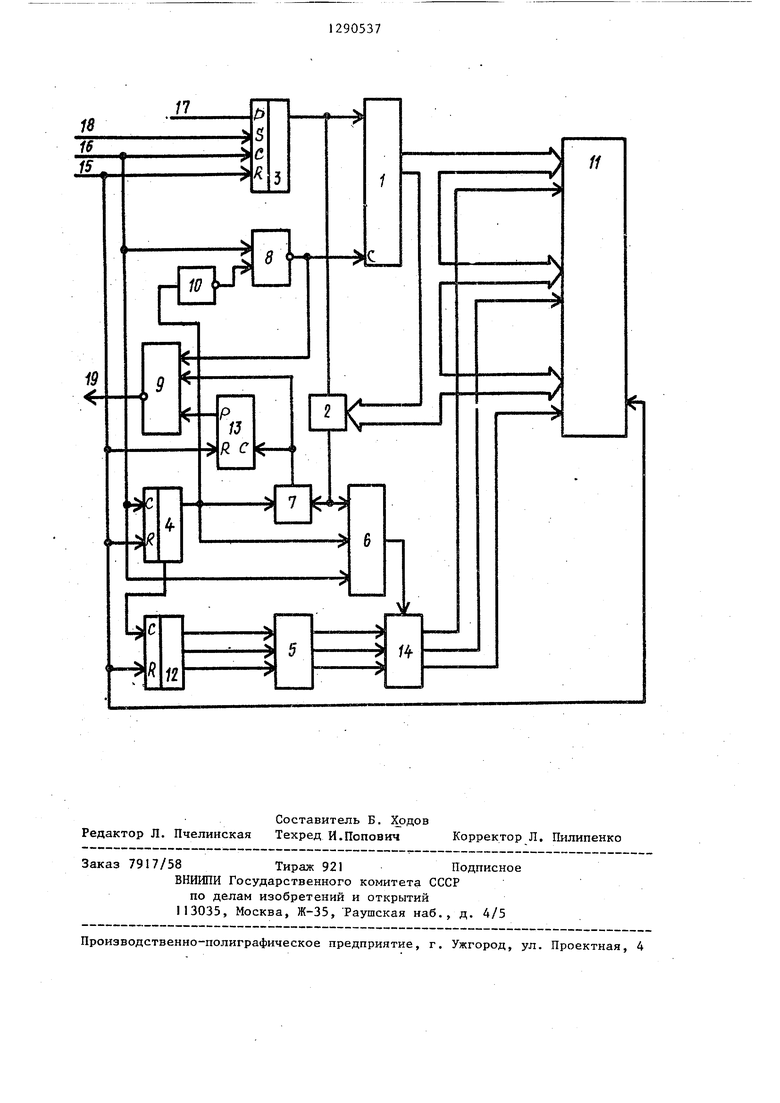

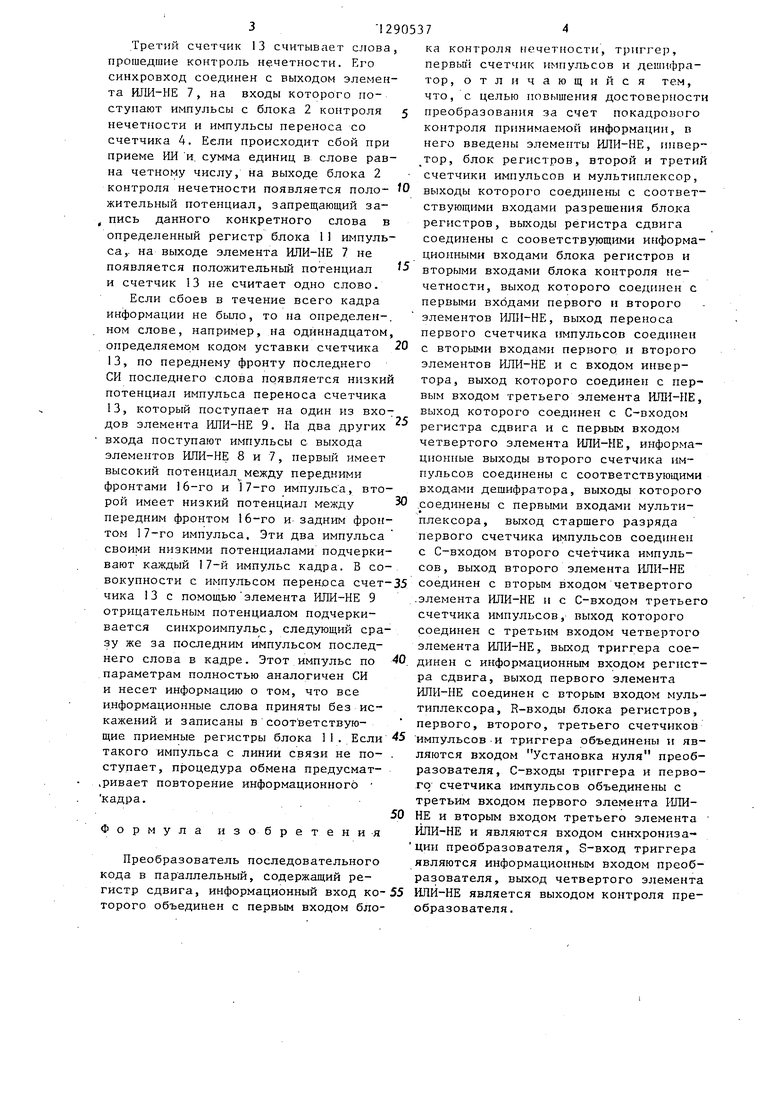

На чертеже представлена блок-схема преобразователя последовательного кода в параллельный.

Преобразователь содержит регистр 1 сдвига, блок 2 контроля нечетности триггер 3, первый счетчик 4 импульсов, дешифратор 5, первый 6, второй 7, третий 8 и четвертый 9 элементы ИЛИ-НЕ, инвертор 10, блок П приемных регистров, второй 12 и третий 13 счетчики импульсов и мультиплексор 14.

На обозначены вход 1 5 установка в нуль, вход 16 синхронизации, отрицательная шина 17 источника напряжения, информационный вход 18 и выход 19 контроля преобразователя.

Преобразователь работает следующим образом.

Перед началом обмена на преобразо ,ватель по входу 15 подается сигнал Признак начала обмена (ПНО), кото- рый приводит в исходное состояние все элементы преобразователя и записывает заданное число в счетчик 13 правильных слов, которое соответствует заведомо заданному-в соответствии с процедурой обмена количеству слов в передаваемом кадре информации. Далее по линии связи на вход 16 следу- Tot синхронно передаваемые синхроимпульсы (си) и информационные импуль сы (ИИ) на вход 18.

В регистр 1 сдвига .информация записывается по перепаду инвертированных СИ. К этому времени на выходе триггера 3, а значит,и на входе по- следоватёльной записи регистра 1 сдвига процессы имеют установившийся характер и записываемая информация является достоверной.Счетчик 4 определяет количество бит в информационном слове. Последний бит информации отводится для контроля достоверности принимаемой информации в слове. Сумма единиц во всех, на72

пример 16-ти, разрядах слова должна быть нечетной-. В этом случае на выходе блока 2 контроля нечетности вырабатывается сигнал низкого уровня, который йовместно с низким уровнем импульса переноса счетчика 4 и низким уровнем на входе 16 синхронизации между 16-м и 7-м импульсами выдает с помощью элемента ИЛИ-НЕ 6 разрешение на запись мультиплексора 14.

Если, например, используется 16- разрядное слово с .кодограммой 1000000000000011, то после 15-го СИ на выходе регистра 1 сдвига устанавливается принимаемое слово. 16-й СИ сдвига в регистре 1 не производится, так как импульс с выхода переноса счетчика 4 блокирует прохождение заднего фронта 16-го СИ на С-вход регистра 1. По заднему фронту 15-го СИ на выходе блока 2 контроля нечетности устанавливается низкий потенциал. Сумма единичных битов равна четному числу, поэтому 16-й ИИ должен быть единичным, однако единичный потенциал не изменяет сигналы на выходе блока 2, оставляя выходной потенциал низким. Если бы 15-й импульс в кодограмме был нулевым, т.е. преобразователь принимал бы слово, например, с кодограммой 1000000000000101, то 6-й импульс своим передним фронтом изменил бы потенциал на выходе блока 2 с высокого (сумма единиц 15 битов информации равна двум) на низкий (сумма единиц 16 битов информации равна трем), разрешая записать слово в блок II приемных регистров. Какой из этих регистров открыт для записи зависит от количества СИ, передаваемых на вход 16 преобразователя. 8-й СИ устанавливает на выходе счетчика 12 код 0001, что соответствует единице , на 1-м выходе дешифратора 5 и разрешению записи в один из регистров блока Ii. Запись информации происходит. По появлению на втором входе мультиплексора 14 положительного импульса с выхода элемента 6. 24-й СИ устанавливает код на выходе счетчика 12 равным 0010, что соответствует BbicoKOMy потенциалу на втором выходе дешифратора 5 и открытому каналу для разрешения па запись в следующий регистр блока 11. 40-й СИ устанавливает код ООП и разрешает запись в еще один регистр блока 11 и т.д.

t

3 12

Третий счетчик 13 считывает слова прошедшие контроль нечетности. Его синхровход соединен с выходом элемента ИГШ-НЕ 7, на входы которого поступают импульсы с блока 2 контроля нечетности и импульсы переноса со счетчика 4. Если происходит сбой при приеме ИИ и. сумма единиц в слове равна четному числу, на выходе блока 2 контроля нечетности появляется поло- жительный потенциал, запрещающий запись данного конкретного слова в определенный регистр блока 11 импульса, на выходе элемента ИЛИ-НЕ 7 не появляется положительный потенциал и счетчик 13 не считает одно слово. Если сбоев в течение всего кадра информации не было, то на определенном слове, например, на одиннадцатом определяемом кодом уставки счетчика 13, по переднему фронту последнего СИ последнего слова появляется низки потенциа;г импульса переноса счетчика 13, который поступает на один из входов элемента I-fflH-HE 9. На два других входа поступают импульсы с выхода элементов ИЛИ-НЕ 8 и 7, первый имеет высокий потенциал между передними фронтами 16-го и 17-го импульса, второй имеет низкий потенциал между передним фронтом 16-го и задним фронтом 17-го импульса. Эти два импульса своими низкими потенциалами подчеркивают каждый 17-й импульс кадра. В совокупности с импульсом переноса счет чика 13 с помощью элемента ИЛИ-НЕ 9 отрицательным потенциалом подчеркивается синхроимпульс, следующий сразу же за последним импульсом последнего слова в кадре. Этот импульс по параметрам полностью аналогичен СИ и несет информацию о том, что все информационные слова приняты без искажений и записаны в соот ветствую

щие приемные регистры блока 1 1 . Если 45 импульсов и триггера объединены и являются входом Установка нуля преобразователя, С-входы триггера и первого счетчика импульсов объединены с третьим входом первого элемента ИЛИ- 50 НЕ и вторьш входом третьего элемента ИЛИ-НЕ и являются входом синхрониза- ции преобразователя, S-вход триггера являются информационным входом преобразователя, выход четвертого элемента

такого импульса с линии связи не поступает, процедура обмена предусмат ривает повторение информационного

кадра.

Формула изобретения

Преобразователь последовательного кода в пар аллельный, содержащий регистр сдвига, информационный вход ко-55 1ШИ-НЕ является выходом контроля пре- торого объединен с первым входом бло- образователя.

5

0

5 О 5

5

ка контроля гечетгсости, триггер, первьп счетчик импульсов и дешифратор, отличающийся тем, что, с целью повышения достоверности преобразования за счет покадрового контроля принимаемой информации, в него введены элементы ИЛИ-НЕ, инвертор, блок регистров, второй и третий счетчики импульсов и мультиплексор, выходы которого соединены с соответствующими входами разрешения блока регистров, выходы регистра сдвига соединены с сооветствующими информационными входами блока регистров и вторыми входами блока контроля нечетности, выход которого соединен с первыми входами первого и второго элементов ИЛИ-НЕ, выход переноса первого счетчика импульсов соединен с вторыми входами первого и второго элементов ИЛИ-НЕ и с входом инвертора, выход которого соединен с первым входом третьего элемента ИЛ11-ПЕ, выход которого соединен с С-входом регистра сдвига и с первым входом четвертого элемента ИЛИ-НЕ, информа- выходы второго счетчика импульсов соединены с соответствующими входами дешифратора, выходы которого .соединены с первыми входами мультиплексора, выход старшего разряда первого счетчика импульсов соединен с С-входом второго счетчика импульсов, выход второго элемента 1ШИ-НЕ

соединен с вторьш входом четвертого элемента ИЛИ-НЕ и с С-входом третьего счетчика импульсов, выход которого соединен с третьим входом четвертого элемента Ш1И-НЕ, выход триггера соединен с информационным входом регистра сдвига, выход первого элемента ИЛИ-НЕ соединен с вторым входом мультиплексора, R-входы блока регистров, первого, второго, третьего счетчиков

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

Изобретение относится к вычислительной технике, а именно к устройствам лреобразования информации, и . может быть использовано для преобразования последовательных кодов, поступающих по линии связи, в параллельный код. Устройство осуществляет пословный контроль принимаемой информации и в конце каждого кадра формирует сигнал контроля достоверности информации, обеспечивая тем самым повышение достоверно сти преобразуемых сигналов. Преобразователь последовательного кода в параллельный содержит регистр сдвига, блок контроля нечетности, триггер, три счет- .:чика импульсов, инвертор, четыре элемента ИЛИ-НЕ, дешифратор, мультиплексор и блок приемных регистров. 1 ил. ю о СП оэ

| Патент США | |||

| СПОСОБ ТЕРМИЧЕСКОЙ ОБРАБОТКИ ОПРАВОК ПРОШИВН1)ГО СТАНА | 0 |

|

SU396379A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-07-10—Подача