тьей группы сумматоров по модулю дна и с входом приема первого векто ра синдрома блока формирования сигнала ошибки, вход приема контрольной суммы которого подключен к первому блокировочному входу блока фик сации второго отказа и к выходу пер вого элемента ИЛИ, вход приема второго вектора синдрома - к первым выходам блока фиксации второго отказа, вход приема третьего вектора синдрома - к выходам проверочного блока, входу приема вектора синдрома блока фиксации второго отказа и к вторым входам третьей группы сумматоров по модулю два, вход фиксации второго отказа- к второму вы ходу блока фиксации второго отказа вход отсутствия ошибки - к второму вь:коду блока обнаружения ошибки, вход двойной овшбки - к первому выходу блока обнаружения ошибки, выход - к контрольному выходу устройства, выходы третьей группы сум маторов по модулю два подключены к входам первого элемента ИЛИ, а второй выход блока фиксации первог отказа - к второму блокировочному входу блока фиксации второго отказ входы первого элемента И-НЕ подсое динены к нулевой шине. 2. Устройство по П.1, отличающееся тем, что, блок фи сации первого (второго) отказа содержит первый элемент ИЛИ-НЕ, вторые элементы И-НЕ, третий и чет вертый элементы И-НЕ, первый и второй элементы И, второй элемент ИЛИ, двоично-десятичные реверсивные счетчики, вход приема вектора синдрома блока подключен к первым входам вторых элементов И-НЕ, вход начальной установки - к первому вхо ду второго элемента ИЛИ, вход сигна ла сброса - к первому входу первого элемента И, вход второго строба, вход тактовых импульсов и первый блокировочный вход - соответственно к первому, второму и. третьему входа третьего элемента И-НЕ, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с вторым блокировочным входом блока, а выход . с вторыми входами вторых элементов И-НЕ, выходы которых соединены с входами 41 соответствующих двоично-десятичных .реверсивных счетчиков вых;од первого элемента И соединен 5 с вторым входом второго элемента ИПИ, выход которого соединен с входами К двоично-десятичных реверсивных счетчиков I D -входы которых соединены с нулевой шиной, С-вход и вход выходом четвертого элемента И-НЕ, первые выходы - с первыми выходами блока, вторые выходы - с входами второго элемента И, выход которого соединен с четвертым входом третьего элемента И-НЕ, вторым входом первого элемента И и вторым выходом блока, входы четвертого элемента И-НЕ подключены к нулевой шине. 3. Устройство по П.1, отличающееся тем, что блок формирования сигнала ошибки содержит четвертую, пятую и шестую группы сумматоров по модулю два, со второго по седьмой элементы ИЛИ-НЕ, первый и второй триггеры, третий элемент И, причем вход приема третьего строба блока соединен с С-входами триггеров, вход начальной установки - с Р-входами триггеров, вход приема первого вектора синдрома с первыми входами четвертой группы сумматоров .по модулю два, вход приема контрольной суммы - с входами второго элемента ИЛИ-НЕ, вход приема второго вектора синдрома - с вторыми входами четвертой группы сумматоров по модулю два и первыми входами пятой группы сумматоров по модулю два, вход приема третьего вектора синдрома - с первыми входами шестой группы сумматоров по модулю два и вторыми входами пятой группы сумматоров по модулю два, выходы четвертой группы сумматоров по модулю два соединены с вторыми входами шестой группы сумматоров по.модулю два, выходы которой соединены с входами третьего элемента ИЛИ-НЕ, выходы пятой группы сумматоров по модулю два соединены с входами четвертого элемента ИЛИ-НЕ, входы пятого элемента ИЛИ-НЕ соединены соответственно с выходами второго, третьего и четвертого элементов ШТИ-НЕ, входом фиксации второго отказа блока и первым входом шестого элемента ИЛИ-НЕ, входом отсутствия ошибки блока, а выход - с J-входами первого триггера, вход двойной ошибки блока соединен через седьмой элемент ИЛИ-НЕ с вторым входом шестого элемента ИЛИ-НЕ, выход которого соединен с J-нх,одами

второго триггера, К и 5 -входы триг- ствующими входами третьего элемента геров подключены к нулевой шине, И, выход которого подключен к выходу выходы триггеров соединены с соответ- блока.

1120335

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

| Устройство для управления переключением резервных блоков | 1984 |

|

SU1190557A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1352490A1 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Постоянное запоминающее устройство с самоконтролем | 1988 |

|

SU1532979A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

1. УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК, содержащее проверочный блок, первые входы которого соединены с выходами основного блока, перBbiMH входами первой группы сумматоров по модулю два и первыми входами блока обнаружения ошибки, вторые входы - с выходами контрольного блока и вторыми входами блока, обнаружения ошибки, выход - с третьими входами блока обнаружения ошибки, входами приема вектора синдрома блока фикса, дни первого отказа и первыми входами второй группы сумматоров по модулю два, выходы которых соединены через первый дешифратор с первыми входами группы элементов ИЖ, выхода которых соединены с вторыми входами первой группы сумматоров по модулю два, первые входы блока фиксации первого отказа соединены с первыми входами первой группы элементов И, выходы которых соединены с вторыми входами второй группы сумматоров по модулю два и через второй дешифратор с вторыми входами группы элементов ИЛИ,, первый выход блока обнаружения ошибки соединен с вторыми входами первой группы элементов И, о т л ичаюшееся тем, что, с целью повышения надежности и достоверности функционирования устройства, в него введены блок фиксации второго отказа, третья группа сумматоров по модулю два, первый элемент ИЛИ, блок формирования сигнала ошибки, вторая группа элементов И, первый элемент И-НЕ,, (Л причем вход первого строба устройства соединен с одноименными входами основного и контрольного блоков, входы тактовых импульсов, второго стро ба, сигнала сброса устройства соединены с одноименными входами блоков фиксации первого и второго отказов, вход начальной установки устройства - с одноименными входами блоков фиксации первого и второго отказов и блока формирования сигнала ошибки, вход третьего строба устройства - с одноименными входами блока формирования сигнала ошибки и первым входом второй группы элементов И, вторые входы которой соединены с выходами первой группы сумматоров по модулю два, а выходы - с информационным выходом устройства, первый блокировочный вход блока фиксации первого отказа соединен с выходом первого элемента И-НЕ, второй блокировочный вход - с нулевой шиной, .первые выходы - с первыми входами тре-

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения высоконадежных цифровых устройств;

Известно устройство для исправления ошибок, содержащее блоки обнаружения ошибок краткости t и , входы которых подключены к прямым и инверсным входным шинам устройства локализатор ошибок кратности f , соединенный выходами с первыми входа корректора ошибок кратности t, выход которого являются выходными шинами устройства 1 .

Недостаток данного устройства состоит в том, что оно не может исправлять ошибки кратности t+l, в том числе и в случае ординарного потока отказов в резервируемом устройстве.

Известно устройство для исправления ошибок, содержащее исходный блок (информационные разряды) и контрольный блок, соединенные через декодер ошибок с входами корректора. При использовании кода Хэмминга и обеспечении минимального кодового расстояния, равного трем, устройство исправляет все одиночные ошибки, а при минимальном кодовом расстоякии, равном четырем, устройство исправляет одиночные и обнаруживает все двойные ошибки, вызванные отказами в исходном и контрольном блоках t2.

Однако устройство не может исправлять двойные ошибки, в том числе и в случае ординарного потока отказов в резервируемом устройстве.

Наиболее близким к изобретению является устройство для исправления ошибок, содержащее локализатор ошиб;ки, выход которого соединен с первыми входами сумматора по модулю два и первого элемента И, выход которого через регистр соединен с :.первым входом второго элемента И, блоки обнаружения одиночной

и двойной ошибок, выходы которых соединены с вторь№1И входами первого и второго элементов И соответствейно, выход второго элемента И через первый дешифратор соединен с первым входом элемента ИЛИ и вторым входом сумматора по модулю два, выход которого через второй дешифратор соединен с вторым входом элемента ИЛИ, выход которого соединен с первым входом корректора, второй вход корректора соединен с входом устройства, входами локализатора ошибки, блоков обнаружения одиночных и двойных ошибок Г33«

Недостаток известного устройства состоит в том, что оно не обеспечивает исправления двухкратных ошибок в случае ординарного потока отказов и возникновения отказов, приводящих к неустойчивым ошибкам выходных сигналов. Практически все отказы элементов дискретных устройств проявляются в виде искажения выходного сигнала лишь на части входных наборов и с этой точки зрения являются неустойчивыми. Кроме того, неспособность к обнаружению трехкратных ошибок ведет к неконтролируемости устройства после возникно- вения второго отказа.

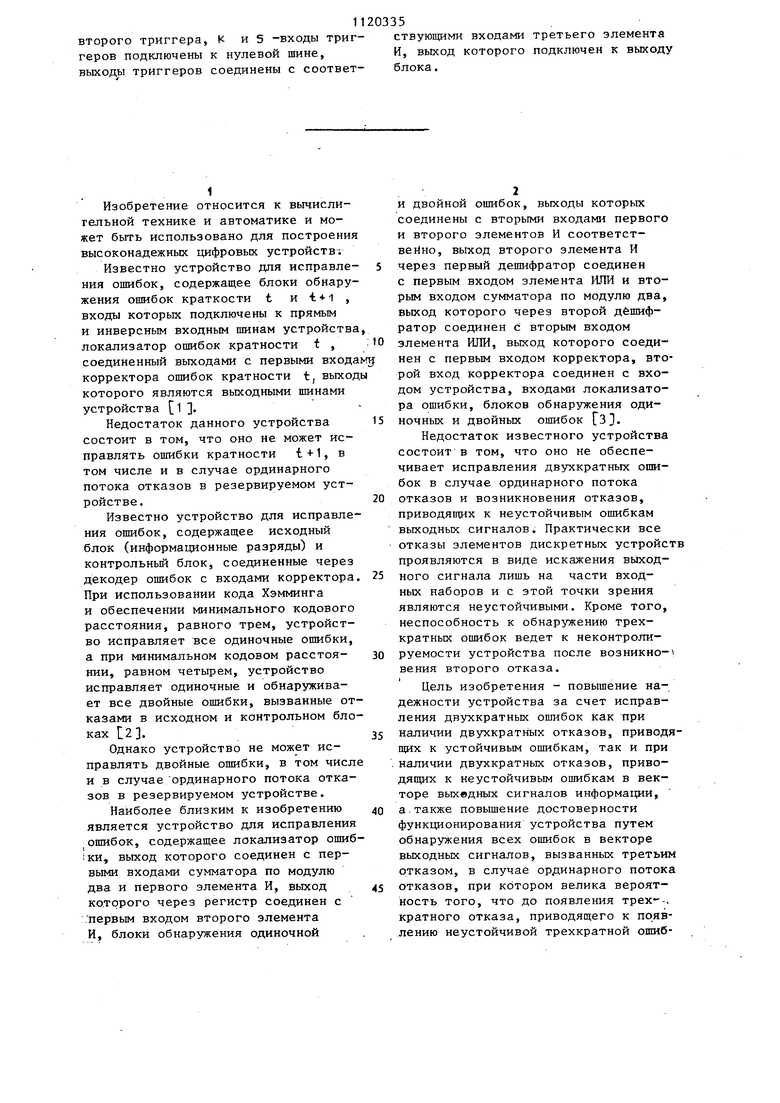

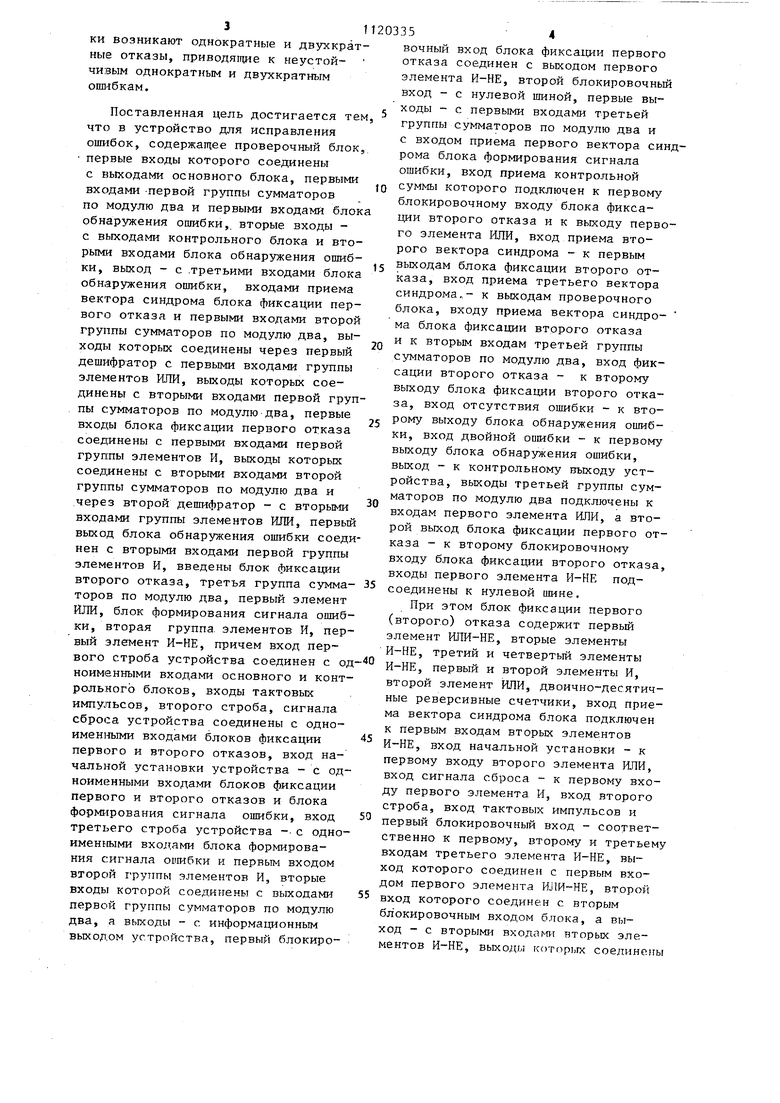

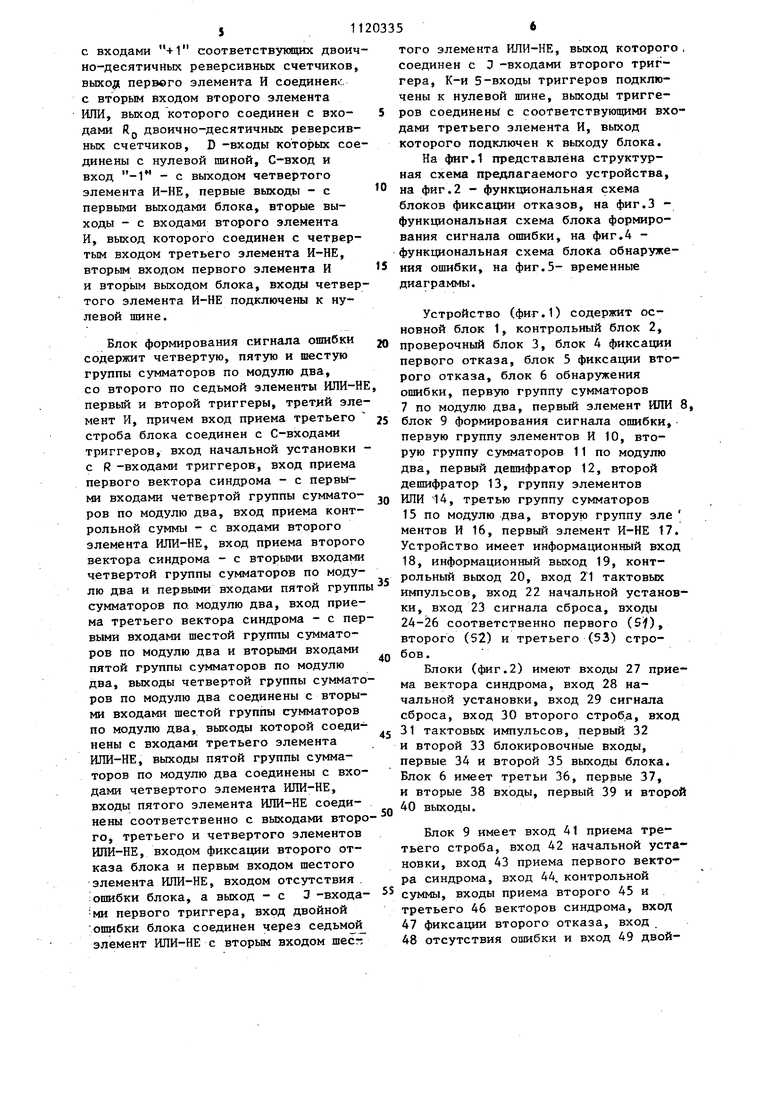

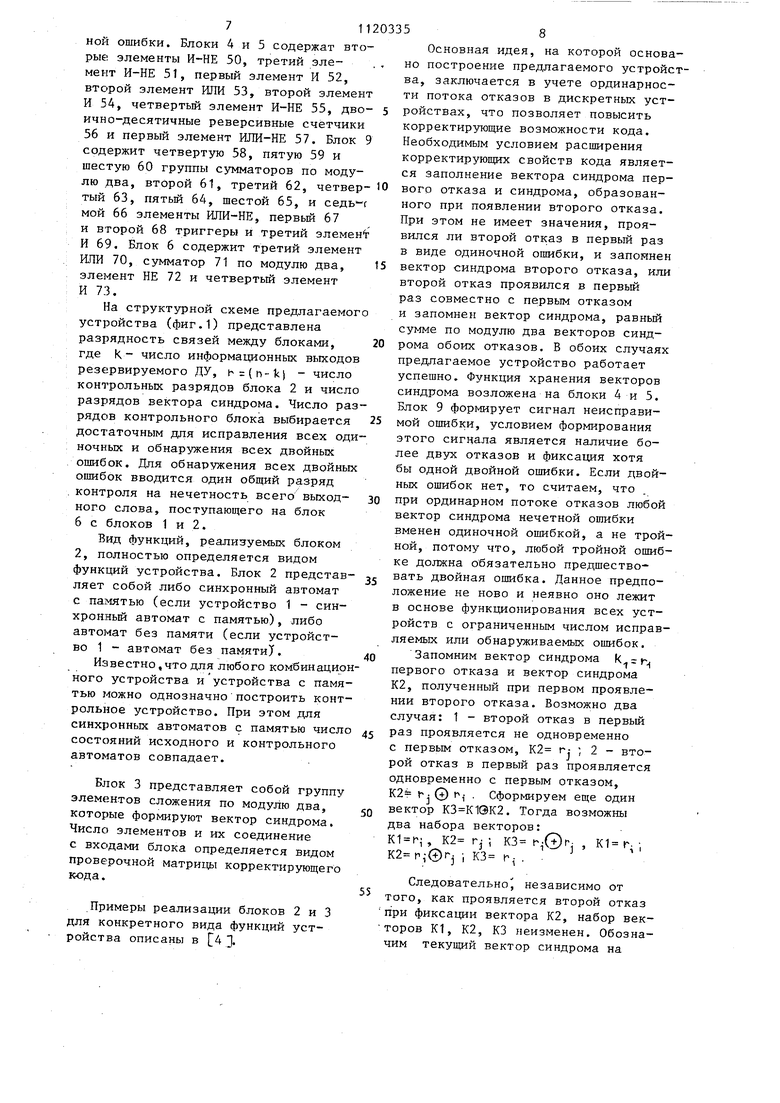

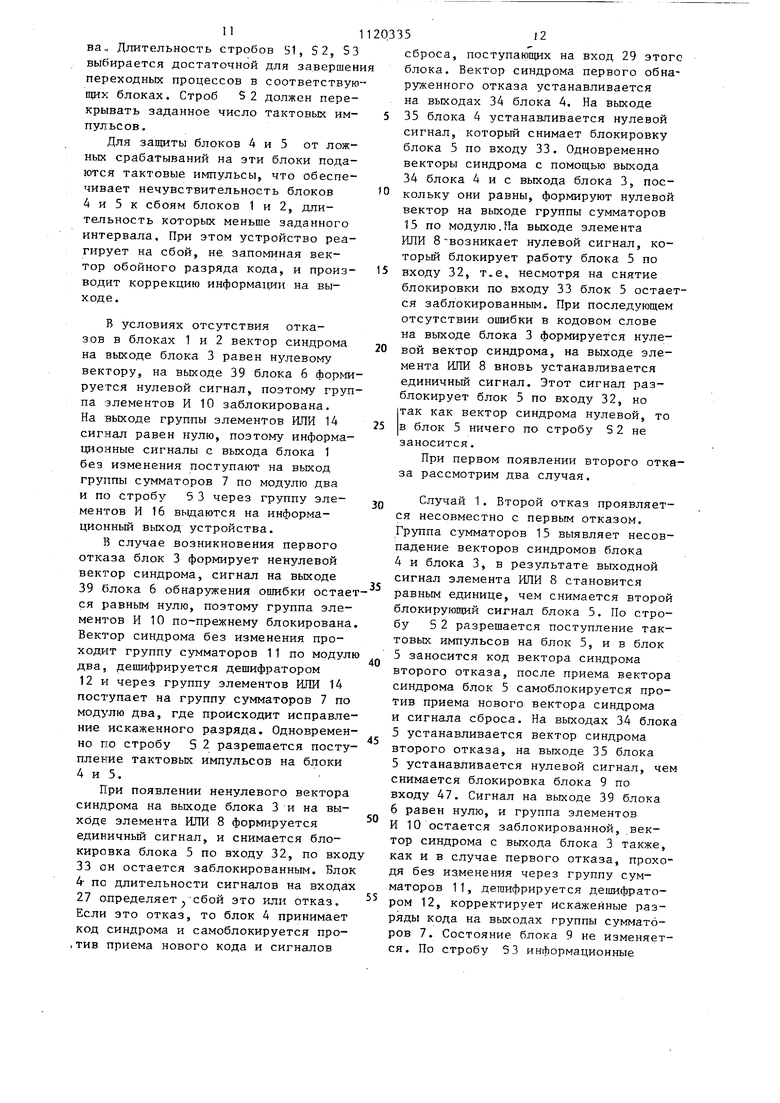

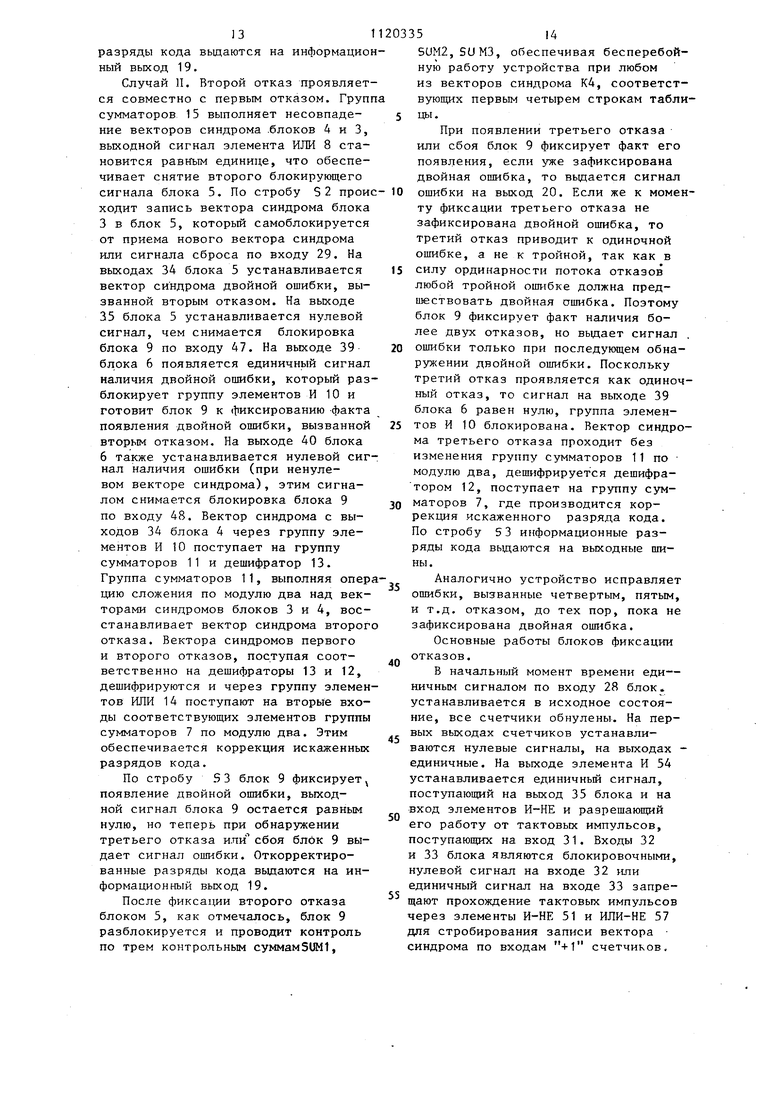

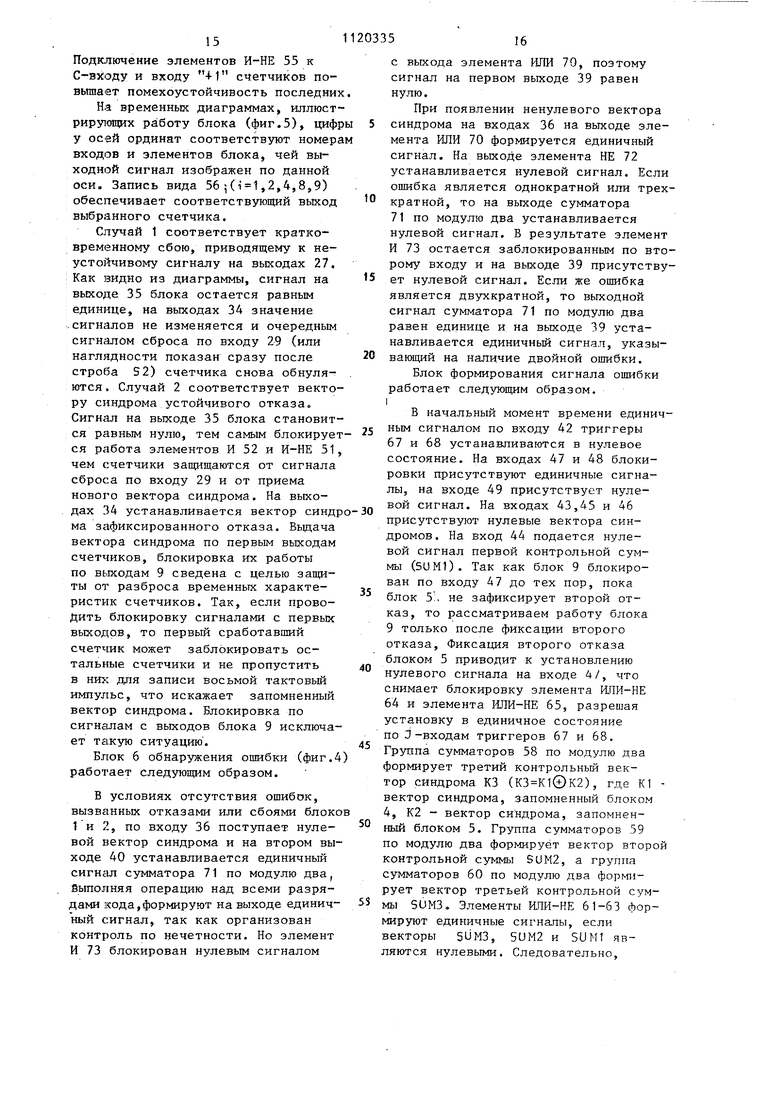

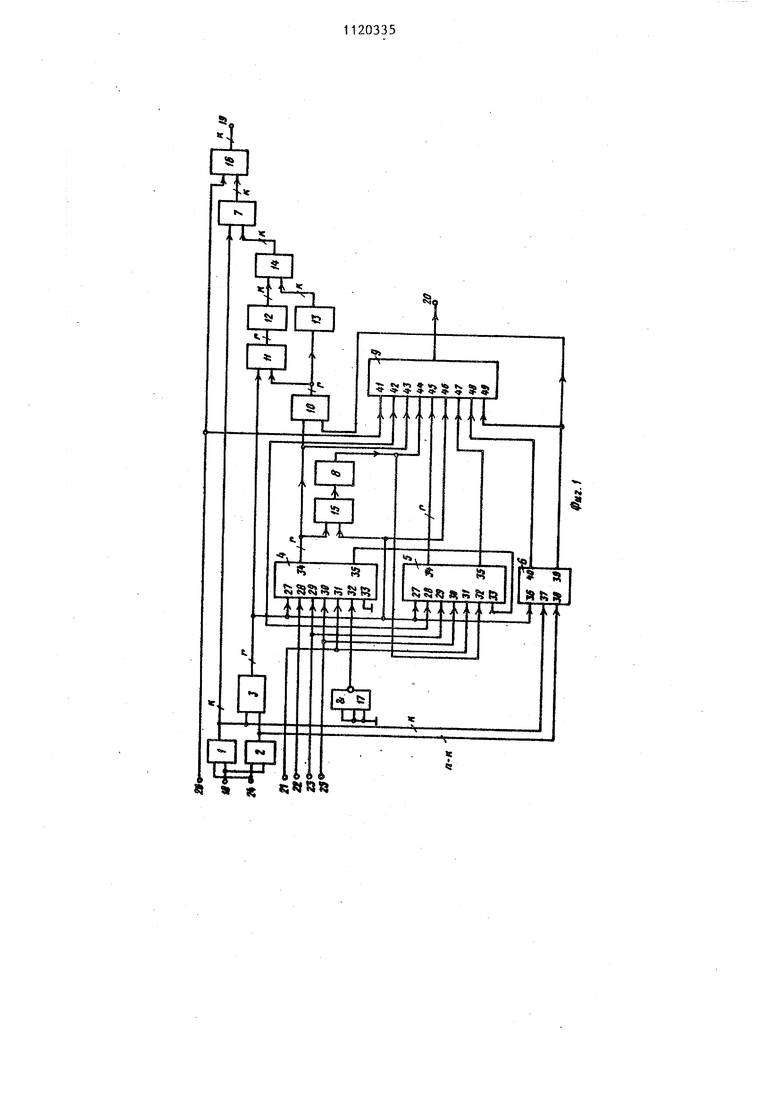

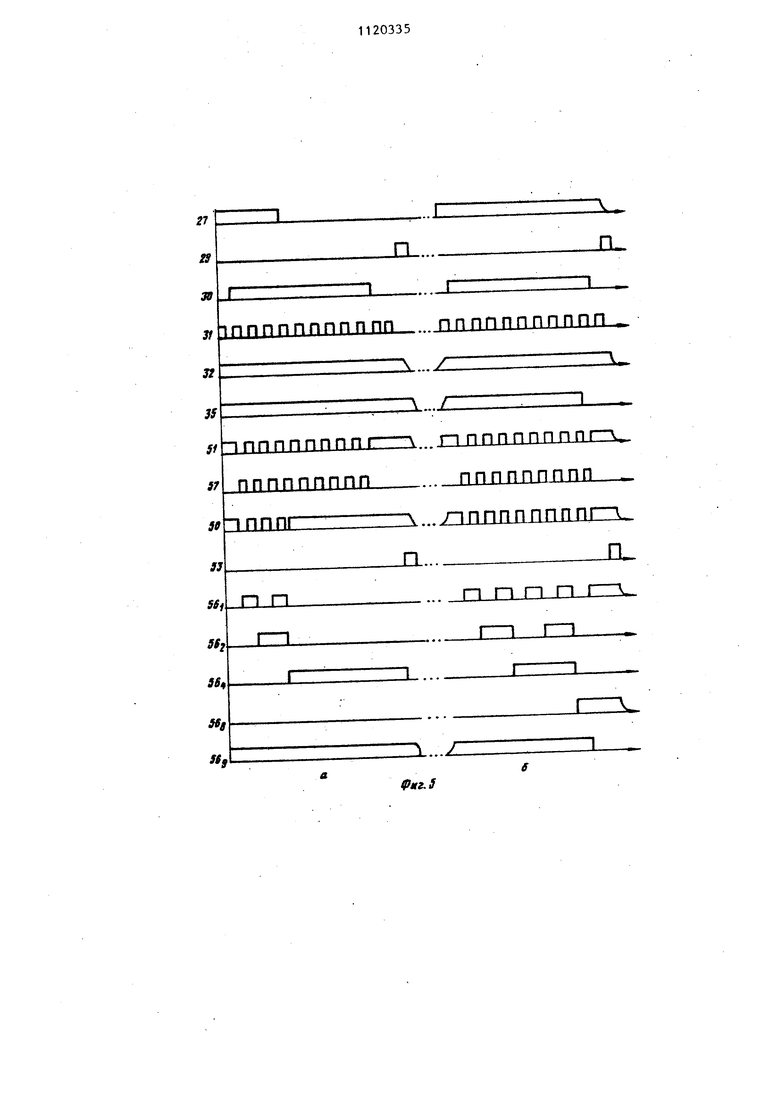

Цель изобретения - повышение надежности устройства за счет исправления двухкратных ошибок как при наличии двухкратных отказов, приводящих к устойчивым ошибкам, так и при наличии двухкратных отказов, привоящих к неустойчивым ошибкам в векторе выхвдных сигналов информации, а.также повышение достоверности ункционирования устройства путем обнаружения всех ошибок в векторе выходных сигналов, вызванных третьим отказом, в случае ординарного потока отказов, при котором велика вероятность того, что до появления , ратного отказа, приводящего к появению неустойчивой трехкратной ошибки возникают однократные и двухкрат ные отказы, приводяпще к неустойчивым однократным и двухкратным ошибкам. Поставленная цель достигается тем что в устройство для исправления ошибок, содержащее проверочный блок первые входы которого соединены с выходами основного блока, первыми входами -первой группы сумматоров по модулю два и первыми входами блок обнаружения ошибки,, вторые входы с выходами контрольного блока и вторыми входами блока обнаружения ошибки, выход - с .третьими входами блока обнаружения ошибки, входами приема вектора синдрома блока фиксации первого отказа и первыми входами второй группы сумматоров по модулю два, выходы которых соединены через первый дешифратор с первыми входами группы элементов ИЛИ, выходы которых соединены с вторыми входами первой груп пы сумматоров по модулю-два, первые входы блока фиксации первого отказа соединены с первыми входами первой группы элементов И, выходы которых соединены с вторыми входами второй группы сумматоров по модулю два и через второй дешифратор - с вторыми входами группы элементов ИЛИ, первый выход блока обнаружения ошибки соеди нен с вторыми входами первой груцпы элементов И, введены блок фиксации второго отказа, третья группа сумматоров по модулю два, первый элемент ИЛИ, блок формирования сигнала ошибки, вторая группа элементов И, первый элемент И-НЕ, причем вход первого строба устройства соединен с од ноименными входами основного и контрольного блоков, входы тактовых импульсов, второго строба, сигнала сброса устройства соединены с одноименными входами блоков фиксации первого и второго отказов, вход начальной установки устройства - с од ноименными входами блоков фиксации первого и второго отказов и блока формирования сигнала ошибки, вход третьего строба устройства - с одно имен1ЕЫми входами блока формирования сигнала ошибки и первым входом второй группы элементов И, вторые входы которой соединены с выходами первой группы сумматоров по модулю два, а выходы - с информационным выходом устройства, первый блокировочный вход блока фиксации первого отказа соединен с выходом первого элемента И-НЕ, второй блокировочный вход - с нулевой шиной, первые выходы - с первыми входами третьей группы сумматоров по модулю два и с входом приема первого вектора синдрома блока формирования сигнала ошибки, вход приема контрольной суммы которого подключен к первому блокировочному входу блока фиксации второго отказа и к выходу первого элемента ИЛИ, вход приема второго вектора синдрома - к первым выходам блока фиксации второго отказа, вход приема третьего вектора синдрома,- к выходам проверочного блока, входу приема вектора синдрома блока фиксации второго отказа и к вторым входам третьей группы сумматоров по модулю два, вход фиксации второго отказа - к второму выходу блока фиксации второго отказа, вход отсутствия ошибки - к второму выходу блока обнаружения ошибки, вход двойной ошибки - к первому выходу блока обнаружения ошибки, выход - к контрольному выходу устройства, выходы третьей группы сумматоров по модулю два подключены к входам первого элемента ИЛИ, а второй выход блока фиксации первого отказа - к второму блокировочному входу блока фиксации второго отказа, входы первого элемента И-НЕ подсоединены к нулевой шине. При этом блок фиксации первого (второго) отказа содержит первый элемент ИЛИ-НЕ, вторые элементы И-НЕ, третий и четвертый элементы И-НЕ, первый и второй элементы И, второй элемент ИЛИ, двоично-десятичные реверсивные счетчики, вход приема вектора синдрома блока подключен к первым входам вторых элементов И-НЕ, вход начальной установки - к первому входу второго элемента ИЛИ, вход сигнала сброса - к первому входу первого элемента И, вход второго строба, вход тактовых импульсов и первый блокировочный вход - соответственно к первому, второму и третьему входам третьего элемента И-НЕ, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с вторым блокировочным входом блока, а выход - с вторыми входами вторых элементов И-НЕ, выходы которых соединены 51 с входами +1 соответствующих двоич но-десятичных реверсивных счетчиков, выхо первого элемента И соединенс с вторым входом второго элемента ИЛИ, выход которого соединен с входами RJJ двоично-десятичных реверсивных счетчиков, D -входы которых сое динены с нулевой шиной. С-вход и вход -1 - с выходом четвертого элемента И-НЕ, первые выходы - с первыми выходами блока, вторые выходы - с входами второго элемента И, выход которого соединен с четрертым входом третьего элемента И-НЕ, вторым входом первого элемента И и вторым выходом блока, входы четвер того элемента И-НЕ подключены к нулевой шине. Блок формирования сигнала ошибки содержит четвертую, пятую и шестую группы сумматоров по модулю два, со второго по седьмой элементы ИЛИ-Н первый и второй триггеры, третий эле мент И, причем вход приема третьего строба блока соединен с С-входами триггеров, вход начальной установки с R -входами триггеров, вход приема первого вектора синдрома - с первыми входами четвертой группы сумматоров по модулю два, вход приема контрольной суммы - с входами второго элемента ИЛИ-НЕ, вход приема второго вектора синдрома - с вторыми входами четвертой группы сумматоров по модулю два и первыми входами пятой групп сумматоров по. модулю два, вход приема третьего вектора синдрома - с пер выми входами шестой группы сумматоров по модулю два и вторыми входами пятой группы сумматоров по модулю два, выходы четвертой группы суммато ров по модулю два соединены с вторыми входами шестой группы сумматоров по модулю два, выходы которой соединены с входами третьего элемента ИЛИ-НЕ, выходы пятой группы сумматоров по модулю два соединены с входами четвертого элемента ИЛИ-НЕ, входы пятого элемента ИЛИ-НЕ соединены соответственно с выходами второ го, третьего и четвертого элементов ИЛИ-НЕ, входом фиксации второго отказа блока и первым входом шестого элемента ИЛИ-НЕ, входом отсутствия, ошибки блока, а выход - с 3 -входами первого триггера, вход двойной ошибки блока соединен через седьмой элемент ИЛИ-НЕ с вторым входом шее:: 5 того элемента ИЛИ-НЕ, выход которого , соединен с J -входами второго триггера, К-и 5-входы триггеров подключены к нулевой шине, выходы триггеров соединены с соответствующими входами третьего элемента И, выход которого подключен к выходу блока. На фиг.1 представлена структурная схема предлагаемого устройства, на фиг.2 - функциональная схема блоков фиксации отказов, на фиг.З функциональная схема блока формирования сигнала ошибки, на фиг,4 функциональная схема блока обнаружения ошибки, на фиг.З- временные диаграммы. Устройство (фиг.1) содержит основной блок 1, контрольный блок 2, проверочный блок 3, блок 4 фиксации первого отказа, блок 5 фиксации второго отказа, блок 6 обнаружения ошибки, первую группу сумматоров 7 по модулю два, первый элемент ИЛИ 8, блок 9 формирования сигнала ошибки, первую группу элементов И 10, вторую группу сумматоров 11 по модулю два, первый дешифратор 12, второй дешифратор 13, группу элементов ИЛИ 14, третью группу сумматоров 15 по модулю два, вторую группу эле ментов И 16, первый элемент И-НЕ 17. Устройство имеет информационный вход 18, информационный выход 19, контрольный выход 20, вход 21 тактовых импульсов, вход 22 начальной установки, вход 23 сигнала сброса, входы 24-26 соответственно первого (Sf), второго (52) и третьего (53) стробов . Блоки (фиг.2) имеют входы 27 приема вектора синдрома, вход 28 начальной установки, вход 29 сигнала сброса, вход 30 второго строба, вход 31 тактовых импульсов, первый 32 и второй 33 блокировочные входы, первые 34 и второй 35 выходы блока. Блок 6 имеет третьи 36, первые 37, и вторые 38 входы, первый 39 и второй лп „. „, v выходы. Блок 9 имеет вход 41 приема третьего строба, вход 42 начальной установки, вход 43 приема первого вектора синдрома, вход 44. контрольной суммы, входы приема второго 45 и третьего 46 векторов синдрома, вход 47фиксации второго отказа, вход 48отсутствия ошибки и вход 49 двоиной ошибки. Блоки 4 и 5 содержат вто рые элементы И-НЕ 50, третий элемент И-НЕ 51, первый элемент И 52, второй элемент ИЛИ 53, второй элемен И 54, четвертый элемент И-НЕ 55, дво ично-десятичные реверсивные счетчики 56 и первый элемент ИЛИ-НЕ 57. Блок содержит четвертую 58, пятую 59 и шестую 60 группы сумматоров по модулю два, второй 61, третий 62, четвер тый 63, пятьй 64, шестой 65, и седь мой 66 элементы ИЛИ-НЕ, первый 67 и второй 68 триггеры и третий элемен И 69. Блок 6 содержит третий элемент ИЛИ 70, сумматор 71 по модулю два, элемент НЕ 72 и четвертый элемент И 73. На структурной схеме предлагаемог устройства (фиг.1) представлена разрядность связей между блоками, где К- число информационных выходов резервируемого ДУ, b {n-k| - число контрольных разрядов блока 2 и число разрядов вектора синдрома. Число раз рядов контрольного блока выбирается достаточным для исправления всех оди ночных и обнаружения всех двойных ошибок. Для обнаружения всех двойных ошибок вводится один общий разряд контроля на нечетность всего выходного слова, поступающего на блок 6 с блоков 1 и 2. Вид функций, реализуемых блоком 2, полностью определяется видом функций устройства. Блок 2 представляет собой либо синхронный автомат с па)чятью (если устройство 1 - синхронный автомат с памятью), либо автомат без памяти (если устройство 1 - автомат без памяти. Известно,что для любого комбинацион ного устройства и устройства с памятью можно однозначно построить контрольное устройство. При этом для синхронных автоматов с памятью число состояний исходного и контрольного автоматов совпадает. Блок 3 представляет собой группу элементов сложения по модулю два, которые формируют вектор синдрома. Число элементов и их соединение с входами блока определяется видом проверочной матри11;ы корректирующего Примеры реализации блоков 2 и 3 для конкретного вида функций устройства описаны в 43Основная идея, на которой основано построение предлагаемого устройства, заключается в учете ординарности потока отказов в дискретных устройствах, что позволяет повысить корректирующие возможности кода. Необходимым условием расширения корректирующих свойств кода является заполнение вектора синдрома первого отказа и синдрома, образованного при появлении второго отказа. При этом не имеет значения, проявился ли второй отказ в первый раз в виде одиночной ошибки, и запомнен вектор синдрома второго отказа, или второй отказ проявился в первый раз совместно с первым отказом и запомнен вектор синдрома, равный сумме по модулю два векторов синдрома обоих отказов. В обоих случаях предлагаемое устройство работает успешно. Функция хранения векторов синдрома возложена на блоки 4 и 5. Блок 9 формирует сигнал неисправимой ошибки, условием формирования этого сигнала является наличие более двух отказов и фиксация хотя бы одной двойной ошибки. Если двойных ошибок нет, то считаем, что при ординарном потоке отказов любой вектор синдрома нечетной ошибки вменен одиночной ошибкой, а не тройной, потому что, любой тройной ошибке должна обязательно предшествовать двойная ошибка. Данное предположение не ново и неявно оно лежит в основе функционирования всех устройств с ограниченным числом исправляемых или обнаруживаемых ошибок. Запомним вектор синдрома k )-ц первого отказа и вектор синдрома К2, полученный при первом проявлении второго отказа. Возможно два случая: 1 - второй отказ в первый раз проявляется не одновременно с первьш отказом, К2 г.- ; 2 - второй отказ в первый раз проявляется одновременно с первым отказом, K2i (+) Сформируем еще один вектор КЗ К1@К2. Тогда возможны два набора векторов: К1 г, К2 Tj ; К3 . , К1 г. , ,-0r.j i К3 h . . Следовательно независимо от того, как проявляется второй отказ при фиксации вектора К2, набор векторов К1, К2, КЗ неизменен. Обозначим текущий вектор синдрома на

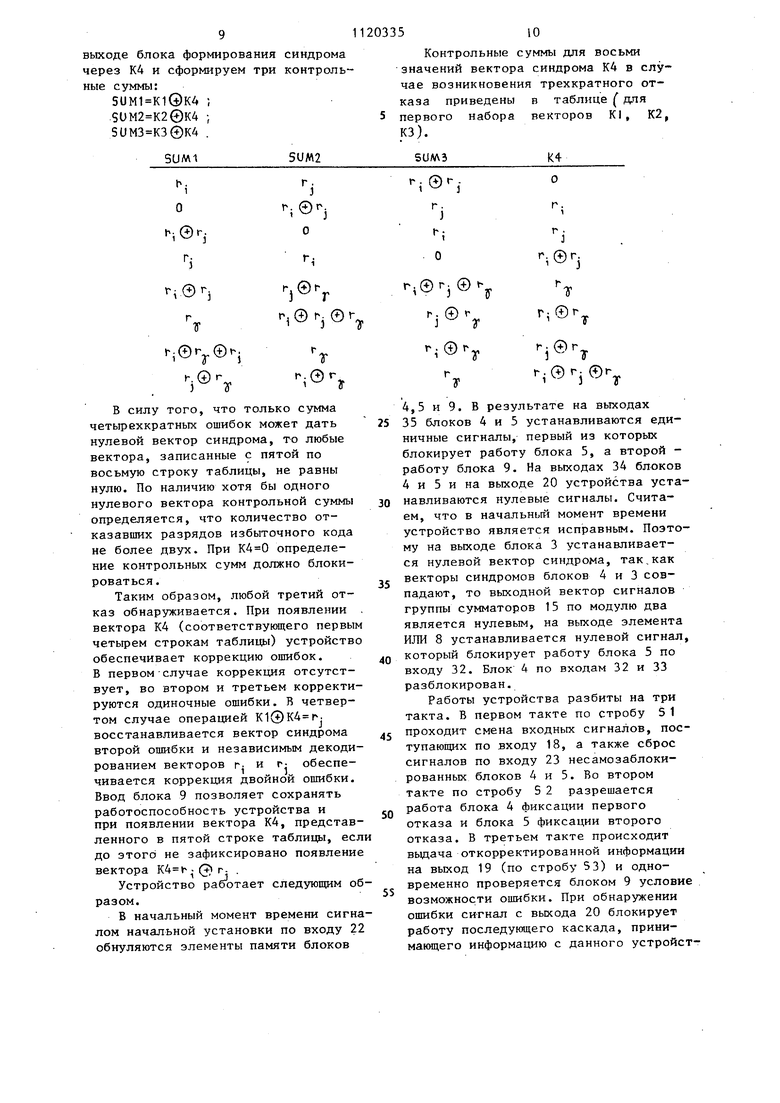

выходе блока формирования через К4 и сформируем три ные суммы:

5иМ1 К10КА ;

.SUM2 K20K4 ;

SUM3 K3©K4 .

5илЛ1

5UM2 В силу того, что только сумма четырехкратных ошибок может дать нулевой вектор синдрома, то любые вектора, записанные с пятой по восьмую строку таблицы, не равны нулю. По наличию хотя бы одного нулевого вектора контрольной суммы определяется, что количество отказавпшх разрядов избыточного кода не более двух. При определение контрольных сумм должно блокироваться. Таким образом, любой третий отказ обнаруживается. При появлении вектора К4 (соответствующего первы четырем строкам таблицы) устройств обеспечивает коррекцию ошибок. В первом случае коррекция отсутствует, во втором и третьем корректи руются одиночные ошибки. В четвертом случае операцией К10К4 г. восстанавливается вектор синдрома второй ошибки и независимым декоди и г- обесперованием векторов г. чивается коррекция двойной ошибки. Ввод блока 9 позволяет сохранять работоспособность устройства и при появлении вектора К4, представ ленного в пятой строке таблицы, ес до этого не зафиксировано появлени вектора (7irУстройство работает следующим о разом. В начальный момент времени сигн лом начальной установки по входу 2 обнуляются элементы памяти блоков

Контрольные суммы для восьми значений вектора синдрома К4 в случае возникновения трехкратного отказа приведены в таблице ( для первого набора векторов К1, К2, КЗ).

SUAA3

К4 4,5 и 9. В результате на выходах 35 блоков 4 и 5 устанавливаются единичные сигналы, первый из которых блокирует работу блока 5, а второй работу блока 9. На выходах 34 блоков 4 и 5 и на выходе 20 устройства устанавливаются нулевые сигналы. Считаем, что в начальный момент времени устройство является исправным. Поэтому на выходе блока 3 устанавливается нулевой вектор синдрома, так,как векторы синдромов блоков 4 и 3 совпадают, то выходной вектор сигналов группы сумматоров 15 по модулю два является нулевым, на выходе элемента ИЛИ 8 устанавливается нулевой сигнал, который блокирует работу блока 5 по входу 32. Блок 4 по входам 32 и 33 разблокирован. Работы устройства разбиты на три такта. В первом такте по стробу 51 проходит смена входных сигналов, поступающих по входу 18, а также сброс сигналов по входу 23 несамозаблокированных блоков 4 и 5. Во втором такте по стробу 5 2 разрешается работа блока 4 фиксации первого отказа и блока 5 фиксации второго отказа. В третьем такте происходит вьщача откорректированной информации на выход 19 (по стробу 53) и одновременно проверяется блоком 9 условие возможности ошибки. При обнаружении ошибки си-гнал с выхода 20 блокирует работу последующего каскада, принимающего информацию с данного устройства., Длительность стробов S1, 52, S3 выбирается достаточной для завершен переходных процессов в соответствую щих блоках. Строб S2 должен перекрывать заданное число тактовых импульсов. Для защиты блоков 4 и 5 от ложных срабатываний на эти блоки подаются тактовые импульсы, что обеспечивает нечувствительность блоков 4 и 5 к сбоям блоков 1 и 2, длитепьность которых меньше заданного интервала. При этом устройство реагирует на сбой, не запоминая вектор обойного разряда кода, и производит коррекцию информации на выходе. В условиях отсутствия отказов в блоках 1 и 2 вектор синдрома на выходе блока 3 равен нулевому вектору, на выходе 39 блока 6 форми руется нулевой сигнал, поэтому груп па элементов И 10 заблокирована. На выходе группы элементов ИЛИ 14 сигнал равен нулю, поэтому информационные сигналы с выхода блока 1 без изменения поступают на выход группы сумматоров 7 по модулю два и по стробу 5 3 через группу элементов И 16 вьщаются на информационный выход устройства. В случае возникновения первого отказа блок 3 формирует ненулевой вектор синдрома, сигнал на выходе 39 ешока 6 обнаружения ошибки остае ся равным нулю, поэтому группа элементов И 10 по-прежнему блокирована Вектор синдрома без изменения проходит группу сумматоров 11 по модул два, дешифрируется дешифратором 12 и через группу элементов ИЛИ 14 поступает на группу сумматоров 7 по модулю два, где происходит исправле ние искаженного разряда. Одновремен но по стробу 5 2 разрешается посту пление тактовых импульсов на блоки 4 и 5. При появлении ненулевого вектора синдрома на выходе блока 3 и на выходе элемента ИЛИ 8 формируется единичный сигнал, и снимается блокировка блока 5 по входу 32, по вхо 33 он остается заблокированным. Бл 4- по длительности сигналов на вход 27 определяетJ-сбой это или отказ. Если это отказ, то блок 4 принимает код синдрома и самоблокируется про,тив приема нового кода и сигналов сброса, поступающих на вход 29 этого блока. Вектор синдрома первого обнаруженного отказа устанавливается на выходах 34 блока 4. На выходе 35 блока 4 устанавливается нулевой сигнал, который снимает блокировку блока 5 по входу 33. Одновременно векторы синдрома с помощью выхода 34 блока 4 и с выхода блока 3, поскольку они равны, формируют нулевой вектор на выходе группы сумматоров 15 по модулю.Па выходе элемента ИЛИ 8-возникает нулевой сигнал, который блокирует работу блока 5 по входу 32, т.е, несмотря на снятие блокировки по входу 33 блок 5 остается заблокированным. При последующем отсутствии оишбки в кодовом слове на выходе блока 3 формируется нулевой вектор синдрома, на выходе элемента ИЛИ 8 вновь устанавливается единичньй сигнал. Этот сигнал разблокирует блок 5 по входу 32, но так как вектор синдрома нулевой, то в блок 5 ничего по стробу S 2 не заносится. Лри первом появлении второго отказа рассмотрим два случая. Случай 1. Второй отказ проявляется несовместно с первым отказом. Группа сумматоров 15 выявляет несовпадение векторов синдромов блока 4и блока 3, в результате выходной сигнал элемента ИЛИ 8 становится равным единице, чем снимается второй блокируювдий сигнал блока 5. Ло стробу 52 разрешается поступление тактовых импульсов на блок 5, и в блок 5заносится код вектора синдрома второго отказа, после приема вектора синдрома блок 5 самоблокируется против приема нового вектора синдрома и сигнала сброса. На выходах 34 блока 5 устанавливается вектор синдрома второго отказа, на выходе 35 блока 5устанавливается нулевой сигнал, чем снимается блокировка блока 9 по входу 47. Сигнал на выходе 39 блока 6равен нулю, и группа элементов И 10 остается заблокированной, вектор синдрома с выхода блока 3 также, как и в случае первого отказа, проходя без изменения через группу сумматоров 11, дешифрируется дешифратором 12, корректирует искаженные разряды кода на выходах группы сумматоров 7. Состояние блока 9 не изменяется. По стробу S3 информационные разряды кода выдаются на информацио ный выход 19. Случай П. Второй отказ проявляет ся совместно с первым отказом. Груп сумматоров 15 выполняет несовпадение векторов синдрома .блоков 4 и 3, выходной сигнал элемента ИЛИ 8 становится равным единице, что обеспечивает снятие второго блокирующего сигнала блока 5. По стробу 52 прои ходит запись вектора синдрома блока 3 в блок 5, который самоблокируется от приема нового вектора синдрома или сигнала сброса по входу 29. На выходах 34 блока 5 устанавливается вектор синдрома двойной ошибки, вызванной вторым отказом. На выходе 35 блока 5 устанавливается нулевой сигнал, чем снимается блокировка блока 9 по входу 47. На выходе 39 блока 6 появляется единичный сигнал наличия двойной ошибки, который раз блокирует группу элементов И 10 и готовит блок 9 к фиксированию -факта появления двойной ошибки, вызванной вторым отказом. На выходе 40 блока 6 также устанавливается нулевой сиг нал наличия ошибки (при ненулевом векторе синдрома), этим сигналом снимается блокировка блока 9 по входу 48. Вектор синдрома с выходов 34 блока 4 через группу элементов И 10 поступает на группу сумматоров 11 и дешифратор 13. Группа сумматоров 11, выполняя опер цию сложения по модулю два над векторами синдромов блоков 3 и 4, восстанавливает вектор синдрома второг отказа. Вектора синдромов первого и второго отказов, поступая соответственно на дешифраторы 13 и 12, дешифрируются и через группу элемен тов ИЛИ 14 поступают на вторые входы соответствующих элементов группы сумматоров 7 по модулю два. Этим обеспечивается коррекция искаженных разрядов кода. По стробу S3 блок 9 фиксирует появление двойной ошибки, выходной сигнал блока 9 остается равным нулю, но теперь при обнаружении третьего отказа или сбоя блок 9 выдает сигнал ошибки. Откорректированные разряды кода вьщаются на информационный выход 19. После фиксации второго отказа блоком 5, как отмечалось, блок 9 разблокируется и проводит контроль по трем контрольным суммамЗЦМ, 5UM2, S(JM3, обеспечивая бесперебойную работу устройства при любом из векторов синдрома К4, соответствующих первым четырем строкам таблицу. При появлении третьего отказа или сбоя блок 9 фиксирует факт его появления, если уже зафиксирована двойная ошибка, то выдается сигнал ошибки на выход 20. Если же к моменту фиксации третьего отказа не зафиксирована двойной ошибка, то третий отказ приводит к одиночной ошибке, а не к тройной, так как в силу ординарности потока отказов любой тройной ошибке должна предшествовать двойная ашибка. Поэтому блок 9 фиксирует факт наличия более двух отказов, но выдает сигнал ошибки только при последующем обнаружении двойной ошибки. Поскольку третий отказ проявляется как одиночный отказ, то сигнал на выходе 39 блока 6 равен нулю, группа элементов И 10 блокирована. Вектор синдрома третьего отказа проходит без изменения группу сумматоров 11 по модулю два, дешифрируется дешифратором 12, поступает на группу сумматоров 7, где производится коррекция искаженного разряда кода. По стробу 53 информационные разряды кода выдаются на выходные шины. Аналогично устройство исправляет ошибки, вызванные четвертым, пятым, и т.д. отказом, до тех пор, пока не зафиксирована двойная ошибка. Основные работы блоков фиксации отказов. В начальный момент времени еди- ничным сигналом по входу 28 блок устанавливается в исходное состояние, все счетчики обнулены. На первых выходах счетчиков устанавливаются нулевые сигналы, на выходах единичные. На выходе элемента И 54 устанавливается единичный сигнал, поступающий на выход 35 блока и на вход элементов И-НЕ и разрешающий его работу от тактовых импульсов, поступающих на вход 31. Входы 32 и 33 блока являются блокировочными, нулевой сигнал на входе 32 или единичный сигнал на входе 33 запреают прохождение тактовых импульсов ерез элементы И-НЕ 51 и ИЛИ-НЕ 57 пя стробирования записи вектора индрома по входам +1 счетчиков Подключение элементов И-НЕ 55 к С-входу и входу 4-1 счетчиков повьшает помехоустойчивость последних На временных диаграммах, иллюстрирутощих работу блока (фиг.5), цифр у осей ординат соответствуют номера входов и элементов блока, чей выходной сигнал изображен по данной оси. Запись вида 56(,2,4,8j9) обеспечивает соответствующий вьтход выбранного счетчика. Случай 1 соответствует кратковременному сбою, приводящему к неустойчивому сигналу на выходах 27. Как видно из диаграммы, сигнал на выходе 35 блока остается равным единице, на выходах 34 значение .сигналов не изменяется и очередным сброса по входу 29 (или наглядности показан сразу после строба 52) счетчика снова обнуляются, Случай 2 соответствует вектору синдрома устойчивого отказа. Сигнал на выходе 35 блока становится равным нулю, тем самым блокирует ся работа элементов И 52 и И-НЕ 51 чем счетчики защищаются от сигнала сброса по входу 29 и от приема нового вектора синдрома. На выходах 34 устанавливается вектор синдр ма зафиксированного отказа. Вьщача вектора синдрома по первым выходам счетчиков, блокировка их работы по ВЕ.кодам 9 сведена с целью защиты от разброса временных характеристик счетчиков. Так, если проводить блокировку сигналами с первых выходов, то первый сработавший счетчик может заблокировать остальные счетчики и не пропустить в для записи восьмой тактовый импульс, что искажает запомненный вектор синдрома. Блокировка по сигнгшам с выходов блока 9 исключает такую ситуацию. Блок 6 обнаружения опшбки (фиг.4 работает следующим образом. В условиях отсутствия ошибок, вызванных отказами или сбоями блок 1 и 2, по входу 36 поступает нулевой вектор синдрома и на втором вы ходе 40 устанавливается единичный сигНсШ сумматора 71 по модулю два, выполняя операцию над всеми разрядами кода,формируют на выходе единичный сигнал, так как организован контроль по нечетности. Но элемент И 73 блокирован нулевым сигналом с выхода элемента ИЛИ 70, поэтому сигнал на первом выходе 39 равен нулю. При появлении ненулевого вектора синдрома на входах 36 на выходе элемента ИЛИ 70 формируется единичный сигнал. На выходе элемента НЕ 72 устанавливается нулевой сигнал. Если ошибка является однократной или трехкратной, то на выходе сумматора 71 по модулю два устанавливается нулевой сигнал, В результате элемент И 73 остается заблокированным по второму входу и на выходе 39 присутствует нулевой сигнал. Если же ошибка является двухкратной, то выходной сигнал сумматора 71 по модулю два равен единице и на выходе 39 устанавливается единичный сигнал, указывакнций на наличие двойной ошибки. Блок формирования сигнала ошибки работает следующим образом. I В начальный момент времени единичным сигналом по входу 42 триггеры 67 и 68 устанавливаются в нулевое состояние. На входах 47 и 48 блокировки присутствуют единичные сигналы, на входе 49 присутствует нулевой сигнал. На входах 43,45 и 46 присутствуют нулевые вектора синдромов. На вход 44 подается нулевой сигнал первой контрольной суммы (SUM1). Так как блок 9 блокирован по входу 47 до тех пор, пока блок 5 не зафиксирует второй отказ, то рассматриваем работу блока 9 только после фиксации второго отказа. Фиксация второго отказа блоком 5 приводит к установлению нулевого сигнала на входе 4/, что снимает блокировку элемента ИЛИ-НЕ 64 и элемента ИЛИ-НЕ 65, разрешая установку в единичное состояние по 3-входам триггеров 67 и 68. Группа сумматоров 58 по модулю два формирует третий контрольный вектор синдрома КЗ (КЗ К1©К2), где К1 вектор синдрома, запомненный блоком 4, К2 - вектор синдрома, запомненный блоком 5, Группа сумматоров 59 по модулю два формирует вектор второй контрольной суммы SUM2, а группа сумматоров 60 по модулю два формирует вектор третьей контрольной суммы 5UM3. Элементы ИЛИ-НЕ 61-63 формируют единичные сигналы, если векторы 5UM3, 5UM2 и SUM1 являются нулевыми. Следовательно, если хотя бы один вектор контрольной суммы является нулевым, то хотя бы один входной сигнал элемента ИЛИ-НЕ 64 является единичным, что блокирует установку J -входов три гера 67 в единичное состояние. При фиксации двух отказов и нулевом векторе синдрома на выходе блока 3 ни одна контрольная сумма не равн нулю, для исключения ложной установ ки триггера 67 в единичное состояни на один из входов элемента ИЛИ-НЕ 64 подается блокирующий единичный сигнал отсутствия ошибок, поступающий на вход 48 блока. При фиксации двух отказов и присутствии единичного сигнала на входе 49 блока на входах D триггер 68 устанавливается единичный сигна Поступление строба S3 на вход 41 блока обеспечивает установку тригге ра 68 в единичное состояние, но так как триггер 67 по-прежнему находится в нулевом состоянии, элемент И 69 заблокирован по первому входу. При появлении ошибки, вызванной третьим отказом или сбоем, все векторы контрольных сумм ненулевые. Блокировка элемента ИЛИ-НЕ 64 по входу 48 блока снята, и на J-входах триггера 67 устанавливается единичный сигнал, который по стробу 53 на входе 41 блока устанавливает триггер 67 в единичное состояние. Если при этом триггер 68 уже установлен в единицу (что свидетель.ствует о фиксации двойной ошибки), то на выходе элемента И 69 устанавливается : единичный сигнал неисправимой ошибки. Если же третий отказ проявляется до появления двойной ошибки, то вначале в единичное состояние уста новлен триггер 67, а при первом появлении двойной ошибки (даже вызванной одним из зафиксированных отказов и сбоем) установлен в единичное состояние триггер 68, что приводит к появлению единичного сигнала на выходе элемента И 69, который подключен к контрольному выходу устройства,

,

5

,

,.

Tni,

9t9Q

8S 91 « «;

f

Т

Ss iSiftgit:

;8fe8t

1

« б

ФигЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Самокорректирующиеся дискретные устройства | |||

| М., Машиностроение, 1975, с.95 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| и Руднев Ю.П | |||

| Повышение надежности цифровых устройств методами избыточного кодирования | |||

| М., Энергия, 1974, с.187-188, рис.7.1 и 7.5. | |||

Авторы

Даты

1984-10-23—Публикация

1982-08-25—Подача