14)

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1985 |

|

SU1300627A1 |

| Устройство для получения суммы и разности частот двух импульсных последовательностей | 1988 |

|

SU1629971A1 |

| Устройство для вычитания и добавления импульсов | 1989 |

|

SU1667233A1 |

| Синтезатор частот | 1986 |

|

SU1385231A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Генератор инфранизких частот | 1986 |

|

SU1429302A1 |

| Устройство синхронизации | 1981 |

|

SU1125759A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Цифровой фазометр | 1983 |

|

SU1155957A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

Изобретение относится к радиотехнике. , Цель изобретения - расширение диапазона выходных частот. Синтезатор содержит опорный г-р 1, делитель 2 частоты на М, D-триггеры 8 и 9, делитель 10 частоты на К, эл-т НЕ 11, сумматор 12 по модулю два и блоки преобразования (БП) 3, каждый из которых состоит из сумматора 4, электронного ключа 5, делителя 6 частоты на два и D-триггера 7. Импульсная последовательность (ИП) с частотой fon от г-ра 1 поступает на последовательно соединенные БП 3 непосредственно и через делитель 2. На выходе последнего БП 3 образуется ИП с частотой F,, фаза которой затем привязывается к фронту сигнала fon с помощью D-триггера 8. Эта ИП поступает на сумматор 12, где складывается с преобразованной входной ИП, имеющей частоту F, /К и фазу, привязанную к спаду fI Т.к. фронты этих ИП не совпадают, то на выходе сумматора 12 формируется ИП с частотой .VK- 1 ™i (Л

п л

11А46688

Изобретение относится к радиотехнике, может быть использовано для генерации импульсных последовательностей с переменной частотой следования импульсов, заданной двоичным кодом в числовой системе, заданной основанием системы счисления, и является усовершенствованием изобретения по авт. св. 1 1300627.

Целью изобретения является расширение диапазона выходных частот.

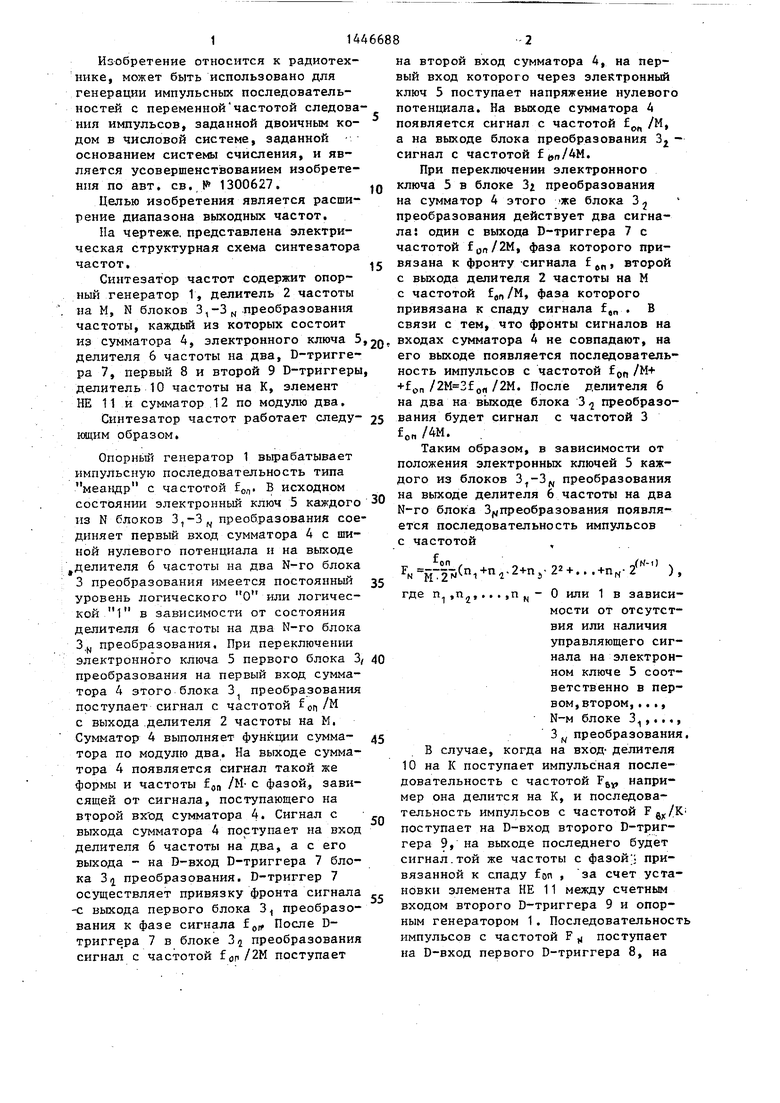

Па чертеже, представлена электрическая структурная схема синтезатора частот.

Синтезатор частот содержит опор- ньлй генератор 1, делитель 2 частоты на М, N блоков 3,-3 .преобразования частоты, каждьй из которых состоит

на второй вход сумматора 4, на первый вход которого через электронный ключ 5 поступает напряжение нулевого потенциала. На выходе сумматора А

появляется сигнал с частотой „ /М,

Зг10

15

on а на выходе блока преобразования

сигнал с частотой f (,п/4М.

При переключении электронного ключа 5 в блоке Зг преобразования на сумматор 4 этого же блока 3 преобразования действует два сигнала; один с выхода D-триггера 7 с частотой fon/2М, фаза которого привязана к фронту сигнала f „, второй с выхода делителя 2 частоты на М с частотой fjn /М, фаза которого привязана к спаду сигнала ,„ . В

связи с тем, что фронты сигналов на из сумматора 4, электронного ключа 5,2Q, входах сумматора 4 не совпадают, на делителя 6 частоты на два, D-триггера 7, первый 8 и второй 9 D-триггеры, делитель 10 частоты на К, элемент НЕ 11 и сумматор 12 по модулю два.

Синтезатор частот работает следу- 25 ющим образом.

его выходе появляется последовательность импульсов с частотой fon/М+ +fon ofl /2М. После делителя 6 на два на выходе блока 3 преобразования будет сигнал с частотой 3

fonMM.

Опорньш генератор 1 вырабатывает импульсную последовательность типа с частотой Гол- Б исходном

меавдр

5 каждого 30

3,-3 1 преобразования соесостоянии электронный ключ

из N блоков

II

диняет первый вход сумматора 4 с шиной нулевого потенциала и на выходе делителя 6 частоты на два N-ro блока 3 преобразования имеется постоянный 35 уровень логического О или логической 1 в зависимости от состояния делителя 6 частоты на два N-ro блока 3,| преобразования. При переключен1 ш электронного ключа 5 первого блока 3 40 преобразования на первый вход сумматора 4 этого блока 3 преобразования

и f on /М

поступает сигнал с частотой -сп с выхода .делителя 2 частоты на М. Сумматор 4 выполняет функции сумматора по модулю два. На вьжоде сумматора 4 появляется сигнал такой же формы и частоты /М- с фазой, зависящей от сигнала, поступающего на второй вх од сумматора 4. Сигнал с выхода сумматора 4 поступает на вход елителя 6 частоты на два, а с его выхода - на D-вход D-триггера 7 блока 3(j преобразования. D-триггер 7 осуществляет привязку фронта сигнала с выхода первого блока 3 преобразования к фазе сигнала После D- триггера 7 в блоке 3 преобразования сигнал с частотой fan/2М поступает

45

50

55

на второй вход сумматора 4, на первый вход которого через электронный ключ 5 поступает напряжение нулевого потенциала. На выходе сумматора А

появляется сигнал с частотой „ /М,

Зг0

5

on а на выходе блока преобразования

сигнал с частотой f (,п/4М.

При переключении электронного ключа 5 в блоке Зг преобразования на сумматор 4 этого же блока 3 преобразования действует два сигнала; один с выхода D-триггера 7 с частотой fon/2М, фаза которого привязана к фронту сигнала f „, второй с выхода делителя 2 частоты на М с частотой fjn /М, фаза которого привязана к спаду сигнала ,„ . В

связи с тем, что фронты сигналов на входах сумматора 4 не совпадают, на

его выходе появляется последовательность импульсов с частотой fon/М+ +fon ofl /2М. После делителя 6 на два на выходе блока 3 преобразования будет сигнал с частотой 3

fonMM.

Таким образом, в зависимости от положения электронных ключей 5 каждого из блоков преобразования на выходе делителя 6 частоты на два N-ro блока 3 преобразования появляется последовательность импульсов с частотой ,

„

FN -2

/N-0

)

де п

,n,j,,. . ,п

О или 1 в зависимости от отсутствия или наличия управляющего сигнала на электронном ключе 5 соответственно в первом, втором, .. .,

N-M блоке 3

1 «

5

0

N

В случае, когда на вход- делителя 10 на К поступает импульсная последовательность с частотой Fjy например она делится на К, и последовать

тельность импульсов с частотой

5

поступает на D-вход второго D-триггера 9, на выходе последнего будет сигнал.той же частоты с фазой;; привязанной к спаду fon , за счет установки элемента НЕ 11 между счетным входом второго D-триггера 9 и опорным генератором 1. Последовательность импульсов с частотой F поступает на D-вход первого D-триггера 8, на

31

выходе которого будет сигнал той же частоты с фазой, привязанной к фронту сигнала fon . В результате на выход сумматора 12 по модулю два поступает два сигнала: один с выхода первого D-триггера 8 с частотой F, фаза которого привязана к фронту сигнала ,„ , второй с выхода второг

D-триггера 9 с частотой ,фаза которого привязана к спаду сигнала fоп В связи с тем, что фронты сигналов на входах сумматора 12 по модулю два не совпадают, на его выход ,появляется последовательность импульсов с частотой

Fe,, FSX/K- В связи с тем, что формирование

необходимой частоты происходит в любой системе счисления К без применения УЗКОПОЛОСНЫХ фильтров, скорость установки частоты и диапазон рабочи частот зависят только от времени включения и предельной частоты работы применяемых микросхем.

При соединении j таких синтезаторов частот на выходе последнего будет последовательность импульсов с частотой

FBH« Fj-+F, -i /K+F,-., /K2 + ...+F, ,

где F,,.., ,F-, ,Fj - собственные частоты соответст

вующкх- двоичных синтезаторов} - основание системы счисления, причем К 2 4N - число блоков 3,-3,у преобразования) ,

Формула изобретения

Синтезатор частот по авт. св. № 1300627 отличающийся тем, что, с целью расширения диапазона выходных частот, введены элемент НЕ, первый D-триггер и последовательно соединенные делитель частоты на К, второй D-триггер и сумматор по модулю два, выход которого является вькодом синтезатора частот, при этом первый вход и выход первого D-триггера подключены соответственно к выходу делителя частоты на два N-ro блока преобразования частоты и к второму входу сумматора по модулю два, второй вход первого D-триггера соединен с входом элемента НЕ и подключен к выходу опорного генератора, выход элемента НЕ соединен с вторым входом второго D-триггера, а вход делителя частоты на К является вхо- дом синтезатора частот.

| Синтезатор частот | 1985 |

|

SU1300627A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-23—Публикация

1986-05-16—Подача