(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬ УРОВНЯ ШУМОВОЙ ИНТЕРМОДУЛЯЦИИ | 2003 |

|

RU2252425C2 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Ультразвуковой дефектоскоп | 1988 |

|

SU1627974A1 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1987 |

|

SU1443745A1 |

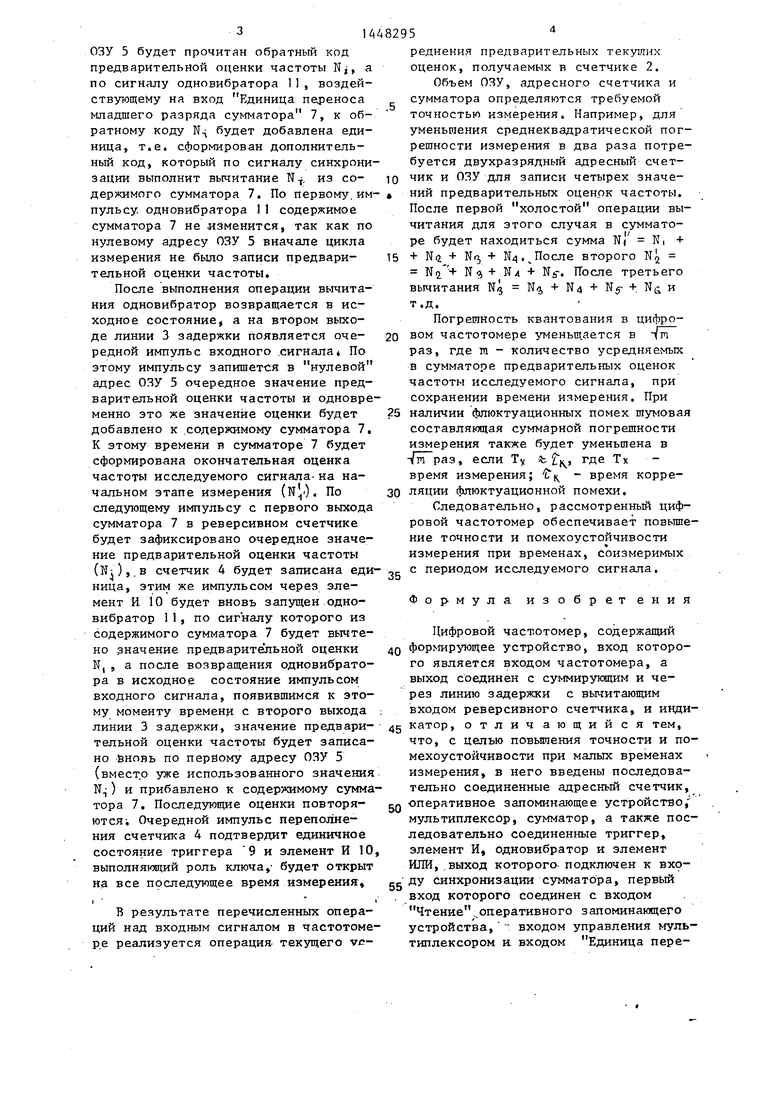

Изобретение относится к измерительной технике. Устройство содержит формирующее устройство 1, реверсивный счетчик 2, линию 3 задержки и индикатор 8. Введение адресного счетчика 4, оперативного запоминающего устройства 5, мультиплексора 6, сумматора 7, триггера 9, элемента И 10, одновибратора 11 и элемента ИЛИ 12 позволяет повысить точность и помехо:устойчивость измерения частоты при малых временных измерениях, соизмеримых с периодом исследуемого сигнала. 1 ил.

4ai 4 00 tN5

СО

СП

Изобретение относится к измерительной технике и может быть использовано для измерения частоты гармонических или импульсных сигналов о

Цель изобретения - повьппение точности и помехоустойчивости измерения частоты при малых временах измерения Цифровой частотомер содержит формирующее устройство 1., вход которо- го является входом частотомера, а выход которого соединен с суммирующим входом реверсивного счетчика 2 .и вхо дом, линии 3 задержки. Первый выход линии задержки подключен к цепочке последовательно соединенных адресного счетчика 4, оперативного запоминающего устройства (ОЗУ) 5, мультиплексора 6, сумматора 7 и индикатора 8. Выход,переполнения счетчика 4 подключен к цепочке последовательно ..соединенных триггера 9 элемента И 1 одновибратора 11 и элемента ИЛИ 12, Выход элемента ИЛИ 12 подключен к входу синхронизации сумматора 7, пер вый вход элемента ИЛИ 12 соединен также с входом Чтение ОЗУ 5, входом управления мультиплексором 6 и входом .Единица-переноса младшего разряда сумматора 7. Второй, вход элемента ИЛИ 12 соединен с входом Запись ОЗУ 5 и вторым выходом линии 3 задержки, первый выход которой также подключен к вычитающему входу реверсивного счетчика 2 и к второму входу элемента И 10. Выход счетчика 2 соединен с вторым входом мультиплексора 6 и шиной входа ОЗУ 5,v

Цифровой частотомер работает следующим образом.

Входной сигнал, частоту которого необходимо измерить, поступает на вход формирующего устройства 1, на- выходе которого образуется поток импульсов , соответствующих моментам перехода гармонического сигнала через нулевой уровень. Эта последовательность импульсов поступает на суммирующий вход реверсивного счетчика 2, а после задержки на время усреднения Т, задаваемое линией 3 задержкиj эта же последовательность импульсов поступает на вычитающий вход реверсивного счетчика 2, После поступления на вычитающий вход счетчика 2 первого импульса задержанной импульсной последовательности в счетчике 2 будет находиться результат предварительной оценки измерения частоты N,. Этот же первый импульс, воздействуя на счетный вход счетчика 4, находящегося в нулевом исходном состоянии, переведет его первый разряд в положение Г ,что будет соответствовать первому дpe- су ОЗУ 5 и через время, определяемое временем срабатывания счетчика 2 и счетчика 4, на втором выходе линии 3 задержки также появляется первый им- пуль-с последовательности, поступающей с формирующего устройства 1.Этот импульс, воздействуя на вход - запись ОЗУ 5, запишет состояние счетчика 2 по первому адресу, предварительно заданному счетчиком 4. Одновременно этот же импульс, воздействуя через элемент ИЛИ 12 на вход синхронизации сумматора 7, запишет значение предварительной оценки частоты N, сформированной в счетчике 2, через мультиплексор 6 в сумматор 7. При поступлении второго импульса входного сигнгша с первого выхода линии 3 задержки в счетчике 2 будет сформирована вторая предварительная оценка частоты исследуемого сигнала Ntj.

Счетчик 4 по этому импульсу также изменит свое состояние - оно будет соответствовать второму адресу.Второй импульс исследуемого сигнала, появившийся после задержки с второго выхода линии 3 задержки, запишет состояние счетчика 2 по второму адресу ОЗУ 5 и в сумматор 7. Состояние сумматора 7 будет Ng. W,) + KQ, Последующа.я работа цифрового частотомера не будет иметь особенностей до переполнения счетчика 4, сигнал переполнения которого переведет триггер 9 в состояние 1, Очередной импульс с первого выхода линии 3 за- держки установит счеТчик 4 в исход- нов состояние и, одновременно, проходя через элемент И 10, запустит од- новибратор 11. Сигнал одновибратора 11, воздействуя на вход управления мультиплексора 6, подключит выходную шину ОЗУ 5 к выходу сумматора 7 и од- нов ременнр, воздействуя на вход Чтение ОЗУ 5 и вход Единица переноса младшего разряда сумматора 7, подготовит необходимые режимы для осуществления операция вычитания в сумматоре 7. Этот же импульс, воздействия через элемент ШШ 12 на вход синхронизации сумматора 7, обеспечит выполнение этой операции. С выхода

31

ОЗУ 5 будет прочитан обратный код предварительной оценки частоты NJ, а по сигналу одновибратора 11, воздействующему на вход Единица переноса младшего разряда сумматора 7, к обратному коду Ид будет добавлена единица, т.е. сформирован дополнительный код, который по сигналу синхронизации выполнит вычитание N, из содержимого сумматора 7. По первому, им пульсу, одновибратора 1 1 содержимое сумматора 7 не изменится, так как по нулевому адресу ОЗУ 5 вначале цикла измерения не было записи предварительной оценки частоты.

После выполнения операции вычитания одновибратор возвращается в исходное состояние, а на втором выходе линии 3 задержки появляется очередной импульс входного .сигнала По этому импульсу запишется в нулевой адрес ОЯУ 5 очередное значение предварительной оценки частоты и одновременно это ке значение оценки будет добавлено к .содержимому сумматора 7, К этому времени в сумматоре 7 будет сформирована окончательная оценка частоты исследуемого сигнала-на начальном этапе измерения (. По следующему импульсу с первого выхода сумматора 7 в реверсивном счетчике будет зафиксировано очередное значение предварительной оценки частоты (NJ),.B счетчик 4 будет записана еди ница, этим же импульсом через элемент И 10 будет вновь запущен одно- вибратор 11, по сигналу которого из содержимого сумматора 7 будет вычтено значение предварительной оценки

N.

а после возвращения одновибратоЦифровой част.отомер, содержащий 4Q формирующее устройство, вход которого является входом частотомера, а выход соединен с суммируклцим и через линию задержки с вычитающим входом реверсивного счетчика, и инди- jg катер, отлич ающийся тем, что, с целью повьшения точности и помехоустойчивости при малых временах

измерения, в него введены последовара в исходное состояние импульсом входного сигнала, появившимся к этому моменту времени с второго выхода , линии 3 задержки, значение предварительной оценки частоты будет записано йновь по пербому адресу ОЯУ 5 (вмест.о уже использованного значения W ) и прибавлено к содержимому сумма- тельно соединенные адресный счетчик, тора 7, Последующие оценки повторя- Q оперативное запоминающее устройство, ются; Очередной импульс переполне-мультиплексор, сумматор, а также последовательно соединенные триггер, элемент И, одновибратор и элемент ИЛИ,.выход которого подключен к вхо- с(. ду синхронизации сумматора, первый . вход которого соединен с входом Чтение оперативного запоминающего устройства, : входом управления мультиплексором и. входом Единица перения счетчика 4 подтвердит единичное состояние триггера 9 и элемент И 10, выполнякщий роль ключа,- будет открыт на все последующее время измерения.

В результате перечисленных операций над входным сигналом в частотомере реализуется операция текущего vc

реднения предварительных текумих оценок, получаемых в счетчике 2.

Объем ОЯУ, адресного счетчика и сумматора определяются требуемой точностью измерения. Например, для уменьшения среднеквадратической погрешности измерения в два раза потребуется двухразрядный адресный счетчик и ОЯУ для записи четырех значений предварительных оцен.ок частоты. После первой холостой операции вычитания для этого случая в сумматоре будет находиться сумма N( N, + + N(i + No, + Ni).После второго N5 N4 + Ni. После третьего вычитания Ni3 N4 + N4 + N5- + Ng и т,д,

Погрешность квантования в цифро

вом частотомере уменьшается в in раз, где та - количество усредняемых в сумматоре предварительных оценок частоты исследуемого сигнала, при сохранении времени измерения. При

наличии флюктуационных помех шумовая составляющая суммарной погрешности измерения также будет уменьшена в /г-Граз, если Ту Гк где Тх время измерения; iTi - время корреляции флюктуационной помехи.

Следовательно, рассмотренный цифровой частотомер обеспечивает повьшге- ние точности и помехоустойчивости измерения при временах, соизмеримых с периодом исследуемого сигнала,

Фор-мула изобретения

с

Цифровой част.отомер, содержащий 4Q формирующее устройство, вход которого является входом частотомера, а выход соединен с суммируклцим и через линию задержки с вычитающим входом реверсивного счетчика, и инди- jg катер, отлич ающийся тем, что, с целью повьшения точности и помехоустойчивости при малых временах

тельно соединенные адресный счетчик, Q оперативное запоминающее устройство, мультиплексор, сумматор, а также посизмерения, в него введены последовательно соединенные адресный счетчик, оперативное запоминающее устройство, мультиплексор, сумматор, а также пос.11

носа младшего разряда сумматора,выход перетолнения которого соеди- второй вход элемента ИЛИ соединен сиен с триггером, при этом выход ре- входом Запись оперативного запоми-версивного счетчика соединен с вто- нающе1 о устройства и вторым выходомрым входом мультиплексора и шиной пинии задержки, первый выход которойвхода оперативного запоминающего . также подключен к второму входу эле-устройства, а выход сумматора под- мента И и входу адресного счетчика,ключей к индикатору.

| 0 |

|

SU161417A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматические измерения и приборы, - Киев: Вища школа, 1980, с | |||

| Саморазгружающаяся железнодорожная платформа | 1921 |

|

SU366A1 |

| J | |||

Авторы

Даты

1988-12-30—Публикация

1986-12-26—Подача