Изобретение относится к области вычислительной техники и может быть использовано при контроле полупроводниковых оперативных запоминающих устройств (ОЗУ) динамического типа.

Цель изобретений - повышение достоверности контроля.

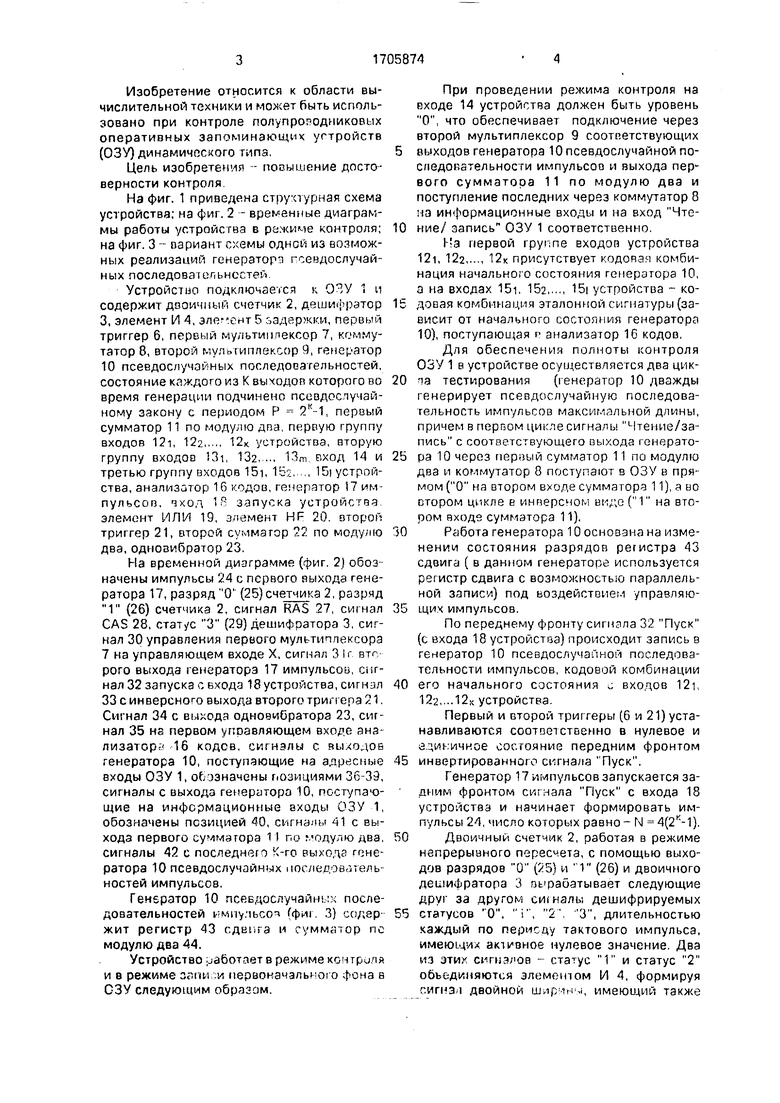

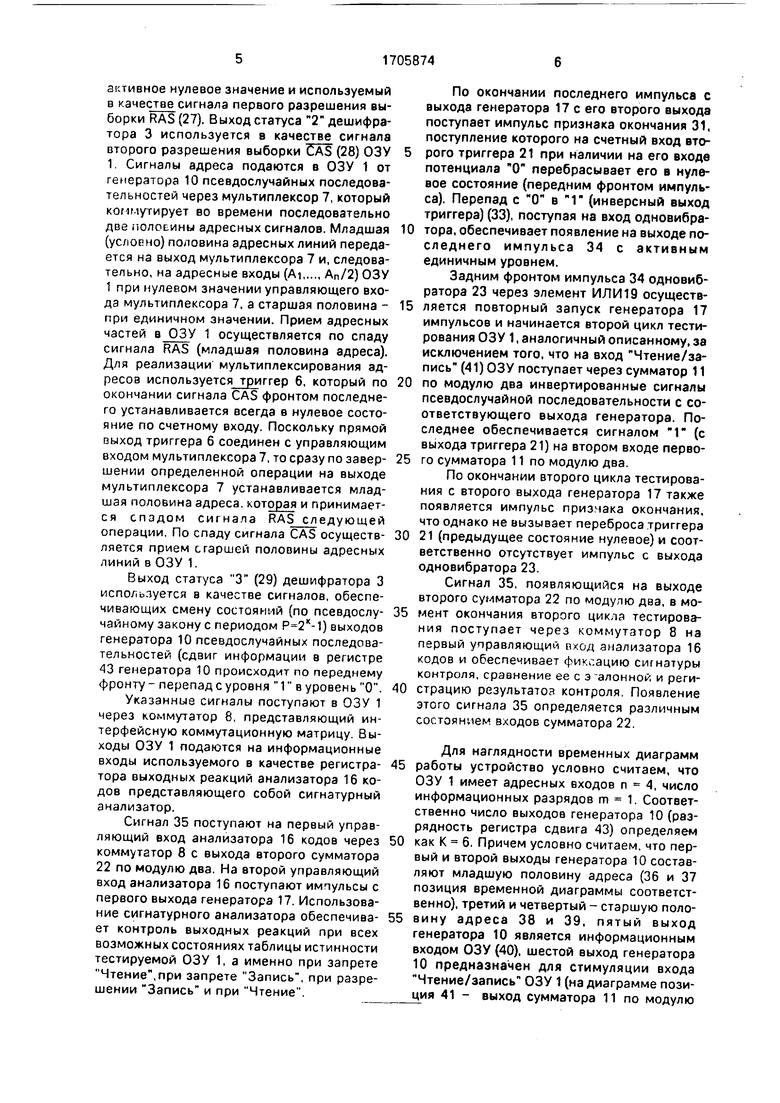

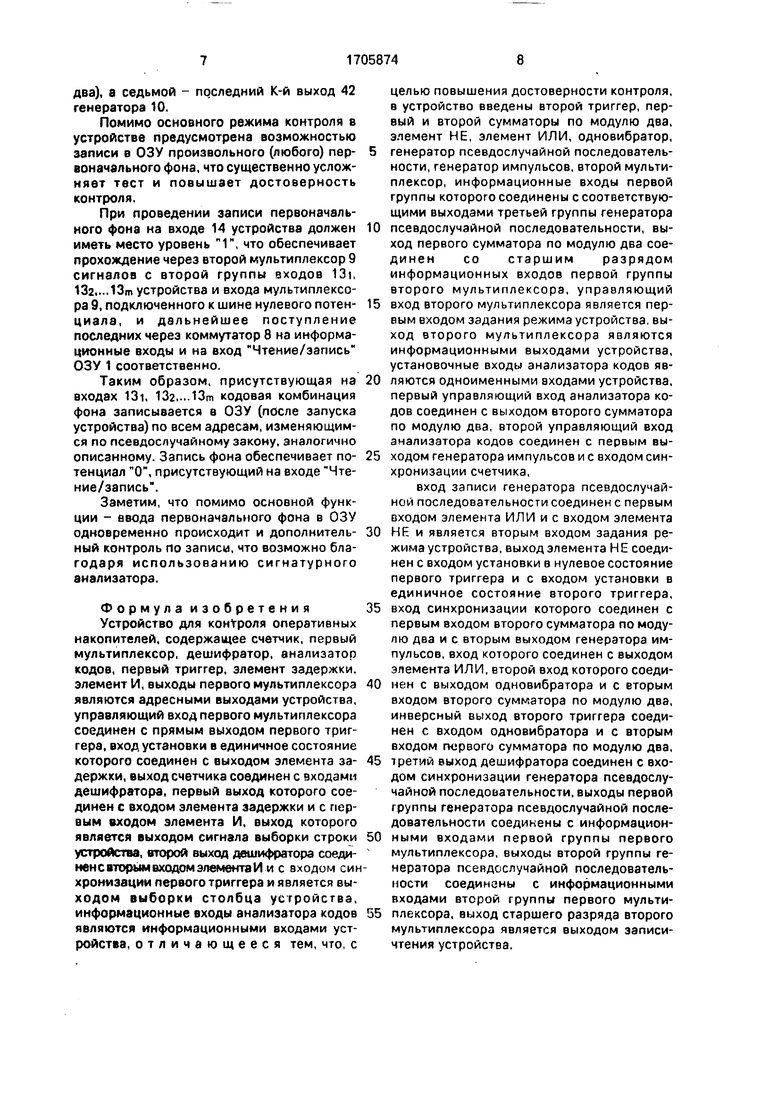

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства в режиме контроля; на фиг. 3 - вариант схемы одной из возможных реализаций генератора псевдослучайных последовательностей,

Устройство подключается к ОЗУ 1 и содержит двоичный счетчик 2, дешифратор 3, элемент И А, .снт 5 задержки, первый триггер 6, первый мультиплексор 7, коммутатор 8, второй мультиплексор 9, генератор 10 псевдослучайных последовательностей, состояние каждого из К выходов которого во время генерации подчинено псевдослучайному закону с периодом Р - 2к-1, первый сумматор 11 по модулю два, первую группу входов 12ч, 122,..., 12к устройства, вторую группу входов 13т, 132, ... 13m вход 14 и третью группу входов 15i, 15г...., 15i устройства, анализатор 16 кодов,генератор 17 импульсов, чход 18 запуска устройства элемент ИЛИ 19, элемент HF 20, второй триггер 21, второй сумматор 22 по модулю два, одновибратор 23.

На временной диаграмме (фиг. 2) обозначены импульсы 24 с первого выхода генератора 17, разряд О (25) счетчика 2, разряд 1 (26) счетчика 2, сигнал RAS 27, сигнал CAS 28, статус 3 (29) дешифратора 3, сигнал 30 управления первого мультиплексора 7 на управляющем входе X, сигнал 3 If второго выхода генератора 17 импульсов, сигнал 32 запуска с входа 18 устройства, сигнал 33 с инверсного выхода второго триггера 21. Сигнал 34 с выхода одновибратора 23, сигнал 35 не первом управляющем входе анализатора 16 кодов, сигналы с. выходов генератора 10, поступающие на адресные входы ОЗУ 1, обозначены позициями Зб-ЗЭ, сигналы с выхода генератора 10, поступающие на информационные входы ОЗУ 1, обозначены позицией 40, сигналы 41 с выхода первого сумматора 11 по модулю два, сигналы 42 с последнего К-го выхода генератора 10 псевдослучайных последовательностей импульсов.

Генератор 10 псевдослучайных последовательностей имиульсо (фиг. 3) содержит регистр 43 сдвига и сумматор по модулю два 44.

Устройство работает в режиме контроля и в режиме записи первоначального фона в ОЗУ следующим образом.

При проведении режима контроля на входе 14 устройства должен быть уровень О, что обеспечивает подключение через второй мультиплексор 9 соответствующих

выходов генератора 10 псевдослучайной последовательности импульсов и выхода первого сумматора 11 по модулю два и поступление последних через коммутатор 8 на информационные входы и на вход Чте0 ние/ запись ОЗУ 1 соответственно.

На первой группе входов устройства 12i, 122,..., 12х присутствует кодовая комбинация начального состояния генератора 10, а на входах 15i, 152,..., 15i устройства - ко5 довая комбинация эталонной сигнатуры (зависит от начального состояния генератора 10), поступающая г анализатор 16 кодов,

Для обеспечения полноты контроля ОЗУ 1 в устройстве осуществляется два цик0 па тестирования (генератор 10 дважды генерирует псевдослучайную последовательность импульсов максимальной длины, причем в первом цикле сигналы Чтение/запись с соответствующего выхода генерато5 ра 10 через первый сумматор 11 по модулю два и коммутатор 8 поступают в ОЗУ в прямом (О на втором входе сумматора 11), а во втором цикле е инверсном виде (1 на втором входе сумматора 11).

0 Работа генератора 10 основана на изменении состояния разрядов регистра 43 сдвига ( в данном генераторе используется регистр сдвига с возможностью параллельной записи) под воздействием управляю5 щих импульсов.

По переднему фронту сигнала 32 Пуск (с входа 18 устройства) происходит запись в генератор 10 псевдослучайной последовательности импульсов, кодовой комбинации

0 его начального состояния и входов 12i, 12з,...12к устройства.

Первый и второй триггеры (6 и 2 устанавливаются соответственно в нулевое и единичное состояние передним фронтом

5 инвертированного сигнала Пуск.

Генератор 17 импульсов запускается задним фронтом сигнала Пуск с входа 18 устройства и начинает формировать импульсы 24, число которых равно- N 4(2к-1).

0Двоичный счетчик 2, работая в режиме непрерывного пересчета, с помощью выходов разрядов О (25) и 1 (26) и двоичного дешифратора 3 вьфабатывает следующие друг за другом сигналы дешифрируемых

5 статусов 0, i, 2, 3, длительностью каждый по периоду тактового импульса, имеющих активное нулевое значение. Два из этих сигналов - статус 1 и статус 2 объединяются элементом И 4, формируя сигнал двойной ширяи .-i, имеющий также

активное нулевое значение и используемый в качестве сигнала первого разрешения выборки RAS (27). Выход статуса дешифратора 3 используется в качестве сигнала второго разрешения выборки С AS (28) ОЗУ 1. Сигналы адреса подаются в ОЗУ 1 от генератора 10 псевдослучайных последовательностей через мультиплексор 7, который коммутирует во времени последовательно две ПОЛОЕИНЫ адресных сигналов. Младшая (условно) половина адресных линий передается на выход мультиплексора 7 и, следовательно, на адресные входы (Ai,..., An/2) ОЗУ 1 при нулевом значении управляющего входа мультиплексора 7. а старшая половина - при единичном значении. Прием адресных частей в ОЗУ 1 осуществляется по спаду сигнала RAS (младшая половина адреса). Для реализации мультиплексирования адресов используется триггер 6, который по окончании сигнала CAS фронтом последнего устанавливается всегда в нулевое состояние по счетному входу. Поскольку прямой выход триггера 6 соединен с управляющим входом мультиплексора 7, то сразу по завер- шении определенной операции на выходе мультиплексора 7 устанавливается младшая половина адреса, которая и принимает- ся спадом сигнала RAS следующей операции. По спаду сигнала CAS осуществ- ляется прием старшей половины адресных линий в ОЗУ 1.

Выход статуса 3 (29) дешифратора 3 используется в качестве сигналов, обеспечивающих смену состояний (по псевдослу- чайному закону с периодом ) выходов генератора 10 псевдослучайных последовательностей (сдвиг информации в регистре 43 генератора 10 происходит по переднему фронту - перепад с уровня 1 в уровень О.

Указанные сигналы поступают в ОЗУ 1 через коммутатор 8, представляющий интерфейсную коммутационную матрицу. Выходы ОЗУ 1 подаются на информационные входы используемого в качестве регистра- тора выходных реакций анализатора 16 кодов представляющего собой сигнатурный анализатор.

Сигнал 35 поступают на первый управляющий вход анализатора 16 кодов через коммутатор 8 с выхода второго сумматора 22 по модулю два. На второй управляющий вход анализатора 16 поступают импульсы с первого выхода генератора 17. Использование сигнатурного анализатора обеспечива- ет контроль выходных реакций при всех возможных состояниях таблицы истинности тестируемой ОЗУ 1, а именно при запрете Чтение,при запрете Запись, при разрешении Запись и при Чтение.

По окончании последнего импульса с выхода генератора 17 с его второго выхода поступает импульс признака окончания 31, поступление которого на счетный вход второго триггера 21 при наличии на его входе потенциала О перебрасывает его в нулевое состояние (передним фронтом импульса). Перепад с О в Г (инверсный выход триггера) (33), поступая на вход одновибра- тора, обеспечивает появление на выходе последнего импульса 34 с активным единичным уровнем.

Задним фронтом импульса 34 одновиб- ратора 23 через элемент ИЛИ19 осуществляется повторный запуск генератора 17 импульсов и начинается второй цикл тестирования ОЗУ 1, аналогичный описанному, за исключением того, что на вход Чтение/запись (41) ОЗУ поступает через сумматор 11 по модулю два инвертированные сигналы псевдослучайной последовательности с соответствующего выхода генератора. Последнее обеспечивается сигналом 1 (с выхода триггера 21) на втором входе первого сумматора 11 по модулю два.

По окончании второго цикла тестирования с второго выхода генератора 17 также появляется импульс признака окончания, что однако не вызывает переброса триггера 21 (предыдущее состояние нулевое) и соответственно отсутствует импульс с выхода одновибратора 23.

Сигнал 35, появляющийся на выходе второго сумматора 22 по модулю два, в момент окончания второго цикла тестирования поступает через коммутатор 8 на первый управляющий вход анализатора 16 кодов и обеспечивает фиксацию сигнатуры контроля, сравнение ее с эталонной и регистрацию результатов контроля. Появление этого сигнала 35 определяется различным состоянием входов сумматора 22.

Для наглядности временных диаграмм работы устройство условно считаем, что ОЗУ 1 имеет адресных входов п 4, число информационных разрядов m 1. Соответственно число выходов генератора 10 (разрядность регистра сдвига 43) определяем как К 6, Причем условно считаем, что первый и второй выходы генератора 10 составляют младшую половину адреса (36 и 37 позиция временной диаграммы соответственно), третий и четвертый - старшую половину адреса 38 и 39, пятый выход генератора 10 является информационным входом ОЗУ (40), шестой выход генератора 10 предназначен для стимуляции входа Чтение/запись ОЗУ 1 (на диаграмме позиция 41 - выход сумматора 11 по модулю

два), а седьмой - последний К-й выход 42 генератора 10.

Помимо основного режима контроля в устройстве предусмотрена возможностью записи в ОЗУ произвольного (любого) пер- воначального фона, что существенно усложняет тест и повышает достоверность контроля.

При проведении записи первоначального фона на входе 14 устройства должен иметь место уровень Г, что обеспечивает прохождение через второй мультиплексор 9 сигналов с второй группы входов 13), 132,...13т устройства и входа мультиплексора 9, подключенного к шине нулевого потен- циала, и дальнейшее поступление последних через коммутатор 8 на информационные входы и на вход Чтение/запись ОЗУ 1 соответственно.

Таким образом, присутствующая на входах 13i, 13a,...13m кодовая комбинация фона записывается в ОЗУ (после запуска устройства) по всем адресам, изменяющимся по псевдослучайному закону, аналогично описанному. Запись фона обеспечивает по- тенциал О, присутствующий на входе Чтение/запись.

Заметим, что помимо основной функции - ввода первоначального фона в ОЗУ одновременно происходит и дополнитель- ный контроль по записи, что возможно благодаря использованию сигнатурного анализатора.

Формулаизобретения Устройство для конУроля оперативных накопителей, содержащее счетчик, первый мультиплексор, дешифратор, анализатор кодов, первый триггер, элемент задержки, элемент И, выходы первого мультиплексора являются адресными выходами устройства, управляющий вход первого мультиплексора соединен с прямым выходом первого триггера, вход установки в единичное состояние которого соединен с выходом элемента за- держки, выход счетчика соединен с входами дешифратора, первый выход которого соединен с входом элемента задержки и с первым входом элемента И, выход которого является выходом сигнала выборки строки устройства, второй выход дешифратора соеди- ненс вторым входом элемента И и с входом синхронизации первого триггера и является выходом выборки столбца устройства, информационные входы анализатора кодов являются информационными входами устройства, отличающееся тем, что, с

целью повышения достоверности контроля, в устройство введены второй триггер, первый и второй сумматоры по модулю два, элемент НЕ, элемент ИЛИ, одновибратор, генератор псевдослучайной последовательности, генератор импульсов, второй мультиплексор, информационные входы первой группы которого соединены с соответствующими выходами третьей группы генератора псевдослучайной последовательности, выход первого сумматора по модулю два соединен со старшим разрядом информационных входов первой группы второго мультиплексора, управляющий вход второго мультиплексора является первым входом задания режима устройства, выход второго мультиплексора являются информационными выходами устройства, установочные входы анализатора кодов являются одноименными входами устройства, первый управляющий вход анализатора кодов соединен с выходом второго сумматора по модулю два, второй управляющий вход анализатора кодов соединен с первым выходом генератора импульсов и с входом синхронизации счетчика,

вход записи генератора псевдослучайной последовательности соединен с первым входом элемента ИЛИ и с входом элемента НЕ и является вторым входом задания режима устройства, выход элемента НЕ соединен с входом установки в нулевое состояние первого триггера и с входом установки в единичное состояние второго триггера, вход синхронизации которого соединен с первым входом второго сумматора по модулю два и с вторым выходом генератора импульсов, вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом одновибратора и с вторым входом второго сумматора по модулю два, инверсный выход второго триггера соединен с входом одновибратора и с вторым входом первого сумматора по модулю два, третий выход дешифратора соединен с входом синхронизации генератора псевдослучайной последовательности, выходы первой группы генератора псевдослучайной последовательности соединены с информационными входами первой группы первого мультиплексора, выходы второй группы генератора псевдослучайной последовательности соединены с информационными входами второй группы первого мультиплексора, выход старшего разряда второго мультиплексора является выходом записи- чтения устройства.

М njoj-uxrurij-LruT-rLruani

uxгuтnJ JaлJ гглJ Jтл-ПJгл.

#-r

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для измерения интервалов времени | 1990 |

|

SU1739361A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Изобретение относится к вычислительной технике и может быть использовано при контроле полупроводниковых оперативных запоминающих устройста динамического типа. Устройство подключается к ОЗУ 1 и содержит счетчик 2, дешифратор 3, элемент И4, элемент 5 задержки, первый триггер 6, первый мультиплексор 7, коммутатор 8, второй мультиплексор 9, генератор 10 псевдослучайных последовательностей, сумматор 11 по модулю два, анализатор кодов 16, генератор 17 импульсов, элемент ИЛИ 19, элемент НЕ 20, второй триггер 21, сумматор 22 по модулю два, одновибратор 23. В устройстве предусмотрена возможность задания любого начального состояния генератора псевдослучайных последовательностей импульсов, что позволяет проводить тестирование ОЗУ в условиях ее работы максимально приближенных к реальным, что повышает достоверность контроля и надежность устройства. 3 ил. с L ч о ел 00 х|

| Устройство для контроля микросхем ОЗУ.-Электронная промышленность | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1992-01-15—Публикация

1989-05-16—Подача