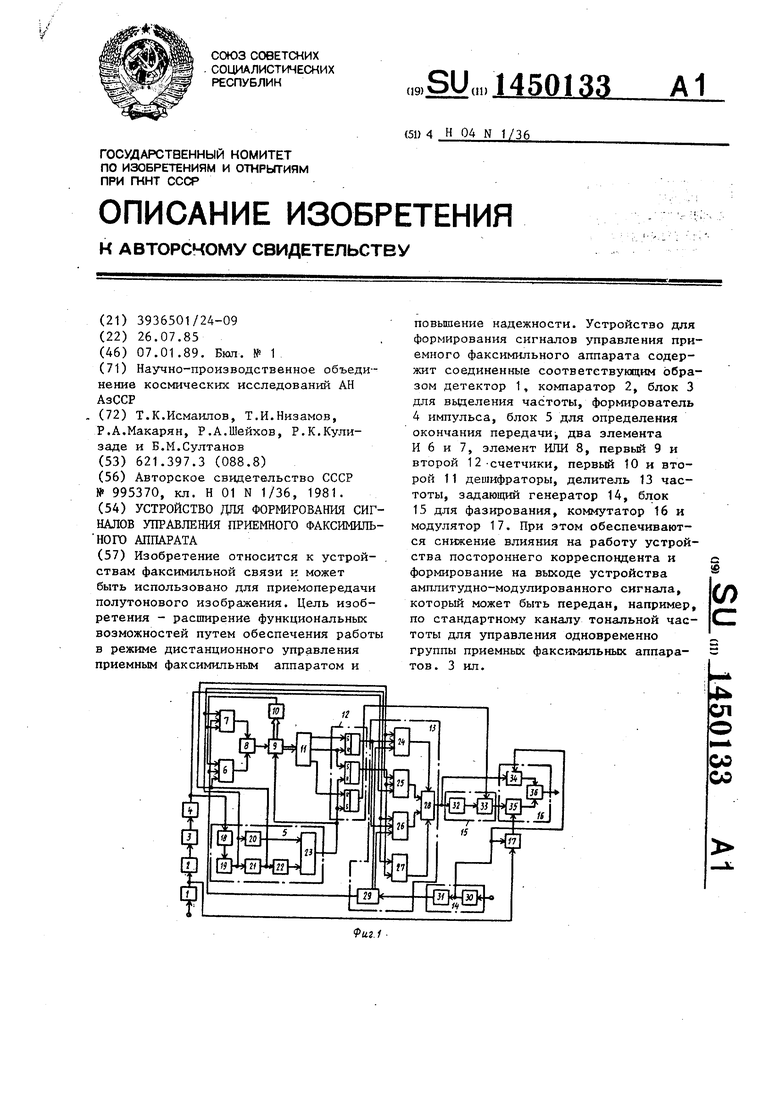

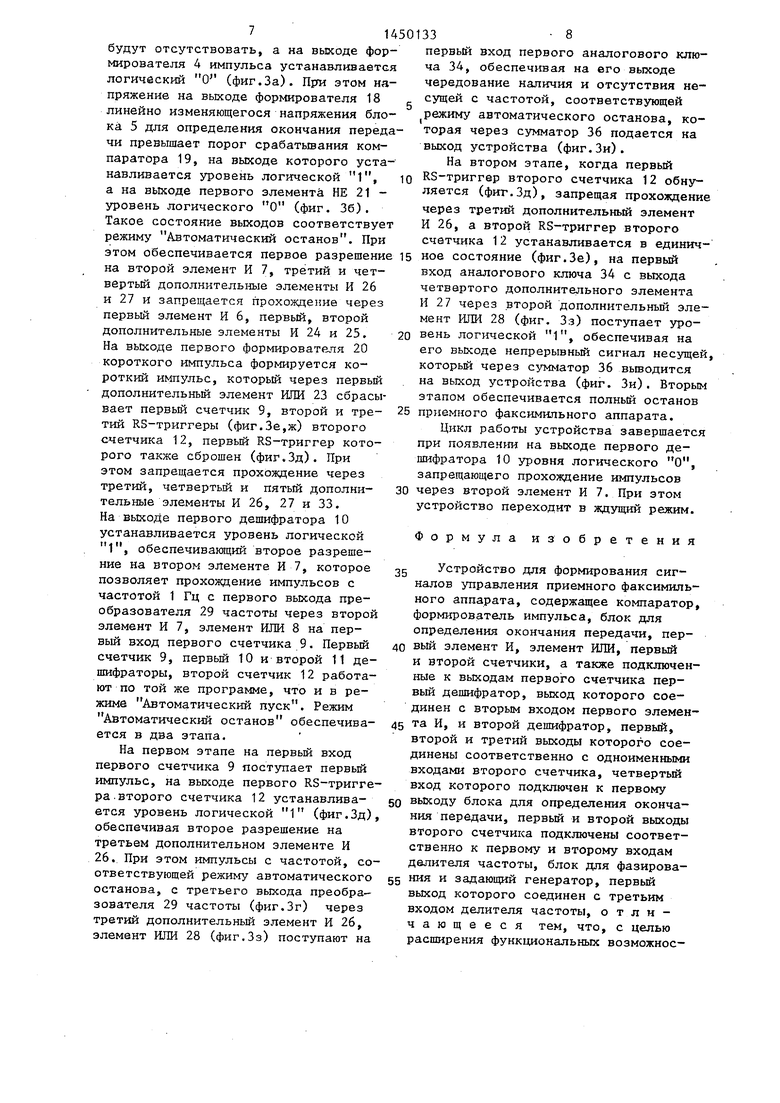

По первому импульсу, поступившему на вход первого счетчика 9, на перво выходе второго дешифратора 11 устанавливается уровень логической 1,ко- торьш записьшается в первый RS-триг- .гер второго счетчика 12, обеспечивая второе разрешение (фиг.Зд) на первом дополнительном элементе И 24.

При этом импульсы с частотой, соответствующей выбору шага (фиг,36), со второго выхода преобразователя 29 частоты через первьй дополнительный элемент И 24 и второй дополни- тельньй элемент ИЛИ 28 (фиг.Зз) поступают .на первьй вход первого аналогового ключа 34, обеспечивая на его вьссоде чередование наличия и отсутствия несущей с частотой выбора шага, которая через сумматор 36 подается на выход устройства (фиг.Зи), связанного с входом приемного факси мильного аппарата, обеспечивая автоматический выбор шага.

Через время, необходимое для выбора шага приемного факсимильного аппарата, первьй счетчик 9 устанавливается в такое состояние, ..при котором логическая 1 появляется на втором выходе второго дешифратора 11. При этом обнуляется первьй RS-триггер (фиг.Зд) второго счетчика 12, запрещая прохождение через первьй дополнительный элемент И 24 импульсов выбора шага со второго выхода преобразователя 29 частоты, и записьшается логическая 1 во второй RS-триггер (фиг. Зе) второго счетчика 12,

ания приемного факсимильного аппарата, первьй счетчик 9 устанавливается

в такое состояние, при котором логическая 1 появляется на третьем выоде второго дешифратора 11 и записывается в третий RS-триггер (фиг.Зж) второго счетчика 12. При этом разрешается прохождение через пятый допол- нительньй элемент И 33, а так как второй RS-триггер второго счетчика - 12 не изменяет своего состояния (фиг. Зе), то импульсы фазовой длительности с выхода второго дополнительного элемента ИЛИ 28 (фиг. Зз) продолжают поступать на первьй анало- говьй ключ 34, обеспечивая передачу фазовых импульсов, а через второй

элемент НЕ 32, открытьй пятьй допол- нительньй элемент И 33 поступает на первьй вход второго аналогового ключа 35, запрещая вывод изображения на время прохождения фазовых импульсов, обеспечивая фазированньй вывод изображения.

С момента записи изображения очередным импульсом, поступающим на первьй счетчик 9, на выходе первого

дешифратора 10 устанавливается уровень логического О, запрещающий прохождение через первьй элемент И 6 импульсов с частотой 1 Гц.

При прекращении подачи на вход

стройства сигнала или при отличии частоты кодового участка входного сигнала от закодированной частоты в блоке 3 для вьщеления частоты на выходе последнего короткие импульсы

будут отсутствовать, а на выходе формирователя 4 импульса устанавливается логический О (фиг.За). Прги этом напряжение на выходе формирователя 18 линейно изменяющегося напряжения бло- ка 5 для определения окончания передачи превышает порог срабатьшания компаратора 19, на выходе которого устанавливается уровень логической 1, ю а на выходе первого элемента НЕ 21 - уровень логического О (фиг. 36). Такое состояние выходов соответствует режиму Автоматический останов. При

первый вход первого аналогового к ча 34, обеспечивая на его выходе чередование наличия и отсутствия сущей с частотой, соответствующей Iрежиму автоматического останова, торая через сумматор 36 подается выход устройства (фиг.Зи).

На втором этапе, когда первьй RS-триггер второго счетчика 12 об ляется (фиг.Зд), запрещая прохоящ через третий дополнительный элеме И 26, а второй RS-триггер второго счетчика 12 устанавливается в еди

этом обеспечивается первое разрешение is ное состояние (фиг.Зе), на первый

на второй элемент И 7, третий и четвертый дополнительные элементы И 26 и 27 и запрещается прохождение через первый элемент И 6, первый, второй дополнительные элементы И 24 и 25. На выходе первого формирователя 20 короткого импульса формируется короткий импульс, который через первый дополнительньй элемент ИЛИ 23 сбрасы вает первьй счетчик 9, второй и третий RS-триггеры (фиг.Зе,ж) второго счетчика 12, первый RS-триггер которого также сброшен (фиг.Зд). При этом запрещается прохождение через третий, четвертый и пятый дополнительные элементы И 26, 27 и 33. На выходе первого дешифратора 10 устанавливается уровень логической

1 , обеспечивающий второе разрешение на втором элементе И 7, которое позволяет прохождение импульсов с частотой 1 Гц с первого выхода преобразователя 29 частоты через второй элемент И 7, элемент ИЛИ 8 на первый вход первого счетчика 9. Первый счетчик 9, первый 10 и второй 11 дешифраторы, второй счетчик 12 работают по той же программе, что и в режиме Автоматический пуск. Режим Автоматический останов обеспечивается в два этапа.

На первом этапе на первый вход первого счетчика 9 поступает первый импульс, на выходе первого RS-тригге- ра.второго счетчика 12 устанавливается уровень логической 1 (фиг.Зд), обеспечивая второе разрешение на третьем дополнительном элементе И 26. При этом импульсы с частотой, соответствующей режиму автоматического останова, с третьего выхода преобразователя 29 частоты (фиг.Зг) через третий дополнительный элемент И 26, элемент ИЛИ 28 (фиг.Зз) поступают на

вход аналогового ключа 34 с выход четвертого дополнительного элемент И 27 через второй дополнительньй э мент ИЛИ 28 (фиг. Зз) поступает ур

20 вень логической 1, обеспечивая н его выходе непрерывньй сигнал несу который через сумматор 36 вьшодитс на вькод устройства (фиг. Зи). Вто этапом обеспечивается полный остан

25 приемного факсимильного аппарата.

Цикл работы устройства завершае при появлении на выходе первого де шифратора 10 уровня логического О запрещающего прохождение импульсов

30 через второй элемент И 7. При этом устройство переходит в ждущий режи

Формула изобретени

35 Устройство для формирования сиг налов управления приемного факсимил ного аппарата, содержащее компарат формирователь импульса, блок для определения окончания передачи, пер

40 вый элемент И, элемент ИЛИ, первый и второй счетчики, а также подключе ные к выходам первого счетчика первый дешифратор, выход которого соединен с вторым входом первого элеме

45 ч И, и второй дешифратор, первый, второй и третий выходы которого сое динены соответственно с одноименным входами второго счетчика, четвертый вход которого подключен к первому

50 выходу блока для определения оконча ния передачи, первьй и второй выход второго счетчика подключены соответ ственно к первому и второму входам делителя частоты, блок для фазирова

55 ния и задающий генератор, первьй выход которого соединен с третьим входом делителя частоты, отличающееся тем, что, с целью расширения функциональных возможноепервый вход первого аналогового ключа 34, обеспечивая на его выходе чередование наличия и отсутствия несущей с частотой, соответствующей Iрежиму автоматического останова, которая через сумматор 36 подается ка выход устройства (фиг.Зи).

На втором этапе, когда первьй RS-триггер второго счетчика 12 обнуляется (фиг.Зд), запрещая прохоящение через третий дополнительный элемент И 26, а второй RS-триггер второго счетчика 12 устанавливается в единичное состояние (фиг.Зе), на первый

is ное состояние (фиг.Зе), на первый

вход аналогового ключа 34 с выхода четвертого дополнительного элемента И 27 через второй дополнительньй элемент ИЛИ 28 (фиг. Зз) поступает уро20 вень логической 1, обеспечивая на его выходе непрерывньй сигнал несущей, который через сумматор 36 вьшодится на вькод устройства (фиг. Зи). Вторым этапом обеспечивается полный останов

25 приемного факсимильного аппарата.

Цикл работы устройства завершается при появлении на выходе первого дешифратора 10 уровня логического О, запрещающего прохождение импульсов

30 через второй элемент И 7. При этом устройство переходит в ждущий режим.

Формула изобретения

35 Устройство для формирования сигналов управления приемного факсимильного аппарата, содержащее компаратор, формирователь импульса, блок для определения окончания передачи, пер0 вый элемент И, элемент ИЛИ, первый и второй счетчики, а также подключенные к выходам первого счетчика первый дешифратор, выход которого соединен с вторым входом первого элемен5 ч И, и второй дешифратор, первый, второй и третий выходы которого соединены соответственно с одноименными входами второго счетчика, четвертый вход которого подключен к первому

0 выходу блока для определения окончания передачи, первьй и второй выходы второго счетчика подключены соответственно к первому и второму входам делителя частоты, блок для фазирова5 ния и задающий генератор, первьй выход которого соединен с третьим входом делителя частоты, отличающееся тем, что, с целью расширения функциональных возможноетей путем обеспечения работы в режиме дистанционного управления приемным ф аксимильным аппаратом и повьшения Надежности, оно снабжено детектором, б|локом для -вьщеления частоты, вторым элементом И, модулятором и коммута- liopOM, выход которого является выхо- устройства, при этом основной ;ЕХОД устройства через последователь- ю соединенные детектор, компаратор, елок для вьщаления частоты и формирователь импульса подключен к входу Елока для определения окончания передачи, второй и третий выходы которого соединены соответственно с первым вхо ром первого элемента И, соединенного четвертым входом делителя частоты, первым входом второго элемента И, оединенного с пятым входом делителя астоты, шестой вход которого соеди- ;ен с выходом формирователя импульса, а первьй выход - с третьими входами первого и второго элементов И, вторые входы которых соединены, а выходы через элемент ИЛИ подключены к первому входу первого счетчика, к второму входу которого подключен первый выход блока для определения окончания передачи, второй выход делител частоты соединен с первыми входами коммутатора и блока для фазирования, второй вход которого соединен с третьим выходом второго счетчика, а выход подключен к второму входу коммутатора, к третьему входу которого подключен выход модулятора, первьй вход которого соединен с выходом детектора, второй выход задающего ге- нератора, вход которого является дополнительным входом устройства, соединен с вторым входом модулятора и четвертым входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1989 |

|

SU1736001A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Устройство для автоматического выбора скорости приемного факсимильного аппарата | 1981 |

|

SU995370A1 |

| Устройство для управления трехфазным транзисторным инвертором с квазисинусоидальным напряжением | 1984 |

|

SU1244772A1 |

| Устройство для измерения скорости звука | 1990 |

|

SU1728672A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| ИЗМЕРИТЕЛЬ СКОРОСТИ ЗВУКА | 1998 |

|

RU2152597C1 |

| Измеритель скорости звука | 1988 |

|

SU1583752A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

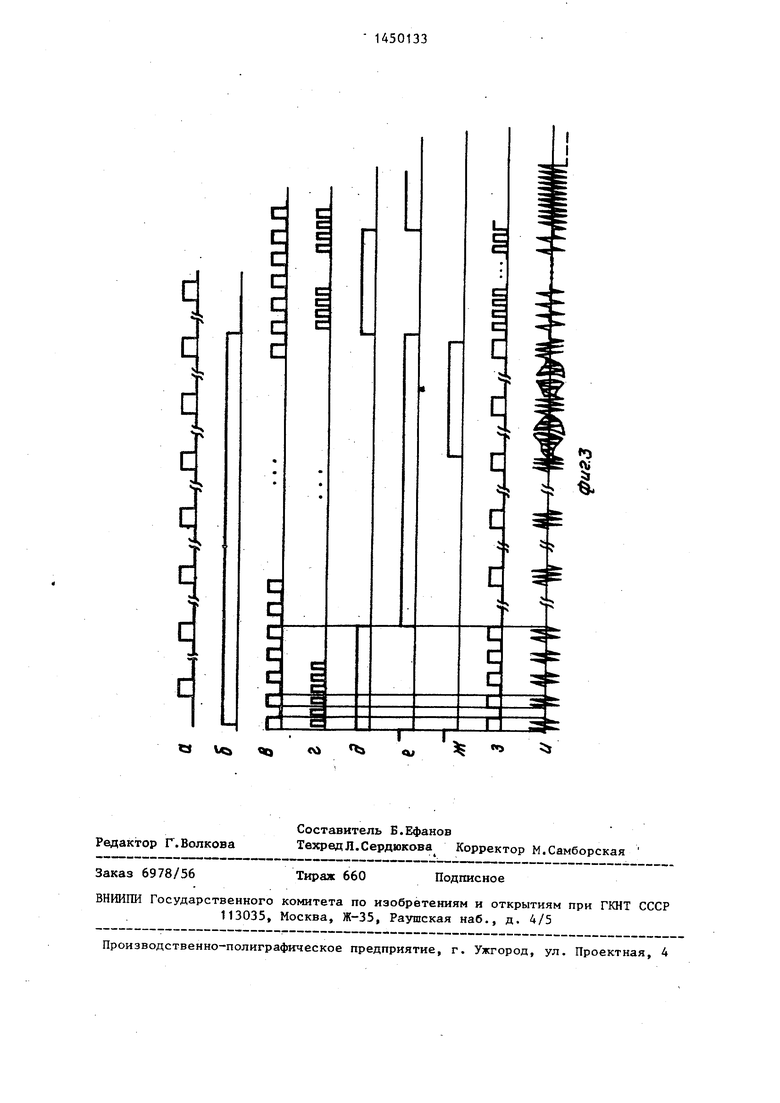

Изобретение относится к устройствам факсимильной связи и может быть использовано для приемопередачи полутонового изображения. Цель изобретения - расширение функциональных возможностей путем обеспечения работы в режиме дистанционного управления приемным факсимильным аппаратом и повышение надежности. Устройство для формирования сигналов управления приемного факсимильного аппарата содержит соединенные соответствующим образом детектор 1, компаратор 2, блок 3 для вьделения частоты, формирователь 4 импульса, блок 5 для определения окончания передачиj два элемента И 6 и 7, элемент ИЛИ 8, первый 9 и второй 12-счетчики, первый 10 и второй 11 дешифраторы, делитель 13 частоты, задающий генератор 14, блок 15 для фазирования, коммутатор 16 и модулятор 17. При этом обеспечиваются снижение влияния на работу устройства постороннего корреспондента и формирование на выходе устройства амплитудно-модулированного сигнала, который может быть передан, например, по стандартному каналу тональной частоты для управления одновременно группы приемных факсимильных аппаратов. 3 ил. 2 (Л

Л

-).

ЛП

е.

ЛЛЛЬ - пр.- -1ППГ -inf-

Составитель Б.Ефанов Редактор Г.Волкова ТехредЛ.Сердюкова Корректор М.Самборская

Заказ 6978/56

Тираж 660

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

.- г-гш- м1 ии-,и, - ц

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для автоматического выбора скорости приемного факсимильного аппарата | 1981 |

|

SU995370A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-01-07—Публикация

1985-07-26—Подача