(/}

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретных сигналов | 1987 |

|

SU1494024A1 |

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Устройство для адаптивного мажоритарного декодирования фазирующих сигналов | 1984 |

|

SU1213492A1 |

| Устройство для передачи и приема цифровой информации | 1987 |

|

SU1481832A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

Изобретение относится к телемеханике и может быть использовано ДЛР передачи цифровой информации по дль ным линиям связи.Цель изобретения - повышение достоверности принимаемой информации. Устройство содержит регистры 4, 7 сдвига, синхронизатор 5, формирователь Ь импульсов, дешифраторы 8, 9, 11, 19, делитель 10 частоты, мажоритарный элемент 12, RS-триггер 13, мультиплексоры 14-16, блоки 17, 22 памяти, счетчик 18, элемент И 20, элемент ИЛИ 21. Устройство позволяет получателю информации одновременно с выдачей информации сообщать о сбоя по каждому разряду выдаваемой информации. 8 ил.

ОЭ

I

фиг.1

Изобретение относится к телемеханике и может быть использовано для передачи цифровой информации по длинным линиям связи.

Цель изобретения - повышение досто1 верности принимаемой информации.

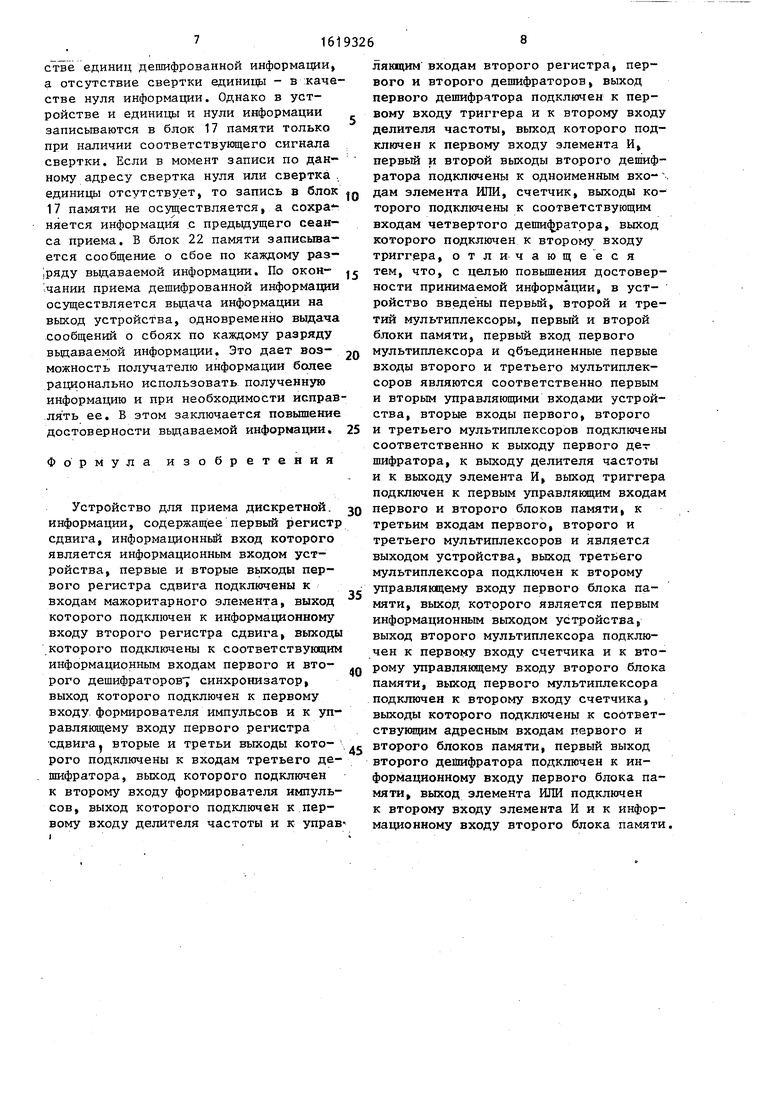

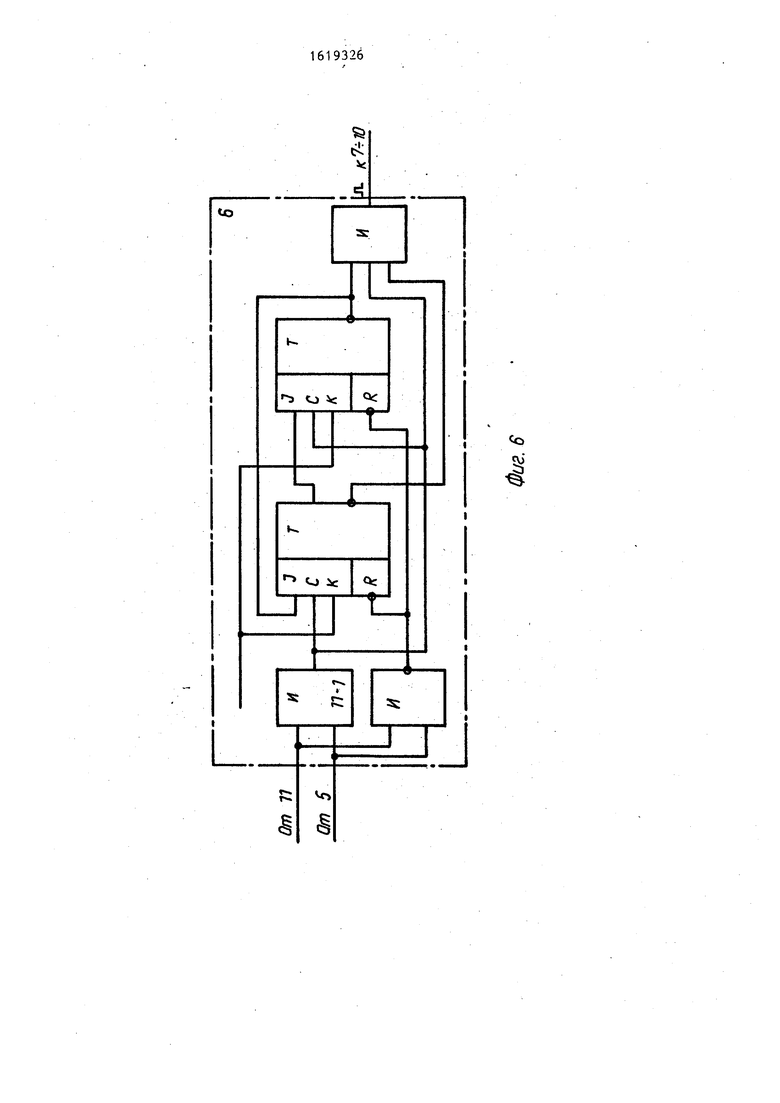

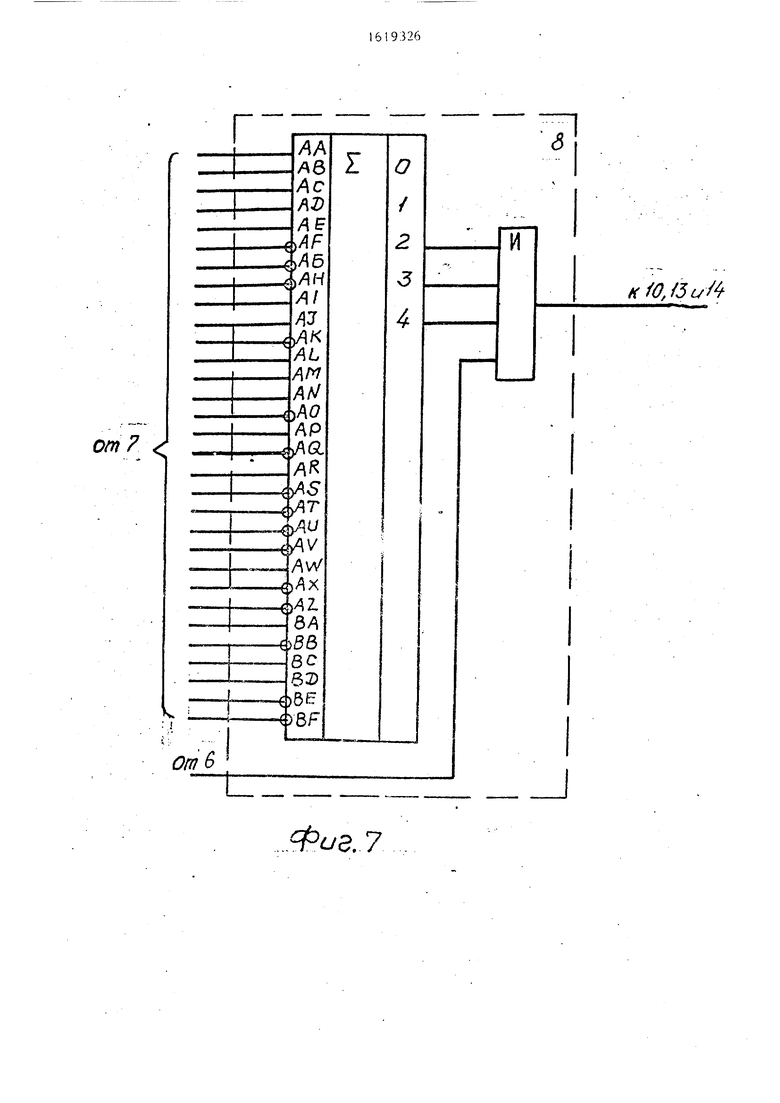

На фиг.1 изображена функциональная схема устройства; на фиг.2 - временная диаграмма работы устройства; на фиг.З - временная диаграмма формирования импульсов записи; на фиг.4 - схема реализации мажоритарного элемента в виде одноразрядного комбинационного сумматора трех чисел; на фиг.З - схема реализации третьего дешифратора в виде логического элемен та 2-2И-2ЩШ-НЕ; на фиг.6 - схема реализации формирователя -импульсов которьй состоит из двух двухвходовых элементов И и делителя частоты импульсов на три, выполненного на двух 1,К-триггерах и одном трехвходовом элементе И; на фиг.7 - схема реализации первого дешифратора, дешифратора кода начала передачи, которая выполнена на одноразрядном комбинационном сумматоре на столько чисел, сколько разрядов содержит код начала передачи, кроме того, второй дешифратор содержит элемент И, которьй на основании анализа состояния двоичного кода на выходах сумматора формирует сигнал свертки кода начала передачи; на фиг.8 - схема реализации второго дешифратора (дешифратора кода) Баркера, которая выполнена на одноразрядном комбинационном сумматоре на семь чисел и двух трехвходовых элементах И.

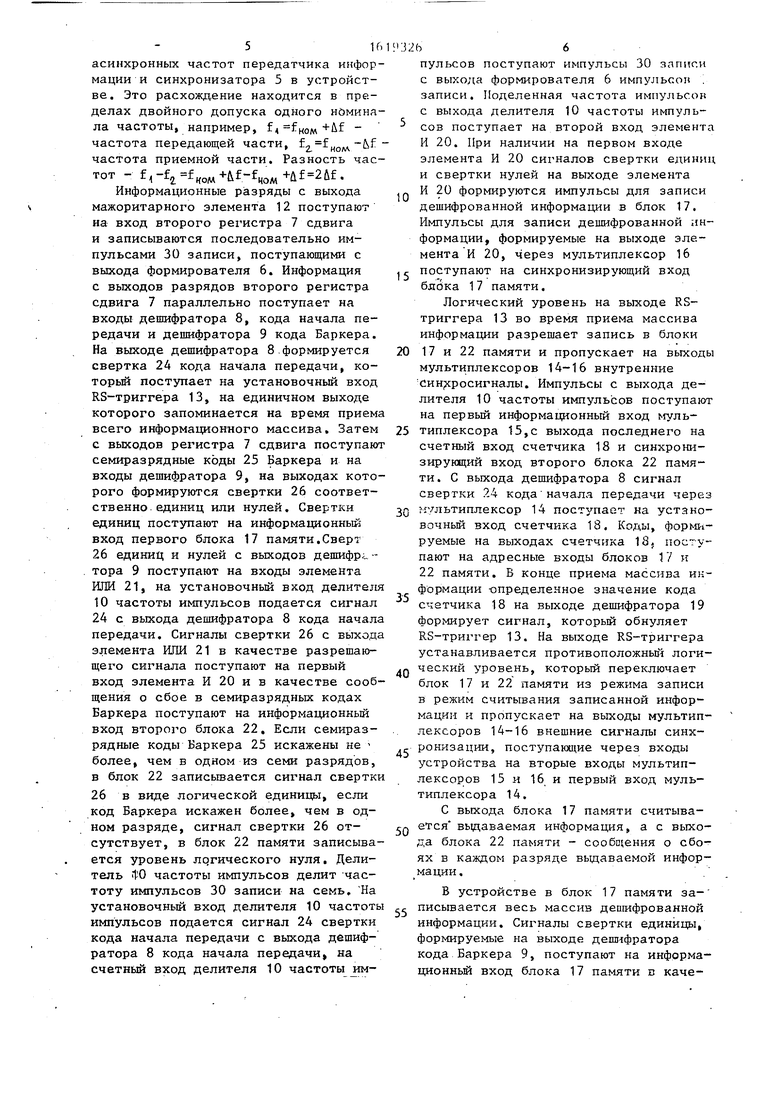

Устройство содержит (фиг.1) вход 1 первый 2 и второй 3 выходы, первый регистр 4 сдвига, синхронизатор 5, формирователь 6 импульсов, второй регистр 7 сдвига, первый дешифратор 8, второй дешифратор 9, делитель 10 частоты (импульсов), третий дешифратор 11, мажоритарный элемент 12, RS- триггер 13, первый мультиплексор 14, второй мультиплексор 15, третий мультиплексор 16, первый блок 17 памяти, счетчик 18, четвертый дешифратор 19, элемент И 20, элемент ИЛИ 21, второй блок 22 памяти. На фиг.2 представлены код 23 начала передачи, свертка 24 кода начала передачи, семиразрядные коды 25 Баркера, свертки 26 семиразрядных кодов Бпркера; на фиг.З представлены: трехкратная частота импульсов 27, разряды информации 28 в линии

10

5

0

5

30

35

40

45

50

55

связи, разряды 29 информации, запй- санные в первьй регистр 4 сдвига, импульсы 30 записи на выходе формирователя 6 импульсов записи.

Устройство работает следующим образом.

На вход 1 поступает массив информации в виде последовательных кодов: кода 23 начала передачи и семиразрядных кодов 25 Баркера, которыми зашифрован каждый разряд информации. Единицы информации зашифрованы в прямые коды Баркера 1110010, нули - в инверсии кодов Баркера - 0001101. Информация 28 поступает на вход 1, затем последовательно записывается в первый регистр 4 сдвига n-кратной частотой импульсов, где - целое нечетное число, поступающие с выхода синхронизатора 5.

Временная диаграмма формирования импульсов записи на фиг.З изображена при .

Записанная информация 30 с четырех выходов старших разрядов шестиразрядного регистра 4 сдвига поступает на входы дешифратора 11. В момент, когда на выходах первых двух старших разрядов регистра 4 оказывается один логический уровень напряжения, а на выходах двух последующих разрядов - второй логический уровень, на его выходе формируется сигнал, который синхронизирует формирователь 6 импульсов записи так, что импульсы 30 записи формируются в средней зоне разряда информации, занимающей одну треть длительности разряда.

В устройстве осуществляется интегральный прием информации, для этого используется мажоритарный элемент 12 два из трех, который анализирует уровень напряжения каждого разряда информации в трех зонах длительности, если не менее, чем в двух зонах из трех разряд имеет один и тот же логический уровень, соответствующий уровень формируется на выходе мажоритарного элемента 12, т.е. мажоритарный элемент 12 исправляет искаженный информационный разряд, если он искажен по уровню в любой зоне разряда информации, но не более, чем на одной трети длительности информационного разряда. Искажение информационного разряда происходит как в лигкш связи, в результате помех, так и при записи в регистр 4 сдвига из-за рirхождения

51 f 1

асинхронных частот передатчика информации и синхронизатора 5 в устройстве. Это расхождение находится в пределах двойного допуска одного номинала частоты, например, f 4 fKOM+uf - частота передающей части, НОЛЛ -&f частота приемной части. Разность час- тот - f -f2 fHoM+&f-f40A,.

Информационные разряды с выхода мажоритарного элемента 12 поступают на вход второго регистра 7 сдвига и записываются последовательно импульсами 30 записи, поступающими с выхода формирователя 6. Информация с выходов разрядов второго регистра сдвига 7 параллельно поступает на входы дешифратора 8, кода начала передачи и дешифратора 9 кода Баркера. На выходе дешифратора 8 формируется свертка 24 кода начала передачи, который поступает на установочный вход RS-триггера 13, на единичном выходе которого запоминается на время приема всего информационного массива. Затем с выходов регистра 7 сдвига поступают семиразрядные коды 25 Баркера и на входы дешифратора 9, на выходах которого формируются свертки 26 соответственно- единиц или нулей. Свертки единиц поступают на информационный вход первого блока 17 памяти.Сверт 26 единиц и нулей с выходов дешифр;. - тора 9 поступают на входы элемента ИЛИ 21, на установочный вход делителя 10 частоты импульсов подается сигнал 24 с выхода дешифратора 8 кода начала передачи. Сигналы свертки 26 с выхода элемента ИЛИ 21 в качестве разрешающего сигнала поступают на первый вход элемента И 20 и в качестве сообщения о сбое в семиразрядных кодах Баркера поступают на информационный вход второго блока 22. Если семиразрядные коды Баркера 25 искажены не более, чем в одном из семи разрядов, в блок 22 записывается сигнал свертки 26 в виде логической единицы, если код Баркера искажен более, чем в одном разряде, сигнал свертки 26 отсутствует, в блок 22 памяти записывается уровень логического нуля. Делитель № частоты импульсов делит частоту импульсов 30 записи на семь. На установочный вход делителя 10 частоты импульсов подается сигнал 24 свертки кода начала передачи с выхода дешифратора 8 кода начала передачи, на счетный вход делителя 10 частоты им0

:3266

пульсов поступают импульсы 30 записи с выхода формирователя 6 импульсон . записи. Поделенная частота импульсов с выхода делителя 10 частоты импуль сов поступает на второй вход элемента И 20. При наличии на первом входе элемента И 20 сигналов свертки единиц и свертки нулей на выходе элемента И 20 формируются импульсы для записи дешифрованной информации в блок 17. Импульсы для записи дешифрованной информации, формируемые на выходе элемента И 20, через мультиплексор 16

5 поступают на синхронизирующий вход блока 17 памяти.

Логический уровень на выходе RS- триггера 13 во время приема массива информации разрешает запись в блоки

0 17 и 22 памяти и пропускает на выходы мультиплексоров 14-16 внутренние Синхросигналы. Импульсы с выхода делителя 10 частоты импульсов поступают на первый информационный вход муль5 типлексора 15,с выхода последнего на счетный вход счетчика 18 и синхронизирующий вход второго блока 22 памяти. С выхода дешифратора 8 сигнал свертки 24 кода начала передачи через

Q н /льтиплексор 14 поступает на установочный вход счетчика 18. Коды, формируемые на выходах счетчика 18{ поступают на адресные входы блоков 17 и 22 памяти. Б конце приема массива информации -определенное значение кода счетчика 18 на выходе дешифратора 19 формирует сигнал, который обнуляет RS-триггер 13. На выходе RS-триггера устанавливается противоположный логиQ ческий уровень, который переключает блок 17 и 22 памяти из режима записи в режим считывания записанной информации и пропускает на выходы мультиплексоров 14-16 внешние сигналы синх5 ронизации, поступающие через входы устройства на вторые входы мультиплексоров 15 и 16 и первый вход мультиплексора 14.

С выхода блока 17 памяти считываQ ется выдаваемая информация, а с выхода блока 22 памяти - сообщения о сбоях в каждом разряде выдаваемой информации.

В устройстве в блок 17 памяти за- е писывается весь массив дешифрованной информации. Сигналы свертки единицы, формируемые на выходе дешифратора кода Баркера 9, поступают на информационный вход блока 17 памяти в каче5

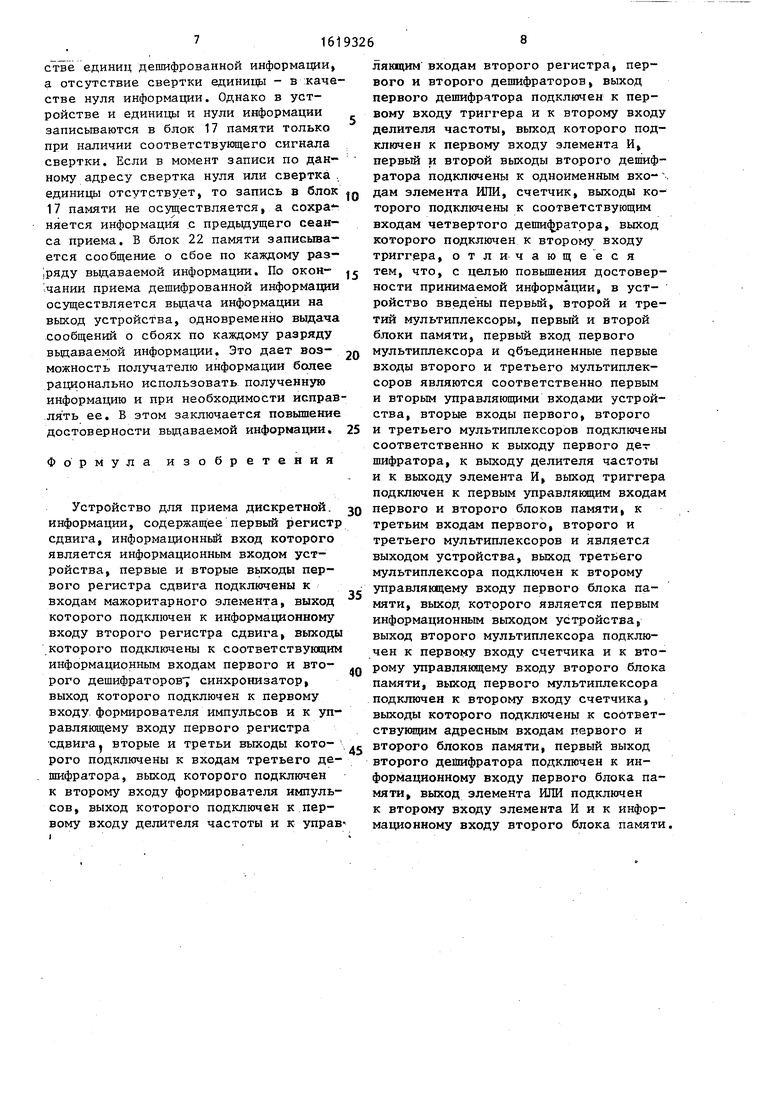

стве единиц дешифрованной информации, а отсутствие свертки единицы - в качестве нуля информации. Однако в устройстве и единицы и нули информации записываются в блок 17 памяти только при наличии соответствующего сигнала свертки. Если в момент записи по данному адресу свертка нуля или свертка единицы отсутствует, то запись в блок 17 памяти не осуществляется, а созсра х

няется информация с предыдущего сеанса приема. В блок 22 памяти записывается сообщение о сбое по каждому раз- ,ряду выдаваемой информации. По окон- чании приема дешифрованной информации осуществляется выдача информации на выход устройства, одновременно выдача сообщений о сбоях по каждому разряду выдаваемой информации. Это дает воз- можность получателю информации более рационально использовать полученную информацию и при необходимости исправлять ее. В этом заключается повышение достоверности выдаваемой информации.

Формула изобретения

Устройство для приема дискретной информации, содержащее первый регистр сднига, информационный вход которого является информационным входом устройства, первые и вторые выходы первого регистра сдвига подключены к входам мажоритарного элемента, выход которого подключен к информационному входу второго регистра сдвига, выходы которого подключены к соответствующим информационным входам первого и второго дешифраторов синхронизатор, выход которого подключен к первому входу формирователя импульсов и к управляющему входу первого регистра

сдвига, вторые и третьи выходы кото-

рого подключены к входам третьего дешифратора, выход которого подключен к второму входу формирователя импульсов, выход которого подключен к первому входу делителя частоты и к управ

5

Q

, 5

5

0

ляющим входам второго регистра, первого и второго дешифраторов, выход первого дешифратора подключен к первому входу триггера и к второму входу делителя частоты, выход которого подключен к первому входу элемента И, первый и второй выходы второго дешифратора подключены к одноименным входам элемента ИЛИ, счетчик, выходы которого подключены к соответствующим входам четвертого дешифратора, выход которого подключен к второму входу триггера, отличающееся тем, что, с целью повышения достоверности принимаемой информации, в устройство введены первый, второй и третий мультиплексоры, первый и второй блоки памяти, первый вход первого мультиплексора и объединенные первые входы второго и третьего мультиплексоров являются соответственно первым и вторым управляющими входами устройства, вторые входы первого, второго и третьего мультиплексоров подключены соответственно к выходу первого дет шифратора, к выходу делителя частоты и к выходу элемента И, выход триггера подключен к первым управляющим входам первого и второго блоков памяти, к третьим входам первого, второго и третьего мультиплексоров и является выходом устройства, выход третьего мультиплексора подключен к второму управляющему входу первого блока памяти, выход которого является первым информационным выходом устройства, выход второго мультиплексора подключен к первому входу счетчика и к второму управляющему входу второго блока памяти, выход первого мультиплексора подключен к второму входу счетчика, выходы которого подключены к соответствующим адресным входам первого и второго блоков памяти, первый выход второго дешифратора подключен к информационному входу первого блока памяти, выход элемента ИЛИ подключен к второму входу элемента И и к информационному входу второго блока памяти.

41

Li

Фм.2

Фиг. З

ФигЛ

1л

1л

inWi

Ъ о ie

-I

К

L.

и Ј

rL

0

4

U

s jwo

9Zt6l9l

от 4

Фиг. 8

| Устройство для передачи и приема дискретных сигналов | 1987 |

|

SU1494024A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-01-07—Публикация

1989-01-05—Подача