Изобретение относится к вычислительной технике и предназначено для построения программируемых контроллеров (ПК).

В ПК программа работы управляемого объекта задается в виде инструкций, представляющих последовательность, воспроизводящую ступенчатую электрическую схему управляемого объекта; В основном ступенчатая электрическая схема строится из элементов ВХОД, ВЫХОД, ВЕТВЬ (НАЧАЛО ВЕТВИ, КОНЕЦ ВЕТВЕЙ), которые образуют определенные конструкции. К элементам ВХОД относятся нормально разомкнутые или нормально замкнутые контакты, соответствующие датчику, кнопке, переключателю, к элементам ВЫХОД - обмотка реле, лампочка индикации и т.п., элементы ВЕТВЬ позволяют образовывать дизъюнкции элементов ВХОД

и их групп в ступенчатой электрической схеме.

Цель изобретения - повышение быстродействия за счет реализации одновременной обработки различных типов инструкций.

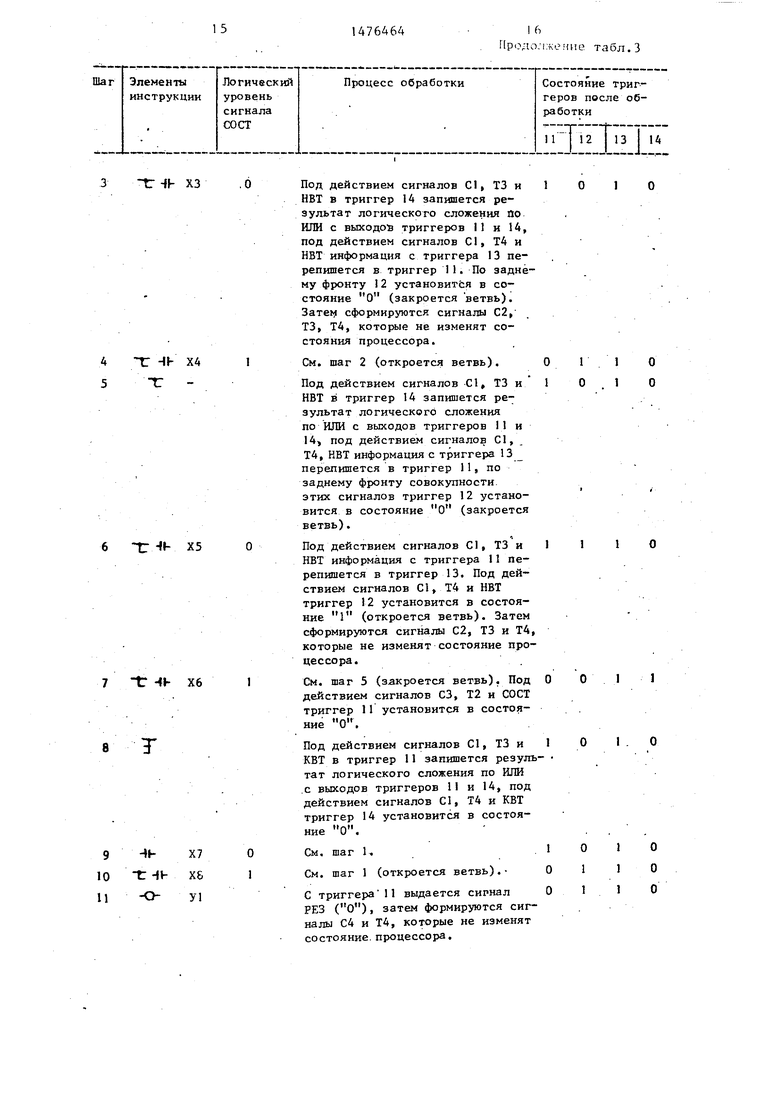

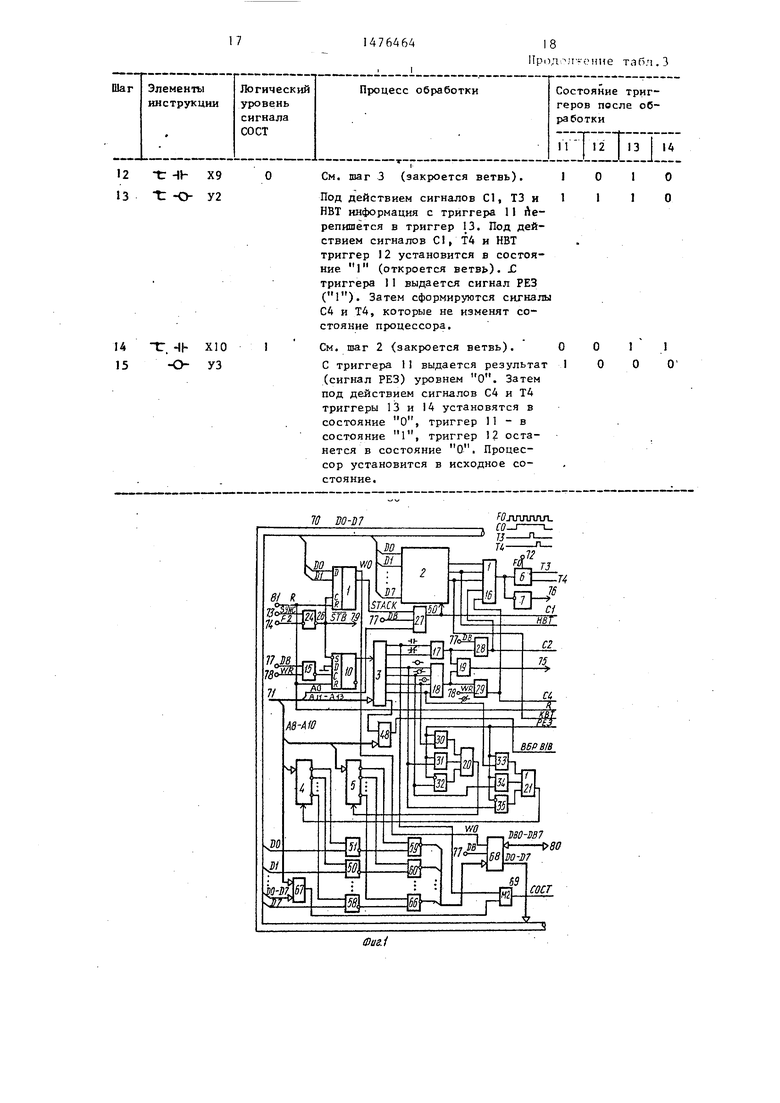

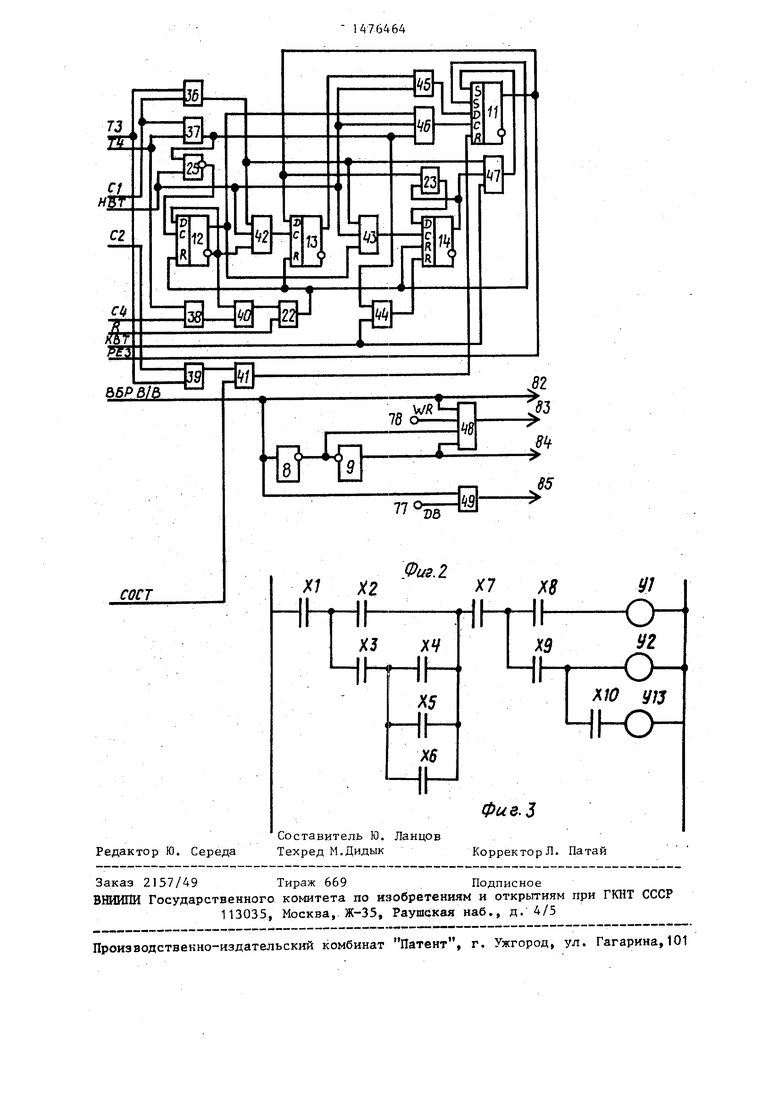

На фиг. 1 и 2 представлена функциональная схема предлагаемого процессора; на фиг. 3 - ступенчатая электрическая схема, которую может обрабатывать данный процессор.

Процессор содержит регистр 1, шифратор 2, дешифратор 3-5, формирователь 6 импульсов, одновибраторы 7-9, триггеры 10-14, элемент ИЛИ-НЕ 15, элементы ИЛИ 16-23, элементы И-НЕ 24 и 25, выход 26 элемента И-НЕ 24, элементы И 27-49, выход 50 элемента И 27, две группы элементов И-НЕ 51-58 и 59-66, мультиплексор 67, узел 68 двунаправленной передачи

Ј 1

О 4 О5 4ь

данных, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 69, шину 70 данных (DO-D7), вход 71 кода команды (АО, А8-А13), второй синхро- вход 72 (FO), вход 73 признака начала обработки (SYNC), первый синхро вход 74 (F2), выход 75 управления модификацией адреса, выход 76 признака окончания обработки инструкций, вход 77 признака режима ввода (DB), вход 78 признака режима вывода (WR), выход 79 признака начала обработки, информационный вход-выход 80, вход 81 сброса, выход 82 признака обращения с каналом ввода-вывода, выход 83 сопровождения вывода, выход 84 готовности и выход 85 сопровождения ввода.

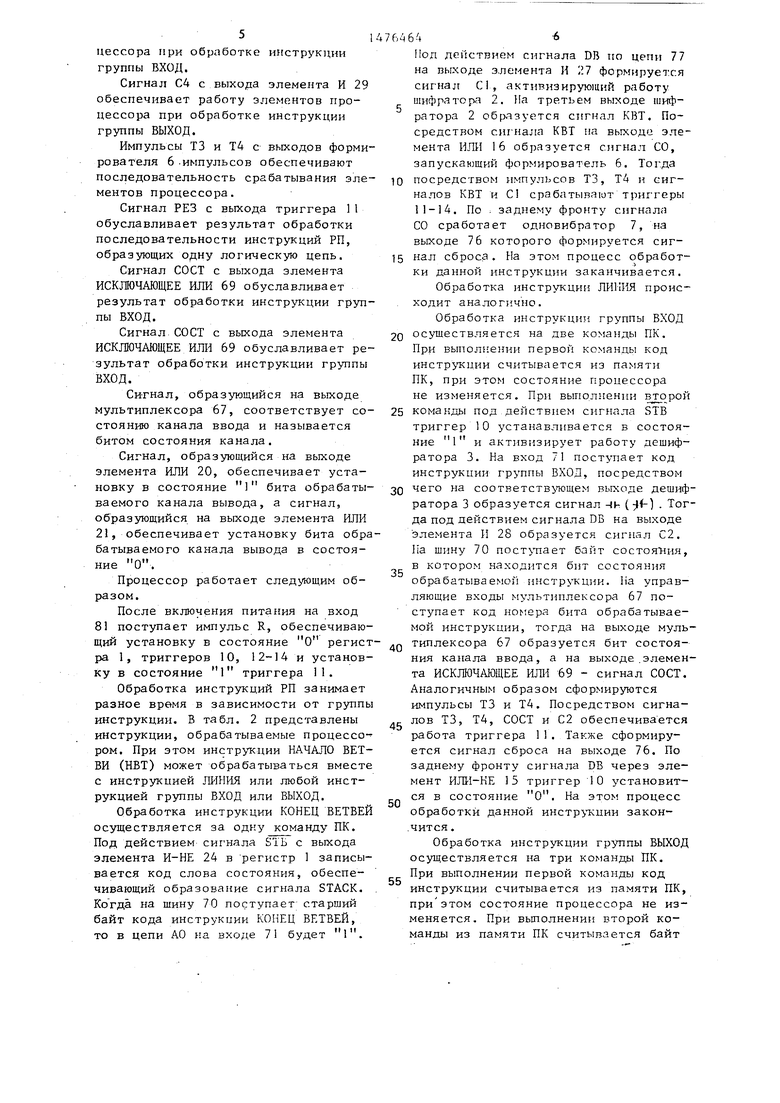

Регистр 1 представляет собой микросхему типа К155ТМ8. Формирователь 6 импульсов состоит из пересчетной схемы (счетчика) и элементов И, что обеспечивает выделение, например, третьего и четвертого импульсов из последовательности импульсов FO под действием запускающего сигнала СО (см. временные диаграммы работы формирователя, изображенные над ним). Узел 68 двунаправленной передачи данных представляет собой переключатель шин с тремя состояниями на выходах и может быть выполнен на двух микросхемах типа К589АП16. Мультиплексор 67 обеспечивает выборку одного бита из байта, передаваемого по шине 70 DO-D7, по адресу, указанному кодом в шине А8-А10. Одновибра- торы 8 и 9 обеспечивают формирование импульсов длительностью примерно 6 и 8 мкс соответственно. Шифратор 2 может быть выполнен на микросхеме типа К556РТ4. В табл. 1 приведен пример кодирования шифратора 2, позволяющий реализовать одновременную обработку инструкции НАЧАЛО ВЕТВИ и ВХОД или ВЫХОД.

Входы и выходы элементов процессора имеют следующее назначение. Сигнал FO на входе 72 обеспечивает образование на выходе формирователя 6 двух импульсов ТЗ и Т4 длительностью по 100 не.

Синхроимпульс F2 на входе 74 и сигнал SYNC (сигнал начала цикла об работки) на входе 73 обеспечивают образование на выходе элемента И-КЕ 24 импульса STB, необходимого для

-

10

15

20

25

30

35

40

45

50

55

стробирования работы элементов процессора .

Сигнал на входе 77 формируется при появлении информации в шине 70 DO-D7 в цикле считывания.

Сигнал WR на вход 78 поступает при появлении информации в шине 70 в цикле записи.

Сигнал R на вход 81 поступает при включении питания ПК и обеспечивает установку элементов процессора в исходное состояние.

Сигнал сброса на выходе 76 образуется по завершении обработки инструкции группы ВХОД, ВЫХОД или инструкции КОНЕЦ ВЕТВЕЙ, линия.

Сигнал управления модификацией адреса на выходе 75 образуется, когда на входе 71 устанавливается код команды, соответствующий обрабатываемой инструкции группы ВХОД или ВЫХОД.

Сигнал ГТ на выходе 84 готовности образуется при передаче информации с шины 70 DO-D7 на вход-выход 80 DBO-DB7 и при передаче информации с входа-выхода 80 на шину 70 в цикле обмена информацией ПК с каналами ввода-вывода.

Сигнал ВБР В/В на выходе 82 формируется при обращении ПК к каналам ввода-вывода и активизирует их работу.

Сигнал вывод на выходе 83 формиру- ется при выдаче информации с ПК в каналы вывода и обеспечивает запись информации, например, в регистры модулей вывода.

Сигнал Ввод на выходе 85 формируется при приеме информации с каналов ввода и обеспечивает синхронизацию их ра бо ты.

Сигнал WO с соответствующего разряда выхода регистра 1 активизирует работу узла 68 по передаче информации с его информационных входов на вход-выход 80.

Сигнал STACK с соответствующего разряда выхода регистра 1 обеспечивает формирование управляющего сигнала в шифратор 2 в цикле поступления кода инструкции РП в шину 70.

Сигнал С1 с выхода элемента И 27 обеспечивает работу элементов процессора при обработке инструкции группы ВЕТВЬ.

Сигнал С2 с выхода элемента И 28 обеспечивает работу элементов процессора при обработке инструкции группы ВХОД.

Сигнал С4 с выхода элемента И 29 обеспечивает работу элементов процессора при обработке инструкции группы ВЫХОД.

Импульсы ТЗ и Т4 с выходов формирователя 6 импульсов обеспечивают последовательность срабатывания элементов процессора.

Сигнал РЕЗ с выхода триггера 11 обуславливает результат обработки последовательности инструкций РП, образующих одну логическую цепь.

Сигнал СОСТ с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 69 обуславливает результат обработки инструкции группы ВХОД.

Сигнал СОСТ с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 69 обуславливает результат обработки инструкции группы ВХОД.

Сигнал, образующийся на выходе мультиплексора 67, соответствует состоянию канала ввода и называется битом состояния канала.

Сигнал, образующийся на выходе элемента ИЛИ 20, обеспечивает установку в состояние 1 бита обрабатываемого канала вывода, а сигнал, образующийся на выходе элемента ИЛИ 21, обеспечивает установку бита обрабатываемого канала вывода в состояние О.

Процессор работает следующим образом.

После включения питания на вход 81 поступает импульс R, обеспечивающий установку в состояние 0м регистра 1, триггеров 10, 12-14 и установку в состояние 1 триггера 11.

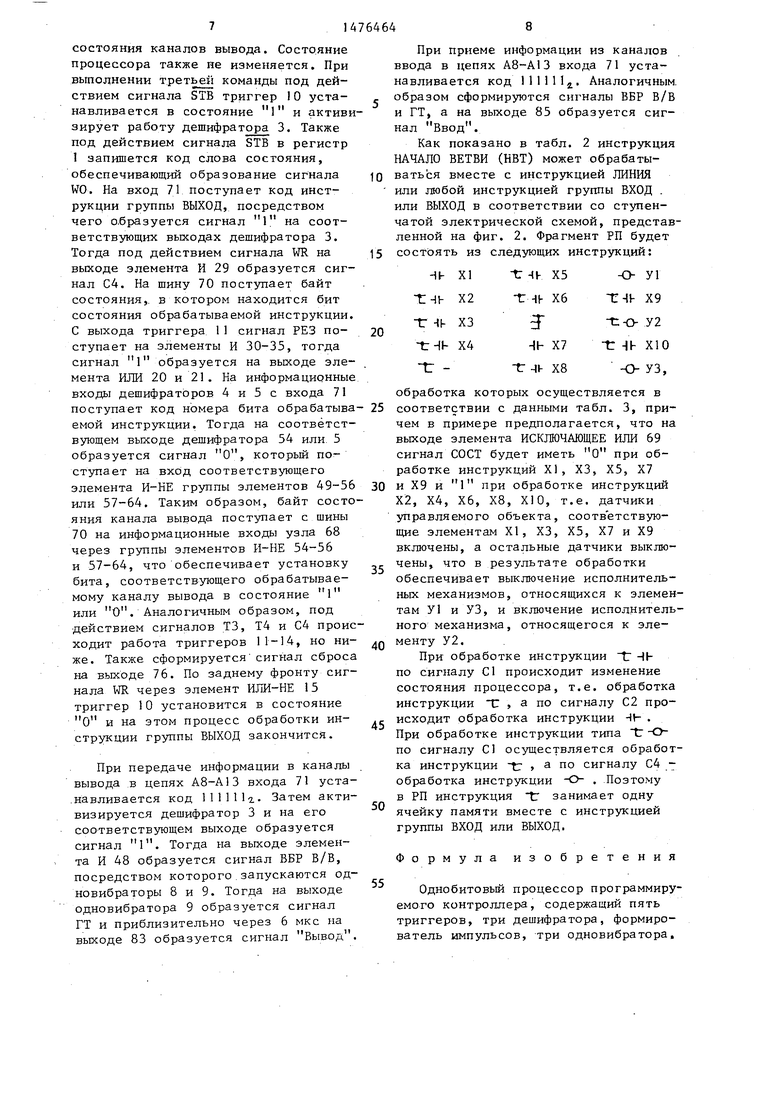

Обработка инструкций РП занимает разное время в зависимости от группы инструкции. В табл. 2 представлены инструкции, обрабатываемые процессором. При этом инструкции НАЧАЛО ВЕТВИ (НЕТ) может обрабатываться вместе с инструкцией ЛИНИЯ или любой инструкцией группы ВХОД или ВЫХОД.

Обработка инструкции КОНЕЦ ВЕТВЕЙ осуществляется за одну команду ПК. Под действием сигнала Sib с выхода элемента И-НЕ 24 в регистр 1 записывается код слова состояния, обеспечивающий образование сигнала STACK. Когда на шину 70 поступает старший байт кода инструкции КОНЕЦ ВЕТВЕЙ, то в цепи АО на входе 71 будет 1.

476ч 6(-6

Под действием сигнала DB по цепи 77 на выходе элемента И 27 формируется сигнал С1, активизирующий работу шифратора 2. На третьем выходе шифратора 2 образуется сигнал КВТ. Посредством сигнала КВТ на выходе элемента ИЛИ 16 образуется сигнал СО, запускающий формирователь 6. Тогда

Ю посредством импульсов ТЗ, Т4 и сигналов КВТ и С1 срабатывают триггеры 11-14. По заднему фронту сигнала СО сработает одновибратор 7, на выходе 76 которого формируется сиг15 нал сброса. На этом процесс обработки данной инструкции заканчивается.

Обработка инструкции ЛИНИЯ происходит аналогично.

Обработка инструкции группы ВХОД

2о осуществляется на две команды ПК. При выполнении первой команды код инструкции считывается из памяти ПК, при этом состояние процессора не изменяется. При выполнении второй

25 команды под действием сигнала STB триггер 10 устанавливается в состоя0

5

0

5

0

5

ние 1 и активизирует работу дешифратора 3. На вход 71 поступает код инструкции группы ВХОД, посредством чего на соответствующем выходе дешифратора 3 образуется сигнал нн ()t-} Тогда под действием сигнала DB на выходе элемента И 28 образуется сигнал С2. На шину 70 поступает байт состояния, в котором находится бит состояния обрабатываемой инструкции, ha управляющие входы мультиплексора 67 поступает код номера бита обрабатываемой инструкции, тогда на выходе мультиплексора 67 образуется бит состояния канала ввода, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 69 - сигнал СОСТ. Аналогичным образом сформируются импульсы ТЗ и Т4. Посредством сигналов ТЗ, Т4, СОСТ и С2 обеспечивается работа триггера 11. Также сформируется сигнал сброса на выходе 76. По заднему фронту сигнала DB через элемент ИЛИ-НЕ 15 триггер 10 установится в состояние О. На этом процесс обработки данной инструкции закончится .

Обработка инструкции группы ВЫХОД осуществляется на три команды ПК. При выполнении первой команды код инструкции считывается из памяти ПК, при этом состояние процессора не изменяется. При выполнении второй команды из памяти ПК считывается байт

состояния каналов вывода. Состояние процессора также не изменяется. При выполнении третьей команды под действием сигнала STB триггер 10 устанавливается в состояние 1 и активизирует работу дешифратора 3. Также под действием сигнала STB в регистр 1 запишется код слова состояния, обеспечивающий образование сигнала WO. На вход 71 поступает код инструкции группы ВЫХОД, посредством чего образуется сигнал 1 на соответствующих выходах дешифратора 3. Тогда под действием сигнала WR на выходе элемента И 29 образуется сигнал С4. На шину 70 поступает байт состояния, в котором находится бит состояния обрабатываемой инструкции. С выхода триггера 11 сигнал РЕЗ поступает на элементы И 30-35, тогда сигнал 1 образуется на выходе элемента ИЛИ 20 и 21. На информационные входы дешифраторов 4 и 5 с входа 71 поступает код номера бита обрабатыва емой инструкции. Тогда на соответствующем выходе дешифратора 54 или 5 образуется сигнал О, который поступает на вход соответствующего элемента И-НЕ группы элементов 49-56 или 57-64. Таким образом, байт состояния канала вывода поступает с шины 70 на информационные входы узла 68 через группы элементов И-НЕ 54-56 и 57-64, что обеспечивает установку бита, соответствующего обрабатываемому каналу вывода в состояние 1 или 0м. Аналогичным образом, под действием сигналов ТЗ, Т4 и С4 происходит работа триггеров 11-14, но ниже. Также сформируется сигнал сброса на выходе 76. По заднему фронту сигнала WR через элемент ИЛИ-НЕ 15 триггер 10 установится в состояние О и на этом процесс обработки инструкции группы ВЫХОД закончится.

При передаче информации в каналы вывода в цепях А8-А13 входа 71 устанавливается код 111 Ills.. Затем активизируется дешифратор 3 и на его соответствующем выходе образуется сигнал 1. Тогда на выходе элемента И 48 образуется сигнал ВБР В/В, посредством которого запускаются одно вибраторы 8 и 9. Тогда на выходе одновибратора 9 образуется сигнал ГТ и приблизительно через 6 мкс на выходе 83 образуется сигнал Вывод.

0

При приеме информации из каналов ввода в цепях А8-А13 входа 71 устанавливается код П1П1а. Аналогичным образом сформируются сигналы ВБР В/В и ГТ, а на выходе 85 образуется сигнал Ввод.

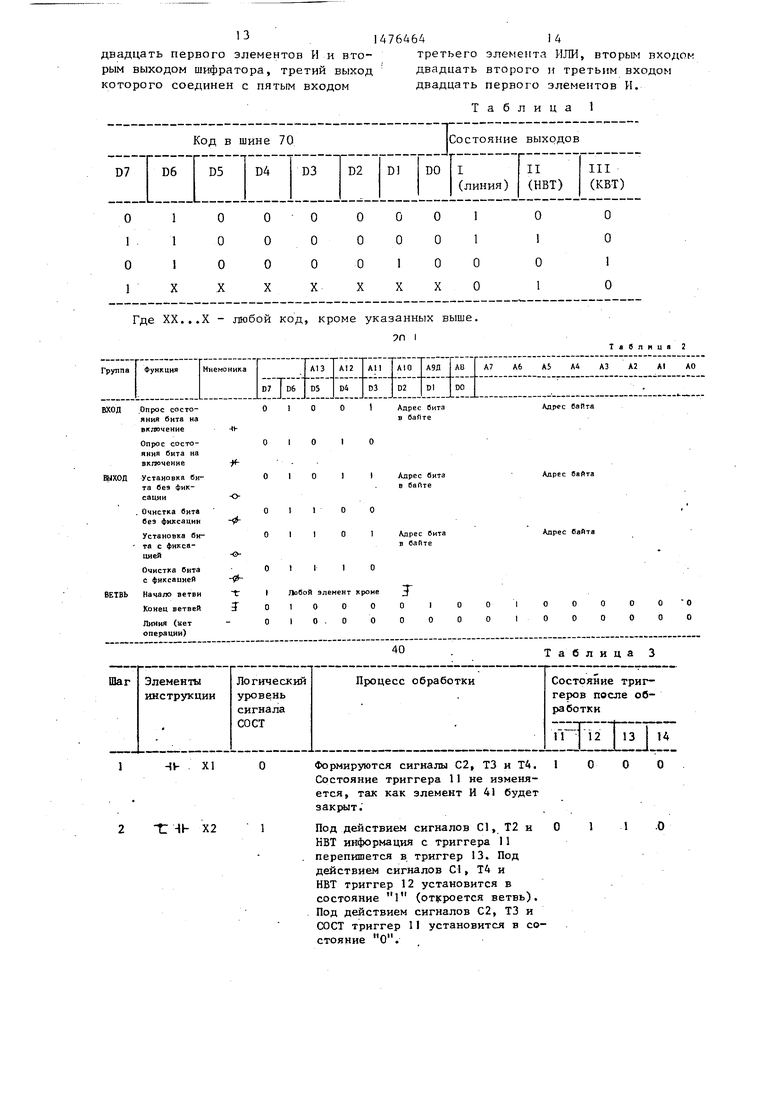

Как показано в табл. 2 инструкция НАЧАЛО ВЕТВИ (НВТ) может обрабатываться вместе с инструкцией ЛИНИЯ или любой инструкцией группы ВХОД или ВЫХОД в соответствии со ступенчатой электрической схемой, представленной на фиг. 2. Фрагмент РП будет состоять из следующих инструкций:

Hh XI

t 41- Х5

-О У1

25

30

35

40

45

50

55

обработка которых осуществляется в соответствии с данными табл. 3, причем в примере предполагается, что на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 69 сигнал СОСТ будет иметь О при обработке инструкций XI, ХЗ, Х5, Х7 и Х9 и 1 при обработке инструкций Х2, Х4, Х6, Х8, Х10, т.е. датчики управляемого объекта, соотв етствую- щие элементам XI, ХЗ, Х5, Х7 и Х9 включены, а остальные датчики выключены, что в результате обработки обеспечивает выключение исполнительных механизмов, относящихся к элементам У1 и УЗ, и включение исполнительного механизма, относящегося к элементу У2.

При обработке инструкции f -lino сигналу С1 происходит изменение состояния процессора, т.е. обработка инструкции С , а по сигналу С2 происходит обработка инструкции -11- . При обработке инструкции типа tr -О- по сигналу С) осуществляется обработка инструкции tr , а по сигналу С4 - обработка инструкции -О- . Поэтому в РП инструкция t занимает одну ячейку памяти вместе с инструкцией группы ВХОД или ВЫХОД.

Формула изобретения

Однобитовый процессор программируемого контроллера, содержащий пять триггеров, три дешифратора, формирователь импульсов, три одновибратора.

13 1

мультиплексор, узел двунаправленной передачи данных, элемент ИСКЛЮЧАЮЩЕЕ ИПИ, дна элемента И-НЕ, элемент ИЛИ-НЕ, лосемъ элементов ИПИ, регистр, две группы элементов И-НЕ и двадцать три элемента И, причем информационный выход узла двунаправленной передачи данных поразрядно подключен к информационному входу мультиплексора и первым входам элементов И-НЕ первой группы, кроме того, первый и второй разряды информационного выхода узла двунаправленной передачи данных подключены соответственно к первому и второму разрядам информационного входа регистра первый и второй разряды выхода которого подключены соответственно к первому управляющему входу узла двунаправленной передачи данных и первому входу первого элемента И, второй вход которого подключен к первому разряду входа кода команды процессора, с второго по четвертый разряды входа кода команды процессора соединены соответственно с первого по третий информационными входами первого и второго дешифраторов, соответственно с первого по третий входами второго элемента И и соответственно с первого по третий управляющими входами мультиплексора, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с первым выходом третьего дешифратора и первым входо. первого элемента ИЛИ, второй вхо, которого соединен с вторым выходом третьего дешифратора, первый вход которого соединен с выходом первого триггера, вход установки в 1 которого соединен с входом синхронизации регистра, выходом первого элемента И-НЕ и подключен к выходу признака начала обработки процессора вход сброса которого подключен к входам установки в О регистра, первог триггера и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен г. выходом пятого элемента И и первым входом третьего элемента ИЛИ, второй вход которого соединен с первым входом шестого элемента И и выходом седьмого элемента И, первый вход которого

0

5

0

5

0

5

0

5

0

5

ЬЧ

по, к p.iopo- Y ynp i нл югц му входу узла двунапраплотной передачи данных, перв /м входам элемент. ИЛИ-НЕ и ног-ъмо:е элемента И, к тро тьему входу перрого элемента И к входу признака режима ниода процессора, вход признака релнмл вывода процессора подключен к второму входу элемента ИЛИ-НЕ и первым входам девятого и пятого элементов И, выход элемента ИЛИ-НЕ соединен с входом синхронизации первого триггера, информационный вход которого подключен к шине нулевого потенциала, с пятого по седьмой разряды входа кода команды процессора подключены к входам соответственно с второго по четвертый третьего дешифратора, выходы первого дешифратора соединены с вторыми входами элементов П-1 .F первой группы, выходы которых соединены с первыми входами элементов И-НЕ второй группы, вторые входы и выходы которых соединены соответственно с выходами второго дешифратора и информационными входами узла двунаправленной передачи данных, информационный вход-выход которого подключен к информационному входу-выходу процессора, третий выход третьего дешифратора соединен с первыми входами четвертого элемента ИЛИ и десятого элемента И, а также с прямым входом одиннадцатого элемента И, инверсный вход которого соединен с первь ми входами с двенадцатого по четырнадцатый элементов И, вторым входам десятого элемента И, выходом второго триггера, инверсным входом пятнадцатого °лемен- та И, прямой вход которого соединен с вторым входом двенадцатого элемента И, вторым входом четвертого элемента ИЛИ и четвертым выходом третьего дешифратора, пятый выход которого соединен с третьим входом четвертого элемента ИЛИ и вторым входом четырнадцатого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, второй и третий входы и выход которого соединены соответственно с выходами десятого и пятнадцатого элементов И и стробируюшим входом второго дешифратора, шестой выход третьего дешифратора соединен с четвертым входом четвертого элемента ИЛИ и вторым входом тринадцатого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ,

второй и третий входы и РЫХОД кото- poio соединетгы соответственно с выходами двенадцатого и одиннадцатого элементов И и стробирующим входом первого дешифратора, седьмой выход третьего дешифратора соединен с четвертым входом второго элемента И, выход которого соединен с i одом первого одновибратора, вторыми входами восьмого и девятого элементов И и подключен к выходу признака обращени к каналам ввода-вывода процессора, выход первого элемента ИЛИ соединен с вторым входом седьмого элемента И и первым входом шестого элемента ИЛИ второй вход которого соединен с выходом четвертого элемента ИЛИ и вторым входом пятого элемента И, выход седьмого элемента ИЛИ подключен к вы ходу управления модификацией адреса процессора, первый синхровход и вход признака начала обработки процессора подключены соответственно к инверсному и прямому входам первого эле- мента И-КЕ, выход третьего элемента ИЛИ соединен с входом запуска формирователя импульсов и входом второго одновибратора, выход которого соединен с выходом признака окончания об- работки инструкций процессора, выход первого элемента И соединен с первыми входами шестнадцатого и семнадцатого элементов И, второй синхровход процессора подключен к тактовому входу формирователя импульсов, первый выход которого соединен с вторым входом шестнадцатого элемента И и вторым входом шестого элемента И, выход которого соединен с первым вхо дом восемнадцатого элемента И, второй вход и выход которого соединены соответственно с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и входом установки в О второго триггера, выход которо го соединен с первым входом восьмого элемента ИЛИ и информационным входом третьего триггера, вход синхронизации которого соединен с выходом девятнадцатого элемента И, первый вход которого соединен с выходом шестнадцатого элемента И и первыми входами двадцатого и двадцать первого элемен- - тов И, выходы которых соединены соответственно с входом синхронизации четвертого триггера и первым входом установки в 1 второго триггера, второй вход установки в 1 которого соединен с выходом второго элемента

5 0 0 д

5

64|

ИЛИ, входами установки в О третьего и пятого триггеров и первым входом установки в О четвертого триггера, выход которого соединен с вторыми входами восьмого элемента ИЛИ и двадцать первого элемента И, выход восьмого элемента ИЛИ соединен с информационным входом четвертого триггера, второй вход установки в О которого соединен с выходом двадцать второго элемента И, первый вход которого соединен с выходом семнадцатого элемента И и первыми входами двадцать третьего элемента И и второго элемента И-НЕ, выходы которых соединены с входами синхронизации соответственно второго и пятого триггеров, второй вход семнадцатого элемента И соединен с вторым выходом формирователя импульсов и вторым входом четвертого элемента И, информационный вход и инверсный выход пятого триггера подключены к вторым входам третьего и девятнадцатого элементов И, прямой выход пятого триггера соединен с вторыми входами двадцатого и двадцать третьего элементов И, выход третьего триггера соединен с первым входом двадцать четвертого элемента И, выход которого соединен с информационным входом второго триггера, выход первого одновибратора соединен с третьим входом девятого элемента И и входом третьего одновибратора, выход которого соединен с четвертым входом девятого элемента И и подключен к выходу признака готовности процессора, выходы сопровождения вывода и сопровождения ввода процессора подключены к выходам соответственно девятого и восьмого элементов И, отличающийся тем, что, с целью повышения быстродействия за счет реализации одновременной обработки различных типов инструкций, он содержит шифратор, с первого по восьмой входы которого объединены и подключены к информационному выходу узла двунаправленной передачи данных, девятый вход и первый выход шифратора соединены соответственно с выходом первого элемента И третьим входом третьего элемента ИЛИ, четвертый вход которого соединен с вторыми входами второго элемента И-НЕ и двадцать четвертого элемента И, третьими входами девятнадцатого, двадцатого и

13

двадцать первого элементов И и вторым выходом шифратора, третий выход которого соединен с пятым входом

1

1476464

14

третьего элемента ИЛИ, вторым входом двадцать второго и третьим входом двадцать первого элементов И.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1984 |

|

SU1453404A1 |

| Однобитовое операционное устройство | 1982 |

|

SU1070542A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для обработки прерываний | 1986 |

|

SU1606975A1 |

| Контроллер прямого доступа к памяти | 1991 |

|

SU1789987A1 |

Изобретение относится к вычислительной технике и предназначено для построения программируемых контроллеров. Целью изобретения является повышение быстродействия. Устройство содержит регистр, шифратор, дешифраторы, формирователь импульсов, одновибраторы, триггеры, элемент ИЛИ-НЕ, элементы ИЛИ, элементы И-НЕ, элементы И, две группы элементов И-НЕ, мультиплексор, узел двунаправленной передачи данных, элемент исключающее ИЛИ. Цель изобретения достигается за счет реализации одновременной обработки различных инструкций (например, "начало ветви" и "вход" или "выход"). 3 ил, 3 табл.

Где XX...X - любой код, кроме указанных выше.

n i

-Jh Х2

Формируются сигналы С2, ТЗ и Т4. 1 Состояние триггера 11 не изменяется, так как элемент И 41 будет закрыт.

Под действием сигналов Cl, T2 н О НВТ информация с триггера 11 перепишется в триггер 13. Под действием сигналов С1, ТА и НВТ триггер 12 установится в состояние 1 (откроется ветвь). Под действием сигналов С2, ТЗ и СОСТ триггер 11 установится в состояние О.

Таблица 2

Т 4h ХЗ

4 5

Т 41т

Х4

Т Х5

t -4Ь Х6

X7 О

t НЬ XS 1

1-О У1

Под действием сигналов С1, ТЗ и 1 НВТ в триггер 14 запишется результат логического сложения ао ИЛИ с выходоъ триггеров 11 и 14, под действием сигналов СI, Т4 и НВТ информация с триггера 13 перепишется в триггер 11. По заднему фронту 12 установится в состояние О (закроется ветвь). Затем сформируются сигналы С2, ТЗ, Т4, которые не изменят состояния процессора.

См. шаг 2 (откроется ветвь). О

Под действием сигналов С1, ТЗ и 1 НВТ в триггер 14 запишется результат логического сложения по ИЛИ с выходов триггеров 11 и 14, под действием сигналов С1, Т4, НВТ информация с триггера 13 перепишется в триггер 11, по заднему фронту совокупности этих сигналов триггер 12 установится в состояние О (закроется ветвь).

Под действием сигналов С1, ТЗ и 1 НВТ информация с триггера 11 перепишется в триггер 13. Под действием сигналов Cl, T4 и НВТ триггер 12 установится в состояние 1 (откроется ветвь). Затем сформируются сигналы С2, ТЗ и Т4, которые не изменят состояние процессора.

См. шаг 5 (закроется ветвь). Под О действием сигналов СЗ, Т2 и СОСТ триггер 11 установится в состояние О.

Под действием сигналов С1, ТЗ и 1 КВТ в триггер 11 запишется резулъ- тат логического сложения по ИЛИ с выходов триггеров II и 14, под действием сигналов Cl, T4 и КВТ триггер 14 установится в состоя- 0.

ние

См, шаг К

См. шаг 1 (откроется ветвь).С триггера 11 выдается сигнал РЕЗ (О), затем формируются сигналы С4 и Т4, которые не изменят состояние процессора.

Продо.( табл.3

1 О

О О

О 1 1

о о о

2 3

tr Hh

и -оХ9У2

5

Т. ЧН

-оХ10УЗ

См. таг 3 (закроется ветвь).

Под действием сигналов Cl, T3 и НВТ информация с триггера 11 Ае- репишется в триггер 13. Под действием сигналов Cl, Т4 и НВТ триггер I2 установится в состояние 1 (откроется ветвь). X триггера 11 выдается сигнал РЕЗ () Затем сформируются сигналы С4 и Т4, которые не изменят состояние процессора.

См. шаг 2 (закроется ветвь). С триггера 11 выдается результат (сигнал РЕЗ) уровнем О. Затем под действием сигналов С4 и Т4 триггеры 13 и 14 установятся в состояние О, триггер 11 - в состояние 1, триггер 12 останется в состояние О. Процессор установится в исходное состояние.

10 1)0-1)7

О 1

О О

Wjuuinnn.

У1

о92

Охю УК

ньон

| Патент США № 4172289, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Программируемый контроллер | 1984 |

|

SU1453404A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-30—Публикация

1986-08-04—Подача