1

Изобретение относится к вычислительной технике и может быть использовано при создании быстродействующих оператщонных систем обработки информации в системах с диалоговом режимом работы, отладки и выполне- -ния программ в аппаратных преобразователях (эмуляторах, интерпретаторах и т.п.) при непосредственной реализации языков высокого уровня, а также в устройствах с адаптивной распределенной обработкой информации повьпиенной достоверности.

Цель изобретения - увеличение бы родействия и расширение функциональных возможностей за счет введения адаптивной распределенной обработки информации.

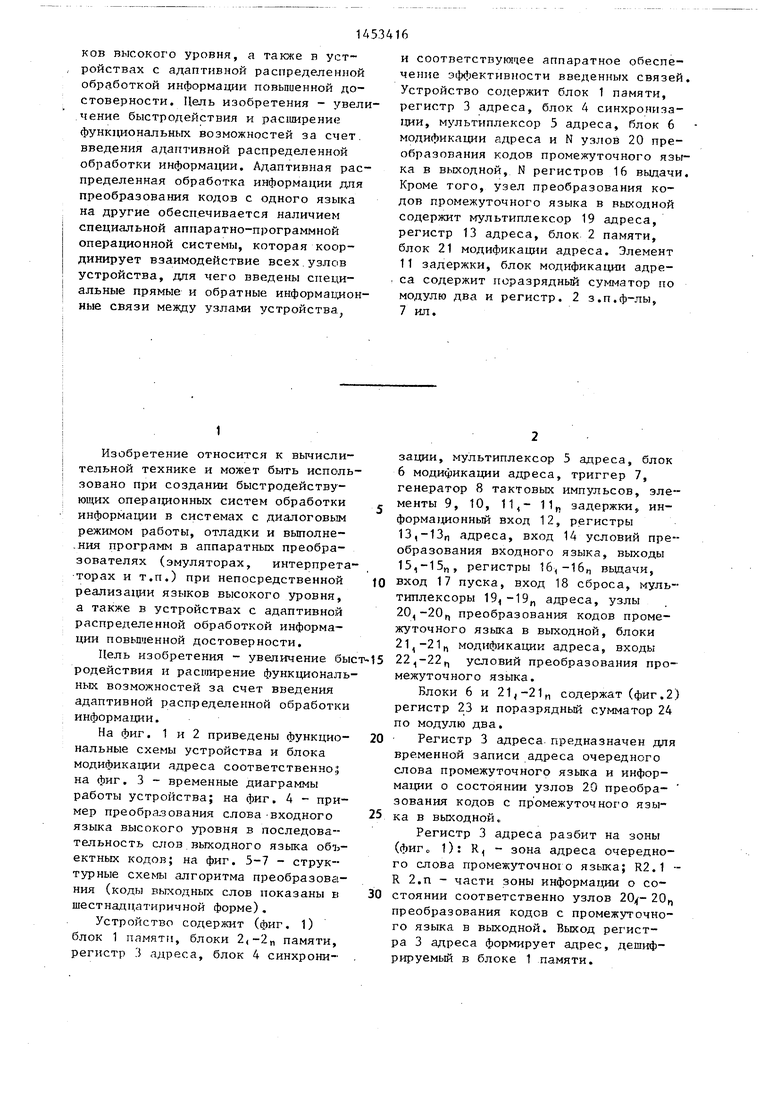

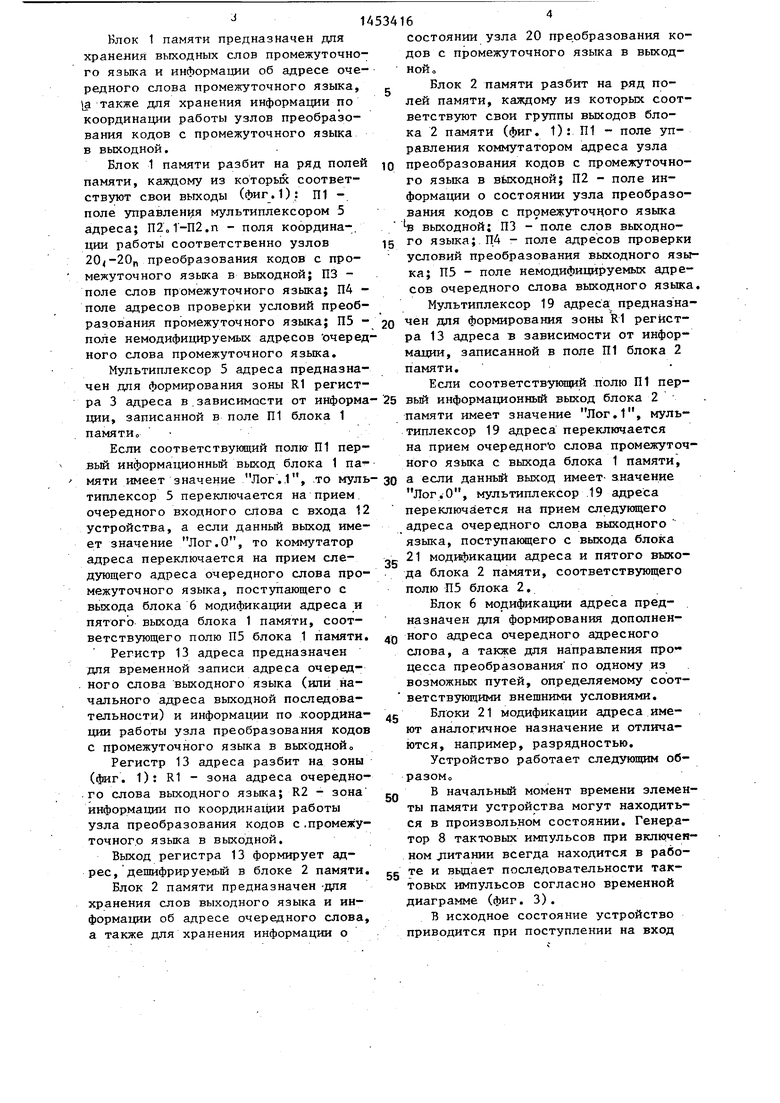

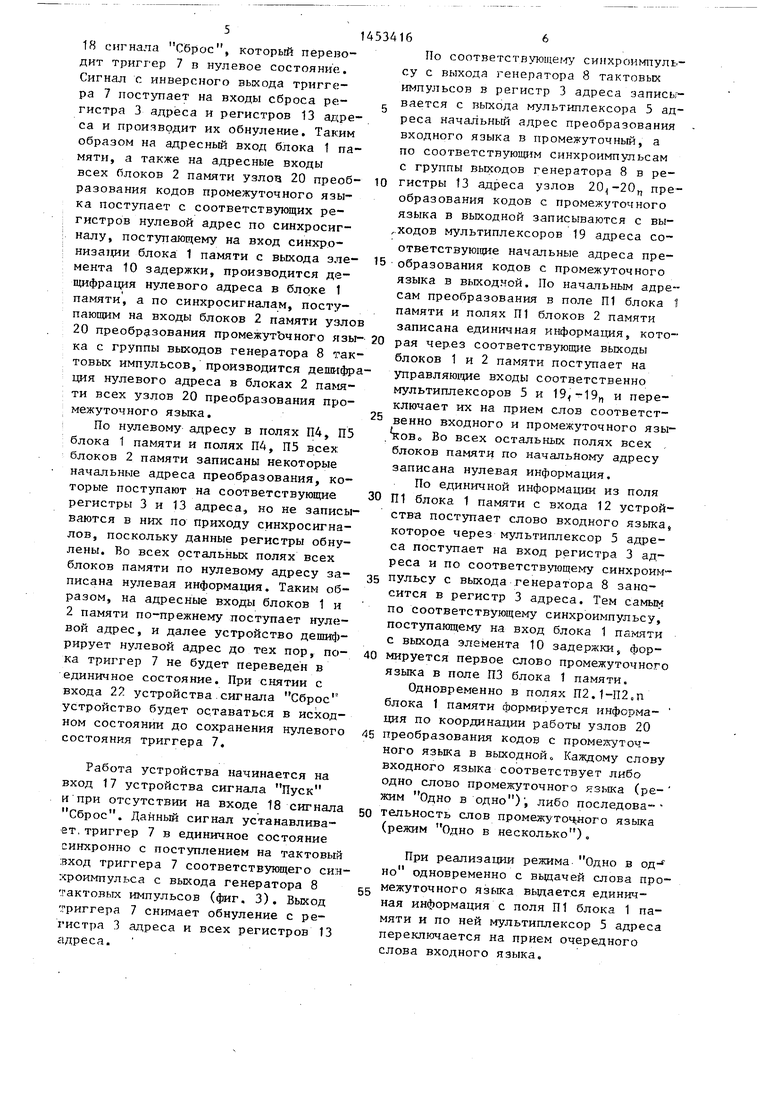

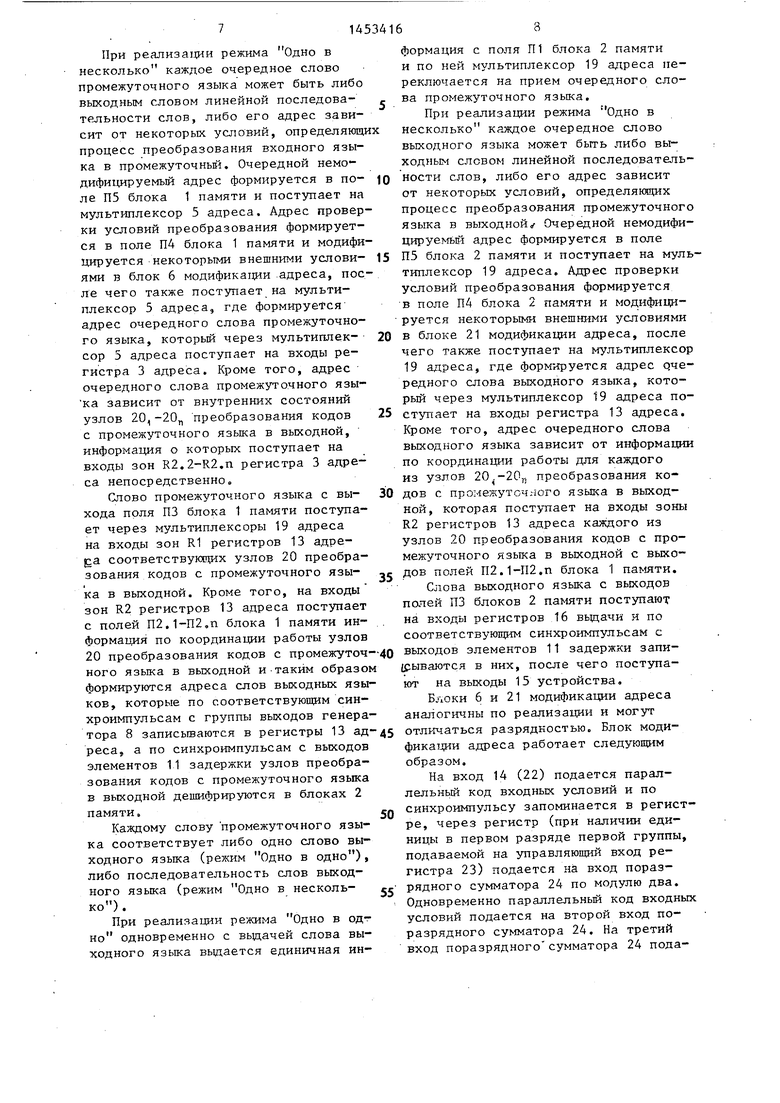

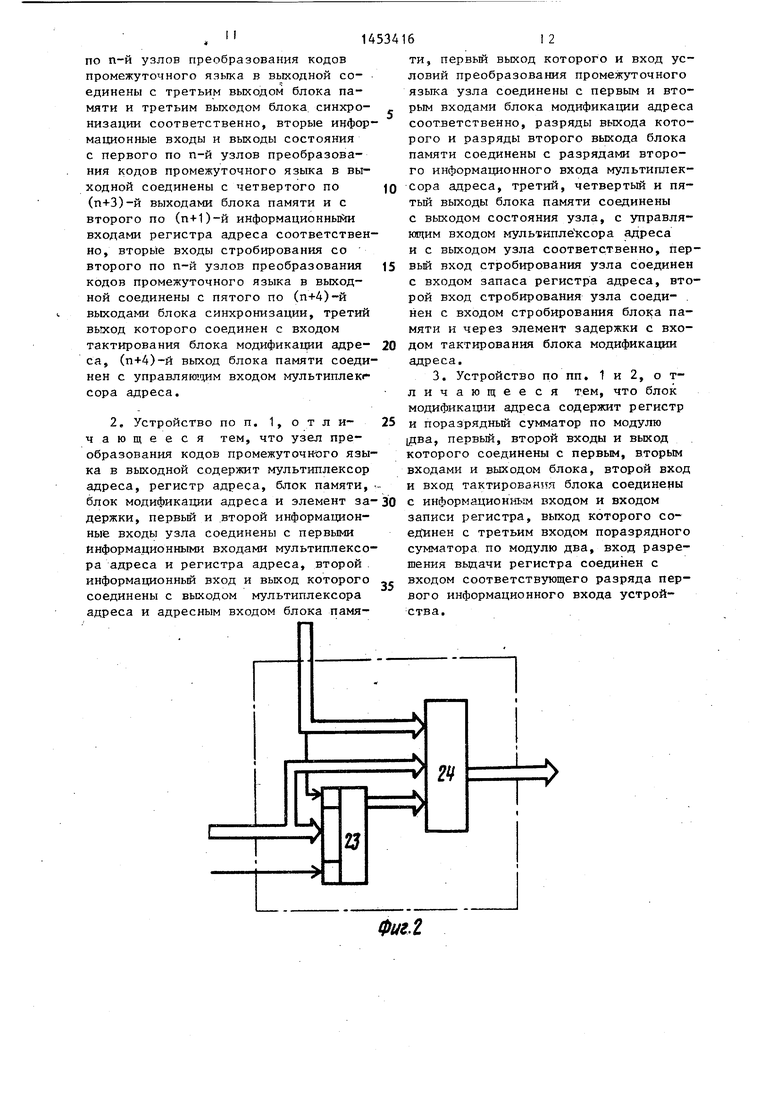

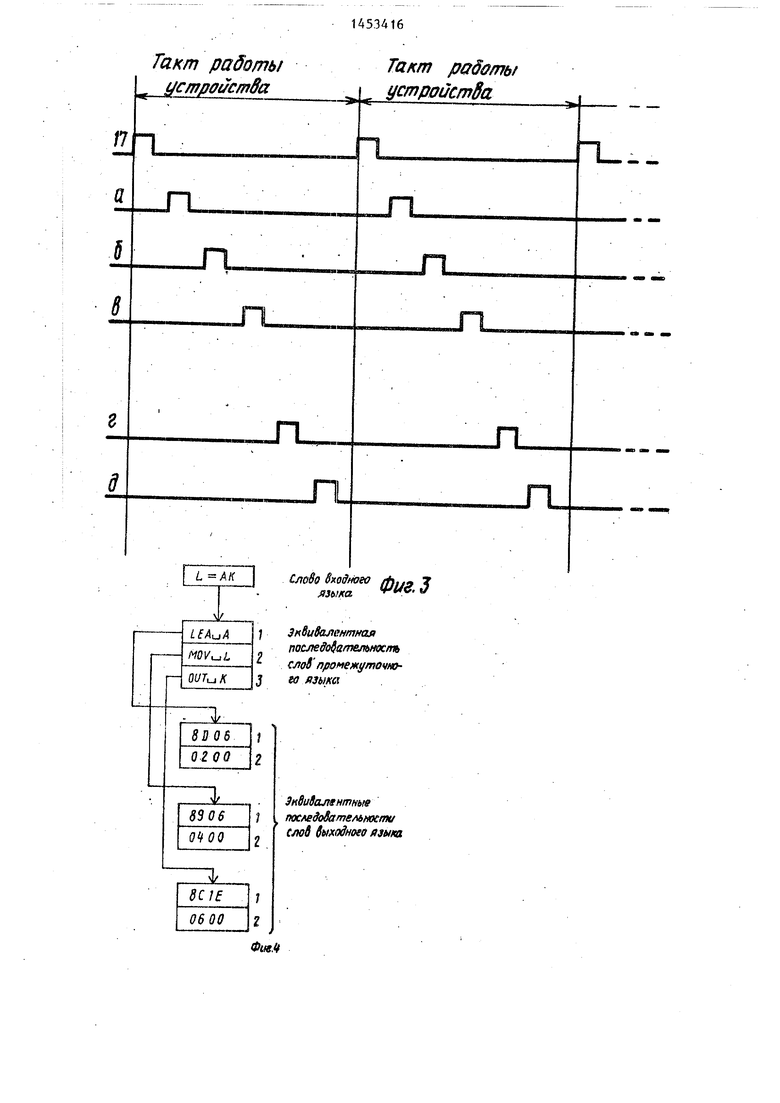

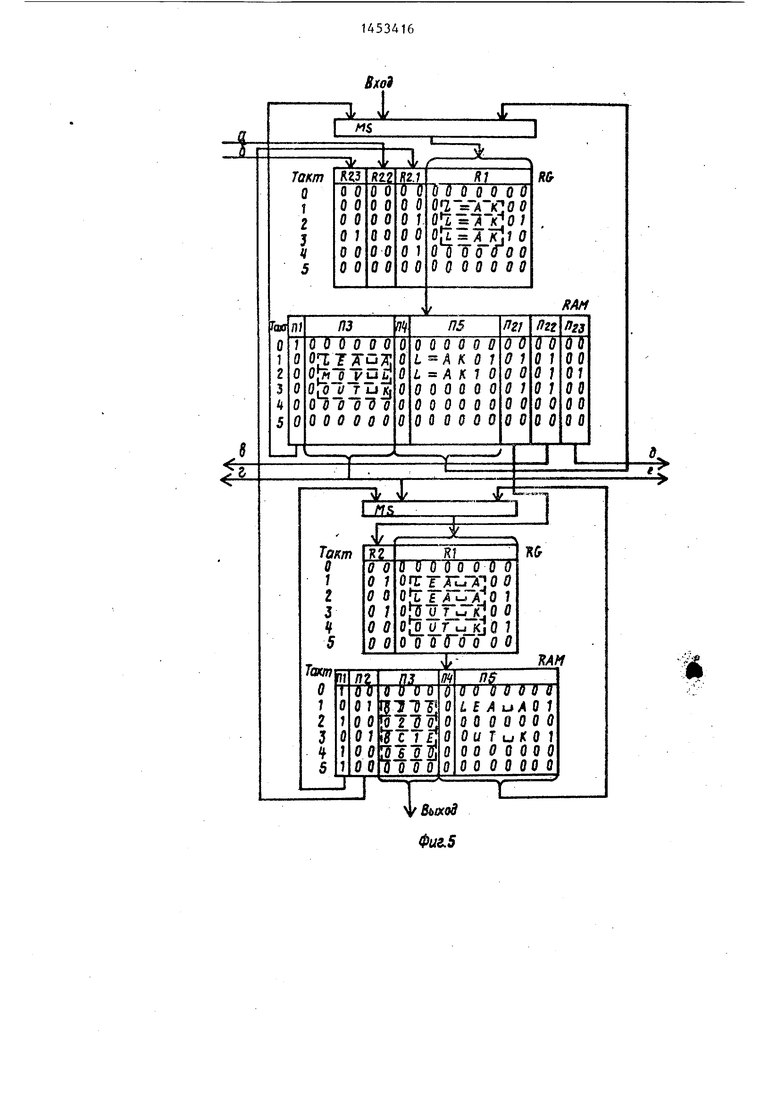

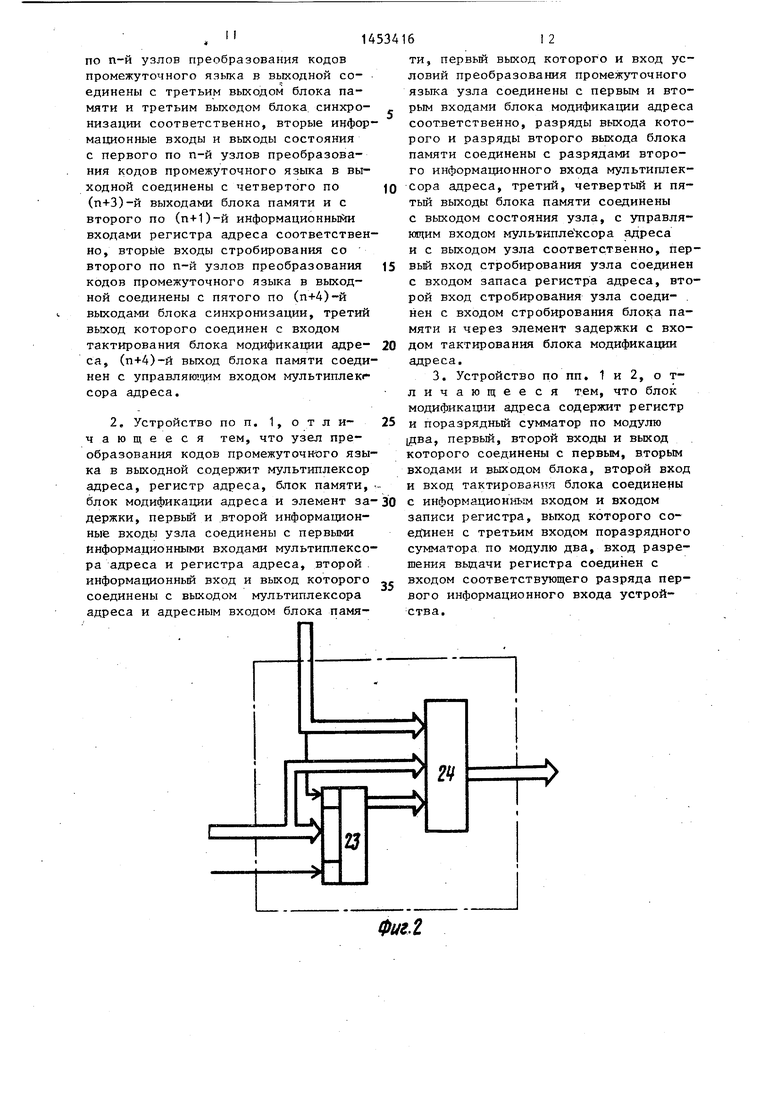

На фиг. 1 и 2 приведены функцио- нальные схемы устройства и блока модификации адреса соответственно;; на фиг. 3 - временные диаграммы работы устройства; на фиг. 4 - пример преобразования слова-входного языка высокого уровня в последовательность слов выходного языка объектных кодов; на фиг. 5-7 - структурные схемы алгоритма преобразования (коды выходных слов показаны в шестнадцатиричной форме),

Устройство содержит (фиг. 1) блок 1 памяти, блоки памяти, регистр 3 адреса, блок 4 синхронизации, мультиплексор 5 адреса, блок 6 модификации адреса, триггер 7, генератор 8 тактовых импульсов, элементы 9, 10, 11,- 11„ задержки, ин- форма)дионный вход 12, регистры 13,-13,, адреса, вход 14 условий преобразования входного языка, выходы 15i-15, регистры 16,-16 вьщачи, вход 17 пуска, вход 18 сброса, мультиплексоры адреса, узлы 20,-20 преобразования кодов промежуточного языка в выходной, блоки модификации адреса, входы 22,-22 условий преобразования промежуточного языка.

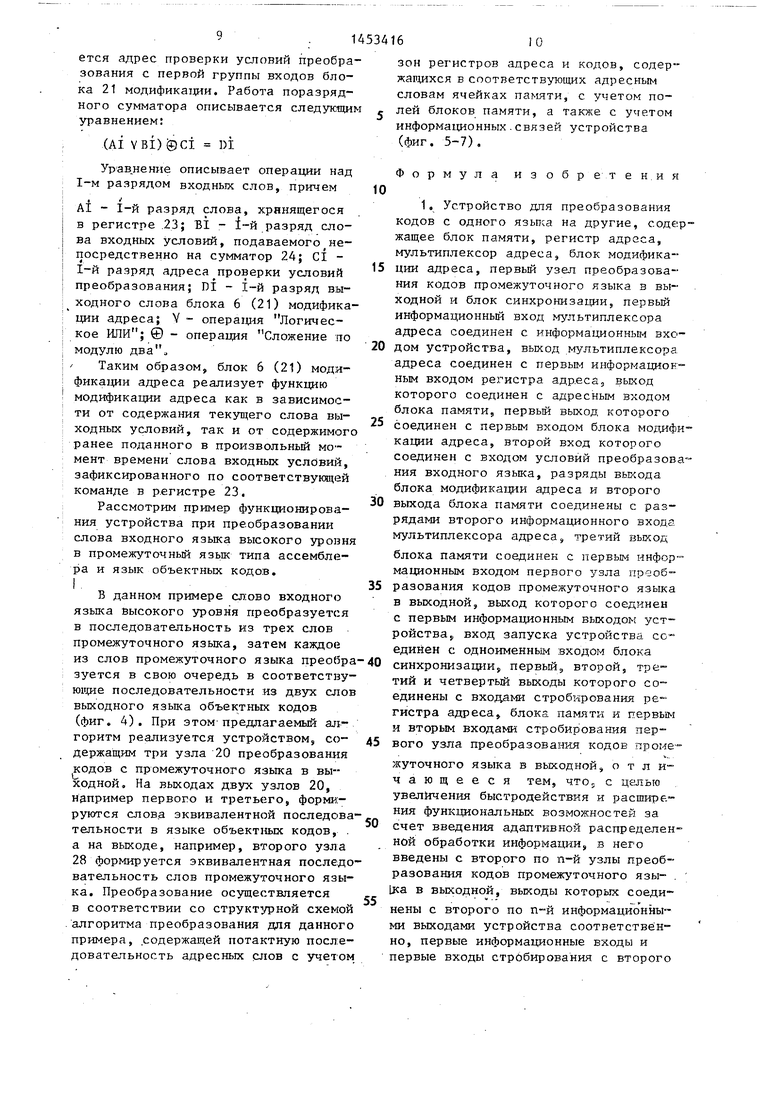

Блоки 6 и содержат (фиг.2) регистр 23 и поразрядный сумматор 24 по модулю два.

Регистр 3 адреса предназначен для временной записи адреса очередного слова промежуточного языка и информации о состоянии узлов 20 преобра- зования кодов с промежуточного языка в выходной„

Регистр 3 адреса разбит на зоны (фиг о 1): R, - зона адреса очередного слова промежуточного языка; R2.1 - R 2.П - части зоны информащш о состоянии соответственно узлов 20 преобразования кодов с промежуточного языка в выходной. Выход регистра 3 адреса формирует адрес, дешифрируемый в блоке 1 памяти.

Блок 1 памяти предназначен для хранения выходных слов промежуточного языка и информации об адресе очередного слова промежуточного языка, а также для хранения информации по координации работы узлов преобразования кодов с промежуточного языка в выходной.

Блок 1 памяти разбит на ряд полей памяти, каждому из которых соответствуют свои выходы (фиг. 1): П1 -, поле управлен1 я мультиплексором 5 адреса; П2о1 -П2.п - поля координа-. ции работы соответственно узлов преобразования кодов с промежуточного языка в выходной; ПЗ - поле слов промежуточного языка; П4 - поле адресов проверки условий преобразования промежуточного языка; П5 - поле немодифидируемых адресов очередного слова промежуточного языка.

Мультиплексор 5 адреса предназнасостоянии узла 20 преобразования кодов с промежуточного языка в выходной.

Блок 2 памяти разбит на ряд полей памяти, каждому из которых соответствуют свои группы выходов блока 2 памяти (фиг. 1): П1 - поле управления коммутатором адреса узла 10 преобразования кодов с промежуточного языка в выходной; П2 - поле информации о состоянии узла преобразования кодов с промежуточного языка в выходной: ПЗ - поле слов выходно- 15 го языка; Ц4 - поле адресов проверки условий преобразования выходного язы ка; П5 - поле немодифицируемых адресов очередного слова выходного языка Мультиплексор 19 адреса предназна- 20 чен для формирования зоны R1 регистра 13 адреса в зависимости от информации, записанной в поле П1 блока 2 памяти.

Если соответствующий полю П1 перчен для формирования зоны R1 регистра 3 адреса в. зависимости от информа- 25 вый информационный выход блока 2 ции, записанной в поле П1 блока 1 памяти имеет значение Лог.1, муль- памятио

Если соответствующий полю- П1 первый информационный выход блока 1 патиплексор 19 адреса переключается на прием очередного слова промежуточного языка с выхода блока 1 памяти.

мяти имеет значение Лог..Г , .то муль- зо а если данньй выход имеет- значение

Лог.О, мультиплексор .19 адреса переключается на прием следующего адреса очередного слова выходного языка, поступакяцего с выхода блока 21 модификации адреса и пятого выхода блока 2 памяти, соответствующего полю ПЗ блока 2,

типлексор 5 переключается на прием. очередного входного слова с входа 12 устройства, а если данный выход имеет значение Лог.О, то коммутатор адреса переключается на прием следующего адреса очередного слова промежуточного языка, поступающего с выхода блока 6 модификации адреса я пятого выхода блока 1 памяти, соответствующего полю П5 блока 1 памяти.

Регистр 13 адреса предназначен дпя временной записи адреса очеред- ного слова выходного языка (ипи начального адреса выходной последовательности) и информации по .координации работы узла преобразования кодов с промежуточного языка в выходной.

Регистр 13 адреса разбит на зоны (фиг. 1): R1 - зона адреса очередно- го слова выходного языка; R2 - зона информации по координа14ии работы узла преобразования кодов с .промежуточного языка в выходной.

Выход регистра 13 формирует адрес, дешифрируемьй в блоке 2 памяти.

Блок 2 памяти предназначен -для хранения слов выходного языка и информации об адресе очередного слова, а также для хранения информации о

состоянии узла 20 преобразования кодов с промежуточного языка в выходной.

Блок 2 памяти разбит на ряд полей памяти, каждому из которых соответствуют свои группы выходов блока 2 памяти (фиг. 1): П1 - поле управления коммутатором адреса узла преобразования кодов с промежуточного языка в выходной; П2 - поле информации о состоянии узла преобразования кодов с промежуточного языка в выходной: ПЗ - поле слов выходно- го языка; Ц4 - поле адресов проверки условий преобразования выходного языка; П5 - поле немодифицируемых адресов очередного слова выходного языка. Мультиплексор 19 адреса предназна- чен для формирования зоны R1 регистра 13 адреса в зависимости от информации, записанной в поле П1 блока 2 памяти.

Если соответствующий полю П1 первый информационный выход блока 2 памяти имеет значение Лог.1, муль-

вый информационный выход блока 2 памяти имеет значение Лог.1, муль-

типлексор 19 адреса переключается на прием очередного слова промежуточного языка с выхода блока 1 памяти.

а если данньй выход имеет- значение

Лог.О, мультиплексор .19 адреса переключается на прием следующего адреса очередного слова выходного языка, поступакяцего с выхода блока 21 модификации адреса и пятого выхода блока 2 памяти, соответствующего полю ПЗ блока 2,

Блок 6 модификации адреса пред- . назначен для формирования дополненного адреса очередного адресного слова, а также для направления процесса преобразования по одному из возможных путей, определяемому соответствующими внешними условиями.

Блоки 21 модификации адреса имеют аналогичное назначение и отличаются, например, разрядностью.

Устройство работает следующим образом,

В начальный момент времени злемен- ты памяти устройства могут находиться в произвольном состоянии. Генератор 8 тактювых импульсов при ном Д1итании всегда находится в рабо- те и вьщает последовательности тактовых импульсов согласно временной диаграмме (фиг. 3).

В исходное состояние устройство приводится при поступлении на вход

18 сигнала Сброс, который переводит триггер 7 в нулевое состояние. Сигнал с инверсного выхода триггера 7 поступает на входы сброса регистра 3 адреса и регистров 13 адреса и производит их обнуление. Таким образом на адресный вход блока 1 памяти, а также на адресные входы всех блоков 2 памяти узлоч 20 преобразования кодов промежуточного языка поступает с соответствующих регистров нулевой адрес по синхросигналу, поступающему на вход синхронизации блока 1 памяти с выхода элемента 10 задержки, производится д,- Щифращ1я нулевого адреса в блоке 1 памяти, а по синхросигналам, поступающим на входы блоков 2 памяти узлов

1453416

10

По соответствующег г, синхроимп су с выхода генератора 8 тактовы импульсов в регистр 3 адреса зап 5 вается с выхода мультиплексора 5 реса начальньй адрес преобразова входного языка в промежуточный, по соответствующем синхроимпульс с группы выходов генератора 8 в гистры 13 адреса узлов образования кодов с промежуточно языка в выходной записываются с .ходов мультиплексоров 19 адреса ответстную1 ще начальные адреса п 15 образования кодов с промежуточно языка в выходной. По начальным а сам преобразования в поле П1 бло памяти и полях П1 блоков 2 памят записана единичная информация, к

ТЧЯС TTfii-ij ч.-..л..

wjxuo и. памяти узлов

/си преобразования промежутЪчного язы- рп «-j- -., к

ка с группы выходов генератора 8 так- Г Т °° твующие вькоды товьк импульсов, производится деяифра- ,. поступает на ция нулевого адреса в блоках 2 памяти всех узлов 20 преобразования промежуточного языка.

По нулевому адресу в полях П4, П5 блока 1 памяти и полях ПА, П5 всех блоков 2 памяти записаны некоторые начальные адреса преобразования, которые поступают на соответствующие регистры 3 и 13 адреса, но не записываются в них по приходу синхросигналов, поскольку данные регистры обнулены. Во всех остальных полях всех блоков памяти по нулевому адресу записана нулевая информация. Таким об- Разом, на адресные входы блоков 1 и памяти по-прежнему поступает нулевой адрес, и далее устройство деший - рирует нулевой адрес до тех пор, поWilT T TTTTnj- T 7... -- fj 1 (2л iiup ,

ка триггер 7 не будет переведен в единичное состояние. При снятии с входа 22 устройства.сигнала Сброс устройство будет оставаться в исходТТОКТ .i-r ttr-r

ном состоянии до сохранения нулевого .. Т Г °°P ™ Работы узлов 2 состояния триггера 7. «У евого 45 преобразования кодов с промежуточ

НПГТ OOLiT/- л Т-, i..

-.j. iiaci Hcl

УправляЮ1чие входы соответственно мультиплексоров 5 и и пер ключает их на прием слов соответс венно входного и промежуточного я .ково Во всех остальных полях всех блоков памяти по начальному адрес записана нулевая информация. in ni «° единичной информации из пол - П1 блока 1 памяти с входа 12 устр ства поступает слово входного язы которое через мультиплексор 5 адр са поступает на вход регистра 3 а реса и по соответствующему синхро 35 пульсу с выхода генератора 8 зано сится в регистр 3 адреса. Тем сам по соответствующему синхроимпульс поступающему на вход блока 1 памя с выхода элемента 10 задержки, Аор 40 мируется первое слово промежуточно языка в поле ПЗ блока 1 памяти.

Одновременно в полях П2.1-П2.п блока 1 памяти формируется инфогжа ция по координации работы узлов 20

ТТТЛ oRn i3f5j-,,..™. - .

ного языка в выходной. Каждому сло входного языка соответствует либо одно слово промежуточного язьжа (р жим Одно в одно), либо последова тельность слов промежуто ного язык (режим Одно в несколько).

Работа устройства начинается на вход 17 устройства сигнала Пуск отсутствии на входе 18 сигнала

. Данный сигнал устанавливает, триггер 7 в единичное состояние синхронно с поступлением на тактовый вход триггера 7 соответствующего синхроимпульса с выхода генератора 8 тактовых импульсов (фиг. 3). Выход триггера 7 снимает обнуление с регистра 3 адреса и всех регистров 13 адреса.

1453416

0

По соответствующег г, синхроимпульсу с выхода генератора 8 тактовых импульсов в регистр 3 адреса записы- 5 вается с выхода мультиплексора 5 адреса начальньй адрес преобразования входного языка в промежуточный, а по соответствующем синхроимпульсам с группы выходов генератора 8 в регистры 13 адреса узлов преобразования кодов с промежуточного языка в выходной записываются с вы- .ходов мультиплексоров 19 адреса со- ответстную1 ще начальные адреса пре- 5 образования кодов с промежуточного языка в выходной. По начальным адресам преобразования в поле П1 блока 1 памяти и полях П1 блоков 2 памяти записана единичная информация, котоТЧЯС TTfii-ij ч.-..л..

п «-j- -., к

Г Т °° твующие вькоды ,. поступает на

Г Т °° твующие вькоды ,. поступает на

. Т Г °°P ™ Работы узлов 2 5 преобразования кодов с промежуточ

-.j. iiaci Hcl

УправляЮ1чие входы соответственно мультиплексоров 5 и и пере- ключает их на прием слов соответственно входного и промежуточного язы- .ково Во всех остальных полях всех блоков памяти по начальному адресу записана нулевая информация. in ni «° единичной информации из поля П1 блока 1 памяти с входа 12 устройства поступает слово входного языка. которое через мультиплексор 5 адреса поступает на вход регистра 3 адреса и по соответствующему синхроим- 5 пульсу с выхода генератора 8 зано- сится в регистр 3 адреса. Тем самым по соответствующему синхроимпульсу поступающему на вход блока 1 памя-и с выхода элемента 10 задержки, Аор- 0 мируется первое слово промежуточного языка в поле ПЗ блока 1 памяти.

Одновременно в полях П2.1-П2.п блока 1 памяти формируется инфогжа- ция по координации работы узлов 20

ТТТЛ oRn i3f5j-,,..™. - .

.. Т Г °°P ™ Работы узлов 2 45 преобразования кодов с промежуточ

НПГТ OOLiT/- л Т-, i..

50

ного языка в выходной. Каждому слову входного языка соответствует либо одно слово промежуточного язьжа (ре- жим Одно в одно), либо последова-. тельность слов промежуто ного языка (режим Одно в несколько).

При реализации режима. Одно в од- но одновременно с вьщачей слова про- 65 межуточного языка вьщается единичная информация с поля П1 блока 1 памяти и по ней мультиплексор 5 адреса переключается на прием очередного слова входного языка.

7145

При реалиэадаи режима Одно в несколько каждое очередное слово промежуточного языка может быть либо выходным словом линейной поеладова- тельности слов, либо его адрес зависит от некоторых условий, определяющи процесс преобразования входного языка в промежуточньй. Очередной немо- дифицируемьй адрес формируется в по- ле П5 блока 1 памяти и поступает на мультиплексор 5 адреса. Адрес проверки условий преобразования формируется в поле П4 блока 1 памяти и модифицируется некоторыми внешними услови- ями в блок 6 модификацией адреса, после чего также поступает на мультиплексор 5 адреса, где формируется адрес очередного слова промежуточного языка, которьм через мультиплек- сор 5 адреса поступает на входы регистра 3 адреса. Кроме того, адрес очередного слова промежуточного язы- ка зависит от внутренних состояний

узлов 20,-20„ преобразования кодов с промежуточного языка в выходной, информация о которых поступает на входы зон R2.2-R2.n регистра 3 адреса непосредственно.

Слово промежуточного языка с вы- хода поля ПЗ блока 1 памяти поступает через мультиплексоры 19 адреса на входы зон R1 регистров 13 адре- ga соответствуюощх узлов 20 преобразования кодов с промежуточного язы- ка в выходной. Кроме того, на входы зон R2 регистров 13 адреса поступает с полей П2.1-П2,п блока 1 памяти информация по координации работы узлов 20 преобразования кодов с промежуточ ного языка в выходной и-таким образо формируются адреса слов выходных языков, которые по соответствующим синхроимпульсам с группы выходов генератора 8 записываются в регистры 13 ад реса, а по синхроимпульсам с выходов элементов 11 задержки узлов преобразования кодов с промежуточного языка в выходной дешифрируются в блоках 2 памяти,

Каждому слову промежуточного языка соответствует либо одно слово выходного языка (режим Одно в одно), либо последовательность слов выходного языка (режим Одно в несколь-

ко).

При реализации режима Одно вод-г но одновременно с вьщачей словавыходного языка выдается единичнаяинормация с поля П1 блока 2 памяти и по ней мультиплексор 19 адреса переключается на прием очередного слова промежуточного языка.

При реализации режима Одно в несколько каждое очередное слово выходного языка может быть либо выходным словом линейной последовательности слов, либо его адрес зависит от некоторых условий, определянщих процесс преобразования промежуточного языка в выходной Очередной немодифи- цируе йзй адрес формируется в поле П5 блока 2 памяти и поступает на мультиплексор 19 адреса. Адрес проверки условий преобразования формируется в поле П4 блока 2 памяти и модифици- руется некоторыми внешними условиями в блоке 21 модификации адреса, после чего также поступает на мультиплексор 19 адреса, где формируется адрес очередного слова выходного языка, который через мультиплексор 19 адреса поступает на входы регистра 13 адреса. Кроме того, адрес очередного слова выходного языка зависит от информации по координации работы для каждого из узлов 20,-20„ преобразования кодов с промежуточного языка в выходной, которая поступает на входы зоны R2 регистров 13 адреса каждого из узлов 20 преобразования кодов с промежуточного языка в выходной с выходов полей П2.1-П2.П блока 1 памяти.

Слова выходного языка с выходов полей ПЗ блоков 2 памяти поступают на входы регистров 16 вьщачи и по соответствующим синхрош-шульсам с выходов элементов 11 задержки запи- рываются в них, после чего поступают на выходы 15 устройства.

Блоки 6 и 21 модификации адреса аналтогичны по реализации и могут отличаться разрядностью. Блок модификации адреса работает следующим образом.

На вход 14 (22) подается парал- лельньй код входных условий и по синхроимпульсу запоминается в регистре, через регистр (при наличии единицы в первом разряде первой группы, подаваемой на уи-равпяют ш вход регистра 23) подается на вход поразрядного сумматора 24 по модулю два. Одновременно параллельньм код входных условий подается на второй вход поразрядного сумматора 24. На третий вход поразрядного сумматора 24 пода9 . 14534 ется адрес проверки условий преобразования с первой группы входов блока 21 модификат ии. Работа поразрядного сумматора описывается следующим уравнением:

15

20

25

30

(А1 YBi)ci Di

Урав.нение описывает операции над 1-м разрядом входных слов, причем ю

I i

AI - 1-й разряд слова, хрянящегося в регистре .23; в - 1-й разряд слова входных условий, подаваемого непосредственно на сумматор 24; С1 - 1-й разряд адреса проверки условий преобразования; DI - 1-й разряд вы- ходного слова блока 6 (21) модификации адреса; Y - операция Логическое © - операция Сложение по модулю ,

Таким образом, блок 6 (21) моди- фикащи адреса реализует функцию модификации адреса как в зависимости от содержания текуп его слова выходных условий, так и от содержимого ранее поданного в произвольный момент времени слова входных условий, зафиксированного по соответствукяцей команде в р.егистре 23.

Рассмотрим пример функционирования устройства при преобразовании слова входного языка высокого уровня в промежуточньй язьж типа ассемблера и язык объектных кодов. I .

В данном примере сл:ово входного

языка Высокого уровня преобразуется в последовательность из трех слов . промежуточного языка, затем каждое из слов промежуточного языка преобра-40 зуется в свою очередь в соответству- Ю1цие последовательности из двух слов выходного языка объектных кодов (фиг. 4), При этом-предлагаемый алгоритм реализуется устройством, со- 45 держащим три узла 20 преобразования кодов с промежуточного язьпса в выходной. На вькодах двух узлов 20, например первого и третьего, форми:- уются слова эквивалентной последовательности в языке объект1и 1х кодов, . а на выходе, например, второго узла 28 формируется эквивалентная последовательность слов промежуточного языа. Преобразование осуществляется в соответствии со структурной схемой алгоритма преобразования для данного римера, содержащей потактную послеовательность адресных слов с учетом

35

50

55

10

6

зон регистров адреса и кодов, содер- жардихся в соответствующих адресным словам ячейках памяти, с учетом полей блоков памяти, а также с учетом информа1и{онных.связей устройства (фиг. 5-7).

15

20

25

30

ю

0 5

5

0

5

Формула изобретения

1. Устройство для преобразования кодов с одного язьпса на другие, содержащее блок памяти, регистр адреса, мультиплексор адреса, блок модификации адреса, первьм узел преобразования кодов промежуточного языка в выходной и блок синхронизации, первьй информационный вход мультиплексора адреса соединен с информационным входом устройства, выход .мультиплексора, адреса соединен с первым инфор -{ациоЕ- ным входом регистра адреса, выход которого соединен с адресным входом блока памяти, первьй выход которого соединен с первым входом блока модификации адреса, второй вход которого соединен с входом условий преобразования входного языка, разряд.ы выхода блока модификации ад.реса и второго выхода блока памяти соединены с разрядами второго информационного входа мультиплексора адреса, третий выход

блока памяти соединен с первым информационным входом первого узла преобразования кодов промежуточного языка в выходной, выход которого соединен с первым информационным выxoдo E устройства, вход запуска устройства соединен с одноименным входом блока синхронизации, первый, второй, третий и четвертый выходы которого соединены с входами стробирования регистра адреса, блока памяти и первым и вторым входами стробирования первого узла преобразования кодов промежуточного языка в выходной, отличающееся тем, что5 с целью увеличения быстродействия и расщире- ния функциональных возможностей за счет введения адаптивной распределенной обработки информации, в него введены с второго по п-й узлы преобразования кодов промежуточного язы- . 1ка в выходной, выходы которых соединены с второго по п-й информационными выходами устройства соответственно, первые информационные входы и первые входы стрббирования с второго

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухуровневое устройство для управления памятью микрокоманд | 1987 |

|

SU1513448A1 |

| Устройство для трансляции кодов с одного языка на другой | 1985 |

|

SU1283798A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

| Устройство для преобразования кодов с одного языка на другой | 1984 |

|

SU1238104A1 |

| Устройство для преобразования кодов с одного языка на другой | 1983 |

|

SU1136183A1 |

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1275471A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1532965A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1283797A1 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

Изобретение относится к вычислительной технике и может быть использовано при создании быстродействующих операционных систем обработки информации в системах с диалоговым режимом работы, отладки и выполнения программ в аппаратных преобразователях (эмуляторах, интерпретаторах ji ТоП.) при непосредственной реализации язы

Фиг.2

Такт работы

Такт рвдоты 1 ycmpoucmSa

Слббо $яодноео языка

Зкдивалентнал tiocJKSo arr№j Mxmb слоб промежуточного языка

Зкдийситнтныв последовательности с/юд быходноео языка

Фиг. З

Ж

RV

Q 0 Q 0 0 0 Q 1 0 0 0 0

ПЗ

000000

Ofrtjj n ОГо и тик, QOO o bQ Q Q О О О Q

yt

Такт О

1

г

3

«

5

Вхо9

I

Ri

i

0 0 0 0 00 00 00

Ш,

in

Q Q Q I 00 0 1 00

Kl

Q Q Q Q Q о о 0 7x1 О О ОТГГОО О О О О О О О

пч

П5

/7г;

/72 ff23

О Q Q О О О

L-A К О 1

L А К 1 00000

000000 000000

О О О 1 О Q О 1 О О О О

О О

Q 1

о J

О 1 О О О О

00 00

or

00 00 00

J L

1 М5

I

В&веод

| Устройство для преобразования кодов с одного языка на другой | 1984 |

|

SU1238104A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для трансляции кодов с одного языка на другой | 1985 |

|

SU1283798A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-23—Публикация

1987-04-27—Подача