сд

оо

4 00

315134А84

памяти кодов настройки, узлы 29 one-обеспечивает адаптивное управление

рационных микрокоманд,коммутаторы 5,6,процессом формирования операционных

32 адреса, регистры 3,4,31 адреса,микрокоманд с оперативным изменением

регистры 14, 15 хранения, регистры 26архитектуры и алгоритмов функционировыдачи, блоки 7, 8, 33 .модификациивания. 3 ил., 2 табл.. адреса, группу элементов MJffl 13 и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кодов с одного языка на другие | 1987 |

|

SU1453416A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Двухуровневое устройство для управления памятью микрокоманд | 1984 |

|

SU1247882A1 |

| Устройство для формирования периодических функций | 1987 |

|

SU1441391A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

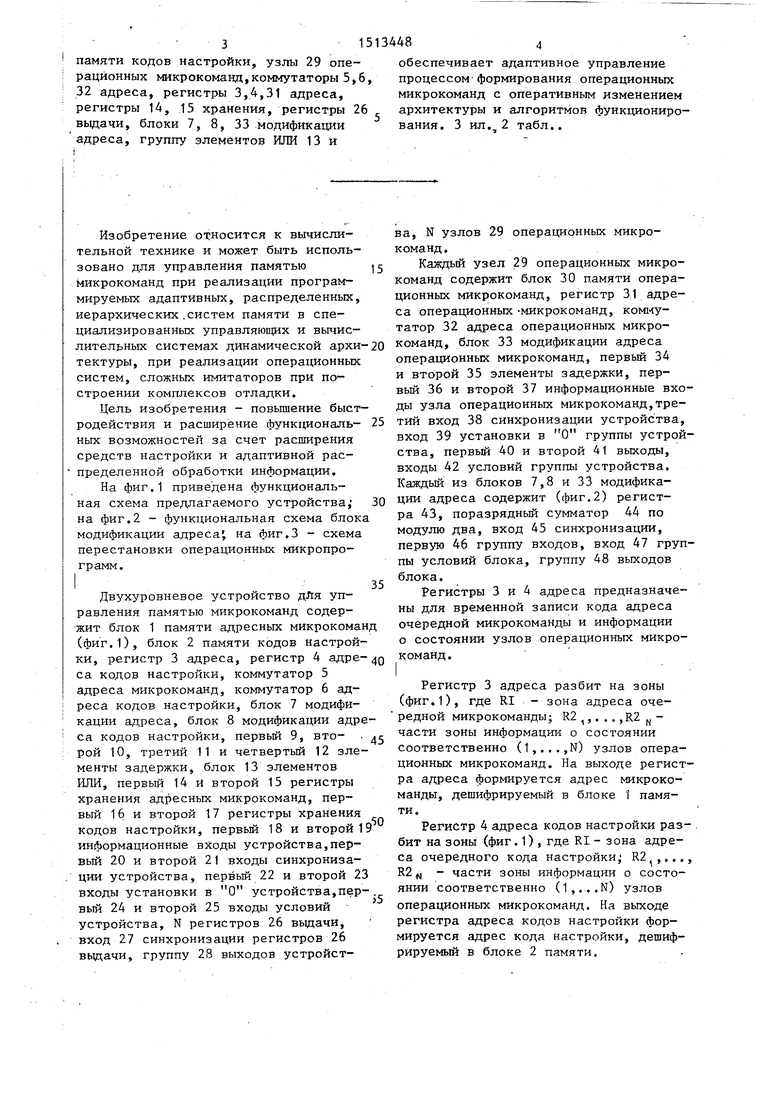

Изобретение относится к программируемым, адаптивным, распределенным системам памяти и может быть использовано в вычислительных системах динамической архитектуры, для реализации операционных систем, сложных имитаторов при построении комплексов отладки. Устройство содержит блок 1 памяти адресных микрокоманд, блок 2 памяти кодов настройки, узлы 29 операционных микрокоманд, коммутаторы 5, 6, 32 адреса, регистры 3, 4, 31 адреса, регистры 14, 15 хранения, регистры 26 выдачи, блоки 7, 8, 33 модификации адреса, группу элементов ИЛИ 13 и обеспечивает адаптивное управление процессом формирования операционных микрокоманд с оперативным изменением архитектуры и алгоритмов функционирования. 4 ил., 2 табл.

Изобретение относится к вычислительной технике и может быть использовано для управления памятью микрокоманд при реализации программируемых адаптивных, распределенных, иерархических.систем памяти в специализированных управляющих и вычислительных системах динамической архитектуры, при реализации операционных систем, сложных имитаторов при построении комплексов отладки.

Цель изобретения - повышение быстродействия и расширение функциональ- ных возможностей за счет расширения средств настройки и адаптивной распределенной обработки информации.

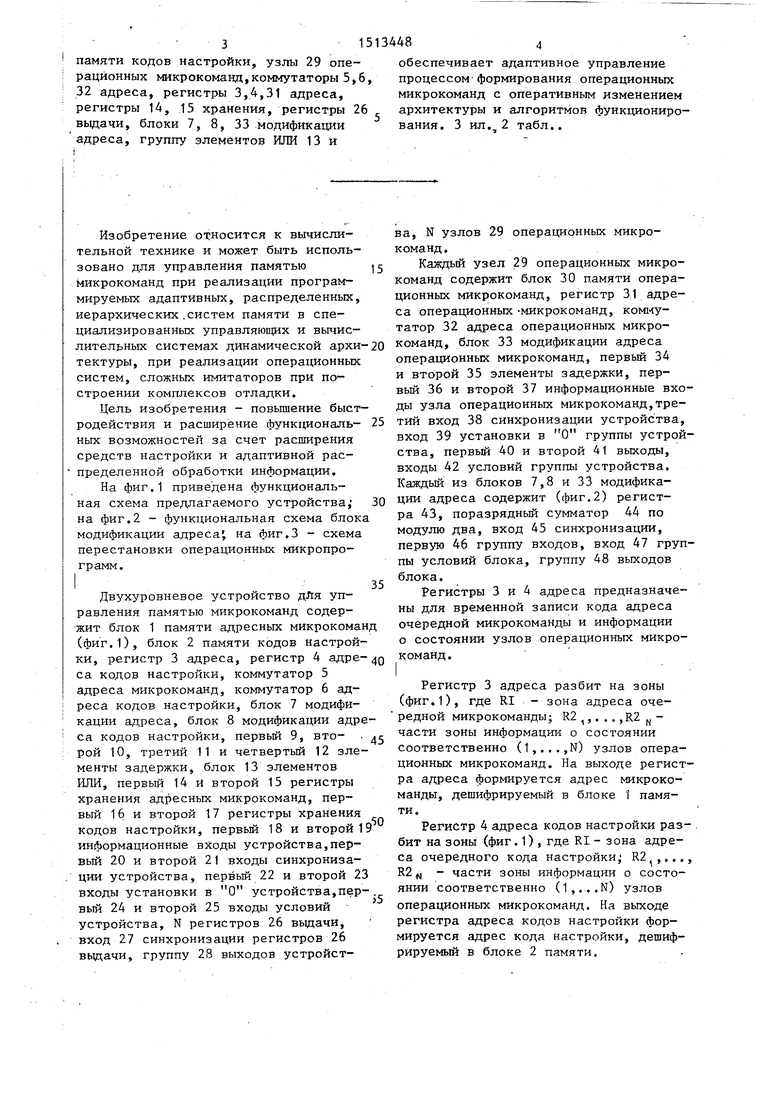

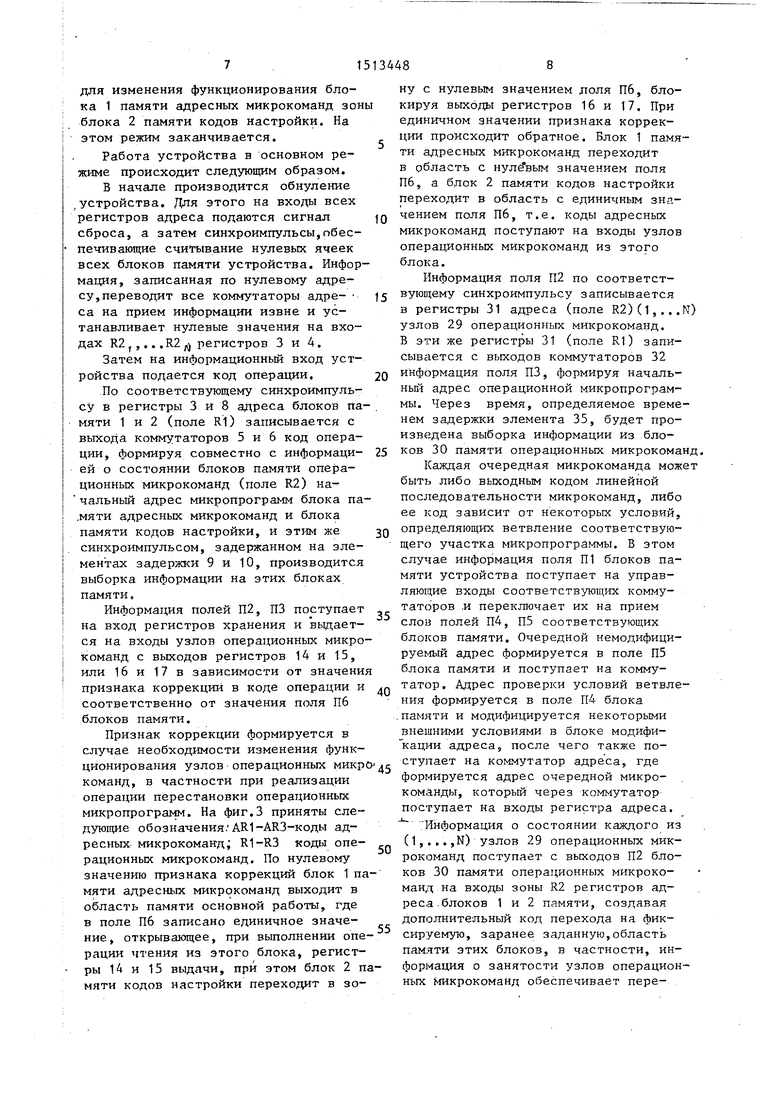

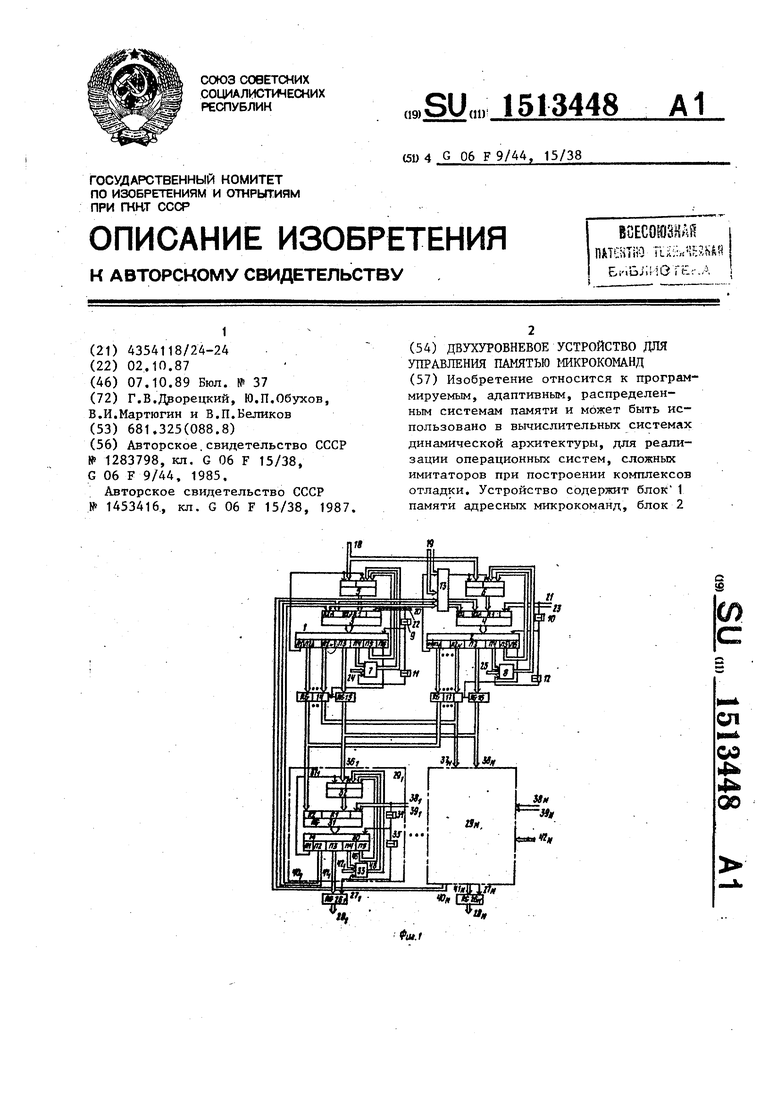

На фиг.1 приведена функциональная схема предлагаемого устройства, на фиг.2 - функциональная схема блока модификации адреса; на фиг.З - схема перестановки операционных микропрограмм.

Двухуровневое устройство дЛя управления памятью микрокоманд содержит блок 1 памяти адресных микрокоман (фиг.1), блок 2 памяти кодов настройки, регистр 3 адреса, регистр 4 адреса кодов настройки, коммутатор 5 адреса микрокоманд, коммутатор 6 адреса кодов настройки, блок 7 модификации адреса, блок 8 модификации адреса кодов настройки, первый 9, вто- . рой 10, третий 11 и четвертый 12 зле- менты задержки, блок 13 элементов ИЛИ, первый 14 и второй 15 регистры хранения адресных микрокоманд, первый 16 и второй 17 регистры хранения кодов настройки, первьй 18 и второй 1 информационные входы устройства,первый 20 и второй 21 входы синхронизации устройства, первый 22 и второй 23 входы установки в О устройства,первый 24 и второй 25 входы условий устройства, N регистров 26 выдачи, вход 27 синхронизации регистров 26 вьщачи, группу 28 выходов устройст

5 0

5

0

5

о

0

на, N узлов 29 операционных микрокоманд .

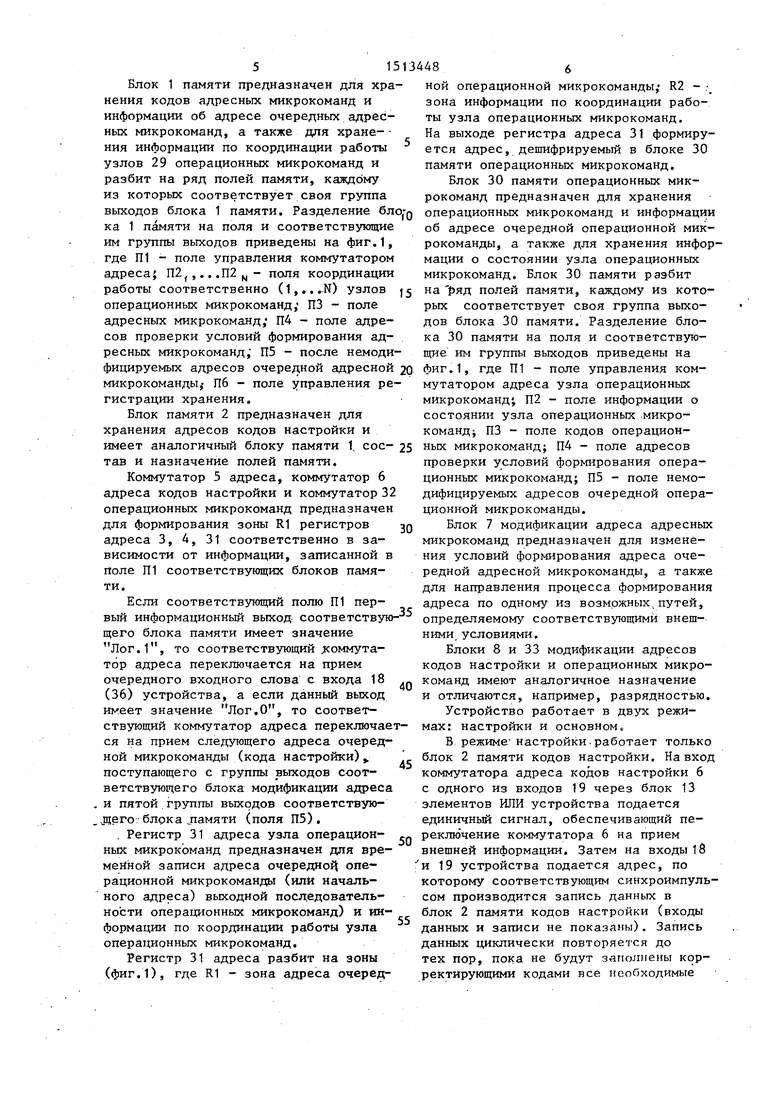

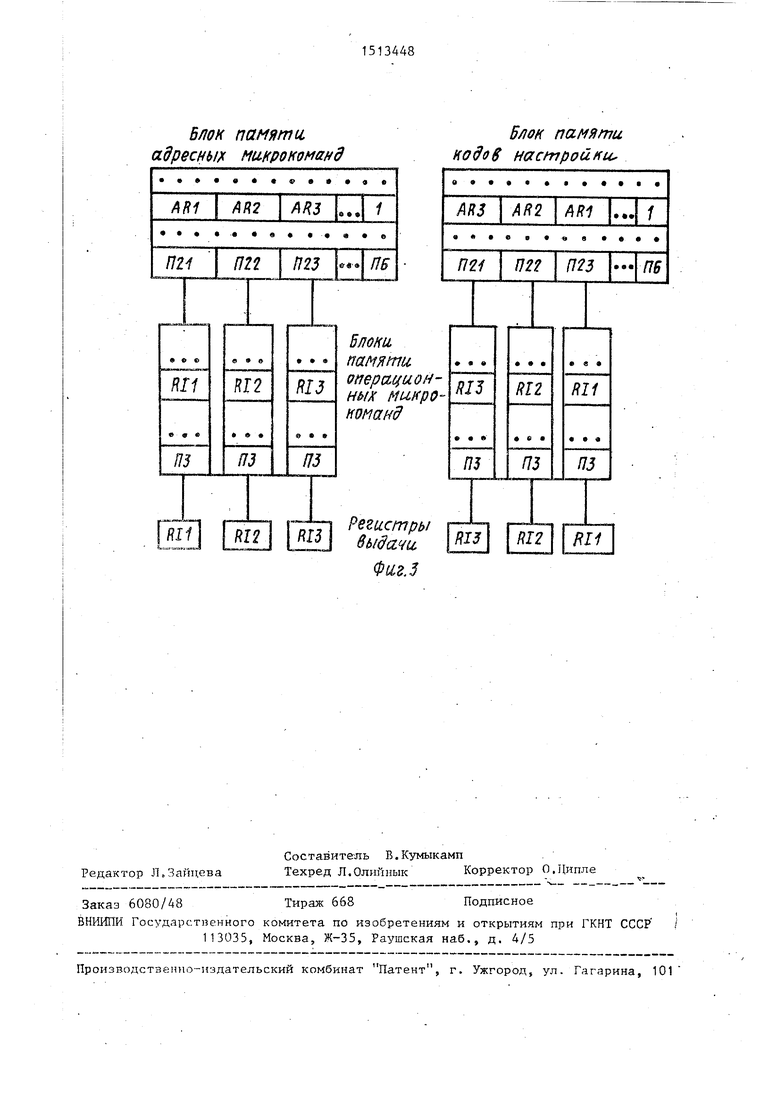

Каждый узел 29 операционных микрокоманд содержит блок 30 памяти операционных микрокоманд, регистр 31 адреса операционных -микрокоманд, KOMi-iy- татор 32 адреса операционных микрокоманд, блок 33 модификации адреса операционных микрокоманд, первый 34 и второй 35 элементы задержки, первый 36 и второй 37 информационные входы узла операционных микрокоманд,третий вход 38 синхронизации устройства, вход 39 установки в О группы устройства, первый 40 и второй 41 выходы, входы 42 условий группы устройства. Каждый из блоков 7,8 и 33 модификации адреса содержит (фиг.2) регистра 43, поразрядный сумматор 44 по модулю два, вход 45 синхронизации, первую 46 группу входов, вход 47 группы условий блока, группу 48 выходов блока.

Регистры 3 и 4 адреса предназначены для временной записи кода адреса очередной микрокоманды и информации о состоянии узлов операционных микрокоманд.

Г. .

Регистр 3 адреса разбит на зоны (фиг,1), где RI - зона адреса оче- редной микрокоманды; R2,,...,R2 - части зоны информации о состоянии соответственно (1,.,.,N) узлов операционных микрокоманд. На выходе регистра адреса формируется адрес микрокоманды, дешифрируемый в блоке 1 памяти.

Регистр 4 адреса кодов настройки раз- . бит на зоны (фиг. 1) , где RI - зона адреса очередного кода настройки; R2,..., R2|j - части зоны информации о состоянии соответственно (1,...N) узлов операционных микрокоманд. На выходе регистра адреса кодов настройки формируется адрес кода настройки, дешифрируемый в блоке 2 памяти.

Блок 1 памяти предназначен для хранения кодов адресных микрокоманд и информации об адресе очередных адрес- ньк микрокоманд, а также для хране- ния информации по координации работы узлов 29 операционных микрокоманд и разбит на ряд полей памяти, каждому из которых соответствует своя группа выходов блока 1 памяти. Разделение бло-д ка 1 памяти на поля и соответствующие им группы выходов приведены на фиг,1, где П1 - поле управления коммутатором адреса; П2,...П2 - поля координации

ной операционной микрокоманды,- R2 - .- зона информации по координации работы узла операционных микрокоманд. На выходе регистра адреса 31 форкгару- ется адрес, дешифрируемый в блоке 30 памяти операционных микрокоманд.

Блок 30 памяти операционных микрокоманд предназначен для хранения операционных микрокоманд и информации об адресе очередной операционной микрокоманды, а также для хранения информации о состоянии узла операционных микрокоманд. Блок 30 памяти разбит

работы соответственно (1,,. .-N) узлов j на ряд полей памяти, каждому из кото- операционных микрокоманд; ПЗ - поле адресных микрокоманд; П4 - поле адресов проверки условий формирования адресных микрокоманд, П5 - после немодирых соответствует своя группа выходов блока 30 памяти. Разделение блока 30 памяти на поля и соответствующие им группы выходов приведены на

фицируемых адресов очередной адресной 20 фиг.1, где П1 - поле управления коммикрокоманды,- П6 - поле управления регистрации хранения.

Блок памяти 2 предназначен для хранения адресов кодов настройки и

мутатором адреса узла операционных микрокоманду П2 - поле информации о состоянии узла операционных микрокоманд j ПЗ - поле кодов операционимеет аналогичный блоку памяти t сое- 25 ных микрокоманд; П4 - поле адресов тав и назначение полей памяти. проверки условий формирования опера- Коммутатор 5 адреса, коммутатор 6 ционных микрокоманд; П5 - поле немо- адреса кодов настройки и коммутатор 32 дифицируемых адресов очередной опера- операционных микрокоманд предназначен

циокной микрокоманды.

30

для формирования зоны R1 регистров адреса 3, 4, 31 соответственно в зависимости от информации, записанной в Поле П1 соответствующих блоков памяти.

Если соответствующий полю П1 первый информационный выход соответствую- щего блока памяти имеет значение Лог.1, то соответствующий .коммутатор адреса переключается на прием очередного входного слова с входа 18 (36) устройства, а если данный выход имеет значение Лог.О, то соответствующий коммутатор адреса переключается на прием следующего адреса очередной микрокоманды (кода настройки) поступающего с группы выходов соответствующего блока модификации адреса

и пятой.группы выходов соответствую..щего, блока .памяти (поля П5) .

. Регистр 31 адреса узла операцион40

45

50

ных микрокоманд предназначен для временной записи адреса очередно операционной микрокоманды (или начального адреса) выходной последовательности операционных микрокоманд) и информации по координации работы узла операционньк микрокоманд.

Регистр 31 адреса разбит на зоны (фиг.1), где R1 - зона адреса очередной операционной микрокоманды,- R2 - .- зона информации по координации работы узла операционных микрокоманд. На выходе регистра адреса 31 форкгару- ется адрес, дешифрируемый в блоке 30 памяти операционных микрокоманд.

Блок 30 памяти операционных микрокоманд предназначен для хранения операционных микрокоманд и информации об адресе очередной операционной микрокоманды, а также для хранения информации о состоянии узла операционных микрокоманд. Блок 30 памяти разбит

на ряд полей памяти, каждому из кото-

рых соответствует своя группа выходов блока 30 памяти. Разделение блока 30 памяти на поля и соответствующие им группы выходов приведены на

мутатором адреса узла операционных микрокоманду П2 - поле информации о состоянии узла операционных микрокоманд j ПЗ - поле кодов операционных микрокоманд; П4 - поле адресов проверки условий формирования опера- ционных микрокоманд; П5 - поле немо- дифицируемых адресов очередной опера-

циокной микрокоманды.

Блок 7 модификации адреса адресных микрокоманд предназначен для изменения условий формирования адреса очередной адресной микрокоманды, а также для направления процесса формирования адреса по одному из возможных путей, определяемому соответствующими внешними условиями.

Блоки 8 и 33 модификации адресов кодов настройки и операционных микрокоманд имеют аналогичное назначение и отличаются, например, разрядностью.

Устройство работает в двух режимах: настройки и основном.

В режиме настройки.работает только блок 2 памяти кодов настройки. На вход коммутатора адреса кодов настройки 6 с одного из входов 19 через блок 13 элементов ИЛИ устройства подается единичный сигнал, обеспечивающий пе- реклю чение коммутатора 6 на прием внешней информации. Затем на входы 18 и 19 устройства подается адрес, по которому соответствующим синхроимпульсом производится запись данных в блок 2 памяти кодов настройки (входы данных и записи не показаны). Запись данных циклически повторяется до тех пор, пока не будут здполиены корректирующими кодами все необходимые

для изменения функционирования блока 1 памяти адресных микрокоманд зон блока 2 памяти кодов настройки. На этом режим заканчивается.

Работа устройства в основном режиме происходит следующим образом.

В начале производится обнуление ,устройства. Лпя этого на входы всех регистров адреса подаются сигнал сброса, а затем синхроимпульсы,обеспечивающие считывание нулевых ячеек всех блоков памяти устройства. Информация, записанная по нулевому адресу, переводит все коммутаторы адре- са на прием информации извне и устанавливает нулевые значения на входах R2,...R2 регистров 3 и 4.

Затем на информационный вход устройства подается код операции.

По соответствующему синхроимпульсу в регистры 3 и 8 адреса блоков па мяти 1 и 2 (поле R1) записывается с выхода коммутаторов 5 и 6 код операции, формируя совместно с информаци- ей о состоянии блоков памяти oneija- ционных микрокоманд (поле R2) на- чальный адрес микропрограмм блока па ,мяти адресных микрокоманд и блока памяти кодов настройки, и этим же синхроимпульсом, задержанном на элементах задержки 9 и 10, производится выборка информации на этих блоках памяти.

Информация полей П2, ПЗ поступает на вход регистров хранения и выдается на входы узлов операционных микрокоманд с выходов регистров 14 и 15, или 16 и 17 в зависимости от значени признака коррекций в коде операции и соответственно от значения поля Пб блоков памяти.

Признак коррекции формируется в случае необходимости изменения функционирования узлов операционных микр команд, в частности при реализации операции перестановки операционных микропрограмм. На фиг.З приняты следующие обозначения. АЕ1-АКЗ-коды адресных микрокоманд; R1-R3 коды one- рационных микрокоманд. По нулевому значению признака коррекций блок 1 памяти адресных микрсэкоманд выходит в область памяти основной работы, где в поле Пб записано единичное значе

ние, открывающее, при выполнении one рации чтения из этого блока, регистры 14 и 15 вьщачи, при этом блок 2 памяти кодов настройки переходит в зо

О

Q

,

5

ну с нулевым значением лоля Пб, блокируя выходы регистров 16 и 17. При единичном значении признака коррекции происходит обратное. Блок 1 памяти адресных микрокоманд переходит в область с нуле вым значением поля Пб, а блок 2 памяти кодов настройки переходит в область с единичным значением поля Пб, т.е. коды адресных микрокоманд поступают на входы узлов операционных микрокоманд из этого блока.

Информация поля П2 по соответствующему синхроимпульсу записывается в регистры 31 адреса (поле R2)(1,...N) узлов 29 операционных микрокоманд. В эти же регистры 31 (поле R1) записывается с выходов коммутаторов 32 информация поля ПЗ, формируя начальный адрес операционной микропрограммы. Через время, определяемое временем задержки элемента 35, будет произведена выборка информации из блоков 30 памяти операционных микрокоманд.

Каждая очередная микрокоманда может быть либо выходным кодом линейной последовательности микрокоманд, либо ее код зависит от некоторых условий, определяющих ветвление соответствующего участка микропрограммы. В этом случае информация поля П1 блоков памяти устройства поступает на управляющие входы соответствующих коммутаторов .и переключает их на прием слон полей П4, П5 соответствующих блоков памяти. Очередной немодифицируемый адрес формируется в поле П5 блока памяти и поступает на коммутатор. Адрес проверки условий ветвления формируется в поле П4 блока ,памяти и модифицируется некоторыми внешними условиями в блоке модифи- кации адреса, после чего также поступает на коммутатор адреса, где формируется адрес очередной микрокоманды, который через коммутатор поступает на входы регистра адреса. Информация о состоянии каждого из (1,...,N) узлов 29 операционных микрокоманд поступает с вьгходов П2 блоков 30 памяти операционных микрокоманд на входы зоны R2 регистров адреса, блоков 1 и 2 памяти, создавая дополнительный код перехода на фиксируемую, заранее заданную,область памяти этих блоков, в частности, информация о занятости узлов операционных микрокоманд обеспечивает переход блоков памяти адресных микроко- манд и настройки в области циклического ожидания сигналов об освобожде- НИИ, блокирующую выдачу информации из этих блоков.

Кода операционньпс микрокоманд с выходов полей ПЗ блоков 30 памяти узлов операционных микрокоманд поступают на входы регистров 26 вьщачи и по соответствующим синхроимпульсам с выходов элементов 35 задержки записываются в них, после чего поступают на выходы устройства.

Блоки 7,8 и 33 модификации адреса работают следующим образом.

На вход группы условий подается параллельный код входных условий и пО синхроимпульсу, подаваемому на вход синхронизации блока,записывается в регистр 43,. через регистр 43 (при наличии единицы в первом разряде первой группы подаваемой на управляющий

Рассмотрим работу устройства в случае возникновения неисправности в отдельных блоках. Факт возникновения неисправности в блоке памяти операционных микрокоманд может быть зафиксирован при выходе этого блока из рабочей зоны путем задания изменения значений поля адресов проверки условий П4 при выходе из этой зоны. Данное изменение выводит блок памяти операг. ционных микрокоманд в область памяти, содержащую в поле П2 код неисправности, который вьшодит блоки памяти ад- pecfhbix микрокоманд или кодов настройки в область памяти, содержащую процедуры, адаптирующие устройство к возникшей неисправности.

Наличие блока 2 памяти кодов настройки с соответствующими связями обеспечивает дополнительные возможности повышения достоверности функционирования устройства.

15

20

.Зафиксированная узлами 29 операвход регистра) подаются на вход пораз- з ц„онньпс микрокоманд.неисправность

блока 1 памяти адресных микрокоманд выводит узлы 44 на участок памяти, в поле 112 которого записан код, выводящий (через зону R2 регистра адреса) блок 1 памяти адресных микрокоманд в зону, блокирующую (с использованием поля Пб) вьщачу информации из этого блока, а блок 2 памяти к:одов

30

рядного сумматора 44 по модулю два. Одновременно параллельный код входных условий подается на второй вход поразрядного сумматора 44. На третий вход поразрядного сумматора 44 подается адрес проверки условий ветвления с первой группы входов блока модификации адреса.

Работа поразрядного сумматора 44 описывается следующим уравнением (уравнение описьгаает операции над i-м 5 разрядом входных слов) (Ai V Bi) 0 Ci . Di,

настройки в зону, разрешающую (поле П6) вьщачу этого блока 2 информации, дублирующей информацию блока 1 памяти адресных микрокоманд. Тем самым производится подмена одного блока памяти другим.

где Ai - i-й разряд слова, хранящего- Bi

Ci Di - V

®

СЯ в запоминающем регистре; i-й разряд слова входных условий, подаваемого непосредственно на сумматор 34; 1-й разряд адреса проверки условий ветвленияj i-й разряд выходного слова блока модификации адресаj операция ЛОГИЧЕСКОЕ ИЛИ; операция СЛОЖЕНИЕ ПО МОДУЛЮ ДВА.

Таким образом, блок модификации ад .реса реализует функцию модификации адреса как в зависимости от содержания текущего кода входных условий, так и от содержимого заранее.поденно- го в произвольный момент времени кода входных условий, зафиксированного по соответствующей команде в запоминающем регистре.

10

51344810

Рассмотрим работу устройства в случае возникновения неисправности в отдельных блоках. Факт возникновения неисправности в блоке памяти операционных микрокоманд может быть зафиксирован при выходе этого блока из рабочей зоны путем задания изменения значений поля адресов проверки условий П4 при выходе из этой зоны. Данное изменение выводит блок памяти операг. ционных микрокоманд в область памяти, содержащую в поле П2 код неисправности, который вьшодит блоки памяти ад- pecfhbix микрокоманд или кодов настройки в область памяти, содержащую процедуры, адаптирующие устройство к возникшей неисправности.

Наличие блока 2 памяти кодов настройки с соответствующими связями обеспечивает дополнительные возможности повышения достоверности функционирования устройства.

15

20

30

настройки в зону, разрешающую (поле П6) вьщачу этого блока 2 информации, дублирующей информацию блока 1 памяти адресных микрокоманд. Тем самым производится подмена одного блока памяти другим.

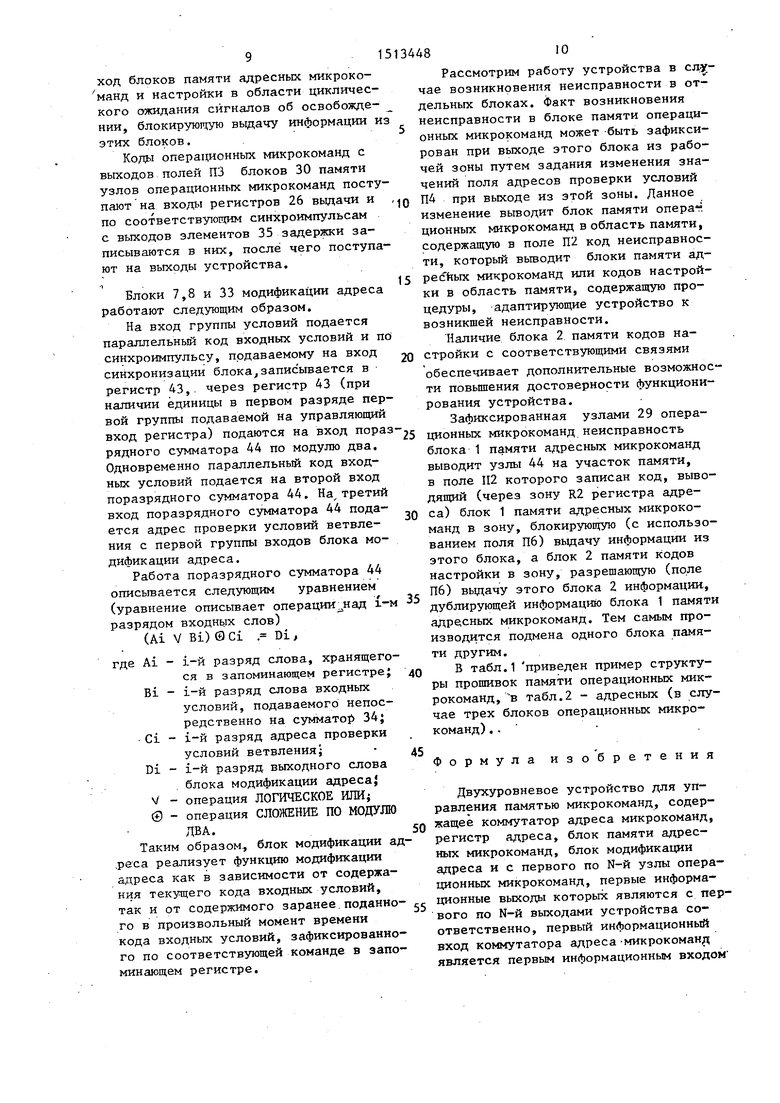

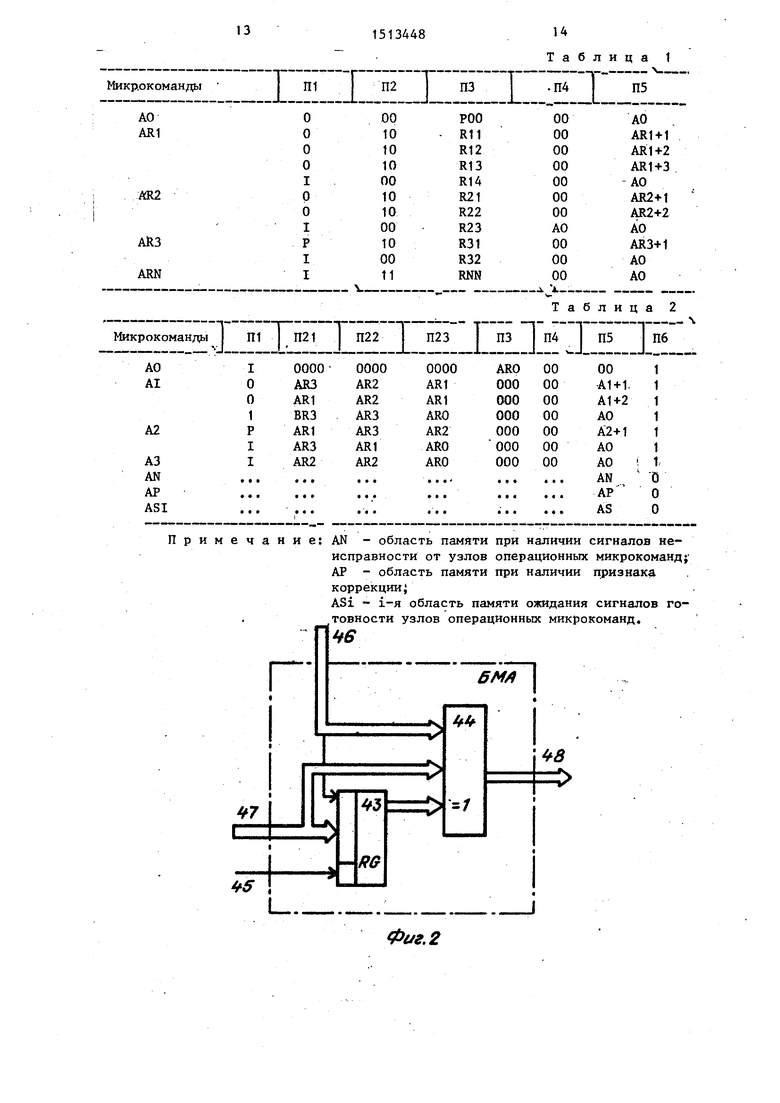

В табл.1 приведен пример структуры прошивок памяти операционных микрокоманд, в табл.2 - адресных (в случае трех блоков операционных микрокоманд) . .

Формула изобретения

Двухуровневое устройство для управления памятью микрокоманд, содер- жащее коммутатор адреса микрокоманд, регистр адреса, блок памяти адресных микрокоманд, блок модификации адреса и с первого по N-й узлы операционных микрокоманд, первые информационные выходы которых являются с первого по N-й выходами устройства соответственно, первый информационный вход коммутатора адреса микрокоман( является первым информационным входом

11

устройства, выход коммутатора адреса микрокоманд соединен с первым информационным входом регистра адреса, выход которого соединен с адресным входом блока адресных микроко манд, выходы первого, пятого и четвертого полей которого соединены с управляющим входом и разрядами первой группы второго информационного входа коммутатора адреса микрокоманд и первым информационным входом блока модификации адреса, второй информационный вход и разрядь вьпсодов которого соединены соответственно с первым входом условий устройства и с разрядами второй группы второго информационного входа коммутатора адреса микрокоманд, вторые информационные выходы с первого по N-й узлов операционных микрокоманд соединены с второго по (Ы+1)-й информационными входами регистра адреса соответственно, входы условий и установки в О с первого по N-й узлов операционных микрокоманд образуют группы входов условий и установки в О устройства .соответственно, входы синхронизации регистра адреса, блока памяти адресньк микрокоманд, блока модификации ад-зо первым и вторым информационными вхо35

реса и с первого по N-й узлов операционных микрокоманд являются соответ- СТВУЮЩ1-1МИ входами группы входов синхронизации устройства, вход установки в О регистра адреса является первьш одношченныМ входом устройства, о тли- чающееся тем, что, с целью по- вьшения быстродействия и расширения функциональных возможностей за счет расширения средств настройки и адаптив д ной распределенной обработки информации, в него введены коммутатор адреса кодов настройки, регистр адреса кодов настройки, блок памяти кодов настройки, блок модификации адреса кодов на- ,;- стройки, блок элементов ИЛИ, первый и второй регистры хранения адресных микрокоманд и первый и второй регистры хранения, кодов настройки, первый ин- формациопньвЧ вход коммутатора адреса 50 кодов настройки соединен с первым информационным входом устройства,выход коммутатора адреса кодов настройки

513448 2

соединен с первым информационньгм входом регистра адреса кодов настройки, вход установки в О и выход которого соединены с вторым входом установки в О устройства и с адресным входом блока памяти кодов настрой| :и, выходы с первого по пятое полей которого соединены с первым входом, блока элемен Q тов ИЛИ, информационными входами первого и второго регистров хранения кодов настройки, первым информационным входом блока модификации адреса кодов настройки и разрядами первой группы

5 второго информационного входа коммутатора адреса кодов настройки, разряды второй группы второго информационного входа которого соединены с разрядами выхода блока модификации адреса кодов

20 настройки, второй информационный

вход которого является вторым входом условий устройства, выходы второго и третьего полей блока памяти адресных микрокоманд соединены с информацион25 ными входами первого и второго регистров хранения адресных микрокоманд соответственно, выходы которых.соединены с выходами первого и второго регистров хранения кодов настройки и

дами всех- узлов операционных микрокоманд соответственно, вторые информационные выходы которых соединены с входами первой группы блока элементов .ИЛИ, выход и выходы группы которого соединены с упр1авляющим входом коммутатора адреса кодов настройки и с второго по (Н+1)-й информационными входами регистра адреса кодов настройг ки соответственно, входы второй группы и второй вход, блока элементов 11ПИ являются вторым информационным входом и входом управления режимом устройства соответственно, входы синхронизации регистра адреса кодов настройки, блока памяти кодов настройки, блока модификации адреса кодов настройки,перых и вторых регистров хранения адресных микрокоманд и кодов настройки являются с оответствующими Входами группы входов синхронизации устройства.

Примечание:

AN - область памяти при наличии сигналов неисправности от узлов операционных микрокоманд; АР - область памяти при наличии признака коррекцииi

ASi - i-я область памяти ожидания сигналов готовности узлов операционных микрокоманд.

Таблица 1

Фиг. 2

Влон памяти, адреснш микрокоманд

Блок памяп7и кодов на стройки

Фав.З

| Устройство для трансляции кодов с одного языка на другой | 1985 |

|

SU1283798A1 |

| Устройство для преобразования кодов с одного языка на другие | 1987 |

|

SU1453416A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-10-02—Подача