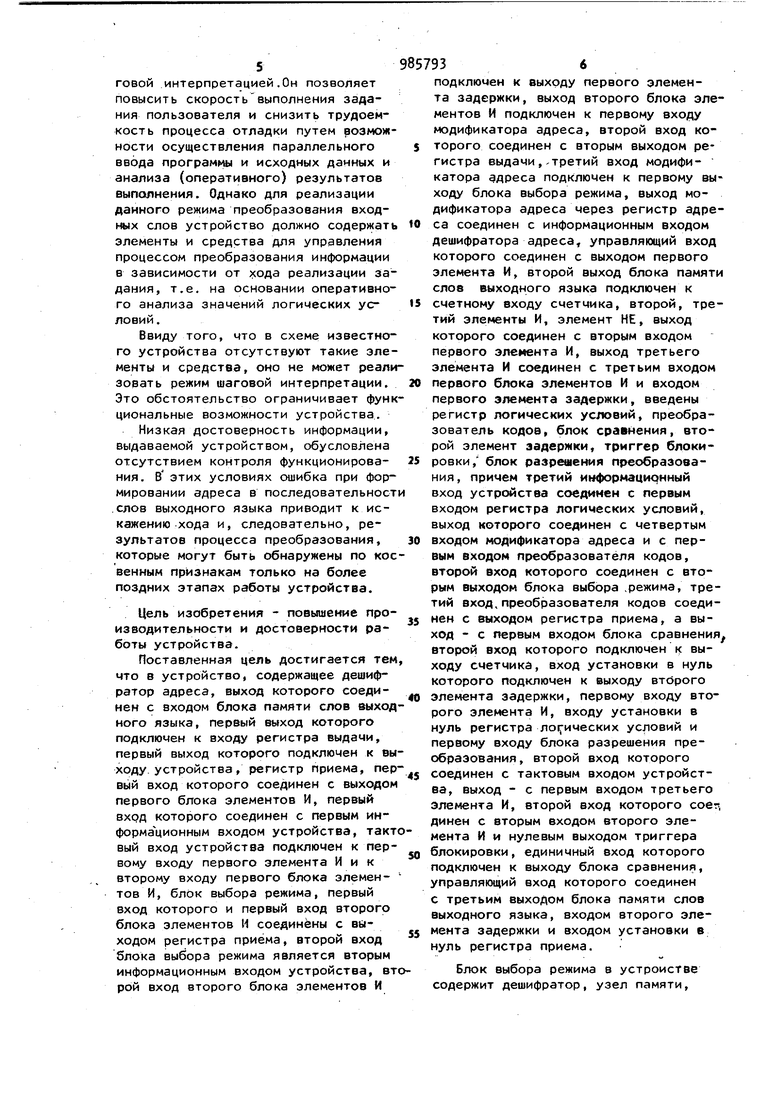

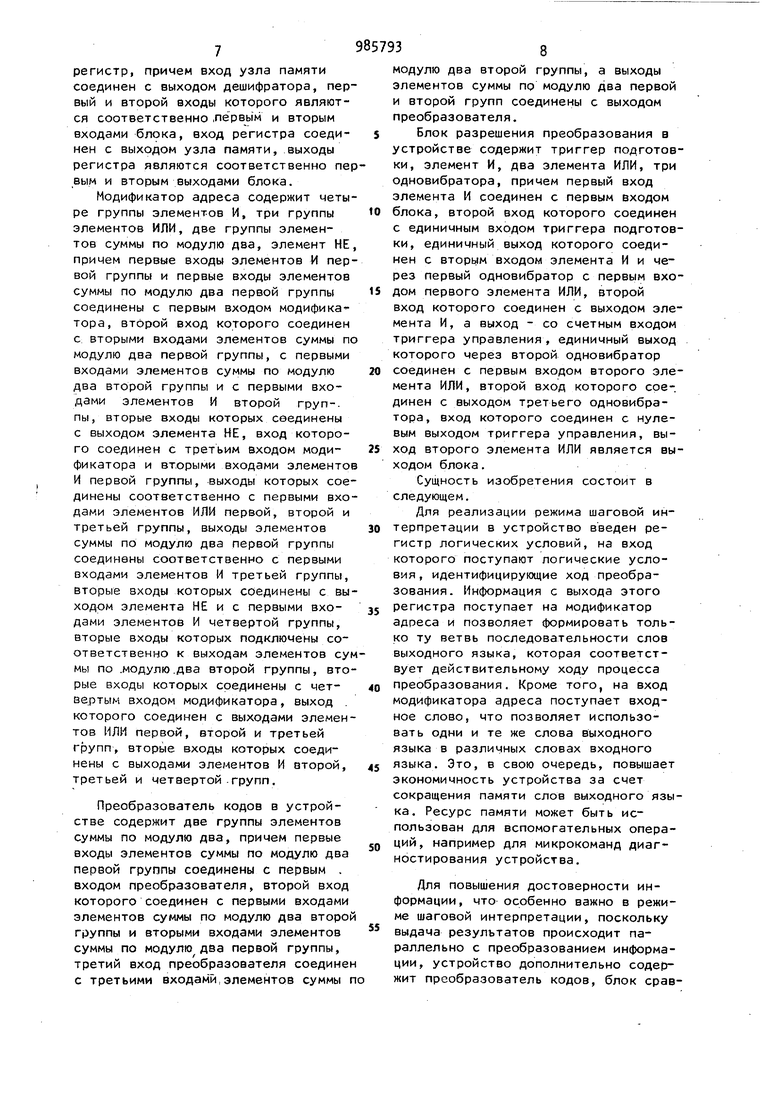

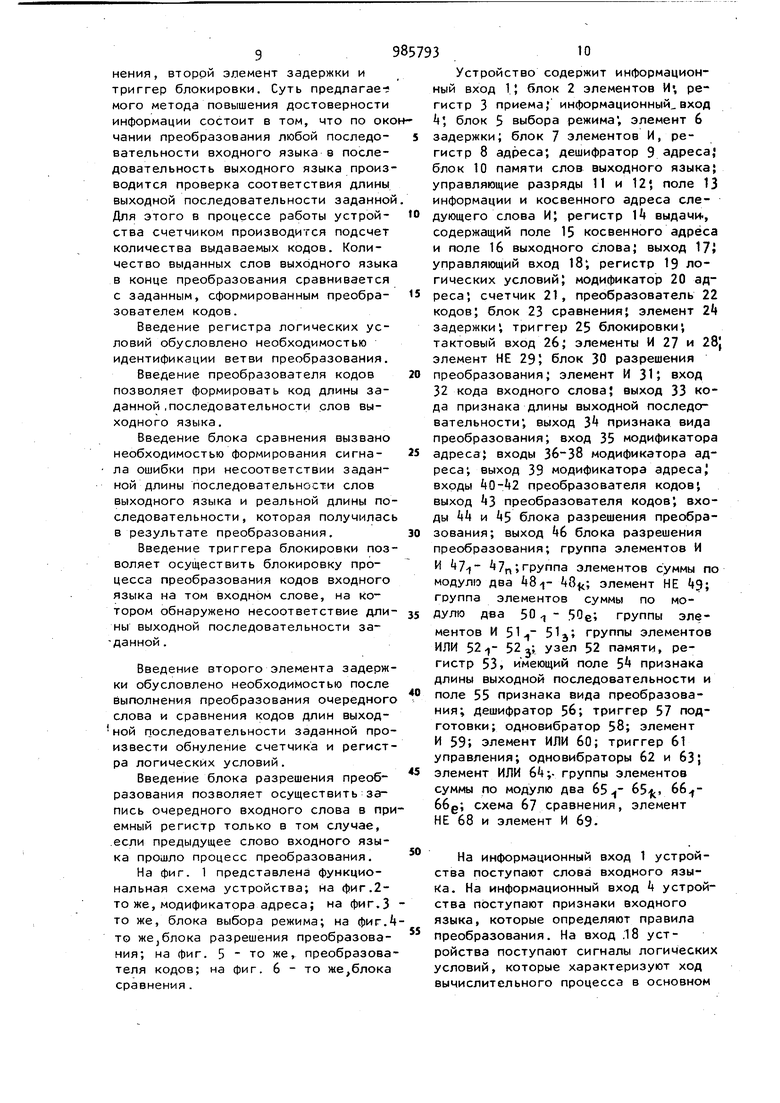

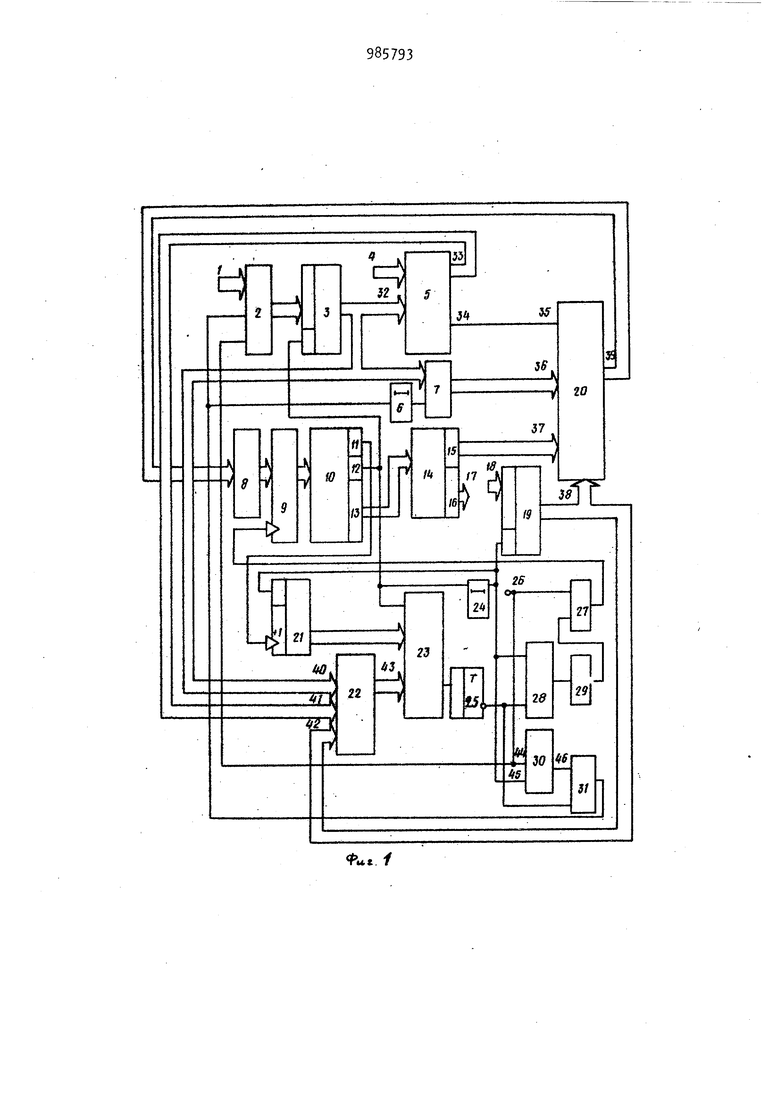

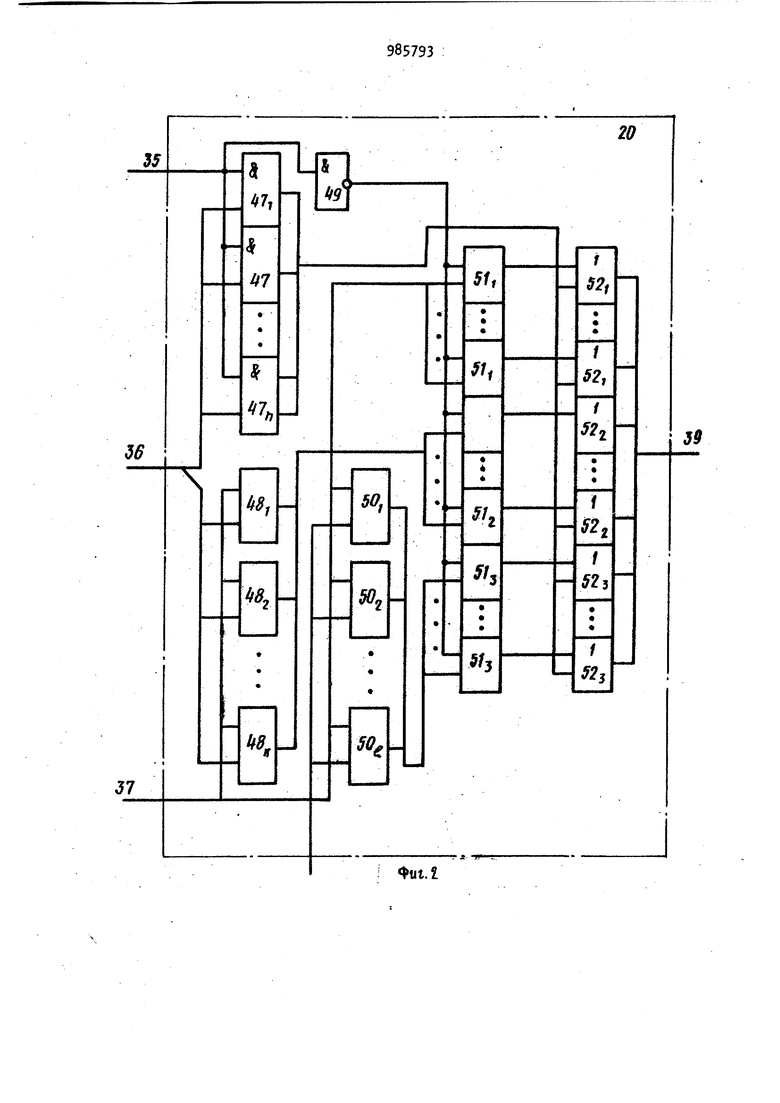

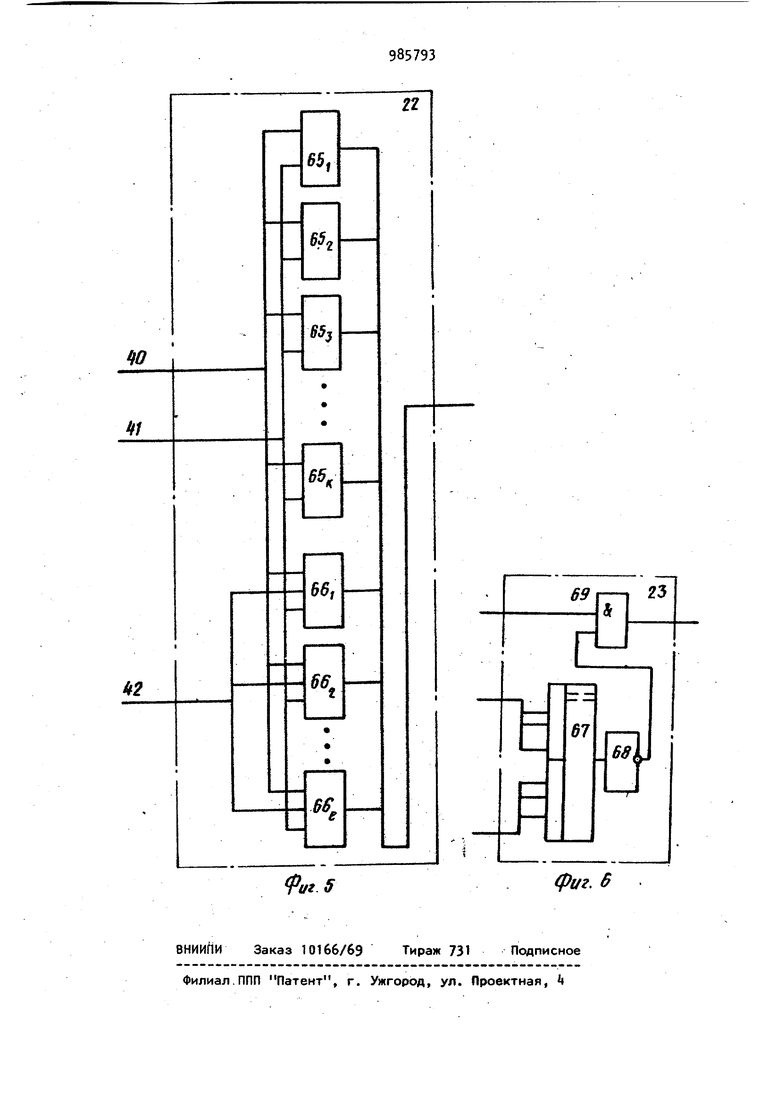

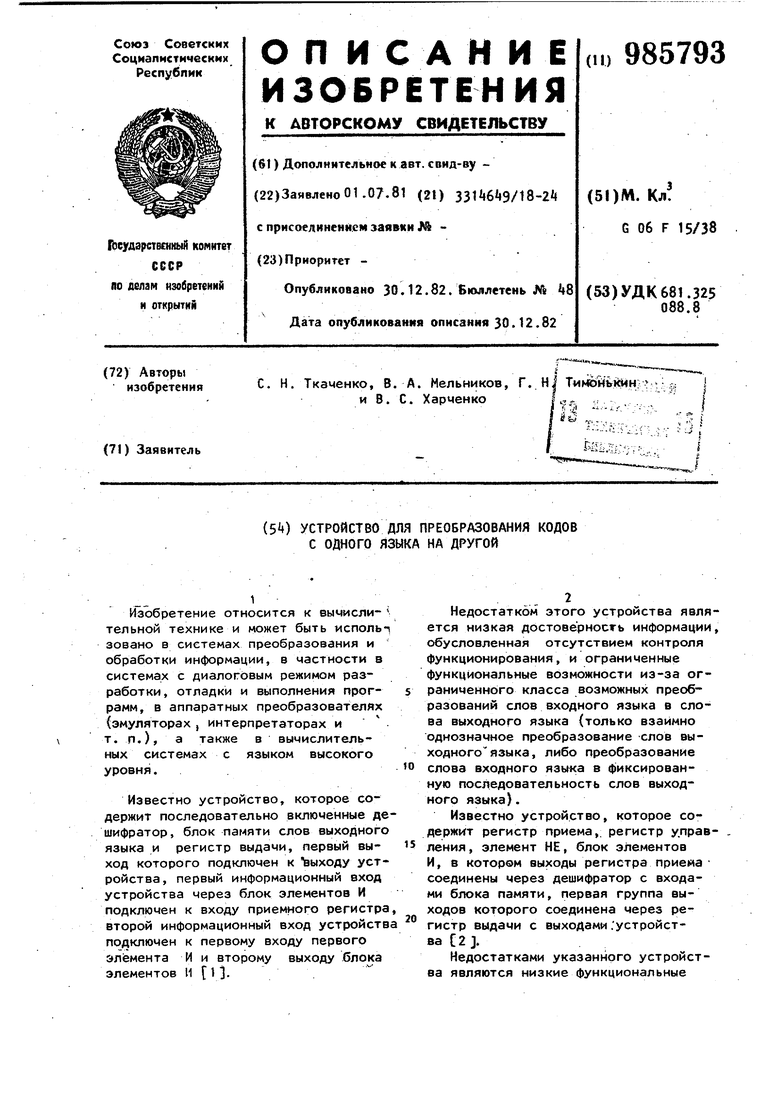

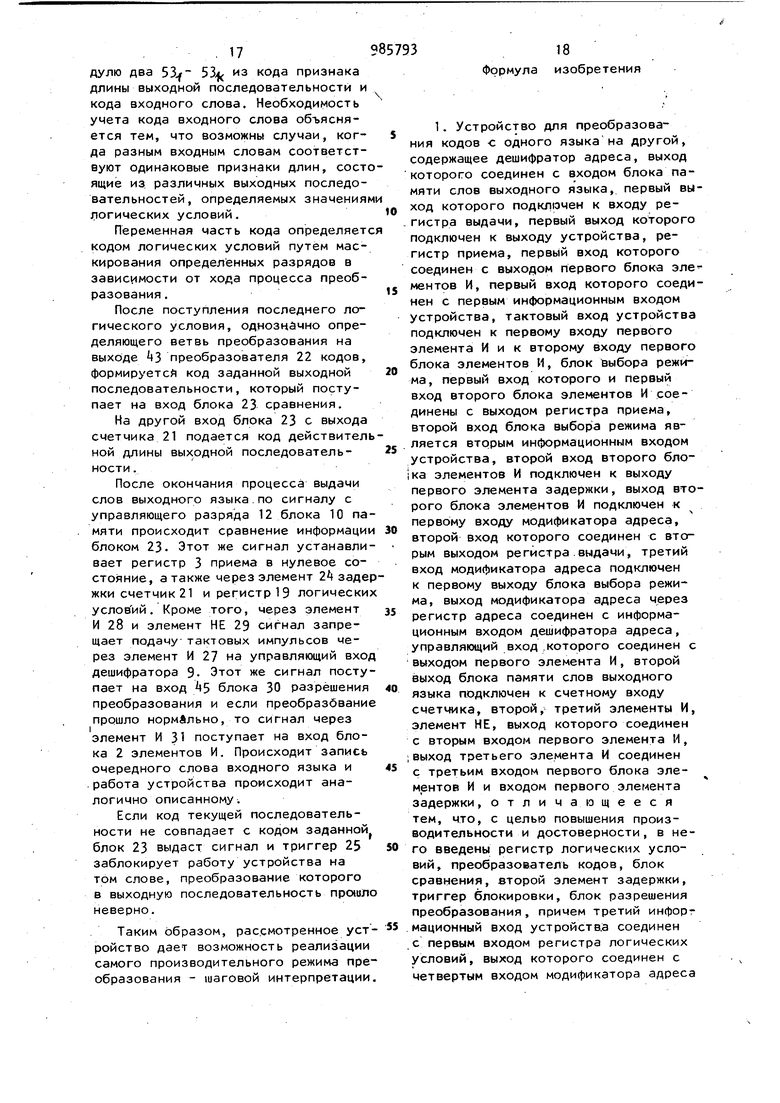

Изобретение относится к вычислительной технике и может быть испольп зовано в системах преобразования и обработки информации, в частности в системах с диалоговым режимом разработки, отладки и выполнения программ, в аппаратных преобразователях (эмуляторах , интерпретаторах и V т. п.), а также а вычислительных системах с языком высокого уровня. Известно устройство, которое содержит последовательно включенные де шифратор, блок памяти слов выходного языка и регистр выдачи, первый выход которого подключен к выходу устройства , первый информационный вход устройства через блок элементов И подключен к входу приемного регистра второй информационный вход устройств подключен к первому входу первого элемента И и второму выходу блока элементов И f1. Недостатком этого устройства является низкая достоверность информации, обусловленная отсутствием контроля функционирования, и ограниченные функциональные возможности из-за ограниченного класса возможных преобразований слов входного языка в слова выходного языка (только взаимно однозначное преобразование слов выходного языка , либо преобразование слова входного языка в фиксированную последовательность слов выходного языка). Известно устройство, которое содержит регистр приема, регистр управления , элемент НЕ, блок элементов И, в котором выходы регистра приема соединены через дешифратор с входами блока памяти, первая группа выходов которого соединена через регистр выдачи с выходами .устройства С 2 J. Недостатками указанного устройства являются низкие функциональные возможности устройства, обусловленные ограниченным классом преобразований слов входного языка, большим временем преобразования, а также отсутствием контроля правильности преобразования 8 последовательность кодов выходного языка. Кроме того, устройству присуща и низкая экономичность, обусловленная большим объемом блока памяти слов выходного языка, в котором для каждого входного слова записана.соответствующая последовательность слов на выходном языке, Поэтому если одно и тоже слово (оператор) выходного языка присутствует в нескольких последовательностях, эквивалентных различным входным словам, то данное слово (оператор ) должно быть записано в блоке памяти несколько раз.Эт приводит к большой избыточности информации в блоке памяти и как следствие - к снижению его экономичности. I Наиболее близким к предлагаемому по технической сущности является уст ройство, содержащее дешифратор, выхо которого соединен с входом блока памяти, первый выход которого подключен к входу регистра выдачи, первый выход которого подключен к выход устройства, регистр приема, первый вход которого соединен с выходом пер вого блока элементов И, первые входы которого соединены с первым информационным входом устройства, тактовый вход которого подключен к первому входу первого элемента И и к вторым входам элементов И первого блока, блок выбора режима, первый вход которого и первый вход второго блока элементов И соединены с выходом приемного регистра, второй вход-блока выбора режима является вторым инфор мационным входом устройства, второй вход второго блока элементов И подключен к выходу первого элемента за держки , выход второго блока элементов И подключен к первому входу модификатора адреса, второй вход кото рого соединен с вторым выходом регистра выдачи, третий вход модификатора адреса соединен с первым вых дом блока выбора режима, выход модификатора адреса через регистр адреса соединен с входом дешифратора адреса, управляющий вход которого соединен с выходом первого элемента 3 И, второй выход блока памяти слов выходного языка подключен к счетному входу счетчика, выход третьего элемента И подключен к третьему входу первого блока элементов И и к входам первого элемента задержки, выход элемента НЕ соединен с вторым входом первого элемента И ГЗ. Недостатками указанного устройства являются узкие функциональные возможности,не позволяющие достигнуть требуемой производительности, и низкая достоверность информации. Ограниченность функциональных возможностей объясняется следующим. Устройство для преобразования кодов может использоваться в вычислительных системах 1ВС ) в режимах компиляции, интерпретации и эмуляции, В режиме компиляции осуществляется ввод текста на исходном (входном ) языке в устройство хранения информации системы обработки информации. После ввода текста производится его преобразование в некоторый объективный (внутренний )код системы с помощью программных (например, как в указанном устройстве ) средств. Далее выполняется синтаксический контроль текста в соответствии с правилами реализуемых языков. Выполнение программы, заданной текстом, возможно только после полного окончания процесса трансляции. Наиболее перспективным в современных системах с разделением времени является режим интерпретации, который позволяет оперативно выполнять задания в системе, В режиме интерпретации параллельно с вводом информации в систему осуществляется анализ текста иа уровне законченных синтаксических конструкций, например операторов входного языка. Однако исходный (входной ) текст может быть запущен на выполнение только после окончания его преобразования целиком в текст на выходном языке. Очевидным недостатком описанных режимов трансляции, компиляции и интерпретации является большое время выполнения задания. Однако весьма существенного повышения эффективности производительности системы можно достичь, если ввод, анализ и реализацию входного текса проводить параллельно (одновременно). Этот режим называется шаговой интерпретацией.Он позволяет повысить скоростьвыполнения задания пользователя и снизить трудоемкость процесса отладки путем возможности осуществления параллельного ввода программы и исходных данных и анализа (оперативного) результатов выполнения. Однако для реализации данного режима преобразования входных слов устройство должно содержать элементы и средства для управления процессом преобразования информации в зависимости от хода реализации задания, т.е. на основании оперативного анализа значений логических условий. Ввиду того, что в схеме известного устройства отсутствуют такие элементы и средства, оно не может реали зовать режим шаговой интерпретации. Это обстоятельство ограничивает функ циональные возможности устройства. Низкая достоверность информации, выдаваемой устройством, обусловлена отсутствием контроля функционирования. в этих условиях ошибка при формировании адреса в последовательност слов выходного языка приводит к искажению хода и, следовательно, результатов процесса преобразования, которые могут быть обнаружены по кос венным признакам только на более поздних этапах работы устройства. Цель изобретения - повышение производительности и достоверности работы устройства. Поставленная цель достигается тем что в устройство, содержащее дешифратор адреса, выход которого соединей с входом блока памяти слов выход ного языка, первый выход которого подключен к входу регистра выдачи, первый выход которого подключен к вы ходу устройства , регистр приема, пер вый вход которого соединен с выходом первого блока элементов И, первый вход которого соединен с первым информационным входом устройства, такт вый вход устройства подключен к первому входу первого элемента И и к второму входу первого блока элементов И, блок выбора режима, первый вход которого и первый вход второго блока элементов И соединены с выходом регистра приема, второй вход блока выбора режима является вторым информационным входом устройства, вт рой вход второго блока элементов И подключен к выходу первого элемента задержки, выход второго блока элементов И подключен к первому входу модификатора адреса, второй вход которого соединен с вторым выходом регистра выдачи,-третий вход модификатора адреса подключен к первому выходу блока выбора режима, выход модификатора адреса через регистр адреса соединен с информационным входом дешифратора адреса, управляющий вход которого соединен с выходом первого элемента И, второй выход блока памяти слое выходного языка подключен к счетному входу счетчика, второй, третий элементы И, элемент НЕ, выход которого соединен с вторым входом первого элемента И, выход третьего элемента И соединен с третьим входом первого блока элементов И и входом первого элемента задержки, введены регистр логических условий, преобразователь кодов, блок сравнения, второй элемент задержки, триггер блокировки, блок разрояения преобразования, причем третий имформационный вход устройства соединен с первым входом регистра логических условий, выход которого соединен с четвертым входом модификатора адреса и с первым входом преобразователя кодов, второй вход которого соединен с вторым выходом блока выбора .режима, третий вход,преобразователя кодов соединен с выходом регистра приема, а выход - с первым входом блока сравнения второй вход которого подключен к выходу счетчика, вход установки в нуль которого подключен к выходу второго элемента задержки, первому входу второго элемента И, входу установки в нуль регистра ло1;-ических условий и первому входу блока разрешения преобразования, второй вход которого соединен с тактовым входом устройства, выход - с первым входом третьего элемента И, второй вход которого сое, динен с вторым входом второго элемента И и нулевым выходом триггера блокировки, единичный вход которого подключен к выходу блока сравнения, управляющий вход которого соединен с третьим выходом блока памяти слое выходного языка, входом второго элемента задержки и входом установки в нуль регистра приема. Блок выбора режима в устройстве содержит дешифратор, узел памяти. регистр, причем вход узла памяти соединен с выходом дешифратора, первый и второй входы которого являются соответственно лервым и вторым входами блока, вход регистра соединен с выходом узла памяти, выходы регистра являются соответственно пер вым и вторым выходами блока. Модификатор адреса содержит четыре группы элементов И, три группы элементов ИЛИ, две группы элементов суммы по модулю два, элемент НЕ примем первые входы элементов И пер вой группы и первые входы элементов суммы по модулю два первой группы соединены с первым входом модификатора, второй вход которого соединен с вторыми входами элементов суммы по модулю два первой группы, с первыми входами элементов суммы по модулю два второй группы и с первыми входами элементов И второй груп-. пы, вторые входы которых соединены с выходом элемента НЕ, вход которого соединен с третьим входом модификатора и вторыми входами элементов И первой группы, выходы которых соединены соответственно с первыми вхо дами элементов ИЛИ первой, второй и третьей группы, выходы элементов суммы по модулю два первой группы соединены соответственно с первыми входами элементов И третьей группы, вторые входы которых соединены с вы ход-ом элемента НЕ и с первыми входами элементов И четвертой группы, вторые входы которых подключены соответственно к выходам элементов су мы по .модулю .два второй группы, вто рые входы которых соединены с четвертым входом модификатора, выход . которого соединен с выходами элемен тов ИЛИ первой, второй и третьей групп, вторые входы которых соединены с выходами элементов И второй, третьей и четвертой групп. Преобразователь кодов в устройстве содержит две группы элементов суммы по модулю два, причем первые входы элементов суммы по модулю два первой группы соединены с первым . входом преобразователя, второй вход которого соединен с первыми входами элементов суммы по модулю два второ группы и вторыми входами элементов суммы по модулю два первой группы, третий вход преобразователя соедине с третьими входами,элементов суммы модулю два второй группы, а выходы элементов суммы по модулю два первой и второй групп соединены с выходом преобразователя. Блок разрешения преобразования в устройстве содержит триггер подготовки, элемент И, два элемента ИЛИ, три одновибратора, причем первый вход элемента И соединен с первым входом блока, второй вход которого соединен с единичным входом триггера подготовки, единичный выход которого соединен с вторым входом элемента И и через первый одновибратор с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход - со счетным входом триггера управления, единичный выход которого через второй одновибратор соединен с первым входом второго элемента ИЛИ, второй вход которого сое-, динен с выходом третьего одновибратора, вход которого соединен с нулевым выходом триггера управления, выход второго элемента ИЛИ является выходом блока. Сущность изобретения состоит в следующем. Для реализации режима шаговой интерпретации в устройство введен регистр логических условий, на вход которого поступают логические условия , идентифицирующие ход преобразования. Информация с выхода этого регистра поступает на модификатор адреса и позволяет формировать только ту ветвь последовательности слов выходного языка, которая соответствует действительному ходу процесса преобразования. Кроме того, на вход модификатора адреса поступает входное слово, что позволяет использовать одни и те же слова выходного языка в различных словах входного языка. Это, в свою очередь, повышает экономичность устройства за счет сокращения памяти слов выходного языка. Ресурс памяти может быть использован для вспомогательных операций, например для микрокоманд диагностирования устройства. Для повышения достоверности информации, что особенно важно в режиме шаговой интерпретации, поскольку выдача результатов происходит параллельно с преобразованием информации, устройство дополнительно содержит преобразователь кодов, блок сравнения, второй элемент задержки и триггер блокировки. Суть предлагаемого метода повышения достоверности информации состоит в том, что по око чании преобразования любой последевательности входного языка в последовательность выходного языка произ водится проверка соответствия длины выходной последовательности заданно Для этого в процессе работы устройства счетчиком производится подсчет количества выдаваемых кодов. Количество выданных слов выходного язык в конце преобразования сравнивается с заданным, сформированным преобразователем кодов. Введение регистра логических условий обусловлено необходимостью идентификации ветви преобразования. Введение преобразователя кодов позволяет формировать код длины заданной .последовательности слов выходного языка. Введение блока сравнения вызвано необходимостью формирования сигнала ошибки при несоответствии заданной длины последовательности слов выходного языка и реальной длины по следовательности, которая получилас в результате преобразования. Введение триггера блокировки поз воляет осуществить блокировку процесса преобразования кодов входного языка на том входном слове, на котором обнаружено несоответствие дли ны выходной последовательности за-данной. Введение второго элемента задерж ки обусловлено необходимостью после выполнения преобразования очередного слова и сравнения кодов длин выходной последовательности заданной произвести обнуление счетчика и регист ра логических условий. Введение блока разрешения преобразования позволяет осуществить - запись очередного входного слова в при емный регистр только в том случае, .если предыдущее слово входного языка прошло процесс преобразования. На фиг. 1 представлена функциональная схема устройства; на фиг.2то же, модификатора адреса; на фиг.З то же, блока выбора режима; на фиг. то же,блока разрешения преобразования; на фиг. 5 - то же, преобразова теля кодов; на фиг. 6 - то же,блока сравнения. 310 Устройство содержит информационный вход 1; блок 2 элементов И регистр 3 приема; информационный,вход блок 5 выбора режима; элемент 6 задержки; блок 7 элементов И, регистр 8 адреса; дешифратор 9 адреса, блок 10 памяти слов выходного языка; управляющие разряды 11 и 12, поле 13 информации и косвенного адреса следующего слова И; регистр k выдачи., содержащий поле 15 косвенного адреса и поле 16 выходного с:лова; выход 17i управляющий вход 18; регистр 19 логических условий; модификатор 20 адреса; счетчик 21, преобразователь 22 кодов; блок 23 сравнения; элемент 2 задержкиi триггер 25 блокировки; тактовый вход 26; элементы И 27 и 28J элемент НЕ 295 блок 30 разрешения преобразования; элемент И 3U вход 32 кода входного слова; выход 33 кода признака длины выходной последо вательности; выход З признака вида преобразования; вход 35 модификатора адреса; входы 36-38 модификатора адреса; выход 39 модификатора адреса; входы преобразователя кодов; выход 3 преобразователя кодов; входы 4 и 5 блока разрешения преобразования; выход () блока разрешения преобразования; группа элементов И И 47-1- 7п; группа элементов суммы по модулю два элемент НЕ «tj; группа элементов суммы по модулю два 50 - 50е; группы элементов И 51 группы элементов ИЛИ 52 j; узел 52 памяти, регистр 53. имеющий поле 5 признака длины выходной последовательности и поле 55 признака вида преобразования; дешифратор 5б; триггер 57 подготовки; одновибратор 58; элемент И 59 элемент ИЛИ 60; триггер 61 управления; одновибраторы б2 и 63| элемент ИЛИ 6 ; группы элементов суммы по модулю два б5, 66 66g; схема 67 сравнения, элемент НЕ 68 и элемент И б9. На информационный вход 1 устройства поступают слова входного языка. На информационный вход устройства поступают признаки входного языка, которые определяют правила преобразования. На вход .18 устройства поступают сигналы логических условий, которые характеризуют ход вычислительного процесса в основном режиме работы устройства - режиме шаговой интерпретации. Работа устройства возможна в трех режимах. Первый режим преобразования - ре жим, когда длина входной последовательности слов совпадает с длиной выходной последовательности, а каж,дое слово входного языка соответствует определенному слову выходного языка режим взаимно однозначного преобразования ) или так называемый режим один к одному. Второй режим преобразования - ре жим, когда длина входной последовательности слов меньше длины выходно последовательности или, так называемый режим один в несколько. Третий режим преобразования - ре жим, когда длина входной последовательности слов больше длины выходно последовательности или, так называемый режим несколько в один. Третий режим преобразования,може быть сведен ко второму, так как некоторые слова выходного языка могут быть пустыми. По этой причине рассмотрим работу устройства в указанных двух первых режимах: режиме вза имно однозначного преобразования (О-режим) и режиме отсутствия взаим но однозначного преобразования Нрежим). Работа устройства в 0-режиме. В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии. Первый тактовый импульс с входа 26 устройства поступает на вход 4 блока 30 разрешения преобразования и перебрасывает триггер 57 в единич ное состояние. Сигнал с единичного выхода триггера 57 через одновибрат 58 и элемент ИЛИ 60 перебрасывает триггер 61 в единичное состояние, а также подготавливается элемент И 59 для выдачи управляющих сигналов на преобразование очередных слов входного языка после окончания преобразования предыдущих. Сигнал с единичного выхода триггера б1 через одновибратор б2 и эле мент ИЛИ 6 с выхода +6 блока 30 по ступает на вход блока 2 элементов И и разрешает по тактовому импульсу, поступающему на вход блока 2, осуществить запись слова входного языка с информационного входа 1 на регистр 3 приема. 3.12 До окончания процесса преобразования первого входного слова блок . 2 элементов И закрыт для прохождения очередных входных слов, так как триггер.61 остается в единичном состоянии и на выходе элемента ИЛИ б отсутствует управляющий сигнал на запись в регистр 3 приема очередного входного слова с входа 1. С выхода регистра 3 приема входное слово поступает на дешифратор 5б блока 5 выбора режима. На основании информации о входном языке, поступающей с информационного входа k устройства, дешифратор 5б выбирает в узле 52 памяти код, содержащий признак (характеристику ) длины последовательности выходного языка и признак вида преобразования, которые записываются соответственно в поля и 55 регистра 53Признак длины выходной последовательности поступает на вход 1 преобразователя 22 кодов, где участвует в выработке заданной длины выходной последовательности в зависимости от кода входного слова, поступающего на вход ЦО преобразователя 22 и кода преобразования данного входного слова в зависимости от логических условий, поступающих на вход i)2) . Признак вида преобразования входного слова (и;)управляет модификатором 20 адреса О, если реализуется вдаимно однозначное преобразование слова входного языка в слово выходного языка, т.е. реализуется процесс u преобразования один к одному, 1, если реализован процесс преобразования один в несколько или несколько в .один. Если осуществляется взаимно однозначное преобразование входного слова, т.е. реализуется процесс преобразования один к одному, адрес выходного слова однозначно определяется кодом входного слова. В этом случае признак вида преобразования, имеющий единичное значение поступает на вход 35 модификатора адреса 20, на вход 36 которого поступает код входного слова, котррый однозначно определяет адрес слова выходного языка. Код адреса слова выходногоязыка сформированный на группе элементов И . - 7„1 поступает через группы элементов ИЛИ 52j на выход 39 модификатора адреса 20. Одновременно с этим разрешающий сигнал на взаимно однозначное преобразование входного слова через элемент НЕ kS запрещает модификацию адреса от косвенного адреса следующе го выходного слова, кода логических условий и кода входного слова. Элемент 6 задержки необходим для задержки первого тактового импульса на время , необходимое для записивxo ного слова в регистр 3 приема и.частичного преобразования информации в блоке 5 выбора режима. Код адреса выходного слова с выхода 39 модификатора 20: поступает на регистр адреса и через дешифратор 9 адреса производит опрос блока 10 па мяти слов выходного языка. Так как.процесс преобразования не закончен, то сигнал с выхода элемента И 28 через элемент НЕ 29 разрешит прохождение тактовых импульсов на управляющий вход дешифратора Э-с тактового входа 2б устройства через элемент И 27. По очередному импульсу происходит считывание дешифратором 9 адреса сло ва из блока 10 памяти слов выходного языка по адресу сформированному, моди фикатором 20 адреса, на основе инфор мации кода входного слова и признака вида преобразования. С выхода 11 блока памяти управляю щий сигнал увеличивает на единицу содержимое счетчика 21, а код-с выхода 17 запи-сывается. в регистр 1 выдачи, в поле 15 которого записывается в регистр 1A выдачи, в поле 15 которого записывается косвенный адрес следующего выходного слова (для рассматриваемого режима работы он будет, нулевым ), а в поле 16 - слово выходного языка. Слово выходного язы ка с поля 16 «поступает на выход 17 устройства. После выдачй слова выходного языка с поля 13 блока 10 памяти выдается сигнал окончания процесса преобразования слова входного языка. Дангный сигнал,поступая на управляющий вход блока 23 ср-авнения, разрешает осуществить сравнение заданной вы:)од ной последовательности., сформированной на преобразователе 22 кодов, с выданной выходной последовательностью, длина которой подсчитана счетчиком 21. Если код, записанный в счетчике 21, не совпадает с кодом, сформированным на преобразователе 22 кодов, то-блок 23 вь1дает сигнал, который перебросит триггер 25 блокировки в единичное состояние. Кроме.того, сигнал с выхода полч 13 блока 10 установит в нулевое состояние регистр 3 приема, а через второй элемент 2t задержки - счетчик 21. На выходе элемента И 28 появляется сигнал, который через элемент НЕ 29 запрещает подачу тактовых импульсов на управляющий вход дешифратора 9 адреса для опроса блока 10 памяти. Одновременно с этим сигнал окончания процесса преобразования входного слова поступает на вход 5 блока 30 . разрешения прербравования. На выходе элемента И 59 появляется сигнал, который через элемент ИЛИ 60 перебросит триггер 61 в противоположное состояние (нулевое). Сигнал с нулевого выхода триггера 61 через одновибратор 62 и элемент ИЛИ 64 разрешит запись очередного слова входного языка с информационного входа 1 на регистр .3 приема. Далее процесс взаимно однозначного преобразования слов входного языка продолжается аналогично описанному. Заканчивается процесс преобразования последовательности слов входного языка в выходную последовательность путем окончания поступления слов входного языка на информационный вход 1 устройства, признаков преобразования на информационный вход Ц и тактовых импульсов на тактовый вход 2б устройства. Работа устройства в Н-режиме. Если записанное в регистр 3 приема входное слово требуется преобраг зовать в некоторую последовательность слов выходного языка, то в поле 5 регистра 53 записывается значение признака длины последовательности выходного язык. В поле 55 формируется признак вида преобразования {в данном случае w 0) . . Первое слово входного языка, поступившее через второй блок 7 элементов И, определяет адрес первого ело- 15ва выходного языка на группах элементов И 51.j 513, который по. разрешающему сигналу с выхода элемента НЕ 49 и через группы элементов ИЛИ 52 - 525 подается на выход 39 модификатора 20 адреса, а с него на вход регистра 8 адреса, . Дешифратор 9 адреса осуществляет выборки слова из блока 10 памяти ана логично рассмотренному для 0-режима С блока 10 памяти в поля регистра выдачи поступает информация. В поле 15 записывается косвенный адрес следующего слова выходного языка, а в поле 16 самб слово, которое поступает на вход 17 устройства. По мере выдачи слов выходного язы ка на выход 17 устройства, содержимое счетчика 21 увеличивается за счет подачи на его счетный вход сиг нала с выхода поля 11 блока 10 памяти. С поступлением кода косвенного адреса следующего входного слова на вход 37 произойдет модификация кода адреса. В общем случае код адреса состои из постоянной и переменной части. Постоянная часть кода образуется некоторыми разрядами кода косвенного адреса и формируется на группе элементов И 5 . Переменная часть кода адреса образуется путем маскирования определенных разрядов кода косвенного адреса кодами входного слова на группе элементов суммы по модулю два Ц8 и кодами логических условий на группе элементов суммы по модулю два 50 е- Переменная часть кода адреса формируется, таким образом,, на группах элементов.И соответствен но 512 513 Так как устройство функционирует в режиме шаговой интерпретации, то при формировании адреса очередного слова выходного языка учитываются сигналы значений логических условий которые хранятся в регистре 13 и поступают на вход 37 модификатора 2 адреса. Это позволяет в случае ветвления алгоритма оперативно формировать неальтернативные ветви алгоритма, а именно ту, которая должна реализоваться в данном случае. Таким образом, в процессе преобразования косвенный код адреса следующего выходного слова модифи циру3ется на основе информации о входном слове и значениях логических условий . Слова выходного языка подаются на выход 17 устройства. С этого выхода информация может записываться во внешний блок памяти , откуда будет производиться считывание во время реализации алгоритма (.программы). В режиме шаговой интерпретации в промежуточном хранении информации необходимости нет, поэтому непосредственно с выхода 17 .выходные последовательности могут подаваться на объект управления, ответные сигналы которого поступают через вход 18 на регистр 19 логических условий. Некоторые слова выходного языка могут быть и пустыми, если признак длины входной последовательности превосходит признак (атрибут) длины выходной последовательности, т.е. в случае преобразования несколько в один. Такая ситуация возможна, например при ретрансляции языков. Устройство функционирует до окончания выдачи текущей выходной последовательности . В момент завершения последовательности выдается последнее слово выходного языка с выхода поля 13 блока 10 памяти, которое поступает в регистр 1й выдачи. С выхода 17 выдается последнее слово данной выходной, последовательности, а в свободном поле 15 записан нулевой код косвенного адреса. В процессе выдачи с регистра It слов выходного языка в зависимости от поступающих логических условий с регистра 19, поступающих на вход k2 преобразователя 22 кодов, происходит модификация кода признака длины выходной последовательности. Модификация кода длины выходной последовательности происходит при идентификации ветви преобразования. Код длины выходной последовательности определяется кодом выходного слова, поступающего на вход tO, кодом признака длины выходной последовательности, поступающего на вход 1 и кодом логических условий, поступающих на вход k2 преобразователя 22 кодов. При этом код длины выходной последовательности состоит из постоянной и переменной частей. Постоянная часть кода формируется на группе элементов суммы по модулю два 53 из кода признака длины выходной последовательности и кода входного слова. Необходимость учета кода входного слова объясняется тем, что возможны случаи, когда разным входным словам соответствуют одинаковые признаки длин, сост ящие из. различных выходных последовательностей, определяемых значения логических условий. Переменная часть кода определяет кодом логических условий путем маскирования определенных разрядов в зависимости от хода процесса преобразования, После поступления последнего логического условия, однозначно определяющего ветвь преобразования на выходе tS преобразователя 22 кодов, формируете код заданной выходной последовательности, который поступает на вход блока 23 сравнения. На другой вход блока 23 с выхода счетчика 21 подается код действител ной длины выходной последовательности. После окончания процесса выдачи слов выходного языка.по сигналу с управляющего разряда 12 блока 10 па мяти происходит сравнение информации блоком 23. Этот же сигнал устанавли вает регистр 3 приема в нулевое состояние, а также через элемент 24 заде жки счетчик 21 и регистр 19 логически условий. Кроме того, через элемент И 28 и элемент НЕ 29 сигнал запрещает подачу тактовых импульсов через элемент И 27 на управляющий вход дешифратора 9- Этот же сигнал поступает на вход kS блока 30 разрешения преобразования и если преобразование прошло нормально, то сигнал через элемент И 31 поступает на вход блока 2 элементов И. Происходит запись очередного слова входного языка и .работа устройства происходит аналогично описанному. Если код текущей последовательности не совпадает с кодом заданной блок 23 выдаст сигнал и триггер 25 заблокирует работу устройства на том слове, преобразование которого в выходную последовательность прошло неверно. Таким образом, рассмотренное устройство дает возможность реализации самого производительного режима преобразования - шаговой интерпретации 3 18 изобретения Формула 1. Устройство для преобразования кодов с одного языка на другой, содержащее дешифратор адреса, выход которого соединен с входом блока памяти слов выходного языка, первый выход которого подключен к входу регистра выдачи, первый выход которого подключен к выходу устройства, регистр приема, первый вход которого соединен с выходом первого блока элвментов И, первый вход которого соединен с первым информационным входом устройства, тактовый вход устройства подключен к первому входу первого элемента И и к второму входу первого блока элементов И, блок выбора режима, первый вход которого и первый вход второго блока элементов И соединены с выходом регистра приема, второй вход блока выбора режима является вторым информационным входом устройства, второй вход второго блока элементов И подключен к выходу первого элемента задержки, выход второго блока элементов И подключен к первому входу модификатора адреса, второй вход которого соединен с втсш рым выходом регистра.выдачи, третий вход модификатора адреса подключен к первому выходу блока выбора режима, выход модификатора адреса через регистр адреса соединен с информационным входом дешифратора адреса, управляющий вход .которого соединен с выходом первого элемента И, второй выход блока памяти слов выходного языка подключен к счетному входу счетчика, второй, третий элементы И, элемент НЕ, выход которого соединен с вторым входом первого элемента И, выход третьего элемента И соединен с третьим входом первого блока элементов И и входом первого элемента задержки, отличающееся тем, что, с целью повышения производительности и достоверности, в него введены регистр логических условий, преобразователь кодов, блок сравнения, второй элемент задержки, триггер блокировки, блок разрешения преобразования, причем третий инфорг мационный вход устройства соединен с первым входом регистра логических условий, выход которого соединен с четвертым входом модификатора адреса 19 и с первым входом преобразователя кодов, второй вход которого соединен с вторым выходом блока выбора режима третий вход преобразователя кодов соединен с выходом регистра прие.ма, а выход- с первым входом блока срав нения , второй вход которого подключен к выходу сметчика, вход установки в нуль которого подключен к выходу второго элемента задержки, пер-. вому входу второго элемента И, входу установки в нуль регистра логических условий и первому входу блока разрешения преобразования, второй вход которого соединен с тактовым входом устройства, выход - с первым входом третьего элемента И, второй вход которого соединей с вторым входом второго элемента И и нулевым выходом триггера блокировки, единичный вход которого подключен к выходу блока сравнения, управляющий вход которого соединен с третьим выходом блока памяти слов выходного языка, входом второго элемента задержки и входом установки в нуль регистра приема. 2, Устройство по П.1, о т л и чающееся тем, что блоквыбора режима содержит дешифратор, узе памяти, регистр, причем вход узла памяти соединен с выходом дешифрато ра , первый и второй входы которого являются соответственно первым и вто рым входами блока, вход регистра со динен с выходом узла памяти, выходы регистра являются соответственно пе вым и вторым выходами блэка. 3. Устройство по П.1, о т л и чающееся тем, что модификатор адреса содержит четыре группы элементов И, три- группы элементов ИЛИ, две группы элементов суммы по модулю два, элемент НЕ, причем первые входы элементов И первой группы и первые входы элементов суммы по модулю два первой группы соединены с первым входом модификатора, второй вход которого соединен с вторыми входами элементов ,суммы по модулю два первой группы, с первыми входами элементов суммы по модулю два вт рой группы и с первыми входами элементов И второй группы, вторые вход которых соединены с выходом элемента НЕ, вход которого соединен с третьим входом модификатора и вторыми входами элементов И первой гру .пы, выходы которых соединены соот3ветственно с первыми входами элементов ИЛИ первой, второй и третьей групп, выходы элементов суммы по модулю два первой группы соединены соответственно с первыми входами эле ментов И третьей группы, вторые входы которых соединены с выходом элемента НЕ и с первыми вход.ами элементов И четвертой группы, вторые входы которых подключены соответственно к выходам элементов суммы по модулю два второй группы, вторые входы которых соединены с четвертым входом модификатора, выход которого соединен с выходами элементов ИЛИ первой, второй и третьей групп, вторые входы которых соединены с выходами элементов И второй, третьей и четвертой групп. А. Устройство по П.1, о т л и чающееся тем, что преобразователь кодов содержит две группы элементов суммы по модулю ва, причем первые входы элементов суммы по моду людна первой группы соединены с. первым входом преобразователя, второй вход которого соединен с первыми входами элементов суммы по модулю два второй группы и вторыми входами эл,ементов суммы по .модулю два первой группы, третий вход преобразователя соединен с третьими входами элементов суммы по модулю два первой группы и вторыми входами элементов суммы по модулю два второй группы, а выходы элементов суммы по модулю два первой и, второй групп соединены с выходом преобразователя. 5. Устройство по П.1, о т л и чающееся тем, что блок разрешения преобразования содержит триггер подготовки, элемент И, два элемента ИЛИ, три одновибратора, причем первый вход элемента И соединен с первым входом блока, второй вход которого срединен с единичным входом триггера подготовки, единичный выход которого соединен с вторым входом элемента И и через первый одновибратор с первым входом первого элемента ИЛИ, Второй вход которого соединен с выходом элемента И, а аыходсо счетным входом триггера управления , единичный выход которого через второй одновибратор соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего одновибратора, вход которого соединен с нулевым выходом триг21 98579322

гера управления-, выход второго эле-,2. Авторское свидетельство СССР

мента ИЛИ является выходом блока.;N 6665i5, кл. G 06 F 15/38, 79Источники информации,

принятые во внимание при экспертизе3. Авторское свидетельство СССР

1. Авторское свидетельство СССР$ по заявке If 2835iOVl8-2«,

ff 631931, кл. G 06 F 15/38, 1976,кл. G 06 F 15/38, 1979 (прототип;.

у

Sff

J4

X

J.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кодов с одного языка на другой | 1983 |

|

SU1136183A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для трансляции кодов с одного языка на другой | 1985 |

|

SU1283798A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для аппаратурной трансляции языков программирования | 1985 |

|

SU1270766A1 |

| Устройство для преобразования языков | 1983 |

|

SU1111176A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1137481A2 |

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

| Устройство для преобразования кодов с одного языка на другой | 1984 |

|

SU1238104A1 |

Ю

8

9

LJ

321

Щ гУ

5

8

n

/

)

J3T

/6

/

24

27

ГЙ

291

25

0

4

t/6

30

«ff

/

rfe

58

451

tpyf.S

62

fy€

г

6Ц

ft 53 Я

.

Авторы

Даты

1982-12-30—Публикация

1981-07-01—Подача