ных слов, второй выход генератора тактовых импульсов соединен с вторы входом второго элемента И и с вторым входом четвертого элемента И, первый выход генератора тактовых импульсов соединен с вторым входом третьего элемента И, выход которого соединен с входом записи запоминающего блока настройки, выход второго элемента И соединен с синхронизирующим входом регистра вьщачи, единичный выход триггера пуска соединен с входом обращения запоминающего блока настройки, выход четвертого элемента И соединен с входом пересчетного блока, информационньй выход которого соединен с первым информационным входом второго коммутатора, выход второго коммутатора соединен с адресным входом запоминающего блока настройки, выход которого соединен с входом дешифратора настройки, выход дешифратора }шстройки соединен с разрешающим входом блока коммутации, выходы которого соединены с соответствующими информционными входами регистра выдачи, управляющий выход пересчетного блока соединен с входом установки в О триггера настройки, вход настройки устройства соединен с информационным входом запоминающего блока настройки, выход адреса настройки блока памяти соединен с вторым информационным входом второго коммутатора, выходы адресов слогов выходных слов блока памяти соединены с адресными входами соответствующих блоков памяти слогов- выходных слов, выходы блоков памяти слогов выходных слов соединены соответственно с информационными входами блока коммутации, приче пересчетньп блок содержит одновибратор, элемент И и счетчик, выходы разрядов которого подключены к информационному выходу блока и к входам элемента И, выход которого соединен ;С входом одновибратора, выход которого подключен к установочному входу счетчика и к управляющему выходу блока, счетньп вход счетчика является входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кодов с одного языка на другой | 1984 |

|

SU1238104A1 |

| Устройство для преобразования кодов с одного языка на другой | 1983 |

|

SU1136183A1 |

| Устройство для формирования периодических функций | 1987 |

|

SU1441391A1 |

| Устройство для аппаратурной трансляции языков программирования | 1985 |

|

SU1270766A1 |

| Устройство для трансляции кодов с одного языка на другой | 1985 |

|

SU1283798A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

УСТРОЙСТВО ДЛЯ АЛПАРАТУРНОЙ ТРАНСЛЯЦИИ, содержащее блок памяти, регистр адреса, мультиплексор логических условий, первьп коммутатор, регистр выдачи, триггер пуска, триггер настройки, дешифратор настройки, генератор тактовых импульсов, первьм, второй, третий и четвертьй элементы И, причем единичный выходтриггера пуска соединен с входом генератора тактовых импульсов, первый вьосод которого соединен с первым входом первого элемента И, выход , первого элемента И соединен с .синхронизирующим входом регистра адреса, выходы разрядов которого соединены с адресным входом блока памяти, выходы немодифицируемых разрядов адреса и выход модифицируемого разряда адреса блока памяти соединены соответ ственно с входами немодифицируемых разрядов адреса первого информационного входа первого коммутатора и с первым информационным входом мультиплексора логических условий, выход которого соединен с входом модифицируемого разряда адреса первого информационного входа первого коммутатора, выход первого коммутатора соединен с информационным входом регистра адреса, выход кода логических условий блока памяти соединен с управляющим входом мультиплексора логических условий, вход логических условий устройства соеди-г нен с вторым информационным входом мультиплексора логических условий, вход слова устройства соединен с вторым информационным входом первого коммутатора, выход конца преобразования входного слова регистра выдачи соединен с разрешакнцим входом первого коммутатора, вькод конца работы регистра выдачи соединен с входом установки в О триггера пус(Л ка, выходы разрядов регистра выдачи . являются выходами устройства, от-, личающееся тем, что, с целью повьшения гибкости базиса слов выходного языка путем выстраивания в требуемом порядке отдельных слогов выходного слова, в него введены бло4 4iii ки памяти слогов выходных слов, запоминакщий блок настройки, пересчетньй блок, второй коммутатор, блок коммутации, причем вход пуска уст00 ройства соединен с входом установки в 1 триггера пуска, а вход настройки устройства соедииен с входом установки в 1 триггера настройки, единичный выход которого соединен с вторым входом первого элемента И, с первыми входами второго, третьего и четвертого элементов И и с разрешающим входом второго коммутатора, нулевой выход триггера настройки соединен с входами обращения блока памяти и блоков памяти слогов выход

Изобретение относится к вычислительной технике и может быть использовано в системах непосредственной реализации языков высокого уровня, а также в системах с диалоговым режимом разработки, отладки и выполнения программ, в аппаратных трансляторах (эмуляторах, интерпретаторах),

Известно устройство, которое содержит регистр приема, регистр выдачи, блок памяти, блок элементов И,причем выходы регистра приема соединены через дешифратор с входами блока памяти, первая группа выходов которого соединена через регистр выдачи с выходом устройства

Недостатками указанного устройств являются его низкие функциональные возможности, обусловленные ограниченным,- классом преобразований слов выходного языка и большим временем преобразования,

Кроме того, устройству присуща и низкая экономичность, обусловленная

большим объемом блока памяти слов выходного языка, в котором длд каждого входного слова записана соответствующая последовательность слов на выходном яйыке. Поэтому если одно и то же слово (оператор) выходного языка присутствует в нескольких последовательностях, эквивалентных различным входным словам, то данное слово, должно быть записано в блоке памяти несколько раз. Это приводит к большой избыточности информации в блоке памяти и, как следствие, к снижению его экономичности.

Известно устройство для преобразования (трансляции) кодов с одного языка на другой, содержащее блок памяти, дешифратор, регистр выдачи, модификатор адреса, блок выбора режима, блок разрешения преобразования, блок элементов И, ИЛИ, элементы задержки, регистр логических условий, преобразователь кодов, блок сравнения, триггер блокировки, счетчик з . 3 Недостатком такого устройства является его сложность, а также невозможность расширения списка выход ных слов при расширении макрофункций системы. Введение новых входных слов языка приводит к необходимости изменения блока памяти устройства, что снижает его гибкость и, следовательно, область применения. Наиболее близким ло технической сущности к изобретению является уст ройство для аппаратурной трансляции содержащее элементы И, блок памяти, информационные входы которого соединены с первой группой информационных входов устройства, а вход записи подключен к первому входу синхроимпульсов устройства, информа ционные выходы блока памяти подключены к первой группе входов регистра выдачи, вторая группа входов которого подключена к выходам регистров символа, информационные входы которых соединены с второй группой информационных входов устро ства, выходы регистра выдачи являются вькодами устройства, схему сравнения, два регистра адпеса, дешифратор кода пробела, два тригге ра, генератор прямоугольных импульсов, элементы задержки и дешифратор входы KOTQporo соединены соответственно с выходами первого регистра адреса, а выходы подключены соответ ственно к управляющим входам регист ров символов, выходы которых подклю чены к первой группе входов схемы сравнения, вторая группа .входов которой соединена с информационными выходами блока памяти, информационные входы первого и второго регистр адреса подключены к информационным выходам блока памяти, вторая группа информационных входов устройства подключена к входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоугольных импульсов, выход которого соединен с входом считывания блока памяти и через первый элемент задер ки с входом второго элемента задерж ки и с первыми входами первого и вт рого элементов И, выход первого эле мента И подключен к второму входу генератора прямоугольных импульсов, к первым управляющим входам приема первого регистра адреса и регистра 84 вьщачи, выход второго элемента И соединен с управлякндим входом схемь( сравнения, первьм выход которой соединен с первым счетным входом второго регистра адреса, второй выход соединен с управляющим входом приема второго регистра адреса и с вторым управляющим входом приема первого регистра адреса, выходы второго регистра адреса соединены соответственно с адресными входами блока памяти,, вход установки исходного состояния устройства соединен с установочными входами первого и второго триггеров и с первым входом элемента ИЛИ, второй вход синхроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и четвертого элемен тов И, первьй и второй выходы условий блока памяти подключены соответственно к первому входу второго триггера и к первому входу пятого элемента И, первьп вход синхроимпульсов устройства через третий элеMeftT задержки соединен с вторым счетным входом второго регистра адресу, первый выход первого триггера соединен с вторым входом четвертого элемента И, второй выход подключен к второму входу третьего элемента И и к входу выбора приема-вьщачи регистров символа, второй вход второго триггера и вход управления выдачей регистра вьщач-и соединен с выходом шестого элемента И, первый выход второго триггера соединен с первым входом шестого элемента И и « с вторыми входами первого и пятого элементов И, второй выход второго триггера подключен к второму входу второго элемента И, выход второго элемента задержки соединен с третьим входом пятого элемента И и через четвертьй элемент задержки с вторым входом шестого элемента И, выход третьего элемента И подключен к счетному входу первого регистра адреса, выход четвертого элемента И соединен с вторым входом элемента ИЛИ, выход которого подключен к установочным входам перпого и второго регистров адреса, выход пятого элемента И соединен с вторым управляняцим входом приема регистра выдачи (3j . Недостатком известного устройства является низкая гибкость форми. руемого этим устройством базиса сло выходного языка. Низкая гибкость устройства обусловлена тем, что структура устройст ва не обеспечивает многократную интерпретацию множества выходных слов (базиса слов выходного языка), т.е коды выходньт слов, хранимые в блок памяти, не могут быть использованы для формирования других выходных слов, которые необходимо ввести, на пример, при увеличении списка выходных слов (при расширении макрофункций системы преобразования) или при введении новых входных языков. Это существенно сужает область прим нения устройства. Гибкость базиса слов выходного языка, формируемого устройством, может быть оценена формулой I - , МБ где М - множество выходных слов, формируемых устройством М, - моцность базиса. В известном устройстве М.. М поэтому L 1. При изменении макро функций системы (например, при вве дении новых входных языков) в известном устройстве необходимо увеличить объем блока памяти это.при водит к существенному увеличению затрат оборудования и, как следств снижению надежности. Увеличение гибкости базиса слов выходного при расширении набора макрофункций может быть обе печено без увеличения его мощности Однако эта возможность в известном устройстве не реализуется. Вследствие низкой гибкос.ти бази са слов выходного языка оно имеет существенно более узкую область пр менения. Цель изобретения - повышение ги кости базиса слов выходного языка путем выстраивания в требуемом порядке отдельных слогов выходного слова. Поставленная цель достигается тем, что в устройство, содержащее блок памяти, регистр адреса, муль типлексор логических условий, первый коммутатор, регистр выдачи, триггер пуска, триггер настройки, дешифратор настройки, генератор та товьк импульсов, первьш, второй, третий и четвертый элементы И, при 86 чем единйчньп выход триггера пуска соединен с входом генератора тактовых импульсов, первьш выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с синхронизирующим входом регистра адреса, выходы разрядов которого соединены с адресным входом блока памяти, выходы немодифицируемых разрядов адреса и выход модифицируемого разряда адреса блока памяти соединены соответственно с входами немодифицируемых разрядов адреса первого информационного входа первого коммутатора и с первым информационным входом мультиплексора логических условий, выход которого соединен с входом модифицируемого разряда адреса первого информационного входа первого коммутатора, вьсход первого коммутатора соединен с информационным входом регистра адреса, выход кода логических условий блока памяти соединен с управляющим входом мультиплексора логичес ких условий, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, вход слова устройства соединен с вторым информационным входом первого коммутатора, выход конца преобразования входного слова регистра выдачи соединен с разрешающим входом первого коммутатора, выход, конца работы регистра выдачи соединен с входом установки в О триггера пуска, выходы разрядов регистра выдачи являются выходами устрой ства, введены блоки памяти слогов выходных слов, запоминающий блок настройки, пересчетный блок, второй коммутатор, блок коммутации, причем вход пуска .устройства соединен с входом установки в 1 триггера пуска, а вход настройки устройства соединен с входом-установки в 1 триггера настройки, единичный выход которого соединен с вторым входом первого элемента И, с первыми входами второго, третьего и четвертого элементов И и с разрешающим входом второго коммутатора, нулевой выход триггера настройки соединен с входами обращения блока памяти и блоков памяти слогов выходных слов, второй выход генератора тактовых импульсов соединен с вторым входом второго элемента И и с вторым входом

четвертого элемента. И, первый выход генератора тактовых импульсов соединен с вторым входом третьего элемента И, выход которого соединен с входом записи запоминающего блока настройки, выход второго элемента И соединен с синхронизирующим входом регистра выдачи, единичный выход триггера пуска соединен с входом обращения запоминающего блока настройки,выход четвертого элемента И соедине с входом пересчетного блока, информационньй выход которого соединен с первым информационным входом второго коммутатора, выход второго крммутатора соединен с адресным входом запоминак-щего блока настройки, выход которого соединен с входом дешифратора настройки, выход дешифратора настройки соединен с разрешающим входом блока коммутации, выходы которого соединены с соответствующими информационными входами регистра выдачи, управляющий выход пересчетного блока соединен с входом установки в О триггера настройки, вход настройки устройства соединен с информационным входом запоминающего блока .настройки, выход адреса настройки блока намяти соединен с вторым информационным входом второго коммутатора, выходы адресов слогов выходных слов блока памяти соединены с адресными входами соответствукяцих блоков памяти слогов выходньк слов, выходы блоков памяти слогов выходных слов соединены соответственно с информационными входами блока коммутации, причем пересчетный блок содержит одновибратор, элемент И и счетчик, выходы разрядов которого подключены к информационному выходу блока и к входам элемента И, выход которого соединен с входом одновибратора, выход которого подключен к установочному входу счетчика и к управлякицему выходу блока, счетньй вход счетчика является входом блока.

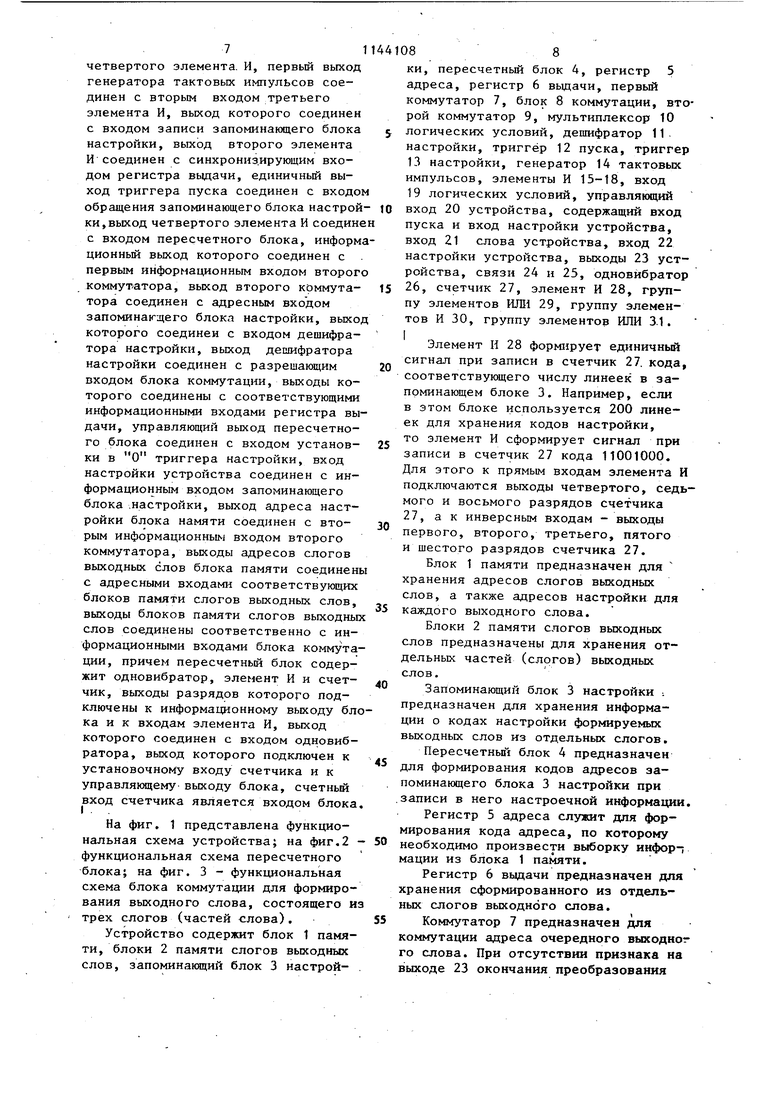

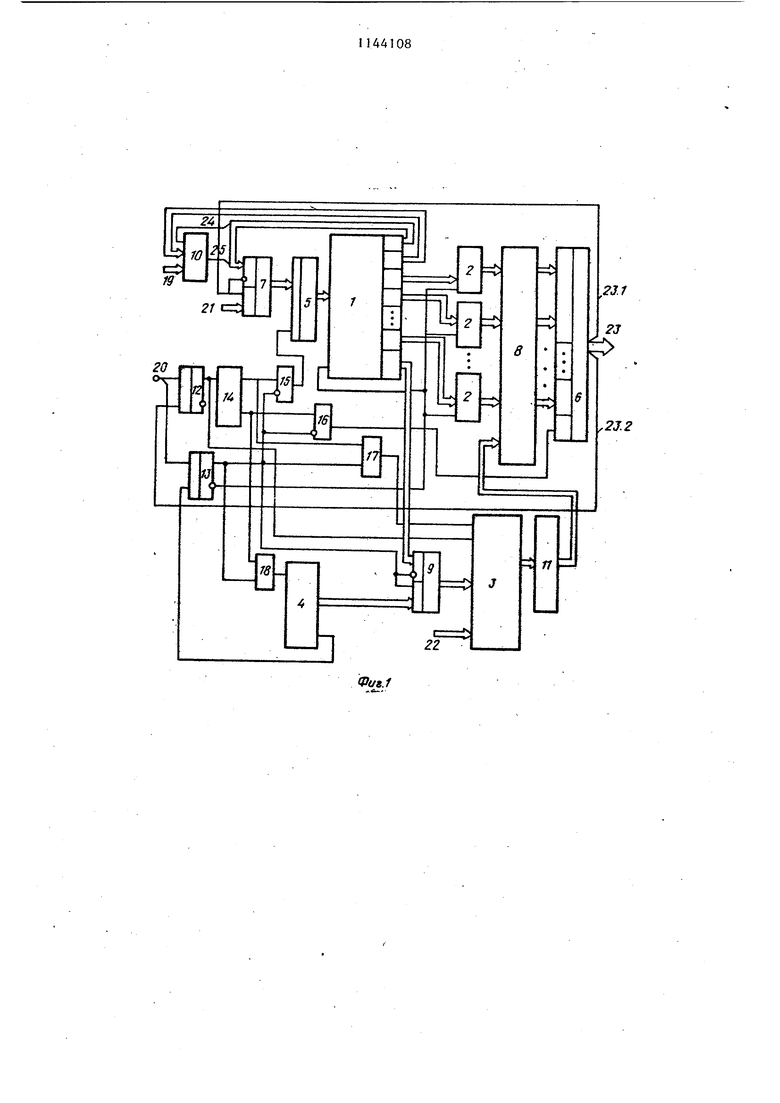

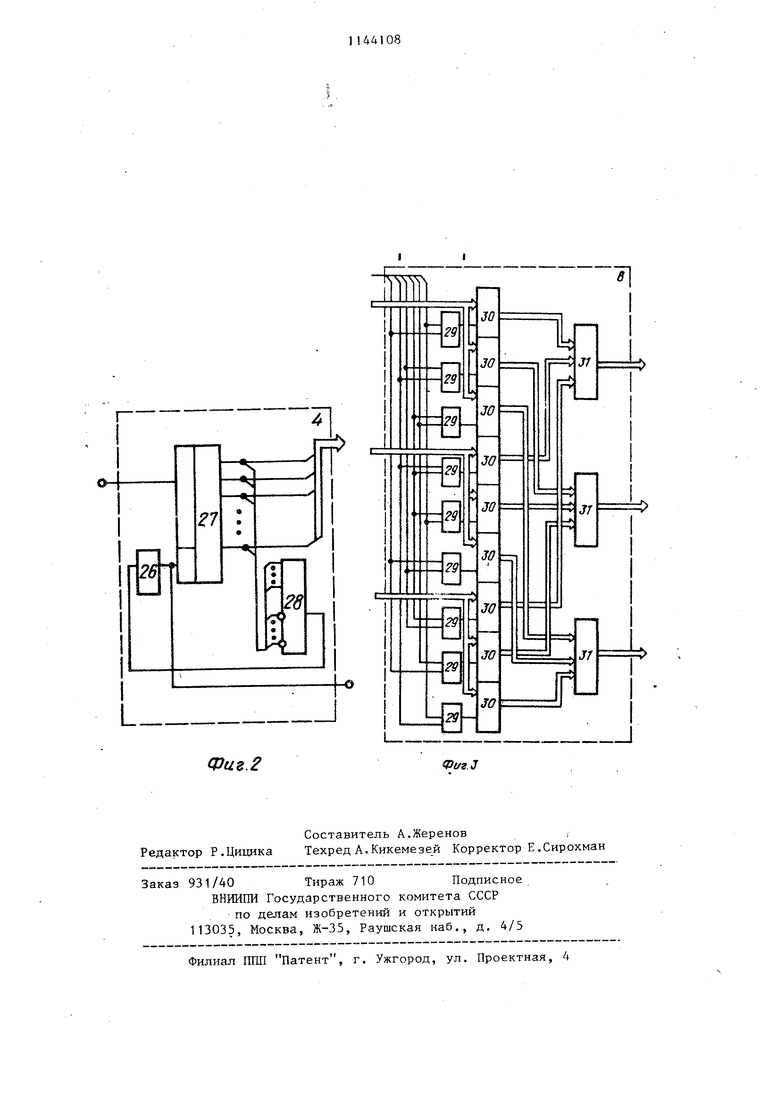

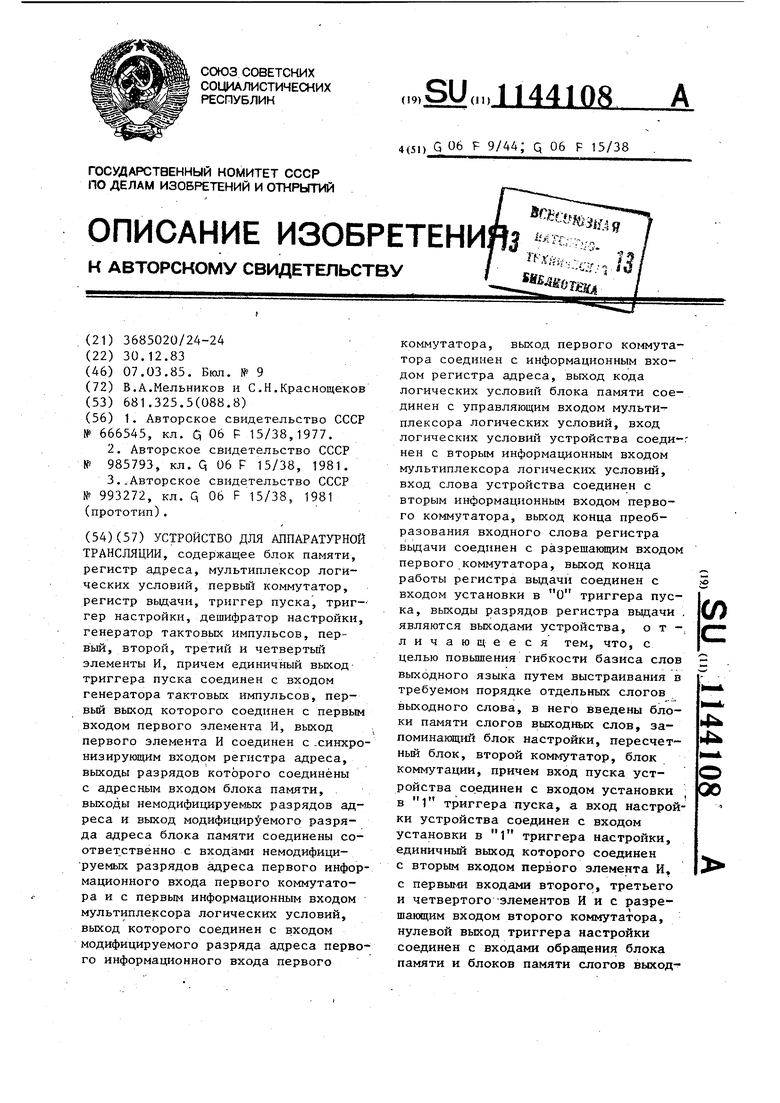

На фиг, 1 представлена функциональная схема устройства; на фиг.2 функциональная схема пересчетного блока; на фиг. 3 - функциональная схема блока коммутации для формирования выходного слова, состоящего из трех слогов (частей слова).

Устройство содержит блок 1 памяти, блоки 2 памяти слогов выходных слов, запоминающий блок 3 настройки, пересчетный блок 4, регистр 5 адреса, регистр 6 выдачи, первый коммутатор 7, блок 8 коммутации, второй коммутатор 9, мультиплексор 10 логических условий, дешифратор 11 настройки, триггер 12 пуска, триггер 13 настройки, генератор 14 тактовых импульсов, элементы И 15-18, вход 19 логических условий, управляющий вход 20 устройства, содержащий вход пуска и вход настройки устройства, вход 21 слова устройства, вход 22 настройки устройства, выходы 23 устройства, связи 24 и 25, одновибратор

26,счетчик 27, элемент И 28, группу элементов ИЛИ 29, группу элементов И 30, группу элементов ИЛИ 3.1.

Элемент Н 28 формирует единичный сигнал при записи в счетчик 27. кода, соответствующего числу линеек в запоминающем блоке 3. Например, если в этом блоке используется 200 линеек для хранения кодов настройки, то элемент И сформирует сигнал при записи в счетчик 27 кода 11001000. Для этого к прямым входам элемента И подключаются выходы четвертого, седьмого и восьмого разрядов счетчика

27,а к инверсным входам - выходы первого, второго, третьего, пятого и шестого разрядов счетчика 27.

Блок 1 памяти предназначен для хранения адресов слогов выходных слов, а также адресов настройки для каждого выходного слова.

Блоки 2 памяти слогов выходных слов предназначены для хранения отдельных частей (слогов) выходных слов.

Запоминающий блок 3 настройки : предназначен для хранения информации о кодах настройки формируемых выходных слов из отдельных слогов.

Пересчетньй блок 4 предназначен для формирования кодов адресов запоминающего блока 3 настройки при .записи в него настроечной информации

Регистр 5 адреса служит для формирования кода адреса, по которому необходимо произвести выборку информации из блока 1 .

Регистр 6 вьщачи предназначен для хранения сформированного из отдельных слогов выходного слова.

Коммутатор 7 предназначен для коммутации адреса очередного выходно го слова. При отсутствии признака на выходе 23 окончания преобразования 9 входного слова регистра 6 выдачи на регистр 5 адреса поступает адрес с выхода блока 1 памяти и мультиплексора 10. В противном случае в регис 5 адреса записывается код очередног входного слова, определяющий адрес первого выходного слова. Блок 8 коммутации предназначен для формирования выходного слова от дельных слогов в зависимости от кода настройки, поступающего с выходо дешифратора 11 настройки. Коммутатор 9 служит для коммутации адреса настройки. При наличии сигнала настройки адрес через коммутатор 9 поступает с выхода блока 4 при записи информации в запоминаю щий блок 3 настройки с входа 22 устройства. В рабочем режиме при отсутствии сигнала настройки адрес информации кодов настройки поступает с выхода блока 1 памяти. Мультиплексор 10 логических условий предназначен для формирования значения модифицируемого разряда адреса выходного слова, поступающего на вход 24 мультиплексора 10, ко торый реализует следующую логическу функцию у + Хзг, + XjZj + ... + где у - вькодной сигнал мультигшек сора 10; - конъюнкция 0, , ос л , соответствующая коду с выхода блока 1 памя ти, разрешающеь-гу прохождение модифицируемого адресного разряда а без изменеНИИ;2 1 , Ф 25 v 3 3 Xj «1.15 ). 2 oi3 3 i «X. 2 Ot- 3 , Oi-t КОНЪЮНКЦИИ, соответствующие кодам, определяющим прохождение на выход мультиплексора 10 одного из сигнало логических условий z,, z , z , -z с входа 19 логических условий. Дешифратор 11 используется для формирования сигнала настройки выходного слова из отдельных слогов. Триггер 12 применяется для запус ка генератора 14, включение которого происходит по сигналу пуска с дхода 20 устройства, а выключение 08 10 по сигналу конца работы с выхода регистра 6 выдачи. Кроме того, триггер 12 разрешаем проводить выборку информации из запоминающего блока 3 настройки. Триггер 13 предназначен для формирования сигнала разрешения работы устройства в режиме настройки. Генератор 14 служит для синхронизации работы устройства. На его выходах формируются первьм и второй тактовые импульсы. Элементы И 15 и 16 предназначены для управления считыванием информации из блока 1 памяти и блоков 2 памяти слогов выходных слов и вьщачи сформированного вЕ 1ходного слова в рабочем режиме на выход 23 устройства. Элемент И 17 предназначен для управления записью информации в запоминающий блок 3 настройки с входа 22 устройства в режиме настройки. Элемент И 18 предназначен для управления блоком 4 в р.ежиме настройки . I Устройство может функционировать в двух режимах: режиме настройки и рабочем режиме. В исходном состоянии элементы памяти устройства находятся в нулевом состоянии, за исключением триггера регистра 6 выдачи, соответствующего выходу конца преобразования. В режиме настройки с входа 20 устройства на входы установки в 1 триггеров 12 и 13 поступает импульс, котор-ый переводит их в единичное состояние, с входа 22 устройства поступает информация, которую необходимо записать в запоминающий блок 3 настройки. Первый тактовый импульс с выхода генератора 14 через элемент И 17 разрешает запись информации с входа 22 в нулевую ячейку запоминающего блока 3 (адрес, по которому происходит запись информации, поступает с выхода блока 4 через коммутатор 9 на вход запоминающего блока 3 настройки). Второй тактовый импульс с выхода генератора 14 через элемент И 18 увеличит содержимое блока 4 на 1 и тем самым подготовит очередной адрес запоминающему блоку 3 настройки для записи информации с входа 22 устройства. Очередным тактовым импульсом производится запись информации настройки с входа 22 в 11 запоминающий блок 3 настройки по адресу, сформированному в блоке 4. Далее режим настройки проходит аналогично рассмотренному. Запись информации в блок 3 происходит до тех пор, пока с выхода блока 4 не сформируется импульс окончания процесса записи информации в запоминаю щий блок 3 настройки. Этот игшульс с выхода блока 4 поступает на вход установки в О триггера 13, и устройство переходит в рабочий режим функционировяния. При функционировании устройства в рабочем режиме с входа 21 через коммутатор 7 в регистр ,5 адреса заноситря входное слово, определяющее . начальный адрес последовательности слов выходного языка. Тактовьп импульс выхода генератора 14 через элемент И 15 поступает на синхронизирующий вход регистра 5 адреса и тем самым производит выборку информации из блока .1 памяти. С блока 1 памяти выдается слово, определяк5щее, во-первых, адрес очередного слова, во-вторых, адреса слогов выходного слова и, в-третьих, адрес линейки с требуемым кодом настройки вьосодного слова. Информация об адре се очередного слова вьщается с выходов блока 1 памяти. Если очередное словоявляется словом линейной последовательности, то адрес очеред ного слова с блока 1 памяти через коммутатор 7 заносится в регистр 5 адреса. Если очередное слово являет ся словом, при котором процесс преобразования может пойти в зависимос ти от определенных условий, то адре очередного слова на выходе блока 1 памяти содержит постоянную часть и один модифицируемьй разряд. . Постоянная часть кода поступает непосредственно на инфорнационньй вход коммутатора 7, а модифицируемьв разряд поступает на вход мультиплек сора 10 логических условий. Если проверяемое логическое условие выполнилось (х 1), то младший разрьщ адреса очередного слова принима ет единичное значение, и сформированный адрес очередного слова при отсутствии признака конца преобразо вания входного слова через коммута,тор 7 записывается в регистр 5 адреса. При поступлении адресов слогов выходного слова с выходов блока 1 0812 на выходах блоков 2 памяти формируются слоги выходного слова, которые поступают на входы блока 8 коммутации. Одновременно с выдачей адресов слогов выходного слова с блока 1 памяти вьщается адрес настройки. Этот адрес через коммутатор 9 поступает на вход запоминающего блока 3 наст- ростки. Запоминающий блок 3 настройки представляет регистров, в которые записана информация о перестройках слогов того или иного выходного слова. По адресу с выхода блока Iпамяти сосчитывается код настройки слогов из запоминающего блока 3 наст-, ройки. На одном из выходов дешифратора I1настройки появляется сигнал, . .поступающий на вход блока 8 коммута- ции и определякиций расположение отдельных слогов в выходном слове. Сформированное из отдельных слогов выходное слово с выходов блока 8 коммутации заносится в регистр 6 вьщачи. По тактовому импульсу, поступающему с выхода генератора 14 через элемент И 16, выходное слово с регистра 6 вьщается на выход 23 устройства. Аналогичным образом устройство функционирует до вьщачи последнего выходного слова. С вьщачей последнего выходного слова на выход 23 устройства вьщается метка-признак окончания преобразования входного слова. Данная метка поступает на вход коммутатора 7 и разрешает тем самым запись нового входного слова с входа 21 устройстве для дальнейшего его преобразования в множество вь1ходных слов. Преобразование входного слова осуществляется аналогично рассмотренному. При вьщаче последнего выходного слова предложения с выхода 23 вьщается метка конца работы, которая поступает на вход установки в О триггера 12 пуска. Устройство переходит в исходное состояние и готово к дальнейшей работе. Если после вьщачи очередного выходного необходимо осуществить перенастройку слогов выходных слов, то на вход 20 поступает единичный сигнал, переводящий устройство в режим настройки. Таким образом, рассмотренное устройство для аппаратурной трансляции позволяет осуществить процесс пре- образования слов входного языка в

13

слова выходного языка в одном из возможных режимов: Один к одному, Один в несколько, Несколько в один и Несколько в несколько. При этом процесс преобразования осуществляется в режиме шаговой интерпретации, т.е. одновременно с преобразованием текста входного язы. ка происходит его вьшолнение. Кроме то го ,в устройстве код вькодного слова М

представляется в виде композиции

М (т,. Го; , Шз , ...,т,), где т; (i 1, п) - слоги выходного слова, хранящиеся в отдельных блоках памяти. Например, для выходного слова, состоящего из трех слогов, имеем М m + fflj +123, где знак + означает операцию сериализации слогов, т.е. последовательного их составления в зависимости от кода настройки.Для рассматриваемого примеру путем настройки (перестроения слогов) можем получить следующий :набор выходных слов

Расширение множества йыходных слов путем их формирования из отдельньЕх слогов, хранимьк в различных блоках памяти, позволяет уменьшить 5 требуемый объем блоков памяти, при отказах отдельных элементов памяти подключать резервные, а путем настройки возможно восстановление выходных Слов и , еле10 довательно , самого процесса трансляции .

Таким образом, устройство позволяет увеличить гибкость базиса слов 15 выходного языка за счет операции

сериализации (выстраивания в требуемом порядке, определяемом кодом настройки) отдельных слогов выходного слова.

Увеличение гибкости базиса слов

выходного языка может быть использовано для повьшения экономичности блоков памяти, при отказах отдельных

5 ячеек памяти для перестройки структуры путем соответствующей настройки на выполнение требуемых преобразований и для адаптации к расширейию множества входных языков.

b

24

u

25

10

19

Г№J П

23

1

8

j

/4

,2j:

MfH-l

§

/7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования кодов с одного языка на другой | 1978 |

|

SU666545A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-07—Публикация

1983-12-30—Подача