Изобретение относится к вычислительной технике и может быть использовано в быстродействующих операционных системах, в частности в системах непосредственной реализации языков высокого уровня, аппаратурных транслирующих системах, построенных на основе однотипных модулей.

Цель изобретения - повышение производительности.

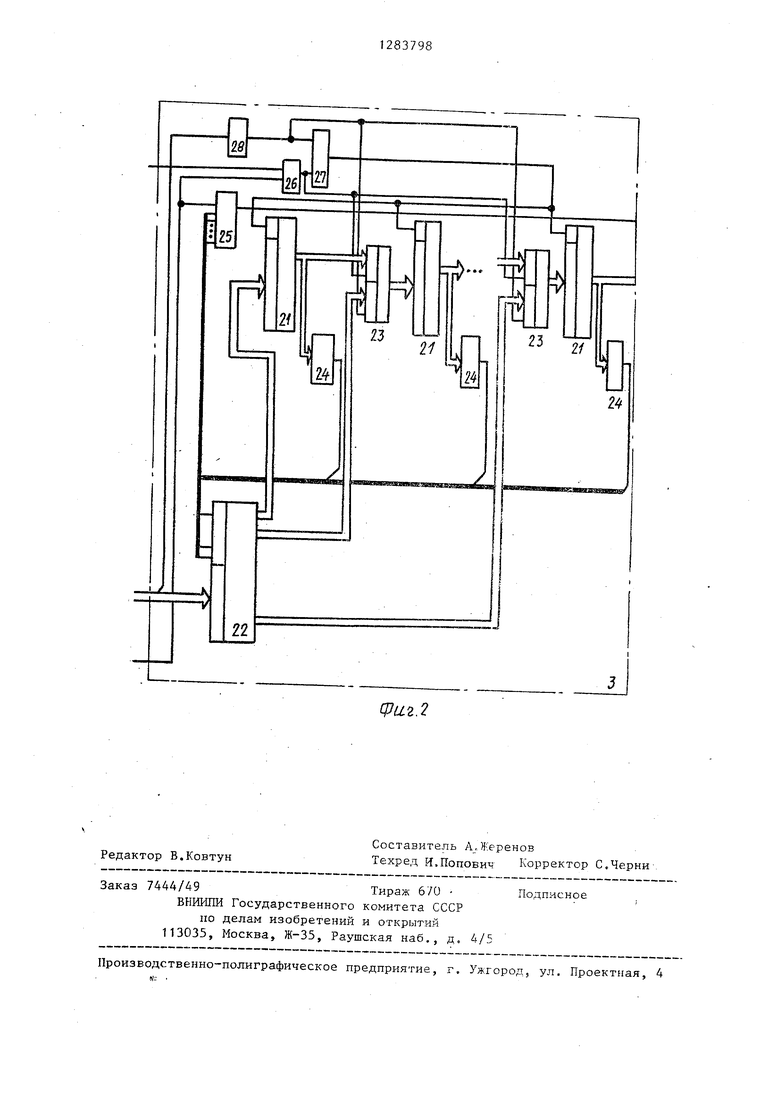

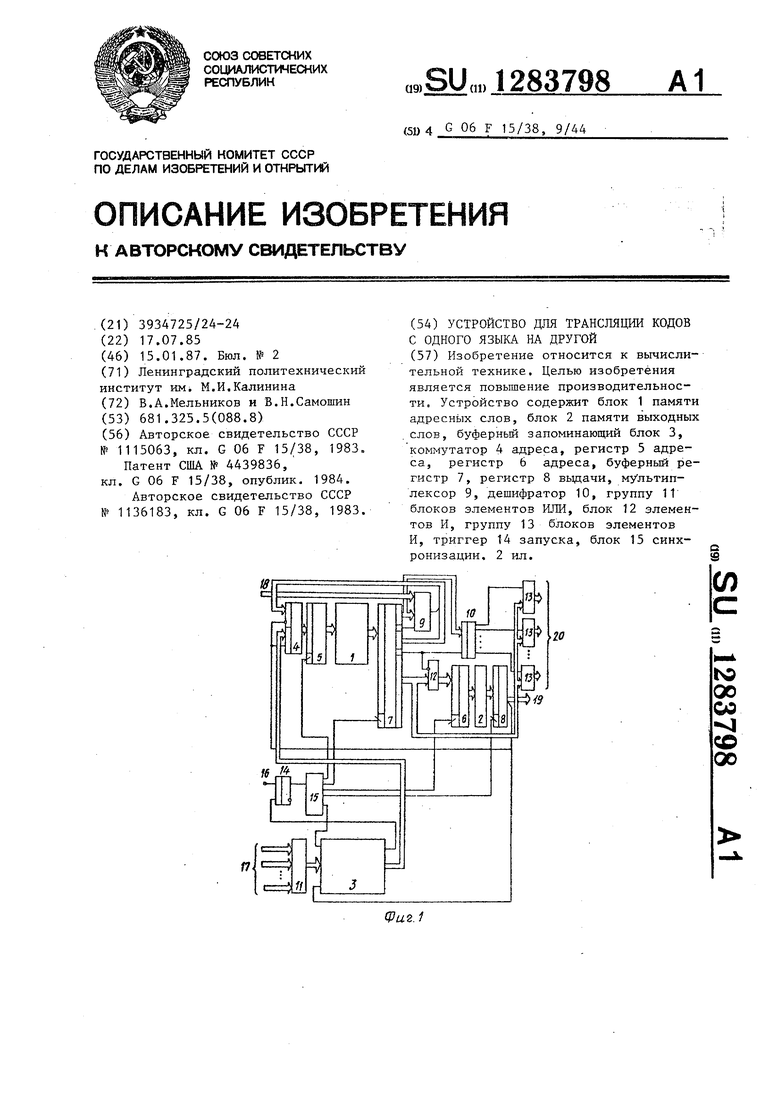

На фиг.1 представлена схема устройства; на фиг.2 - функциональная схема буферного запоминающего блока.

Устройство содержит блок 1 памяти 15 адресных слов, блок 2 памяти выходных слов, буферный запоминающий блок (БЗБ) 3, коммутатор 4 адреса, регистр 5 адреса, регистр 6 адреса, буферньй

Буферный запоминающий блок организует обслуживание поступивших входных слов на преобраз ование в соответствии с дисциплиной первым пришел - первым обслужен. Так как в начальный момент времени все регистры 21 находились в нулевом состоянии, то на выходах группы 24 элементов И образуется управляющий код, поступающий на управляющий вход демультиплексора 22 и ра зрешаю- щий запись входного слова с входа буферного запоминающего блока 3 в регистр 21. Состояние этого регистра будет отличным от нулевого и на выходе элемента И 24 будет сигнал логической единицы. Этот сигнал, поступая на управляющий вход демультиплексора

25

пегисто 7. регистр В выдачи, мультип-20 „„ pcinv-Jt , f f , запрещает прохождение с его входа

лексор 9, дешифратор 10, группу 11 блоков элементов ИЛИ, блок 12 элементов И, группу 13 блоков элементов И, триггер 14 запуска, блок 15 синхронизации, вход 16 запуска устройства, информационные входы 17 устройства, вход 18 условий преобразования, выходы 19 и 20 устройства, группу 21 регистров, демультиплексор 22, группу 23 коммутаторов, группу 24 элеме нтов И, элемент И 25, элемент И 26, элемент ИЛИ 27, одновибратор 28.

Устройство функционирует следующим образом.

очередного входного слова в первый регистр 21 и разрешает заполнение последующих регистров.

I Работа устройства начинается путем подачи импульса на вход 16. При поступлении этого импульса триггер 14 запуска переходит в единичное состояние и тем самым разрешает формирование серии тактовых импульсов с выходов блока 15 для синхронизации работы устройства.

С выхода первого регистра 21 информация первого входного слова поВ исходном состоянии элементы па- 35 ступает на выход буферного запоминающего блока 3 и с его выхода через

30

мяти устройства находятся в нулевом состоянии (за исключением разряда регистра 8 вьздачи, определяющего окончание процесса преобразования входного слова).40

Устройство может функционировать в двух режимах: режиме преобразования входного слова, поступившего на данкоммутатор 4 адреса по тактовому импульсу заносится в регистр 5 адреса.

Входное слово представляет начальный адрес программы преобразования (трансляции) кодов (слов) входного языка в множество кодов (слов) выходного языка. При этом возможно три режима преобразования: Один в нескольное устройство; режиме передачи слова45 ко, Один в один, Несколько в

с заданного устройства на его преобразование .аналогичным устройством транслирующей системы. При этом передача слова с одного устройства на

другое устройство системы осуществля-50 первом уровне происходит преобразова- ется в процессе преобразования неко- ние адресных слов, на втором - непосредственно формирование выходных слов. По очередному тактовому импульсу в буферный регистр 7 заносится ад торого макрослова (макрооператора), входного языка.

При поступлении входного слова на первый вход 17 (другие входы 17 сое- ресное слово, определяющее режим ра- динены с соответствующими выходами боты, адрес очередного адресного сло- аналогичных устройств транслирующей системы) через группу 11 блоков элева и адрес выходного слова. В свою очередь, очередной адрес адресного слова определяется кодом условий проментов ИЛИ это слово заносится в пер

вьй регистр 21 (фиг.2) буферного запоминающего блока 3.

Буферный запоминающий блок организует обслуживание поступивших входных слов на преобраз ование в соответствии с дисциплиной первым пришел - первым обслужен. Так как в начальный момент времени все регистры 21 находились в нулевом состоянии, то на выходах группы 24 элементов И образуется управляющий код, поступающий на управляющий вход демультиплексора 22 и ра зрешаю- щий запись входного слова с входа буферного запоминающего блока 3 в регистр 21. Состояние этого регистра будет отличным от нулевого и на выходе элемента И 24 будет сигнал логической единицы. Этот сигнал, поступая на управляющий вход демультиплексора

„„ 22, запрещает прохождение с его входа

коммутатор 4 адреса по тактовому импульсу заносится в регистр 5 адреса.

Входное слово представляет начальный адрес программы преобразования (трансляции) кодов (слов) входного языка в множество кодов (слов) выходного языка. При этом возможно три режима преобразования: Один в нескольодин . Некоторые выходные слова могут быть пустыми.

Устройство реализует ортогональное (двухуровневое) преобразование. На

су в буферный регистр 7 заносится адресное слово, определяющее режим ра- боты, адрес очередного адресного сло-

ресное слово, определяющее режим ра- боты, адрес очередного адресного сло-

ва и адрес выходного слова. В свою очередь, очередной адрес адресного слова определяется кодом условий процесса преобразования с выхода первого поля буферного регистра 7, вторым полем буферного регистра 7 и меткой- признаком.

Если очередное адресное слово за- г висит от некоторых условий процесса преобразования, то код самого условия заносится в первое поле буферного регистра 7, во второе поле заносится немодифицируемая часть адреса, а пер- fO вал метка-признак определяет модифицируемый разряд адреса адресного слова.

Мультиплексор 9 реализует логичес- 15 кую функцию вида y.,a+X2Zj+X3Z2 + ,.. .,+Х| + г2ч, где у - выходной сигнал мультиплексора 9; X V -

са и далее. Устройство функционирует аналогично рассмотренному выше.

Б том случае, если вьщается последнее выходное слово после преобразования входного слова и в буферный ззггоми лающин блок 3 от других анало- гниных устройств или от супервизорно- го устройства входных слов на преоб- разова:-1ие не поступило, то одновременно с выдачей последнего выходного слова, с выхода регистра 8 выдается метка-признак окончания процесса преобразования. Эта метка-признак поступает на вход буферного запоминающего блока 3 и, так как регистры 21 находятся Е Ji yjiepOM состоянии, на выходе элемента И 25 образуется потенциал лсгичсской еднниф). Этим сигналом триггер 14 запуска устанавливается в

- конъюнкция c/j . ,., d.f СО- 20 нулевое состояние и работа устройства

ответствующая коду условии преобразования, разрешающему прохождение модифицируемого адресного разряда а без изменений;25

0/ .6/, , ,о(2,.

,о(

«(.

Х, orjo,ot

. ,с(| - КОНЪЮНКЦИИ, соответствующие кодам, оп- 30 ределяющим прохождение на выход мультиплексора 9 одного из сигналов условий преобразования Z, 35 Zj ,... . ,Z с входа 18.

Если очередное адресное слово не зависит от условий преобразования, то то оно определяется кодом второго по- ля буферного регистра 7. В третьем поле регистра 7 находится адрес выходного слова, который по очередному тактовому импульсу с выхода блока 15 заносится в регистр 6 адреса. Из блока 2 памяти начинается выборка информации. По очередному тактовому импульсу выбранное выходное слово заносится в регистр 8 выдачи и с его

выхода поступает на выход 19, Признак 50 признака регистра 7 определяет режим окончания процесса преобразования на выходе регистра 8 выдачи исчезает и тем самым запрещается сдвиг информации в буферном ;гап6минающем блоке 3 и ее прохождение через коммутатор 4 адреса для занесения в регистр 5. Адрес очередного адресного слова с буферного регистра 7 через коммутатор 4 адреса заносится в регистр 5 адрепередачи слова аналогичному устройству. При выдаче метки-признака передачи слова код устройства, которому необходимо передать это слово, поступа- 55 ет на вход дешифратора 10. Последний преобразует ДЕОИЧНЬШ код в унитарный код и открывает соответствующий блок элементов И группы 13 для передачи слеза, на. один из выходов 20. С выхода

са и далее. Устройство функционирует аналогично рассмотренному выше.

Б том случае, если вьщается последнее выходное слово после преобразования входного слова и в буферный ззггоми лающин блок 3 от других анало- гниных устройств или от супервизорно- го устройства входных слов на преоб- разова:-1ие не поступило, то одновременно с выдачей последнего выходного слова, с выхода регистра 8 выдается метка-признак окончания процесса преобразования. Эта метка-признак поступает на вход буферного запоминающего блока 3 и, так как регистры 21 находятся Е Ji yjiepOM состоянии, на выходе элемента И 25 образуется потенциал лсгичсской еднниф). Этим сигналом триггер 14 запуска устанавливается в

завершается.

Если, в буферном запоминающем блоке 3 была занесена информация на преобразование, то метка-признак окончания процесса преобразования предьщу- щего слова с выхода регистра 8 выдачи поступая на вход буферного запоминающего блока 3. производит сдвиг инфор- мац11 -1 в регистрах 21 и запись инфор- мации 3 регистр 5. адреса. Далее устройство функционирует аналогично рассмотренному вьшге.

Второй релдам работы устройства является подрелопчок и осуществляется в процессе Быгюлнения первого режима. Так при необходимости передачи некоторых слов для их дальнейшего преобразования в адресное слово (информация буферного регистра 7) заносится следующая информация. В первое поле регистра 7 заносится Код устройства, которому необходимо передать слово для дальне1 п1;его его преобразования, Во второе поле, как и в первом релси- ма 5 з 1носится адрес очередного адресного слова, 3 третье поле регистра 7 заносится код слова, которое необходимо для дальнейутего его преобразования. Кроме того, выход второй меткипризнака регистра 7 определяет режим

передачи слова аналогичному устройству. При выдаче метки-признака передачи слова код устройства, которому необходимо передать это слово, поступа- ет на вход дешифратора 10. Последний преобразует ДЕОИЧНЬШ код в унитарный код и открывает соответствующий блок элементов И группы 13 для передачи слеза, на. один из выходов 20. С выхода

устройства входное слово поступает на соответствующий информационный вход другого устройства и через группу 11 бпоков элементов ИЛИ заносится в буферный запоминающий блок 3 для его дальнейшего преобразования.

Фо, рмула изобретения

Устройство для трансляции кодов с одного языка на другой, содержащее блок памяти адресных слов, блок памяти выходных слов, коммутатор адреса,

12837986

низации соединен с синхронизирующим

fO

входом регистра выдачи, информационный выход которого соединен с первым информационным выходом устройства, вход условий преобразования устройства соединен со вторым информационным входом мультиплексора, выход которого соединен с первым информацион ным входом коммутатора адреса, выхо признака регистра соединен с прямым и инверсным управляющими входами коммутатора адреса, отличающееся тем, что, -с целью повьшения производительности, в него

первый регистр адреса,- второй регистр 5 введены буферный запоминающий блок.

25

адреса, буферный регистр, р егистр выдачи, мультиплексор, блок элементов И, триггер запуска, блок синхронизации, причем вход запуска устройства соединен с единичным входом триггера 20 запуска, единичный выход которого со- единен с управляющим входом блока синхронизации, первый выход блока синхронизации соединен с синхронизи- руюищм входом первого регистра адреса, выход которого соединен с адресным входом блока, памяти адресных слов, выход блока памяти адресных слов соединен с информационным входом буферного регистра, выходы разрядов -30 первого поля которого соединены с управляющим входом мультиплексора, выход первой метки-признака буферного регистра соединен с первым информационным входом мультиплексора выходы разрядов второго поля буферного регистра соединены с первым информационным входом коммутатора адреса, выход которого соединен с информационным входом первого регистра адреса, второй выход блока синхронизации соединен с синхронизирующим входом буфе|5- ного регистра, выход второго регистра адреса соединен с адресным входом

35

40

блока.памяти выходных слов, выход ко- 45коммутатора адреса, выход признака

торого соединен с информационным вхо-регистра вьщачи соединен с входом

дом регистра вьщачи, третий выходпризнака буферного запоминающего блоблока синхронизации соединен с синх-ка, выход признака окончания которого

ронизирующим входом второго регистрасоединен с нулевым входом триггера

адреса, четвертью выход блока синхро- 50запуска.

входом регистра выдачи, информационный выход которого соединен с первым информационным выходом устройства, вход условий преобразования устройства соединен со вторым информационным входом мультиплексора, выход которого соединен с первым информационным входом коммутатора адреса, выход признака регистра соединен с прямым и инверсным управляющими входами коммутатора адреса, отличающееся тем, что, -с целью повьшения производительности, в него

введены буферный запоминающий блок.

5

0 0

группа блоков элементов И, группа блоков элементов 1-ШИ и дешифратор, причем выходы разрядов первого поля буферного регистра соединены с информационным входом дешифратора, выход второй метки-признака буферного регистра соединен с управляющим входом дешифратора и с инверсным входом блока элементов И, разрядов тре- - тьего поля буферного регистра соединены с информационным входом блока элементов И и с информационными входами блоков элементов И группы, выходы дешифратора соединены соответственно с управляющими входами блоков элементов И группы, выходы которых соединены с вторым информационным выходом устройства, выход блока элементов И соединен с информационным вхо- 5 дом второго регистра адреса, информационный вход устройства соединен с входами блоков элементов ИЛИ группы, выходы которых соединены с информаци- oHHbw входом буферного запоминающего блока, пятый выход блока синхронизации соединен с синхронизирующим входом буферного запоминающего блока, информационный выход которого соединен с вторым информационным входом

0

24

t

Редактор В.Ковтун

Заказ 7444/49Тираж 670

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

V

l

сриг.2

Составитель А.Жеренов

Техред Я.Попович Корректор С.Черни

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для преобразования кодов с одного языка на другой | 1984 |

|

SU1238104A1 |

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для формирования периодических функций | 1987 |

|

SU1441391A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение производительности. Устройство содержит блок 1 памяти адресных слов, блок 2 памяти выходных слов, буферный запоминающий блок 3, коммутатор 4 адреса, регистр 5 адреса, регистр 6 адреса, буферный регистр 7, регистр 8 выдачи, мультиплексор 9, дешифратор 10, группу 11 блоков элементов ИЛИ, блок 12 элементов И, группу 13 блоков элементов И, триггер 14 запуска, блок 15 синхронизации. 2 ил. (Л tvd 00 оо QD 00

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4439836, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для преобразования кодов с одного языка на другой | 1983 |

|

SU1136183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-17—Подача