СО

С

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для сопряжения двух магистралей | 1987 |

|

SU1418728A1 |

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Многомашинная вычислительная система | 1990 |

|

SU1798798A1 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1587520A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

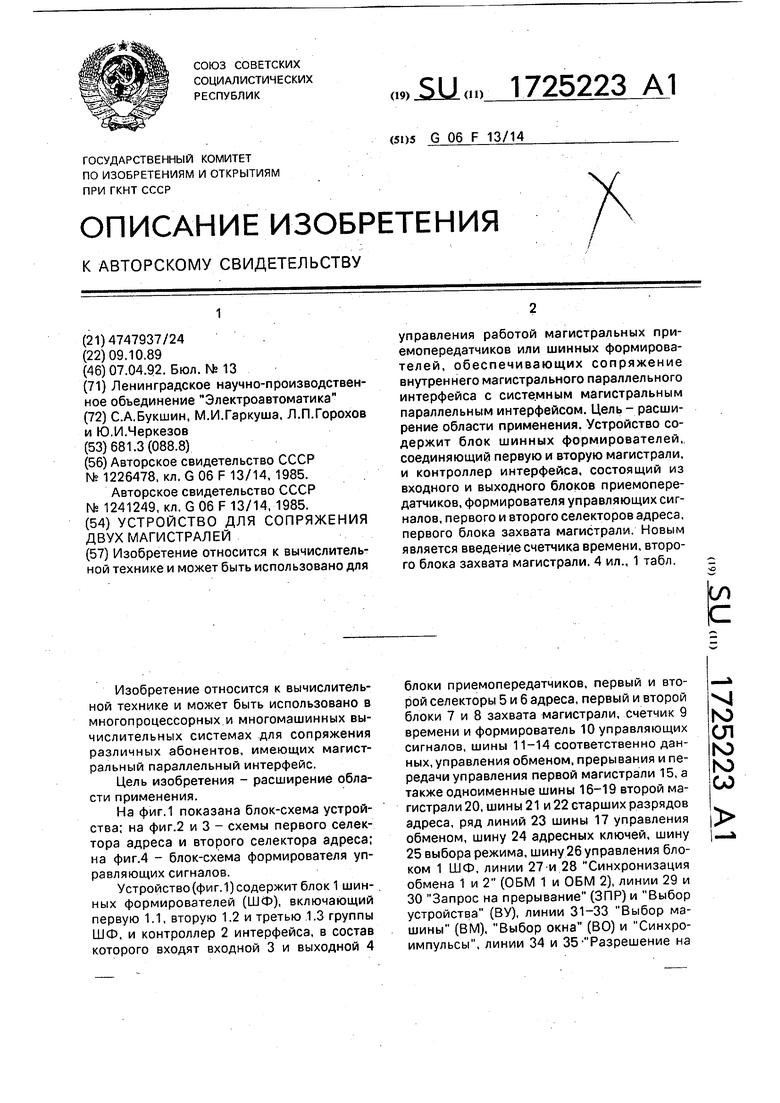

Изобретение относится к вычислительной технике и может быть использовано для управления работой магистральных приемопередатчиков или шинных формирователей, обеспечивающих сопряжение внутреннего магистрального параллельного интерфейса с системным магистральным параллельным интерфейсом. Цель -расширение области применения. Устройство содержит блок шинных формирователей, соединяющий первую и вторую магистрали, и контроллер интерфейса, состоящий из входного и выходного блоков приемопередатчиков, формирователя управляющих сигналов, первого и второго селекторов адреса, первого блока захвата магистрали. Новым является введение счетчика времени, второго блока захвата магистрали. 4 ил., 1 табл.

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных и многомашинных вычислительных системах для сопряжения различных абонентов, имеющих магистральный параллельный интерфейс.

Цель изобретения - расширение области применения.

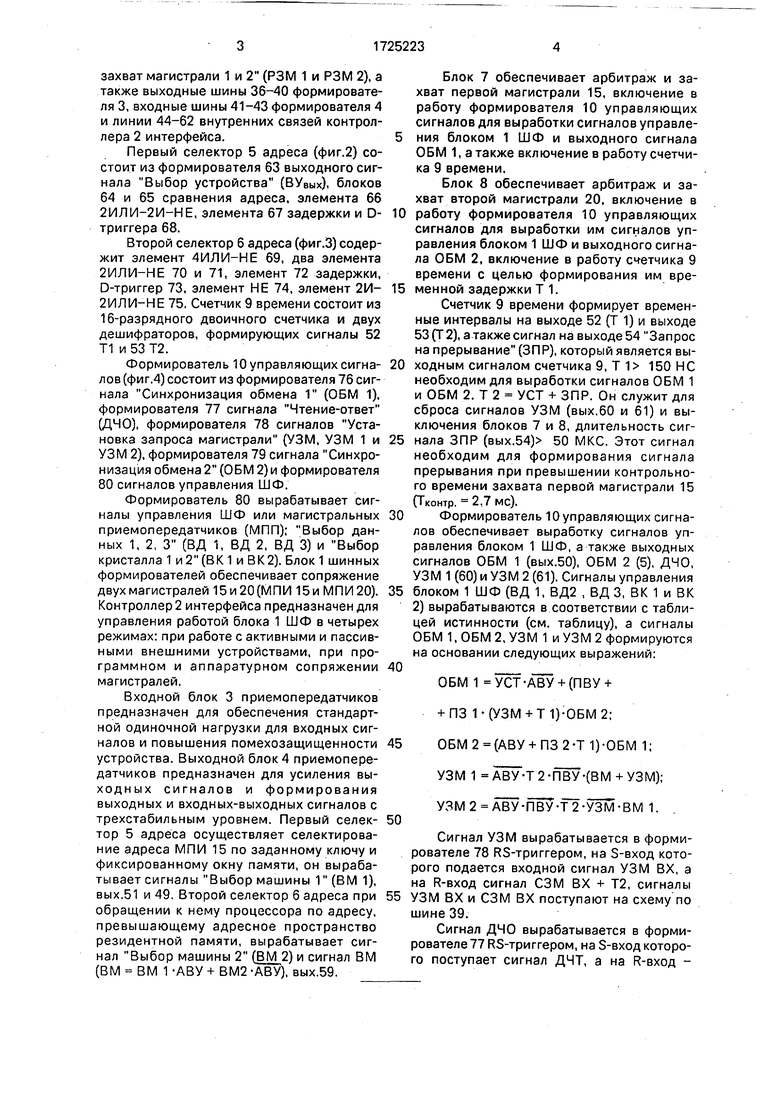

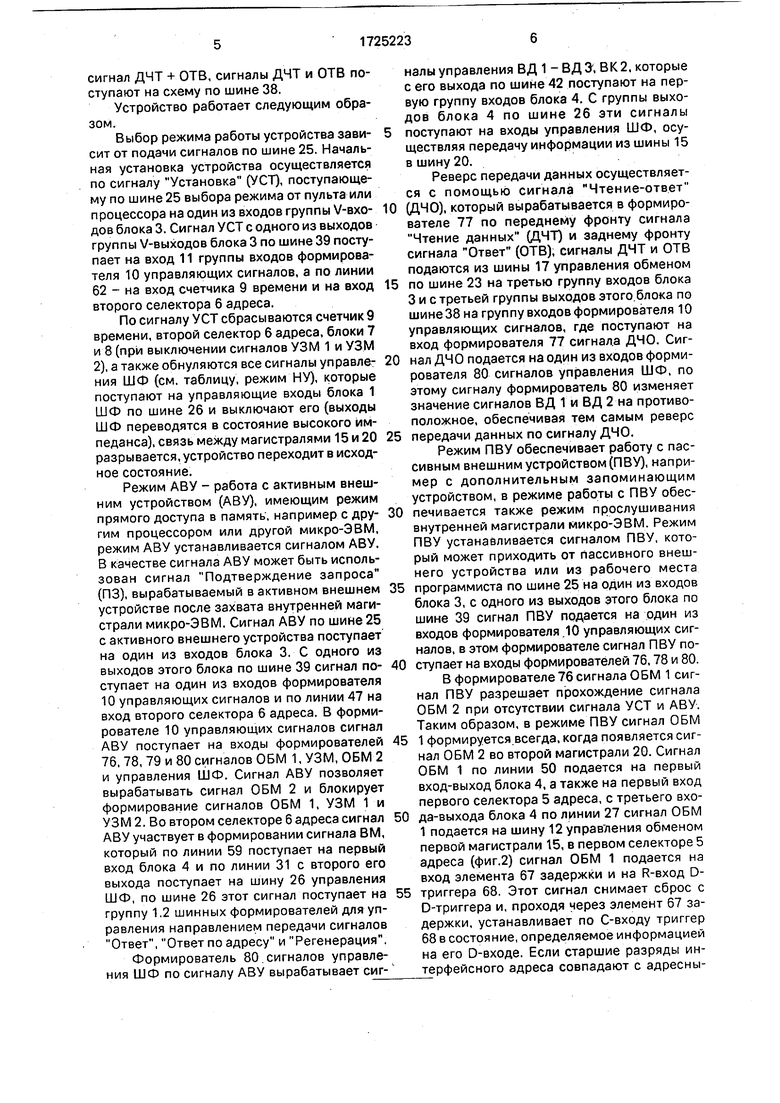

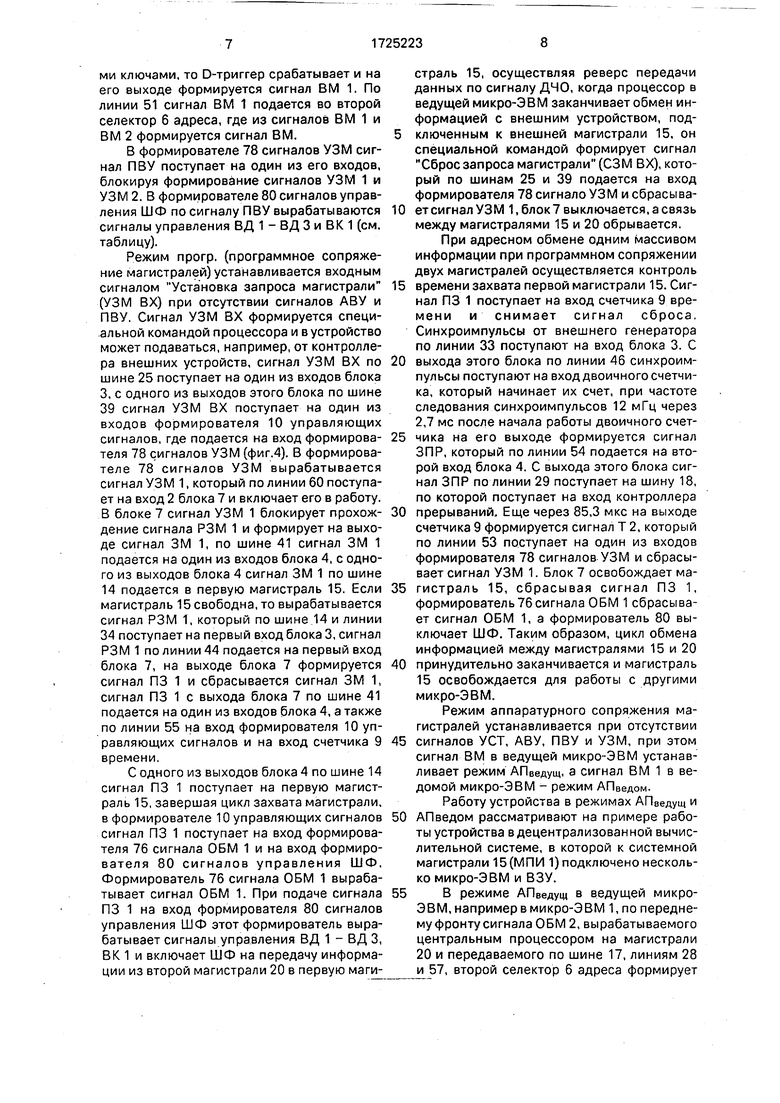

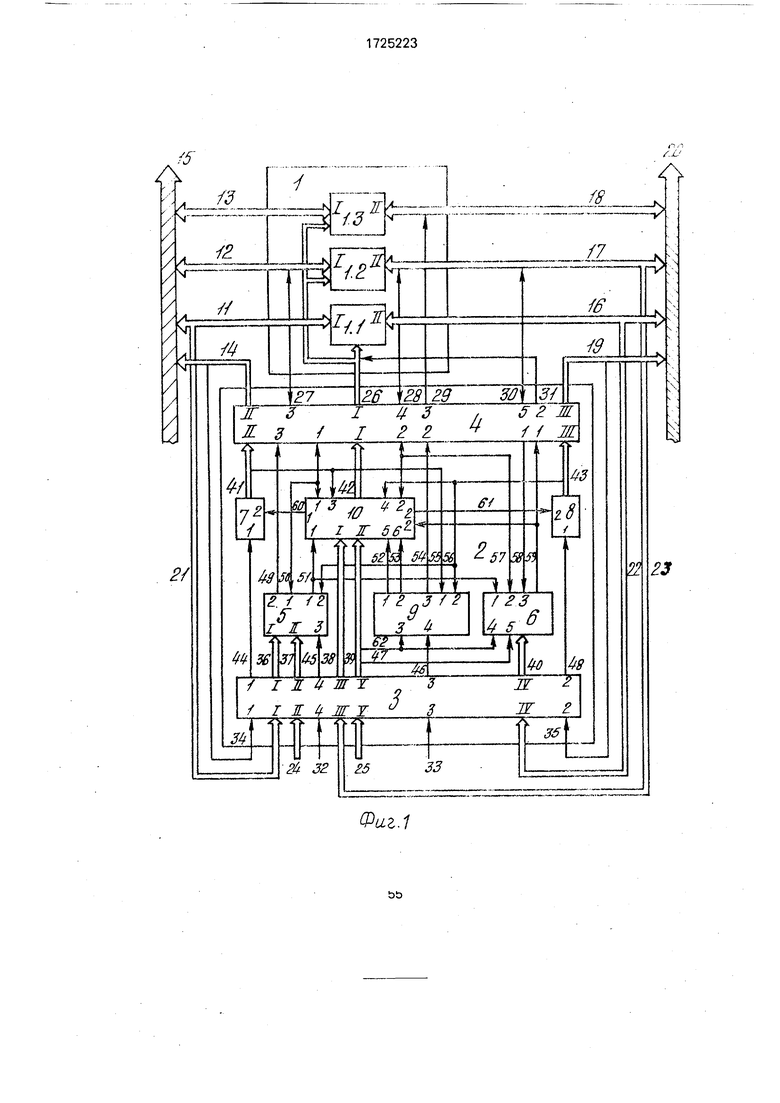

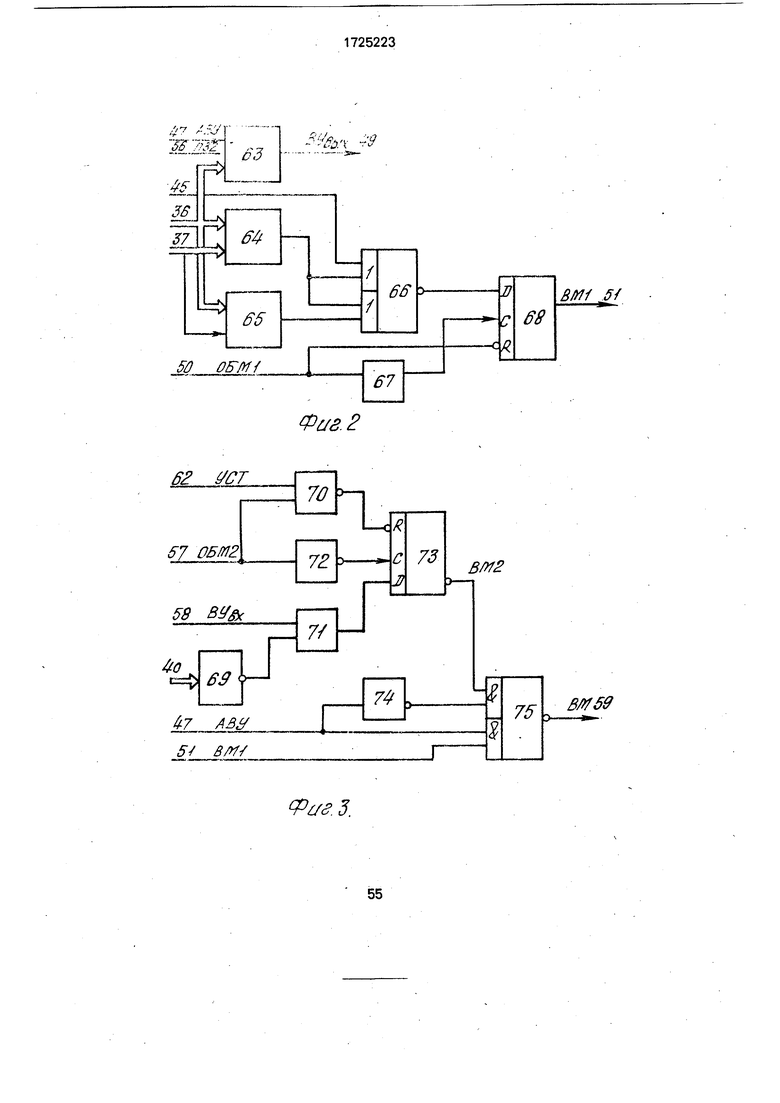

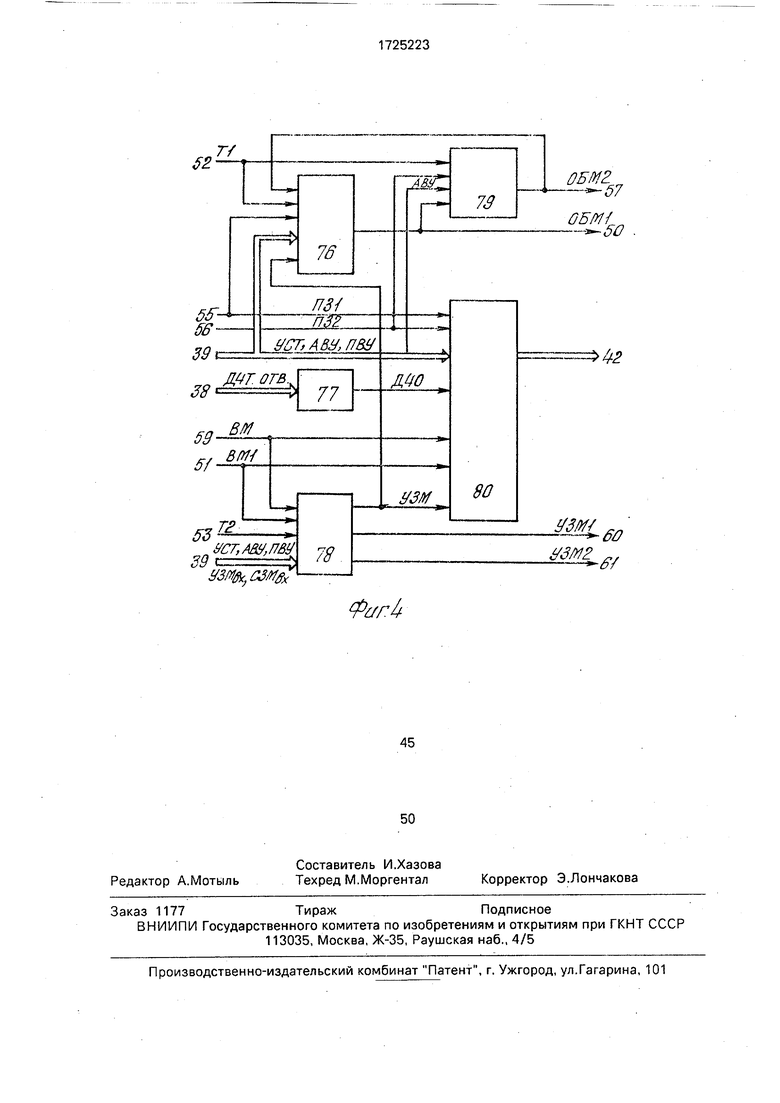

На фиг.1 показана блок-схема устройства; на фиг.2 и 3 - схемы первого селектора адреса и второго селектора адреса; на фиг.4 - блок-схема формирователя управляющих сигналов.

Устройство (фиг.1) содержит блок 1 шинных формирователей (ШФ), включающий первую 1.1, вторую 1.2 и третью .1.3 группы ШФ, и контроллер 2 интерфейса, в состав которого входят входной 3 и выходной 4

блоки приемопередатчиков, первый и второй селекторы 5 и 6 адреса, первый и второй блоки 7 и 8 захвата магистрали, счетчик 9 времени и формирователь 10 управляющих сигналов, шины 11-14 соответственно данных, управления обменом, прерывания и передачи управления первой магистрали 15, а также одноименные шины 16-19 второй магистрали 20, шины 21 и 22 старших разрядов адреса, ряд линий 23 шины 17 управления обменом, шину 24 адресных ключей, шину 25 выбора режима, шину 26 управления блоком 1 ШФ, линии 27 и 28 Синхронизация обмена 1 и 2 (ОБМ 1 и ОБМ 2), линии 29 и 30 Запрос на прерывание (ЗПР) и Выбор устройства (ВУ), линии 31-33 Выбор машины (ВМ), Выбор окна (ВО) и Синхроимпульсы, линии 34 и 35- Разрешение на

XI

ю ел ю ю со

захват магистрали 1 и 2 (РЗМ 1 и РЗМ 2), а также выходные шины 36-40 формирователя 3, входные шины 41-43 формирователя 4 и линии 44-62 внутренних связей контроллера 2 интерфейса.

Первый селектор 5 адреса (фиг.2) состоит из формирователя 63 выходного сигнала Выбор устройства (ВУвых), блоков 64 и 65 сравнения адреса, элемента 66 2ИЛИ-2И-НЕ, элемента 67 задержки и D- триггера 68.

Второй селектор 6 адреса (фиг.З) содержит элемент 4ИЛИ-НЕ 69, два элемента 2ИЛ1/1-НЕ 70 и 71, элемент 72 задержки, D-триггер 73, элемент НЕ 74, элемент 2И- 2ИЛИ-НЕ 75. Счетчик 9 времени состоит из 16-разрядного двоичного счетчика и двух дешифраторов, формирующих сигналы 52 Т1 и 53 Т2.

Формирователь 10 управляющих сигналов (фиг.4) состоит из формирователя 76 сигнала Синхронизация обмена 1 (ОБМ 1), формирователя 77 сигнала Чтение-ответ (ДЧО), формирователя 78 сигналов Установка запроса магистрали (УЗМ, УЗМ 1 и УЗМ 2), формирователя 79 сигнала Синхронизация обмена 2 (ОБМ 2) и формирователя 80 сигналов управления ШФ.

Формирователь 80 вырабатывает сигналы управления ШФ или магистральных приемопередатчиков (МПП); Выбор данных 1, 2, 3 (ВД 1, ВД 2, ВД 3) и Выбор кристалла 1 и2(ВК1 и ВК2). Блок 1 шинных формирователей обеспечивает сопряжение двух магистралей 15и20(МПИ 15и МПИ20). Контроллер 2 интерфейса предназначен для управления работой блока 1 ШФ в четырех режимах: при работе с активными и пассивными внешними устройствами, при программном и аппаратурном сопряжении магистралей.

Входной блок 3 приемопередатчиков предназначен для обеспечения стандартной одиночной нагрузки для входных сигналов и повышения помехозащищенности устройства. Выходной блок 4 приемопередатчиков предназначен для усиления выходных сигналов и формирования выходных и входных-выходных сигналов с трехстабильным уровнем. Первый селектор 5 адреса осуществляет селектирова- ние адреса МПИ 15 по заданному ключу и фиксированному окну памяти, он вырабатывает сигналы Выбор машины 1(ВМ 1), вых.51 и 49. Второй селектор 6 адреса при обращении к нему процессора по адресу, превышающему адресное пространство резидентной памяти, вырабатывает сигнал Выбор машины 2 (ВМ 2) и сигнал ВМ (ВМ ВМ 1 -АВУ + ВМ2 -АВУ), вых.59.

Блок 7 обеспечивает арбитраж и захват первой магистрали 15, включение в работу формирователя 10 управляющих сигналов для выработки сигналов управления блоком 1 ШФ и выходного сигнала ОБМ 1, а также включение в работу счетчика 9 времени.

Блок 8 обеспечивает арбитраж и захват второй магистрали 20, включение в работу формирователя 10 управляющих сигналов для выработки им сигналов управления блоком 1 ШФ и выходного сигнала ОБМ 2, включение в работу счетчика 9 времени с целью формирования им временной задержки Т 1.

Счетчик 9 времени формирует временные интервалы на выходе 52 (Т 1) и выходе 53 (Т 2), а также сигнал на выходе 54 Запрос на прерывание (ЗПР), который является выходным сигналом счетчика 9, Т 1 150 НС необходим для выработки сигналов ОБМ 1 и ОБМ 2. Т 2 УСТ + ЗПР. Он служит для сброса сигналов УЗМ (вых.60 и 61) и выключения блоков 7 и 8, длительность сигнала ЗПР (вых.54) 50 МКС. Этот сигнал необходим для формирования сигнала прерывания при превышении контрольного времени захвата первой магистрали 15 (Тконтр. 2,7 мс).

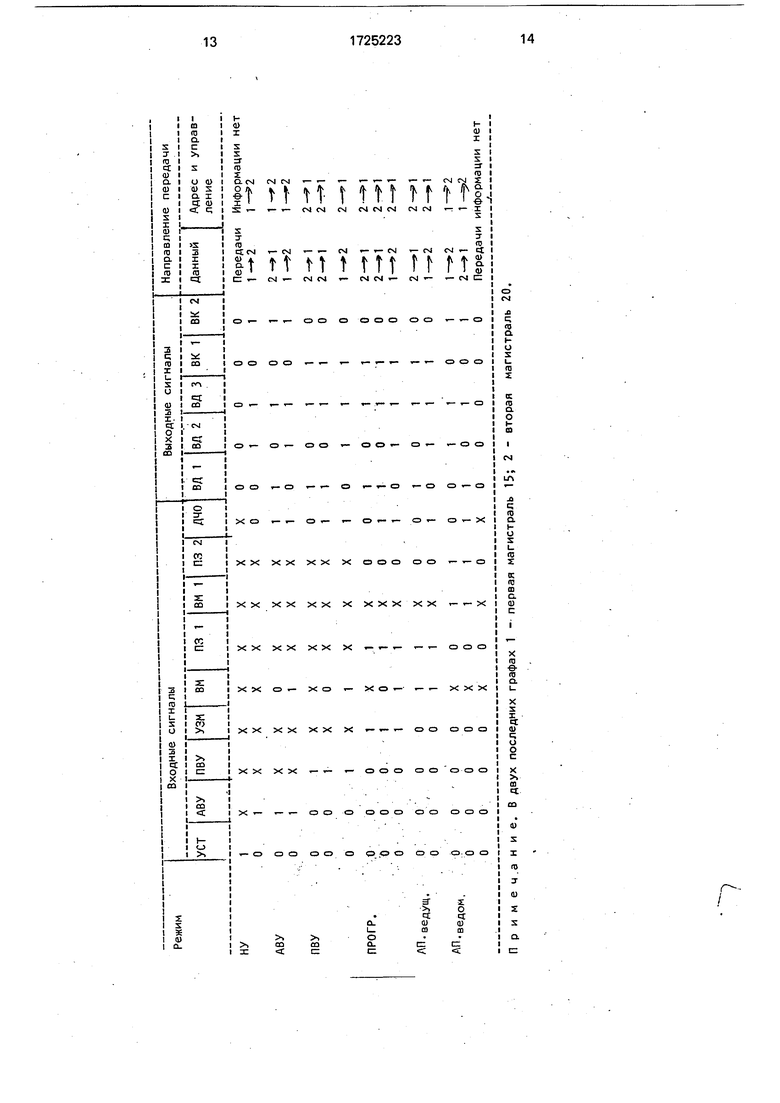

Формирователь 10 управляющих сигналов обеспечивает выработку сигналов управления блоком 1 ШФ, а также выходных сигналов ОБМ 1 (вых.50). ОБМ 2 (5), ДЧО, УЗМ 1 (60) и УЗМ 2 (61). Сигналы управления блоком 1 ШФ (ВД 1, ВД2 , ВД 3, ВК 1 и ВК 2) вырабатываются в соответствии с таблицей истинности (см. таблицу), а сигналы ОБМ 1, ОБМ 2, УЗМ 1 и УЗМ 2 формируются на основании следующих выражений:

ОБМ 1 УСТ-АВУ + (ПВУ + + ПЗ 1-(УЗМ + Т1)-ОБМ2;

0

5

0

5

0

5

0

45 ОБМ2 (АВУ + П32-Т1)-ОБМ 1; УЗМ 1 АВУ-Т2-ПВУ-(ВМ + УЗМ);

50

УЗМ2 АВУ-ПВУ-Т2-УЗМ-ВМ 1.

Сигнал УЗМ вырабатывается в формирователе 78 RS-триггером, на S-вход которого подается входной сигнал УЗМ ВХ, а на R-вход сигнал СЗМ ВХ + Т2, сигналы УЗМ ВХ и СЗМ ВХ поступают на схему по шине 39.

Сигнал ДЧО вырабатывается в формирователе 77 RS-триггером, на S-вход которого поступает сигнал ДЧТ, а на R-вход сигнал ДЧТ + ОТВ, сигналы ДЧТ и ОТВ поступают на схему по шине 38.

Устройство работает следующим образом.

Выбор режима работы устройства зависит от подачи сигналов по шине 25. Начальная установка устройства осуществляется по сигналу Установка (УСТ), поступающему по шине 25 выбора режима от пульта или процессора на один из входов группы V-BXO- дов блока 3. Сигнал УСТ с одного из выходов группы V-выходов блока 3 по шине 39 поступает на вход 11 группы входов формирователя 10 управляющих сигналов, а по линии 62 - на вход счетчика 9 времени и на вход второго селектора 6 адреса.

По сигналу УСТ сбрасываются счетчик 9 времени, второй селектор 6 адреса, блоки 7 и 8 (при выключении сигналов УЗМ 1 и УЗМ 2), а также обнуляются все сигналы управления ШФ (см. таблицу, режим НУ), которые поступают на управляющие входы блока 1 ШФ по шине 26 и выключают его (выходы ШФ переводятся в состояние высокого импеданса), связь между магистралями 15 и 20 разрывается, устройство переходит в исходное состояние.

Режим АВУ - работа с активным внешним устройством (АВУ), имеющим режим прямого доступа в память , например с другим процессором или другой микро-ЭВМ, режим АВУ устанавливается сигналом АВУ. В качестве сигнала АВУ может быть использован сигнал Подтверждение запроса (ПЗ), вырабатываемый в активном внешнем устройстве после захвата внутренней магистрали микро-ЭВМ. Сигнал АВУ по шине 25 с активного внешнего устройства поступает на один из входов блока 3. С одного из выходов этого блока по шине 39 сигнал поступает на один из входов формирователя 10 управляющих сигналов и по линии 47 на вход второго селектора 6 адреса. В формирователе 10 управляющих сигналов сигнал АВУ поступает на входы формирователей 76, 78, 79 и 80 сигналов ОБМ 1, УЗМ, ОБМ 2 и управления ШФ. Сигнал АВУ позволяет вырабатывать сигнал ОБМ 2 и блокирует формирование сигналов ОБМ 1, УЗМ 1 и УЗМ 2. Во втором селекторе 6 адреса сигнал АВУ участвует в формировании сигнала ВМ, который по линии 59 поступает на первый вход блока 4 и по линии 31 с второго его выхода поступает на шину 26 управления ШФ, по шине 26 этот сигнал поступает на группу 1.2 шинных формирователей для управления направлением передачи сигналов Ответ, Ответ по адресу и Регенерация,

Формирователь 80.сигналов управления ШФ по сигналу АВУ вырабатывает сигналы управления ВД 1 - ВД 3, ВК2. которые с его выхода по шине 42 поступают на первую группу входов блока 4. С группы выходов блока 4 по шине 26 эти сигналы

поступают на входы управления ШФ, осуществляя передачу информации из шины 15 в шину 20.

Реверс передачи данных осуществляется с помощью сигнала Чтение-ответ

0 (ДЧО), который вырабатывается в формирователе 77 по переднему фронту сигнала Чтение данных (ДЧТ) и заднему фронту сигнала Ответ (ОТВ), сигналы ДЧТ и ОТВ подаются из шины 17 управления обменом

5 по шине 23 на третью группу входов блока 3 и с третьей группы выходов этого.блока по шине 38 на группу входов формирователя 10 управляющих сигналов, где поступают на вход формирователя 77 сигнала ДЧО. Сиг0 нал ДЧО подается на один из входов формирователя 80 сигналов управления ШФ, по этому сигналу формирователь 80 изменяет значение сигналов ВД Т и ВД 2 на противоположное, обеспечивая тем самым реверс

5 передачи данных по сигналу ДЧО.

Режим ПВУ обеспечивает работу с пассивным внешним устройством (ПВУ), например с дополнительным запоминающим устройством, в режиме работы с ПВУ обес0 печивается также режим прослушивания внутренней магистрали микро-ЭВМ. Режим ПВУ устанавливается сигналом ПВУ, который может приходить от пассивного внешнего устройства или из рабочего места

5 программиста по шине 25 на один из входов блока 3, с одного из выходов этого блока по шине 39 сигнал ПВУ подается на один из входов формирователя,10 управляющих сигналов, в этом формирователе сигнал ПВУ по0 ступает на входы формирователей 76,78 и 80. В формирователе 76 сигнала ОБМ 1 сигнал ПВУ разрешает прохождение сигнала ОБМ 2 при отсутствии сигнала УСТ и АВУ. Таким образом, в режиме ПВУ сигнал ОБМ

5 1 формируется всегда, когда появляется сигнал ОБМ 2 во второй магистрали 20. Сигнал ОБМ 1 по линии 50 подается на первый вход-выход блока 4, а также на первый вход первого селектора 5 адреса, с третьего вхо0 да-выхода блока 4 по линии 27 сигнал ОБМ 1 подается на шину 12 управления обменом первой магистрали 15, в первом селекторе 5 адреса (фиг.2) сигнал ОБМ 1 подается на вход элемента 67 задержки и на R-вход D5 триггера 68. Этот сигнал снимает сброс с D-триггера и, проходя через элемент 67 задержки, устанавливает по С-входу триггер 68 в состояние, определяемое информацией на его D-входе. Если старшие разряды интерфейсного адреса совпадают с адресными ключами, то D-триггер срабатывает и на его выходе формируется сигнал ВМ 1. По линии 51 сигнал ВМ 1 подается во второй селектор 6 адреса, где из сигналов ВМ 1 и ВМ 2 формируется сигнал ВМ.

В формирователе 78 сигналов УЗМ сигнал ПВУ поступает на один из его входов, блокируя формирование сигналов УЗМ 1 и УЗМ 2. В формирователе 80 сигналов управления ШФ по сигналу ПВУ вырабатываются сигналы управления ВД 1 - ВД 3 и ВК 1 (см. таблицу).

Режим прогр. (программное сопряжение магистралей) устанавливается входным сигналом Установка запроса магистрали (УЗМ ВХ) при отсутствии сигналов АВУ и ПВУ. Сигнал УЗМ ВХ формируется специальной командой процессора и в устройство может подаваться, например, от контроллера внешних устройств, сигнал УЗМ ВХ по шине 25 поступает на один из входов блока 3, с одного из выходов этого блока по шине 39 сигнал УЗМ ВХ поступает на один из входов формирователя 10 управляющих сигналов, где подается на вход формирователя 78 сигналов УЗМ (фиг,4). В формирователе 78 сигналов УЗМ вырабатывается сигнал УЗМ 1, который по линии 60 поступает на вход 2 блока 7 и включает его в работу. В блоке 7 сигнал УЗМ 1 блокирует прохождение сигнала РЗМ 1 и формирует на выходе сигнал ЗМ 1, по шине 41 сигнал ЗМ 1 подается на один из входов блока 4, с одного из выходов блока 4 сигнал ЗМ 1 по шине 14 подается в первую магистраль 15. Если магистраль 15 свободна, то вырабатывается сигнал РЗМ 1, который по шине 14 и линии 34 поступает на первый вход блока 3, сигнал РЗМ 1 по линии 44 подается на первый вход блока 7, на выходе блока 7 формируется сигнал ПЗ 1 и сбрасывается сигнал ЗМ 1, сигнал ПЗ 1 с выхода блока 7 по шине 41 подается на один из входов блока 4, а также по линии 55 на вход формирователя 10 управляющих сигналов и на вход счетчика 9 времени.

С одного из выходов блока 4 по шине 14 сигнал ПЗ 1 поступает на первую магистраль 15, завершая цикл захвата магистрали, в формирователе 10 управляющих сигналов сигнал ПЗ 1 поступает на вход формирователя 76 сигнала ОБМ 1 и на вход формирователя 80 сигналов управления ШФ. Формирователь 76 сигнала ОБМ 1 вырабатывает сигнал ОБМ 1. При подаче сигнала ПЗ 1 на вход формирователя 80 сигналов управления ШФ этот формирователь вырабатывает сигналы управления ВД 1 - ВД 3, ВК 1 и включает ШФ на передачу информации из второй магистрали 20 в первую магистраль 15, осуществляя реверс передачи данных по сигналу ДЧО, когда процессор в ведущей микро-ЭВМ заканчивает обмен информацией с внешним устройством, под5 ключенным к внешней магистрали 15, он специальной командой формирует сигнал Сброс запроса магистрали (СЗМ ВХ), который по шинам 25 и 39 подается на вход формирователя 78 сигнале УЗМ и сбрасыва10 ет сигнал УЗМ 1, блок 7 выключается, а связь между магистралями 15 и 20 обрывается.

При адресном обмене одним массивом информации при программном сопряжении двух магистралей осуществляется контроль

5 времени захвата первой магистрали 15. Сигнал ПЗ 1 поступает на вход счетчика 9 времени и снимает сигнал сброса, Синхроимпульсы от внешнего генератора по линии 33 поступают на вход блока 3. С

0 выхода этого блока по линии 46 синхроимпульсы поступают на вход двоичного счетчика, который начинает их счет, при частоте следования синхроимпульсов 12 мГц через 2,7 мс после начала работы двоичного счет5 чика на его выходе формируется сигнал ЗПР, который по линии 54 подается на второй вход блока 4. С выхода этого блока сигнал ЗПР по линии 29 поступает на шину 18, по которой поступает на вход контроллера

0 прерываний. Еще через 85,3 мкс на выходе счетчика 9 формируется сигнал Т 2, который по линии 53 поступает на один из входов формирователя 78 сигналов УЗМ и сбрасывает сигнал УЗМ 1. Блок 7 освобождает ма5 гистраль 15, сбрасывая сигнал ПЗ 1, формирователь 76 сигнала ОБМ 1 сбрасывает сигнал ОБМ 1, а формирователь 80 выключает ШФ. Таким образом, цикл обмена информацией между магистралями 15 и 20

0 принудительно заканчивается и магистраль 15 освобождается для работы с другими микро-ЭВМ.

Режим аппаратурного сопряжения магистралей устанавливается при отсутствии

5 сигналов УСТ, АВУ, ПВУ и УЗМ, при этом сигнал ВМ в ведущей микро-ЭВМ устанавливает режим АПведущ, а сигнал ВМ 1 в ведомой микро-ЭВМ - режим АПведом.

Работу устройства в режимах АПведущ и

0 АПведом рассматривают на примере работы устройства в децентрализованной вычислительной системе, в которой к системной магистрали 15(МПИ 1) подключено несколько микро-ЭВМ и ВЗУ.

5 В режиме АПведущ в ведущей микро- ЭВМ, например в микро-ЭВМ 1,по переднему фронту сигнала ОБМ 2, вырабатываемого центральным процессором на магистрали 20 и передаваемого по шине 17, линиям 28 , второй селектор 6 адреса формирует

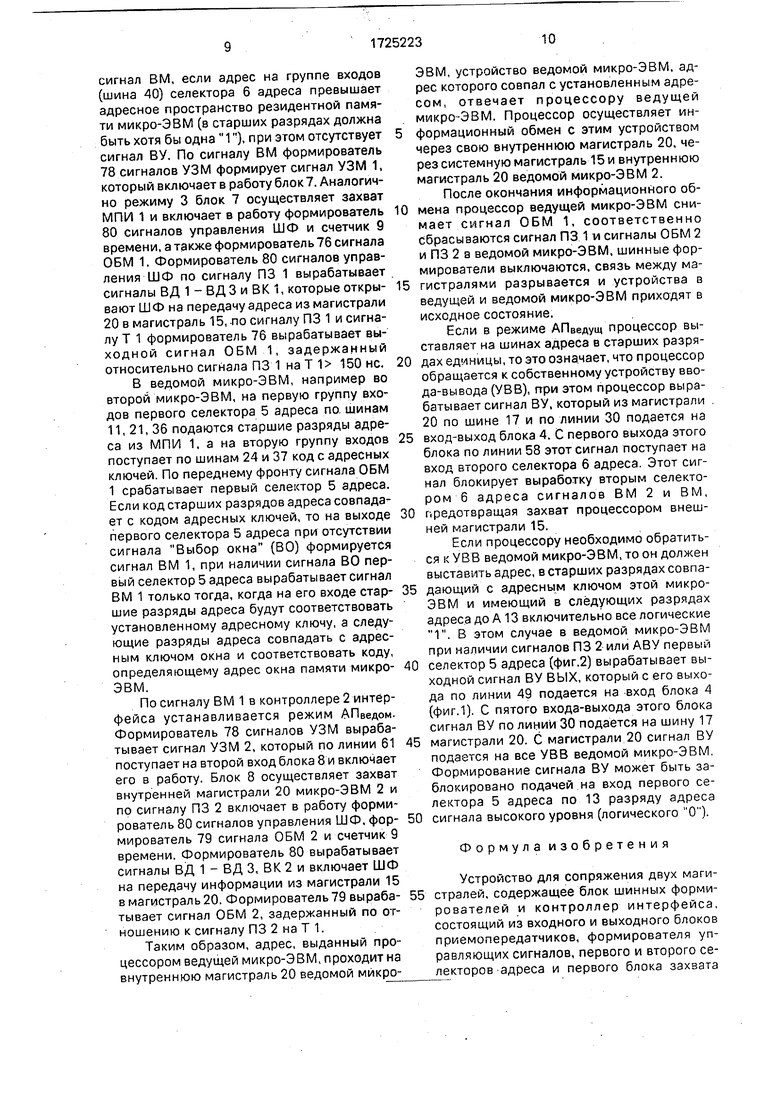

сигнал ВМ, если адрес на группе входов (шина 40) селектора 6 адреса превышает адресное пространство резидентной памяти микро-ЭВМ (в старших разрядах должна быть хотя бы одна 1), при этом отсутствует сигнал ВУ. По сигналу ВМ формирователь 78 сигналов УЗМ формирует сигнал УЗМ 1, который включает в работу блок 7. Аналогично режиму 3 блок 7 осуществляет захват МПИ 1 и включает в работу формирователь 80 сигналов управления ШФ и счетчик 9 времени, а также формирователь 76 сигнала ОБМ 1. Формирователь 80 сигналов управления ШФ по сигналу ПЗ 1 вырабатывает сигналы ВД 1 - ВД 3 и ВК 1, которые открывают ШФ на передачу адреса из магистрали 20 в магистраль 15, ло сигналу ПЗ 1 и сигналу Т 1 формирователь 76 вырабатывает выходной сигнал ОБМ 1, задержанный относительно сигнала ПЗ 1 на Т 1 150 не.

В ведомой микро-ЭВМ, например во второй микро-ЭВМ, на первую группу входов первого селектора 5 адреса по. шинам 11, 21, 36 подаются старшие разряды адреса из МПИ 1. а на вторую группу входов поступает по шинам 24 и 37 код с адресных ключей. По переднему фронту сигнала ОБМ 1 срабатывает первый селектор 5 адреса. Если код старших разрядов адреса совпадает с кодом адресных ключей, то на выходе первого селектора 5 адреса при отсутствии сигнала Выбор окна (ВО) формируется сигнал ВМ 1, при наличии сигнала ВО первый селектор 5 адреса вырабатывает сигнал ВМ 1 только тогда, когда на его входе старшие разряды адреса будут соответствовать установленному адресному ключу, а следующие разряды адреса совпадать с адресным ключом окна и соответствовать коду, определяющему адрес окна памяти микро- ЭВМ.

По сигналу ВМ 1 в контроллере 2 интерфейса устанавливается режим АПведом. Формирователь 78 сигналов УЗМ вырабатывает сигнал УЗМ 2, который по линии 61 поступает на второй вход блока 8 и включает его в работу. Блок 8 осуществляет захват внутренней магистрали 20 микро-ЭВМ 2 и по сигналу ПЗ 2 включает в работу формирователь 80 сигналов управления ШФ, формирователь 79 сигнала ОБМ 2 и счетчик 9 времени. Формирователь 80 вырабатывает сигналы ВД 1 - ВД 3, ВК 2 и включает ШФ на передачу информации из магистрали 15 в магистраль 20. Формирователь 79 вырабатывает сигнал ОБМ 2, задержанный по отношению к сигналу ПЗ 2 на Т 1.

Таким образом, адрес, выданный процессором ведущей микро-ЭВМ, проходит на внутреннюю магистраль 20 ведомой микроЭВМ, устройство ведомой микро-ЭВМ, адрес которого совпал с установленным адресом, отвечает процессору ведущей микро-ЭВМ. Процессор осуществляет информационный обмен с этим устройством через свою внутреннюю магистраль 20, через системную магистраль 15 и внутреннюю магистраль 20 ведомой микро-ЭВМ 2.

После окончания информационного обмена процессор ведущей микро-ЭВМ снимает сигнал ОБМ 1, соответственно Сбрасываются сигнал ПЗ 1 vi сигналы ОБМ 2 и ПЗ 2 в ведомой микро-ЭВМ, шинные формирователи выключаются, связь между магистралями разрывается и устройства в ведущей и ведомой микро-ЭВМ приходят в исходное состояние.

Если в режиме АПведущ процессор выставляет на шинах адреса в старших разрядах единицы, то это означает, что процессор обращается к собственному устройству ввода-вывода (УВВ), при этом процессор вырабатывает сигнал ВУ, который из магистрали 20 по шине 17 и по линии 30 подается на

вход-выход блока 4. С первого выхода этого блока по линии 58 этот сигнал поступает на вход второго селектора 6 адреса. Этот сигнал блокирует выработку вторым селектором 6 адреса сигналов ВМ 2 и ВМ,

предотвращая захват процессором внешней магистрали 15.

Если процессору необходимо обратиться к УВВ ведомой микро-ЭВМ, то он должен выставить адрес, в старших разрядах совпадающий с адресным ключом этой микро- ЭВМ и имеющий в следующих разрядах адреса до А13 включительно все логические 1, В этом случае в ведомой микро-ЭВМ при наличии сигналов ПЗ 2 или АВУ первый

селектор 5 адреса (фиг.2) вырабатывает выходной сигнал ВУ ВЫХ, который с его выхода по линии 49 подается на -вход блока 4 (фиг.1). С пятого входа-выхода этого блока сигнал ВУ по линии 30 подается на шину 17

магистрали 20. С магистрали 20 сигнал ВУ подается на все УВВ ведомой микро-ЭВМ. Формирование сигнала ВУ может быть заблокировано подачей на вход первого селектора 5 адреса по 13 разряду адреса

сигнала высокого уровня (логического О).

Формула изобретения

Устройство для сопряжения двух маги- стралей, содержащее блок шинных формирователей и контроллер интерфейса, состоящий из входного и выходного блоков приемопередатчиков, формирователя управляющих сигналов, первого и второго селекторов-адреса и первого блока захвата

магистрали, первый вход которого соединен с первым выходом входного блока приемопередатчиков, а второй вход- с первым выходом формирователя управляющих сигналов, первый, второй и третий входы которого подключены соответственно к первому выходу первого селектора адреса, к выходу второго селектора адреса, соединенного также с первым входом выходного блока приемопередатчиков, и к группе выходов первого блока захвата магистрали, первый вход-выход формирователя управляющих сигналов соединен с первым входом первого селектора адреса и с первым входом-выходом выходного блока приемопередатчиков, второй вход-выход - с первым входом второго селектора адреса и с вторым входом-выходом выходного блока приемопередатчиков, группа выходов формирователя управляющих сигналов - с первой группой входов выходного блока приемопередатчиков, вторая группа входов которого подключена к группе выходов первого блока захвата магистрали, первая группа выходов выходного блока приемопередатчиков - к группе управляющих входов блока шинных формирователей, вторая группа выходов является шиной передачи управления первой магистрали устройства, одна из линий которой соединена с первым входом входного блока приемопередатчиков, с первой по четвертую группы входов которого являются линиями старших разрядов адреса первой магистрали, шиной адресных ключей устройства, шиной управления обменом второй магистрали устройства и линиями старших разрядов адреса второй магистрали устройства, с первой по четвертую группы выходов подключены соответственно к первой и второй группам входов первого селектора адреса, к первой группе входов формирователя управляющих сигналов и к группе входов второго селектора адреса, второй вход которого соединен с первым выходом выходного блока приемопередатчиков, второй выход которого является выходом Выбор машины устройства, а третий, четвертый и пятый входы-выходы являются линиями Синхронизация обмена первой и второй магистралей и линией Выбор устройства второй магистрали устройства, первые группы входов-выходов блока шинных формирователей подключены соответственно к шине

обмена информацией, шине управления обменом и к шине прерывания первой магистрали устройства, а их вторые группы входов-выходов - к одноименным шинам

второй магистрали устройства, отличающееся тем, что, с целью расширения области применения, в контроллер интерфейса введены счетчик времени и второй блок захвата магистрали, первый вход которого подсоединен к второму выходу входного блока приемопередатчиков, второй вход - к второму выходу формирователя управляющих сигналов, а группа выходов - к третьей группе входов выходного блока

приемопередатчиков, причем один из выходов второго блока захвата магистрали соединен с четвертым входом формирователя управляющих сигналов, с вторым входом первого селектора адреса и с первым входом счетчика времени, второй вход которого соединен с одним из выходов первого блока захвата магистрали и с третьим входом формирователя управляющих сигналов, а третий вход - с третьим выходом входного

блока приемопередатчиков, первый, второй и третий выходы счетчика времени соединены соответственно с пятым и шестым входами формирователя управляющих сигналов и с вторым входом выходного блока приемопередатчиков, третий выход которого является одной из линий шины прерывания второй магистрали устройства, третья группа выходов выходного блока приемопередатчиков является шиной передачи

управления второй магистрали устройства, причем одна из линий этой шины соединена с вторым входом входного блока приемопередатчиков, пятая группа входов которого является шиной Выбор режима устройства, третий и четвертый входы являются входами Синхроимпульсы и Выбор окна устройства, четвертый выход соединен с третьим входом первого селектора адреса, пятая группа выходов - с второй группой

входов формирователя управляющих сигналов, при этом одна из линий этой группы подключена также к третьему входу второго селектора адреса, а другая линия этой группы соединена с четвертым входом счетчика

времени и четвертым входом второго селектора адреса, пятый вход которого соединен с первым выходом первого селектора адреса, второй выход которого соединен с третьим входом выходного блока приемопередатчиков.

Фиг.1

63

У , 4. j z;

- - t-Д { v

50 OFflff

Фиг. 2

Фхг.З

- fiff

Б

вм jf

67

62

Т/

...4L II 14.

76

М .MIL

УСТ, АЗУ, ПВУ

59- 5/ВМ

ВМ

53

12

39i

&СТ,АВУ,/7ВУ

ySftfoMMfc

73

ОБМ2

OSMf

-50

УЗМ

80

M&L а

РЈ/Г&

| Устройство управления обменом по магистрали | 1984 |

|

SU1226478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-07—Публикация

1989-10-09—Подача